## ILLUSTRATIONS

| PAGE    |             |                                                |

|---------|-------------|------------------------------------------------|

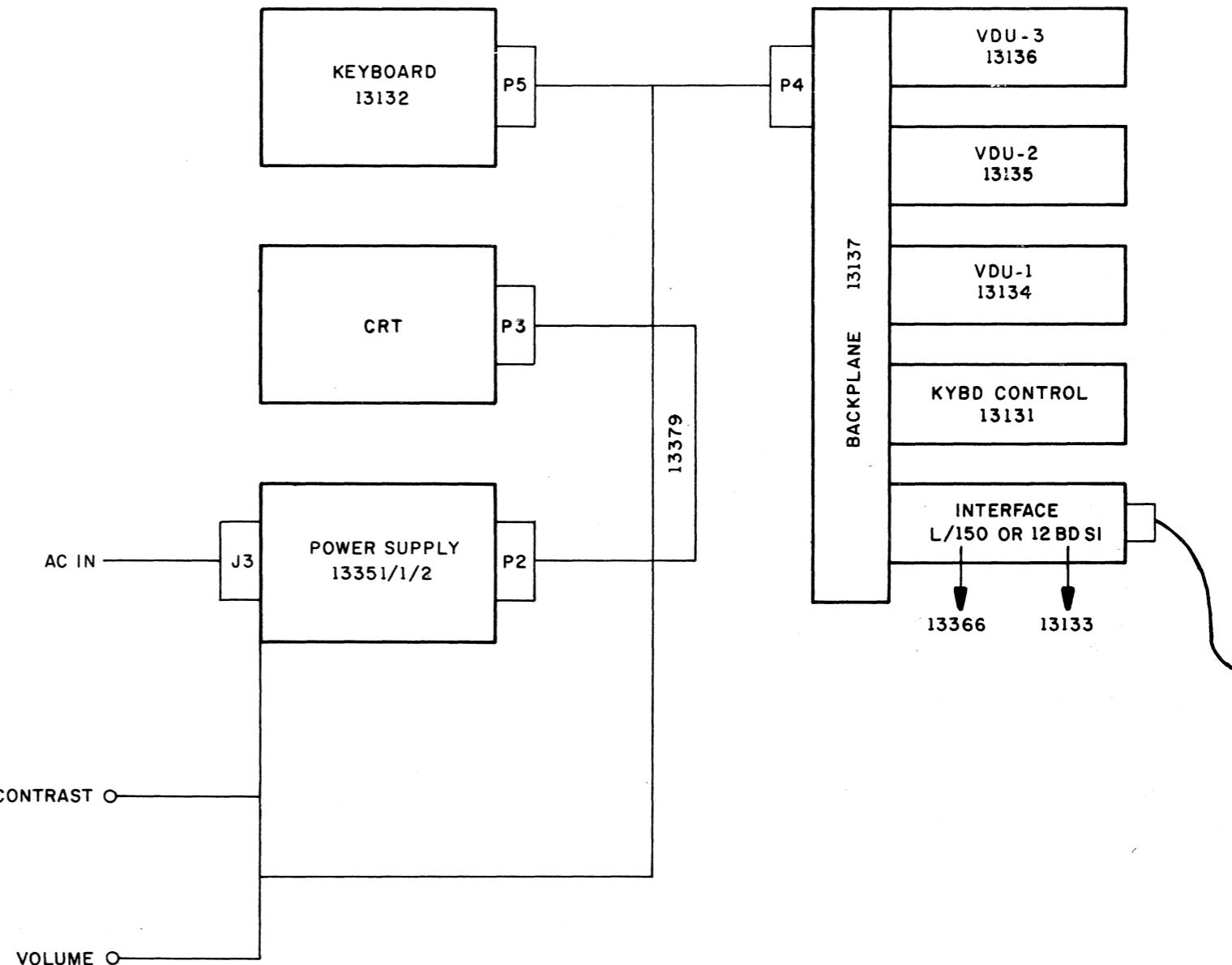

| 2A-1    | Figure 2A-1 | KE 50 DT Configuration                         |

| 2A-1    | 2A-2        | KE 1000 DT Configuration                       |

| 2A-3    | 2A-3        | Data Terminal Indicators                       |

| 2A-3    | 2A-4        | Data Terminal Controls                         |

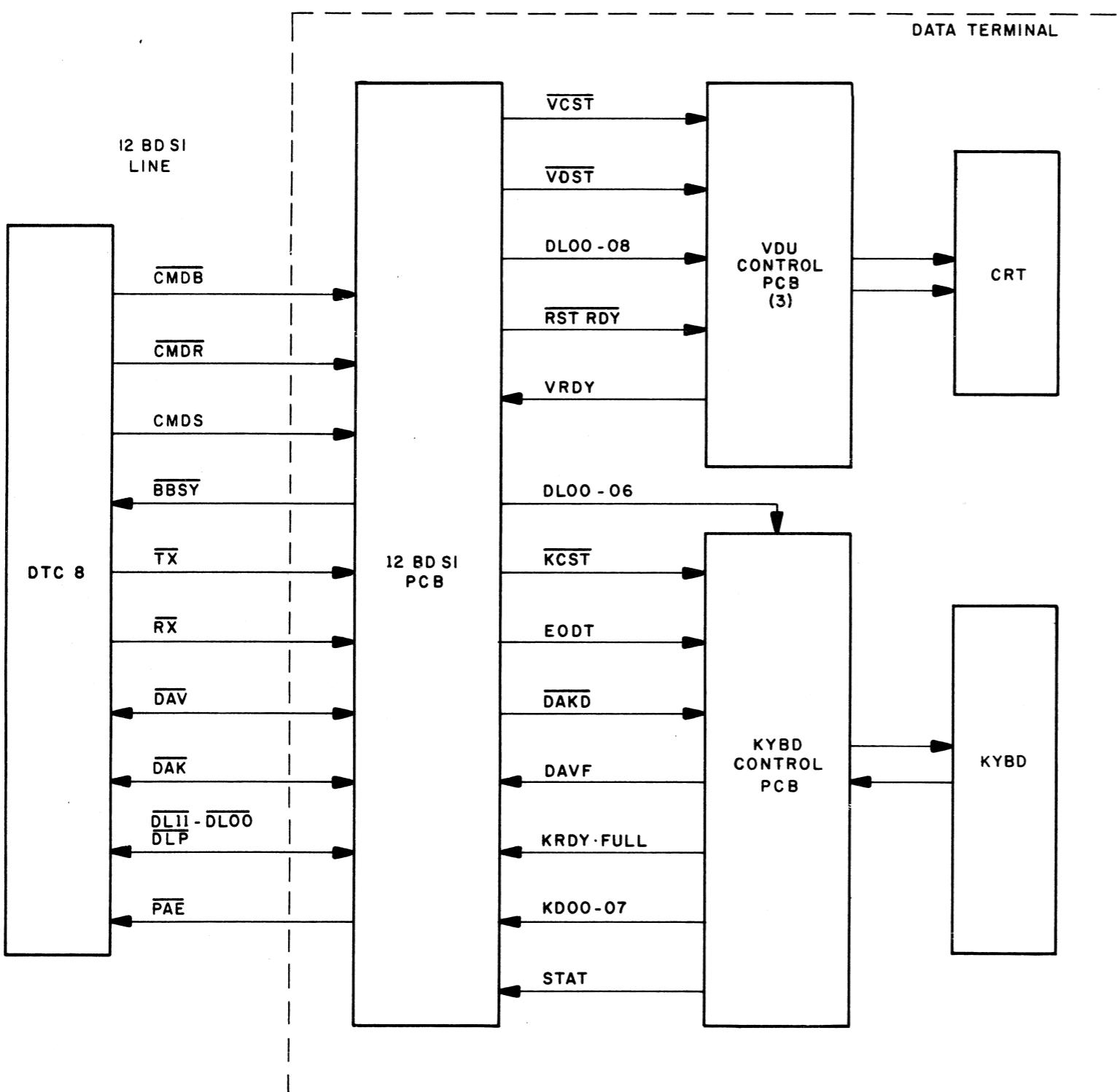

| 2A-5    | 2A-5        | 12 BD SI Data Flow and Control                 |

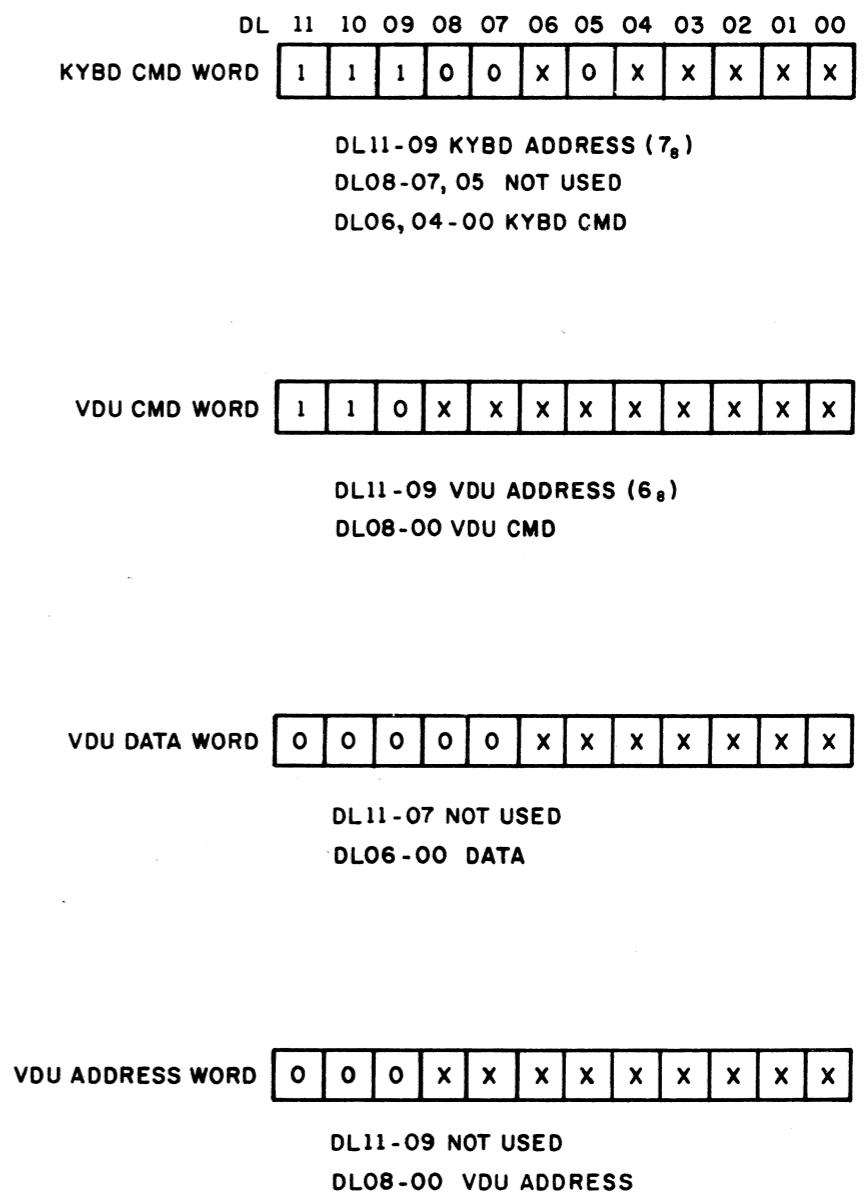

| 2A-5    | 2A-6        | 12 BD SI Transmit Word Structure               |

| 2A-7    | 2A-7        | 12 BD SI Receive Word Structure                |

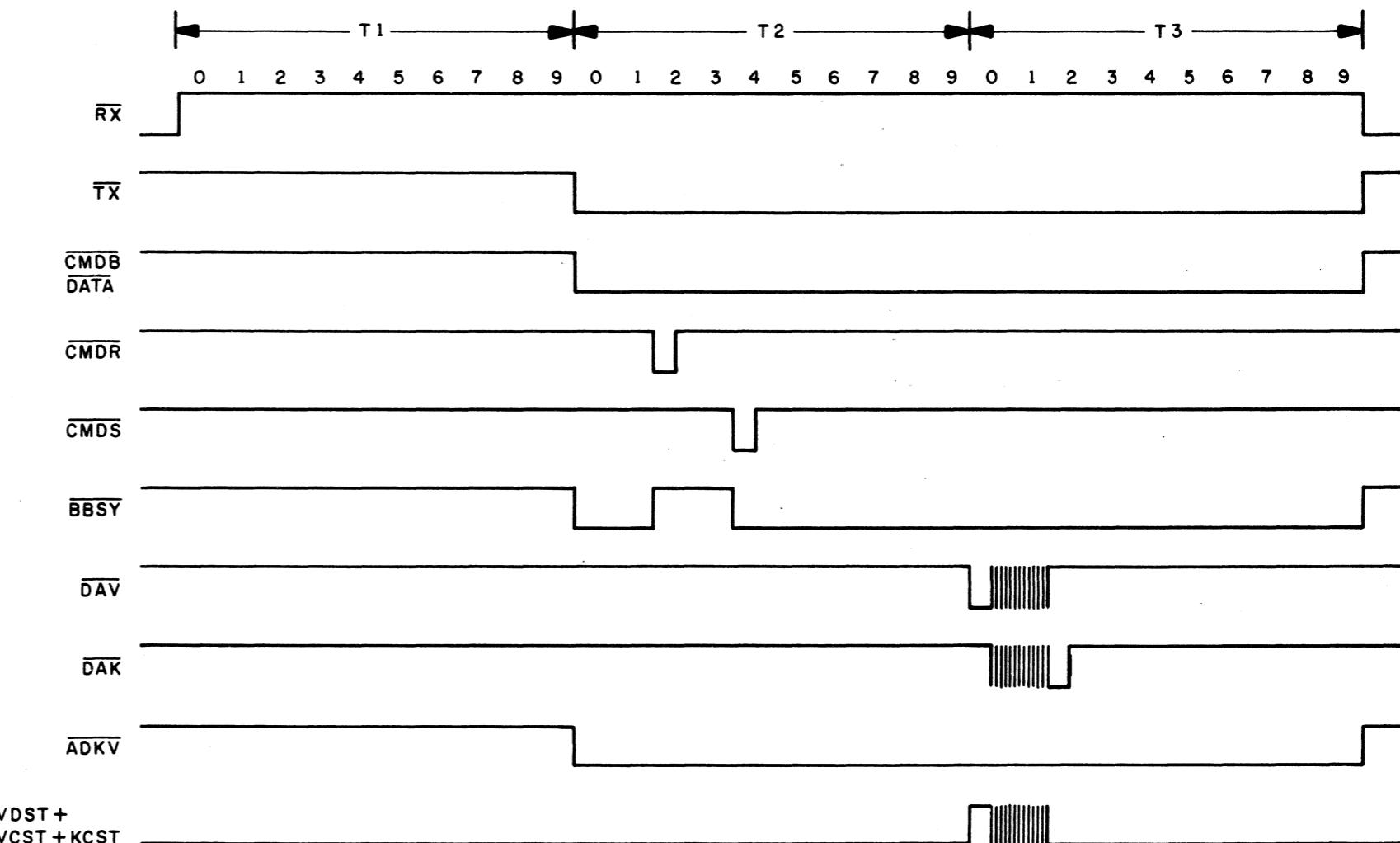

| 2A-8    | 2A-8        | 12 BD SI Transmit Mode Timing                  |

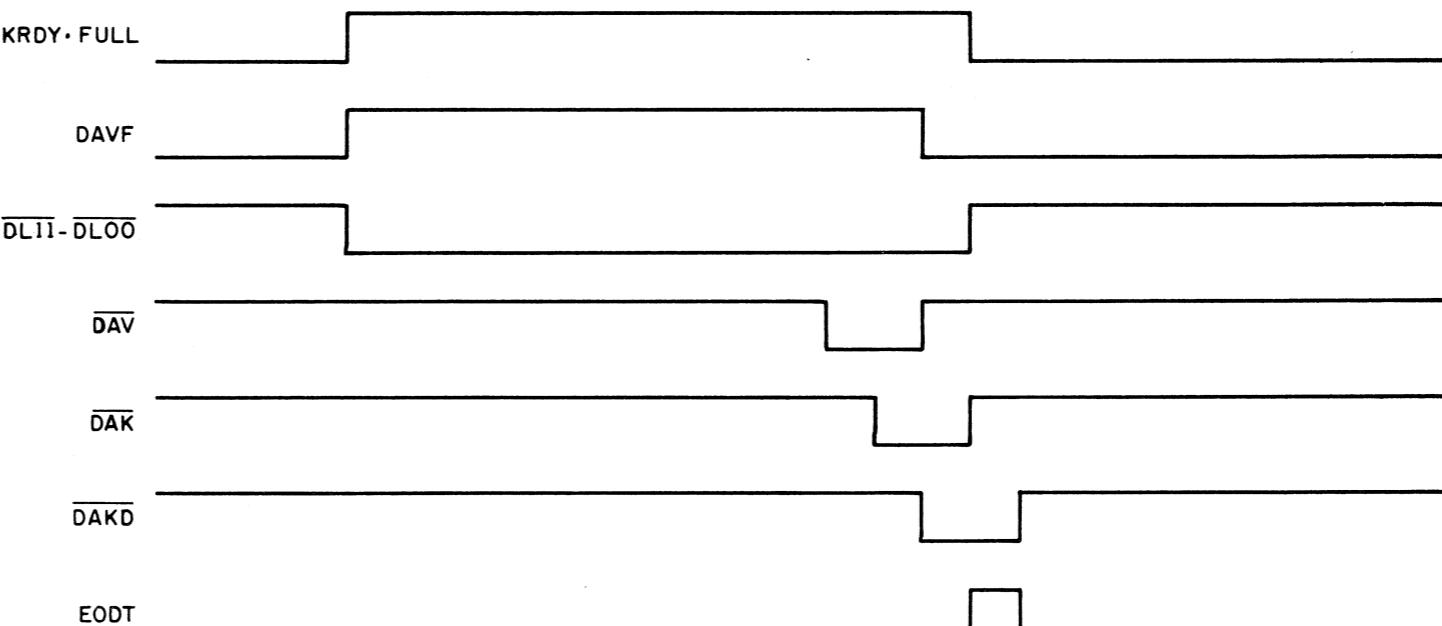

| 2A-9    | 2A-9        | 12 BD SI Receive Mode Timing                   |

| (2A-10) | D13133 L    | 12 BD SI PCB Logic (sheets 1 and 2)            |

| 2A-12   | 2A-10       | L/150 Data Flow and Control                    |

| 2A-13   | 2A-11       | L/150 Transmit Mode Words                      |

| 2A-13   | 2A-12       | L/150 Receive Mode Words                       |

| 2A-14   | 2A-13       | L/150 Transmit Mode Timing                     |

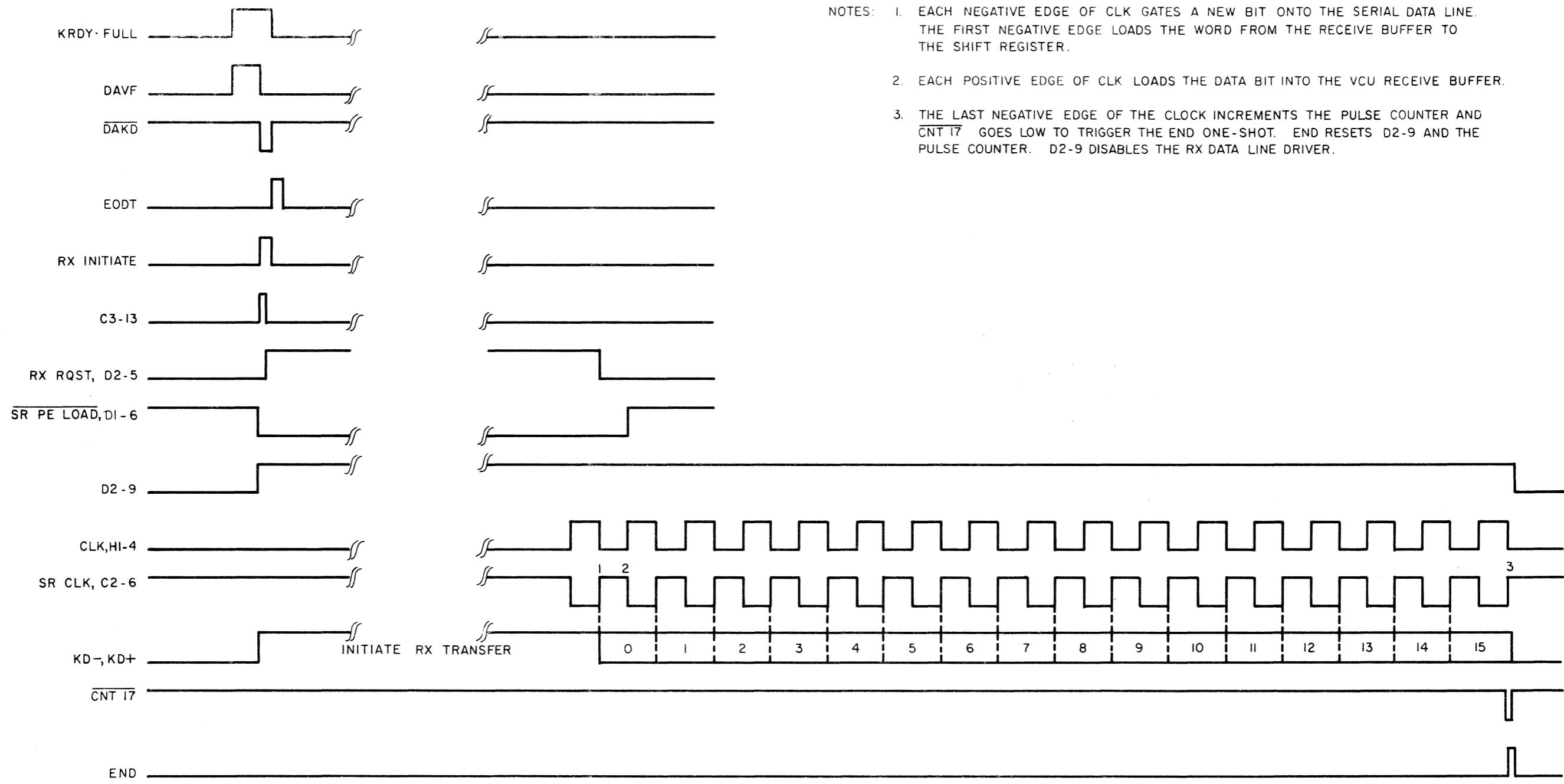

| 2A-15   | 2A-14       | L/150 Receive Mode Timing                      |

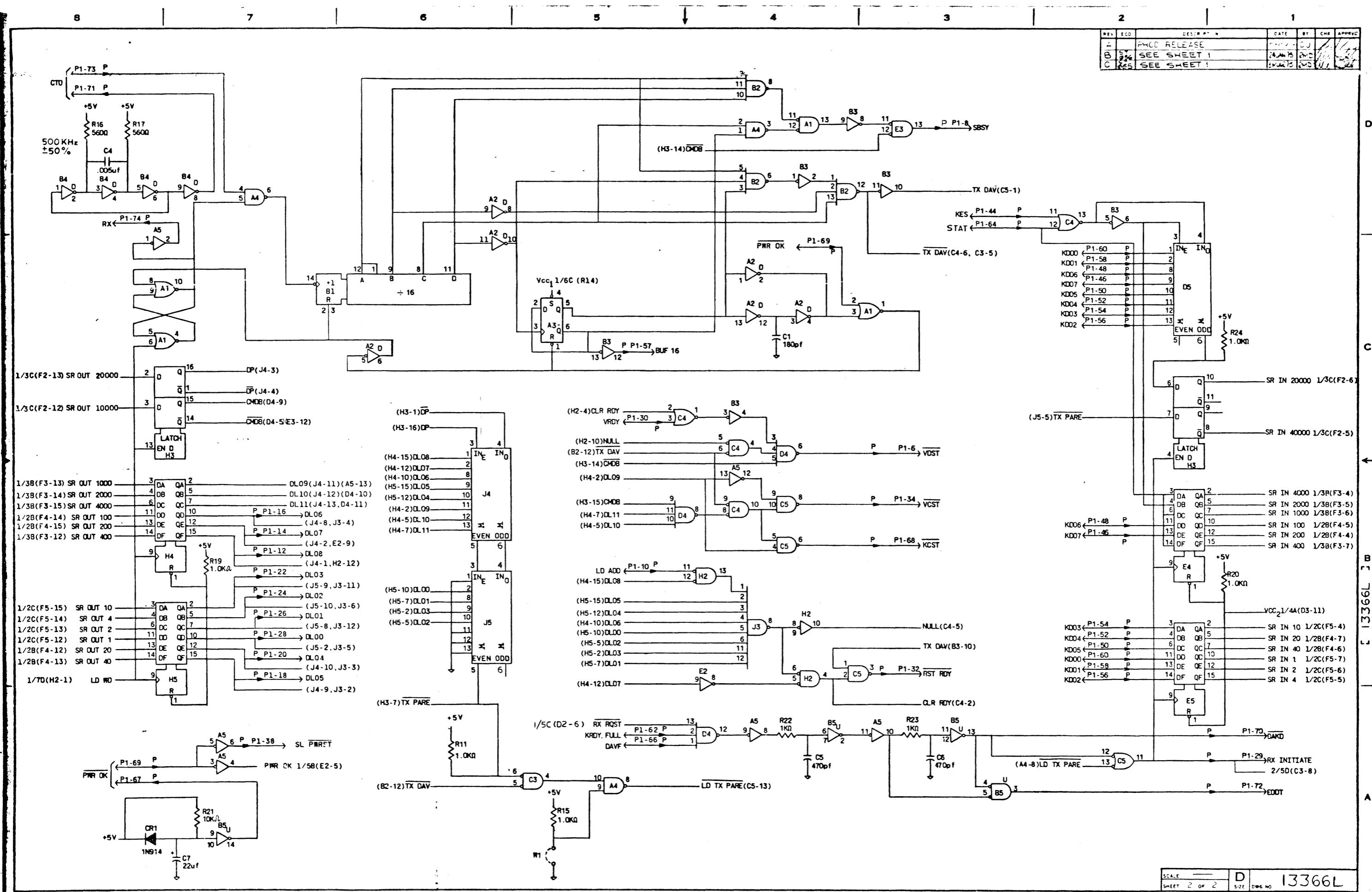

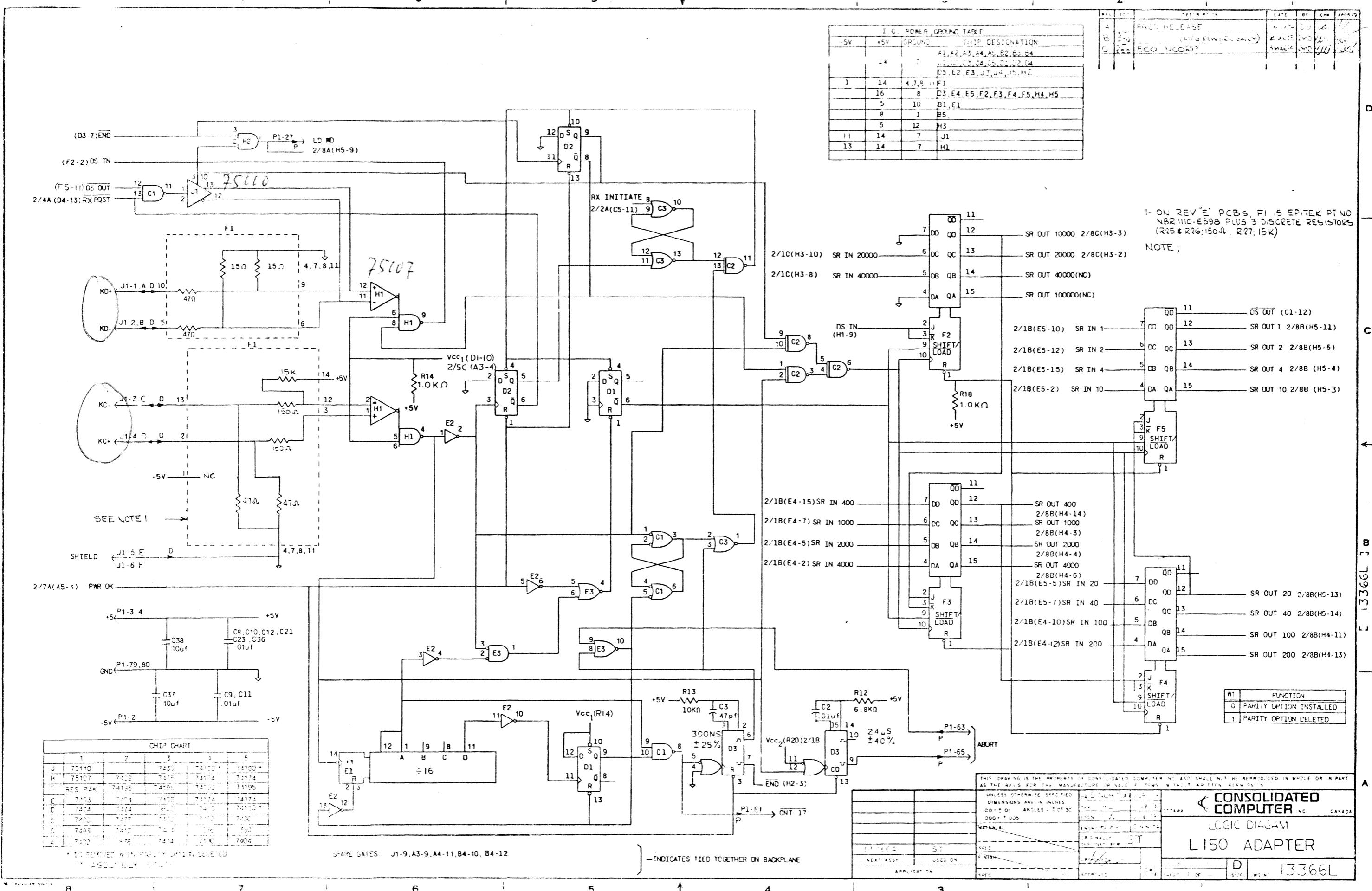

| (2A-17) | D13366 L    | L/150 Adapter PCB Logic (sheets 1 and 2)       |

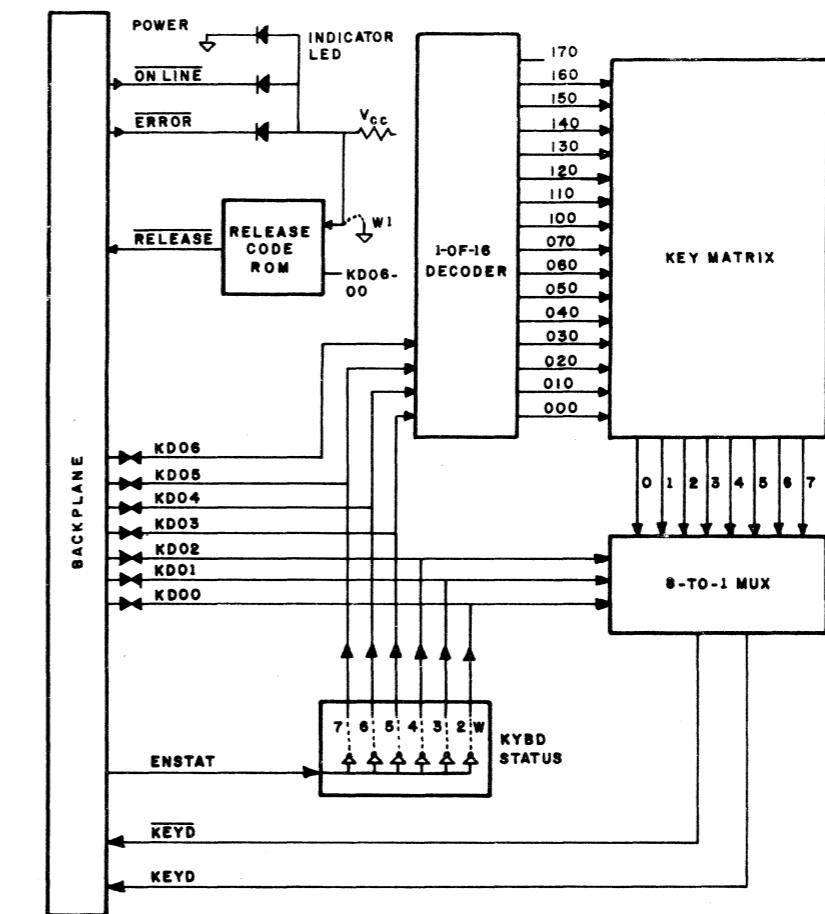

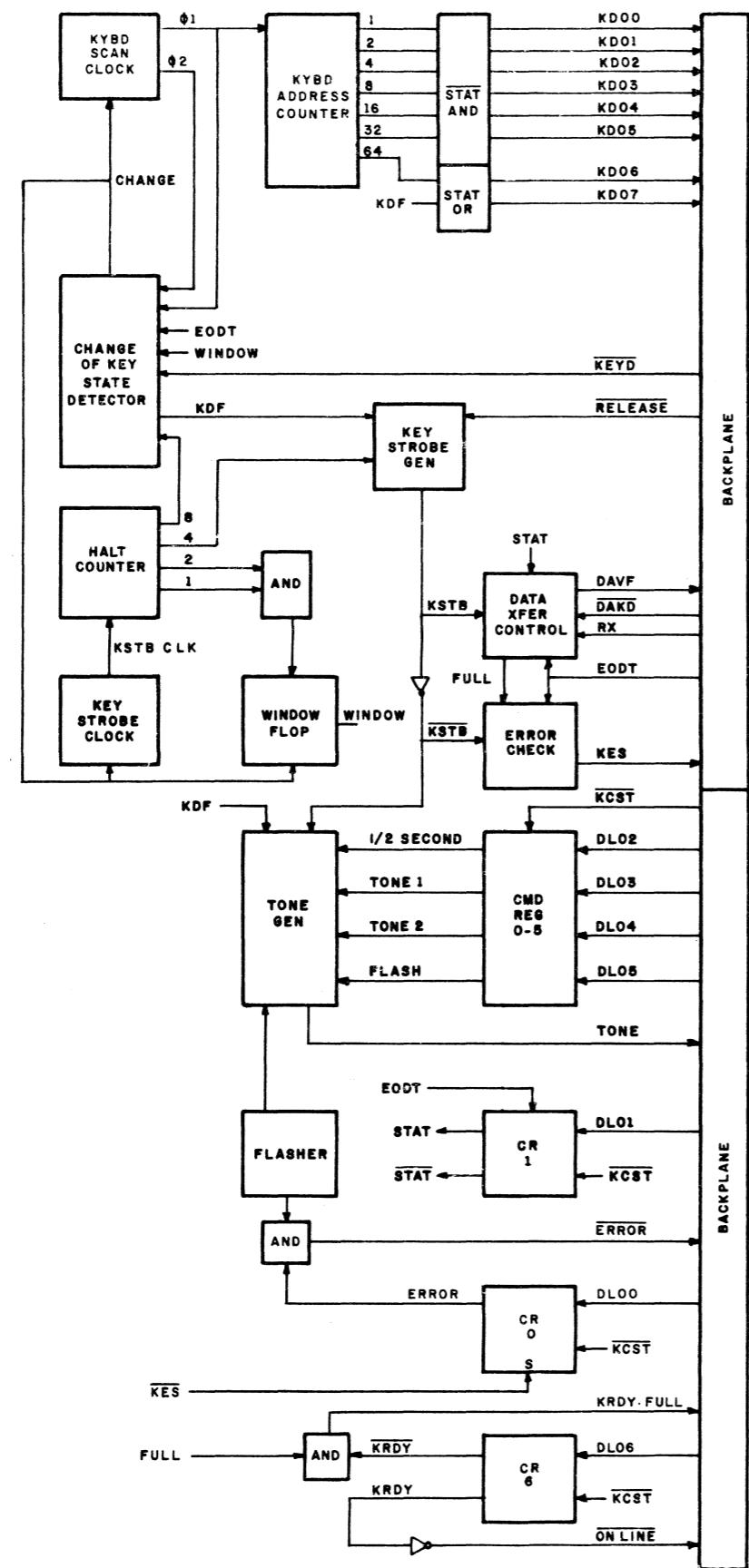

| 2A-20   | 2A-15       | Keyboard Block Diagram                         |

| 2A-20   | 2A-16       | Status Word                                    |

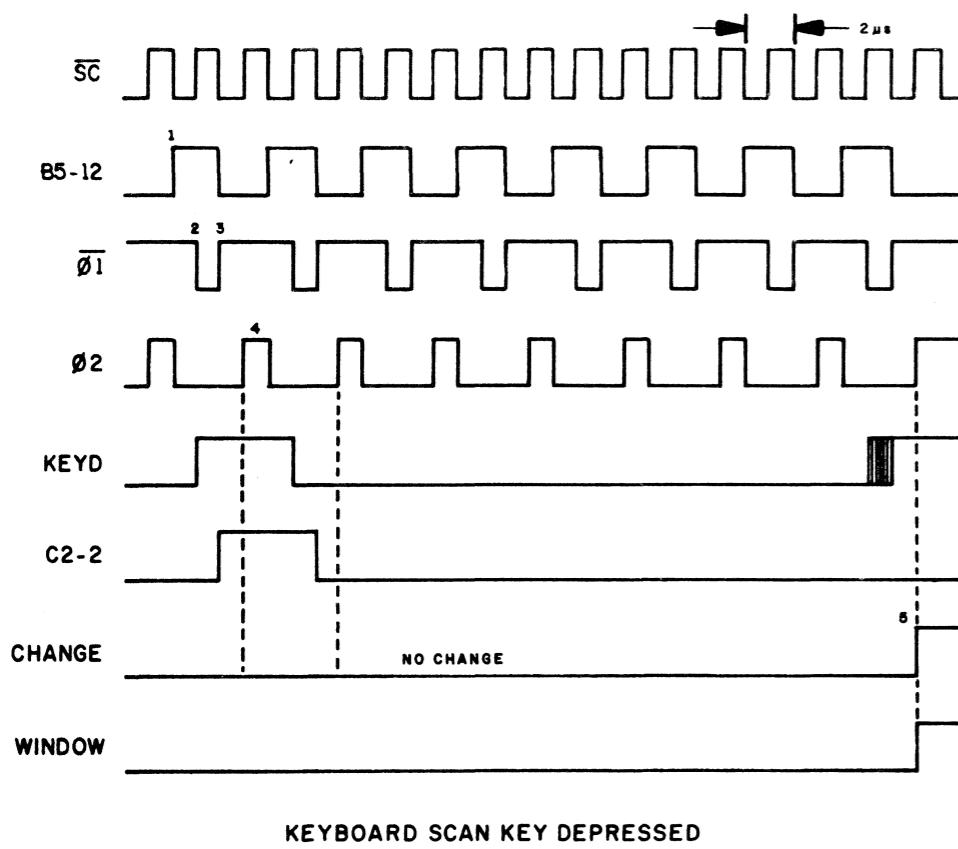

| 2A-22   | 2A-17       | Scan Clock Timing                              |

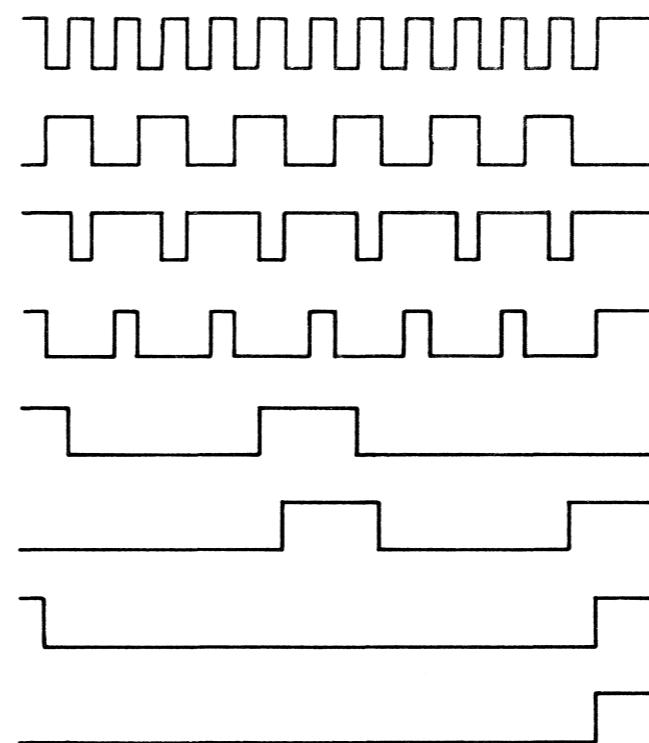

| 2A-24   | 2A-18       | Depress Halt Timing                            |

| 2A-24   | 2A-19       | Release Halt Timing                            |

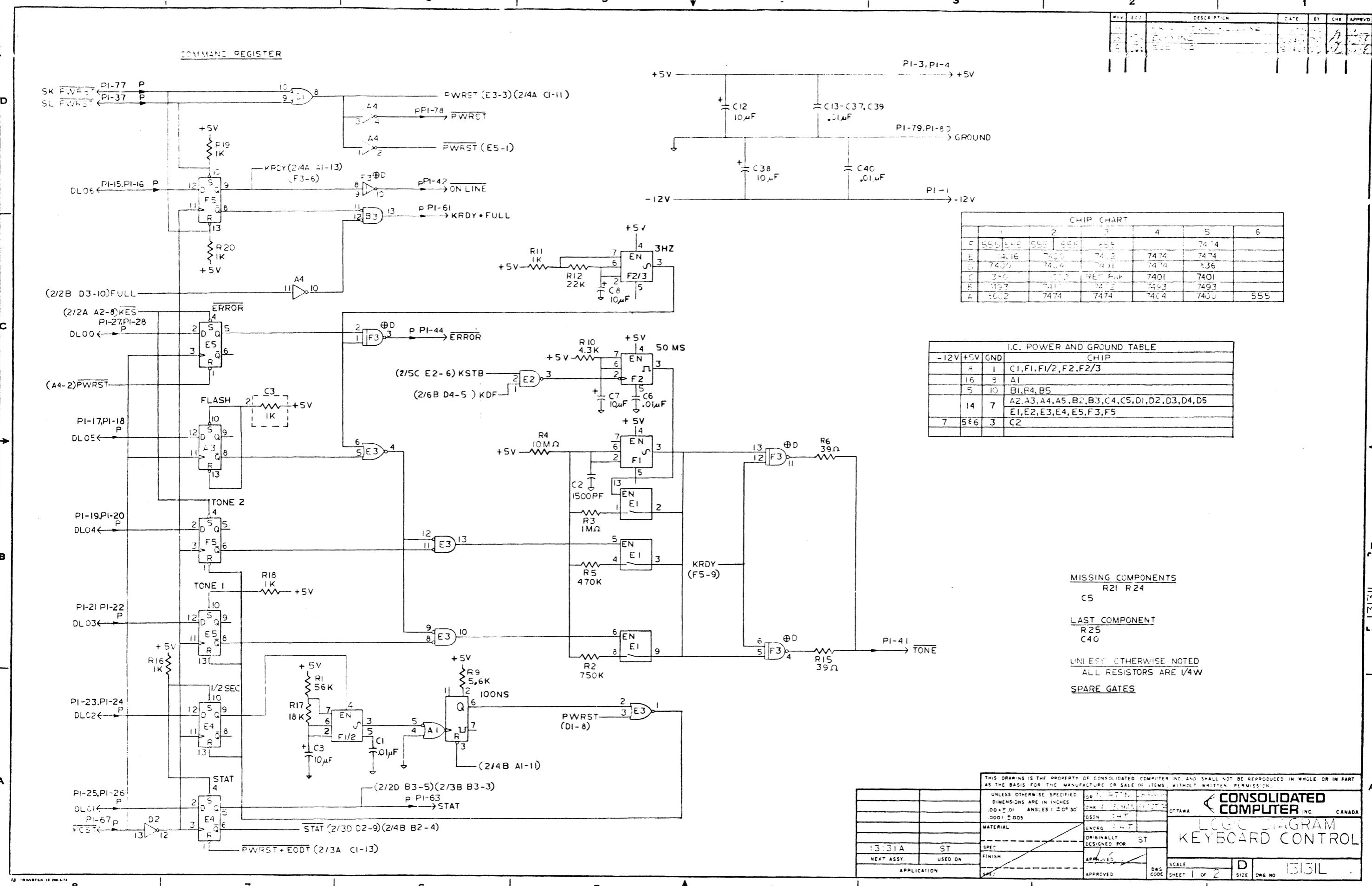

| (2A-26) | D13131 L    | Keyboard Control PCB Logic<br>(sheets 1 and 2) |

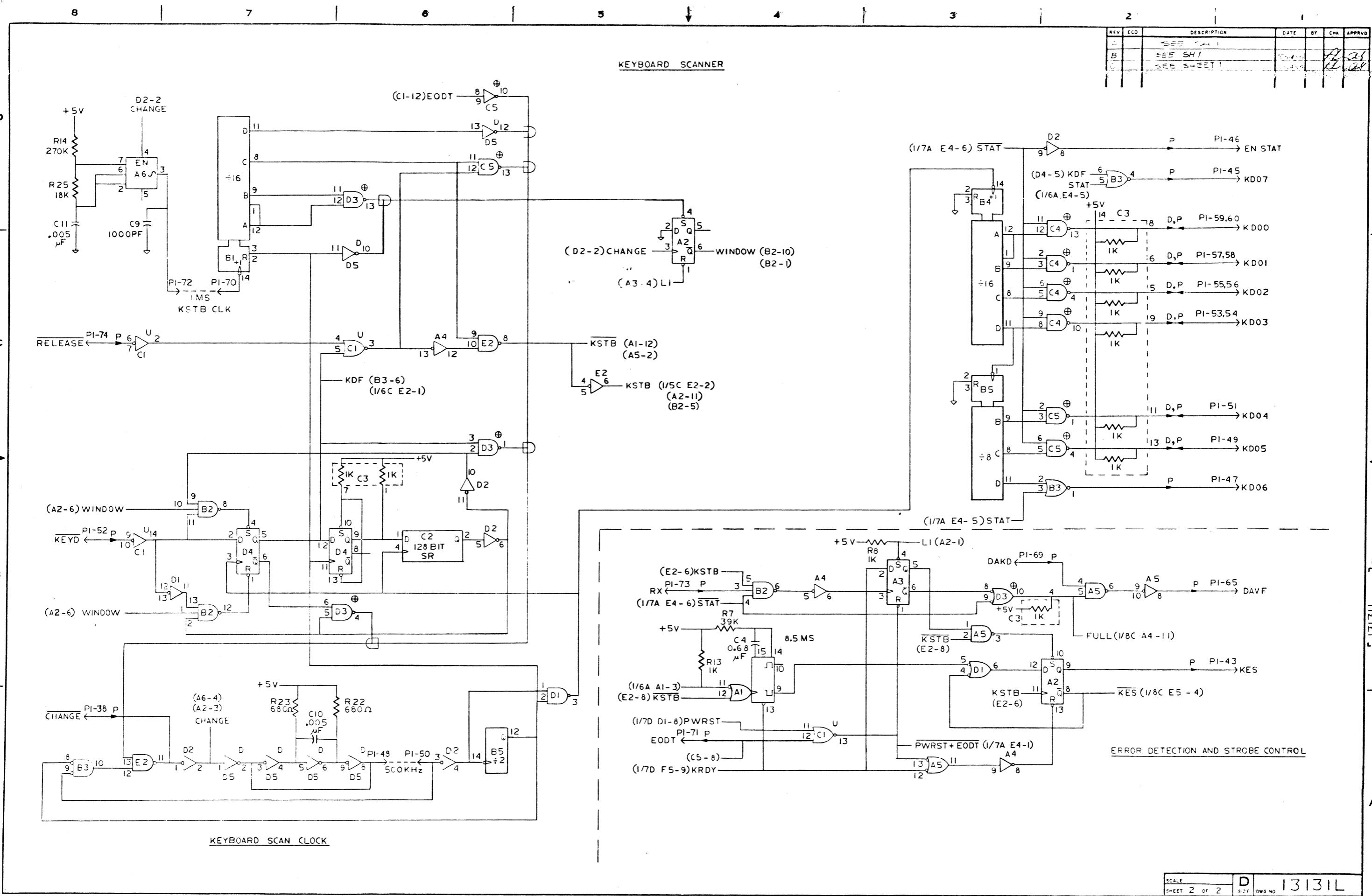

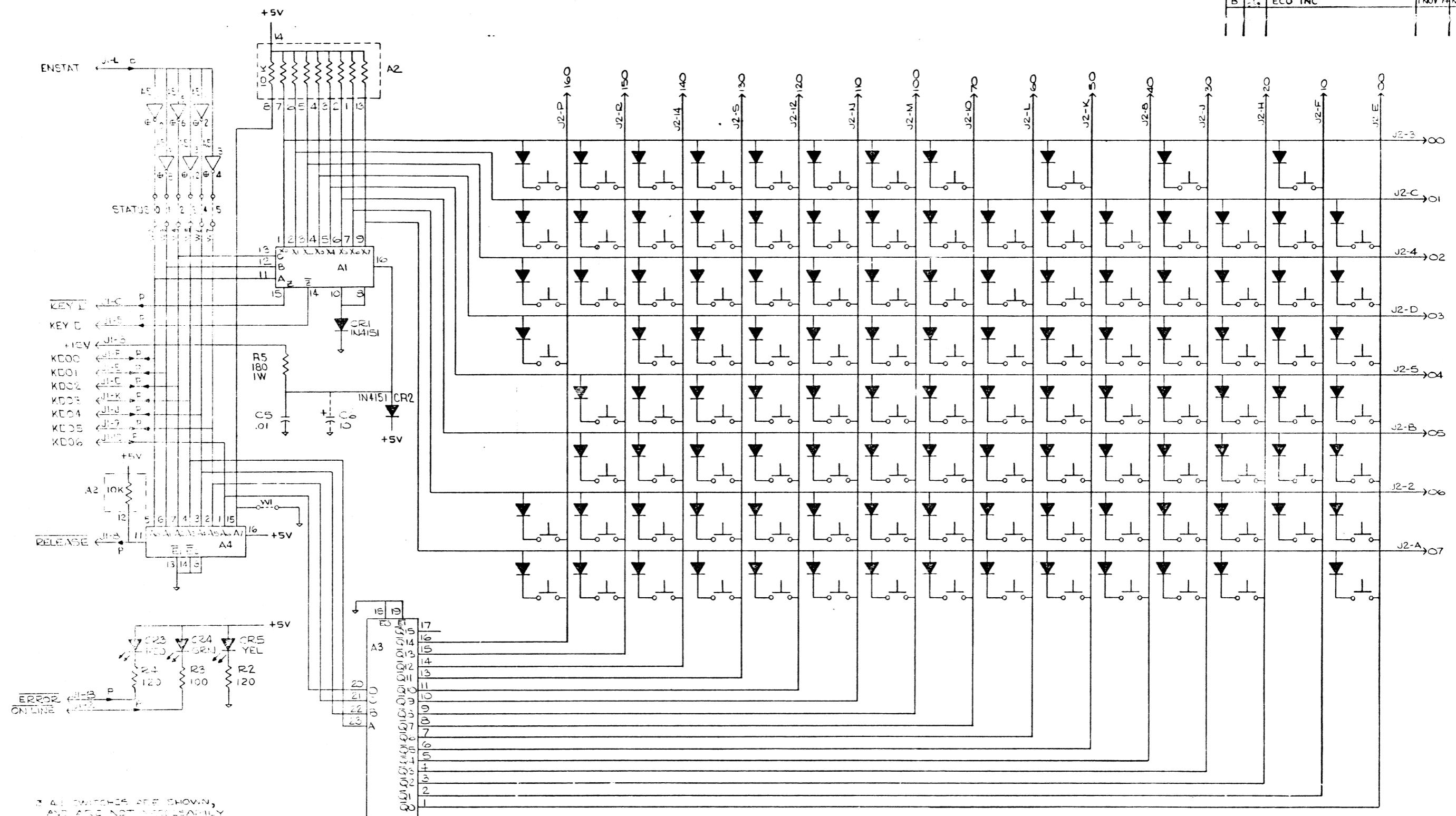

| (2A-28) | D13132 L    | Keyboard PCB Logic (sheet 1)                   |

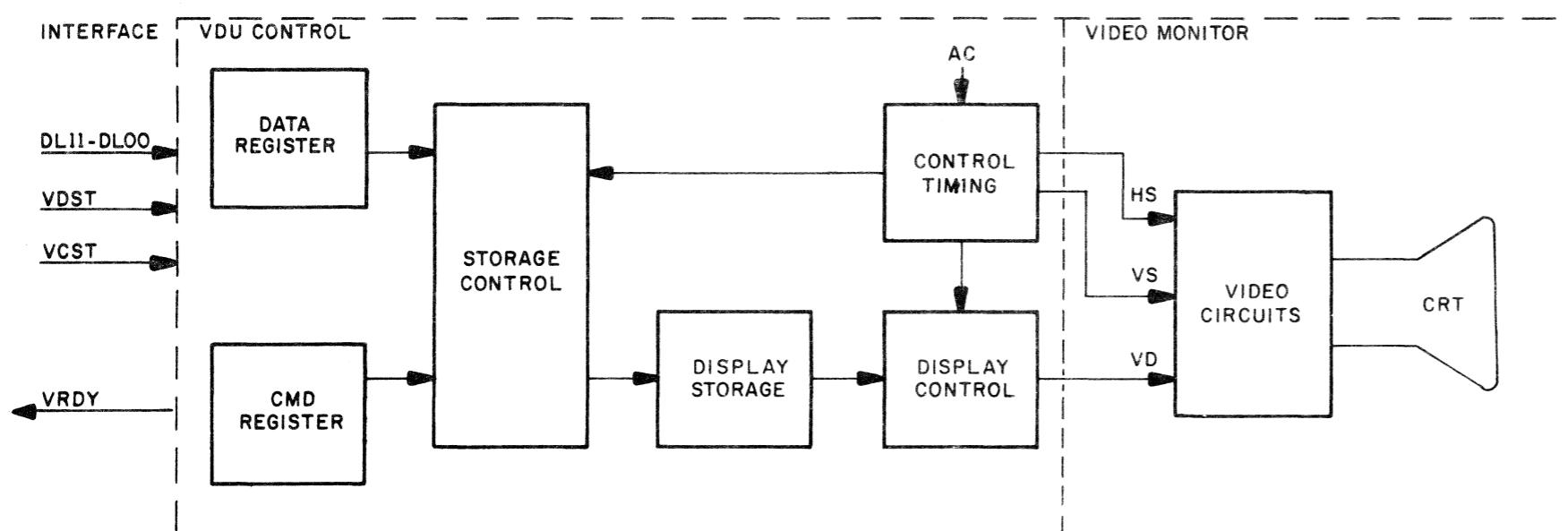

| 2A-29   | 2A-20       | VDU Block Diagram                              |

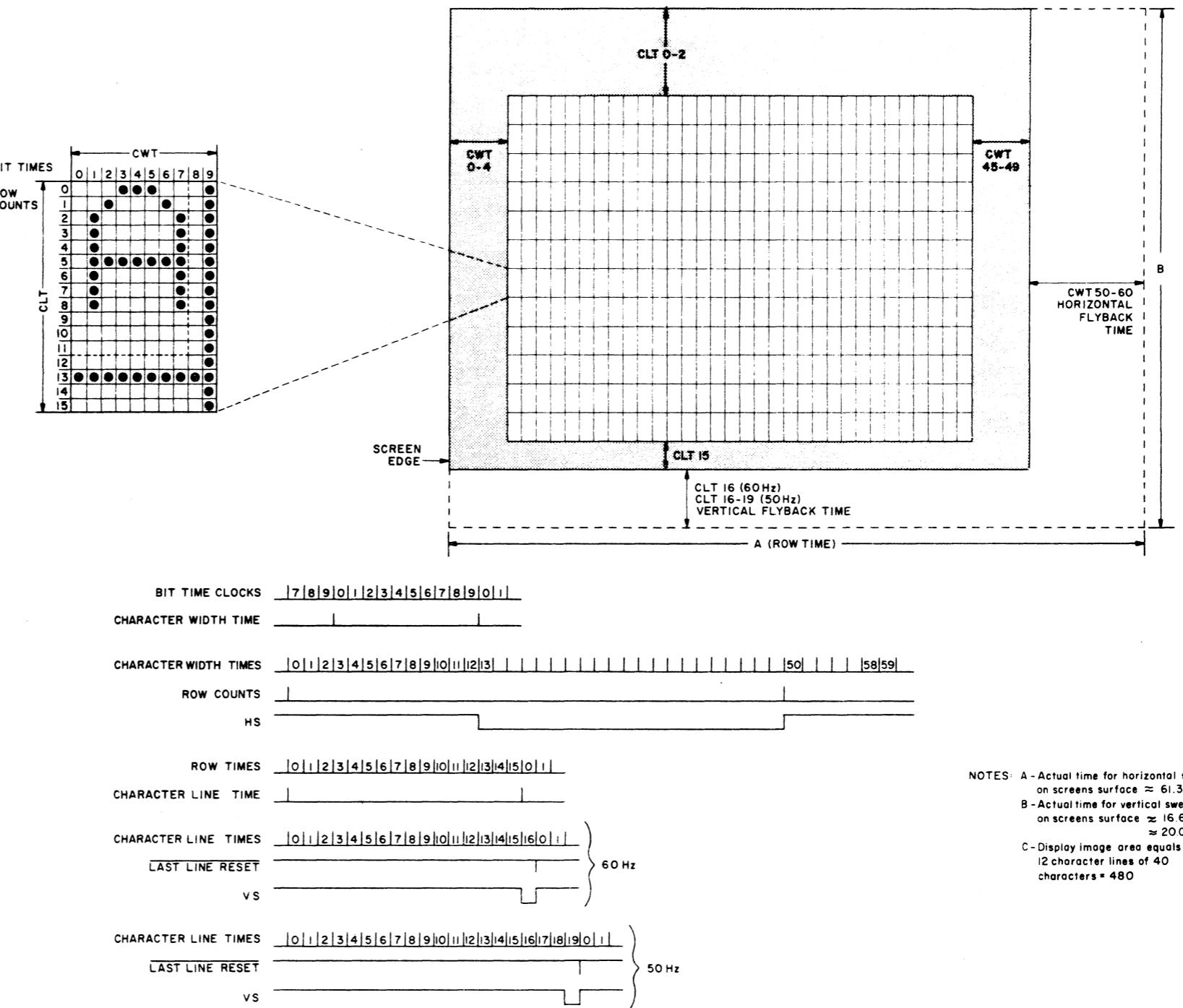

| 2A-30   | 2A-21       | Main Timing and Display Format                 |

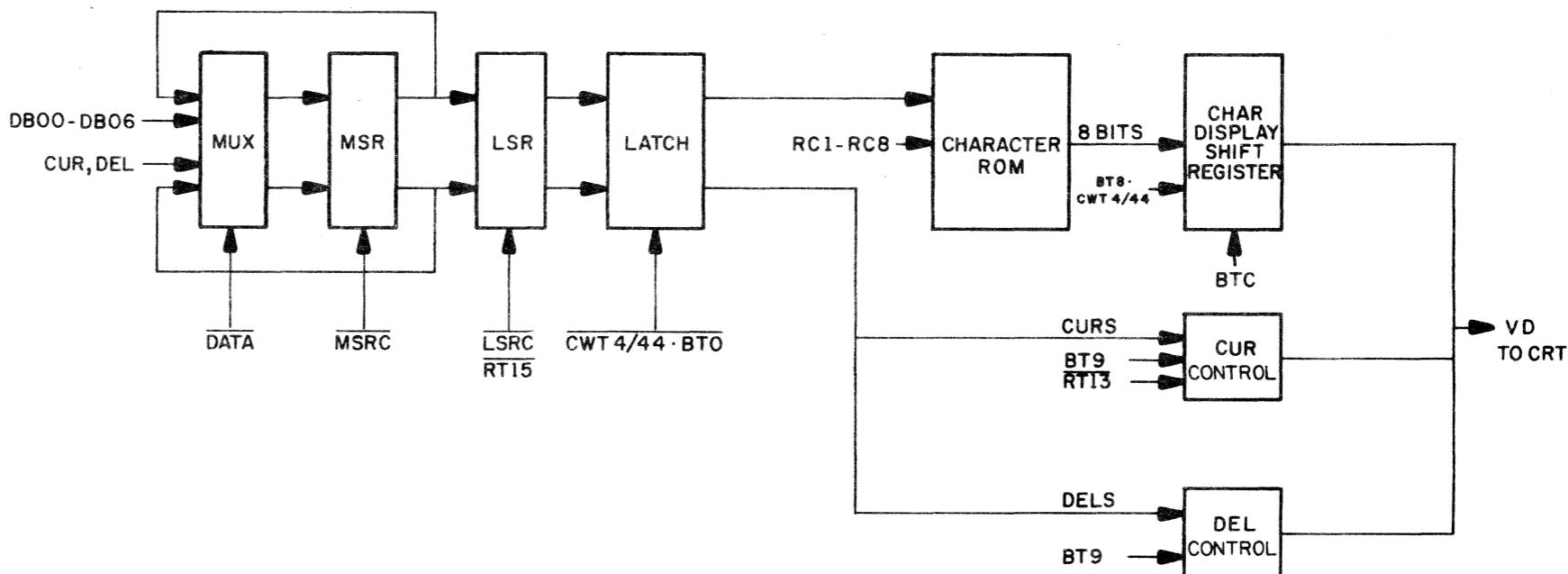

| 2A-31   | 2A-22       | Video Drive Control                            |

## ILLUSTRATIONS

| PAGE    |              |                                          |

|---------|--------------|------------------------------------------|

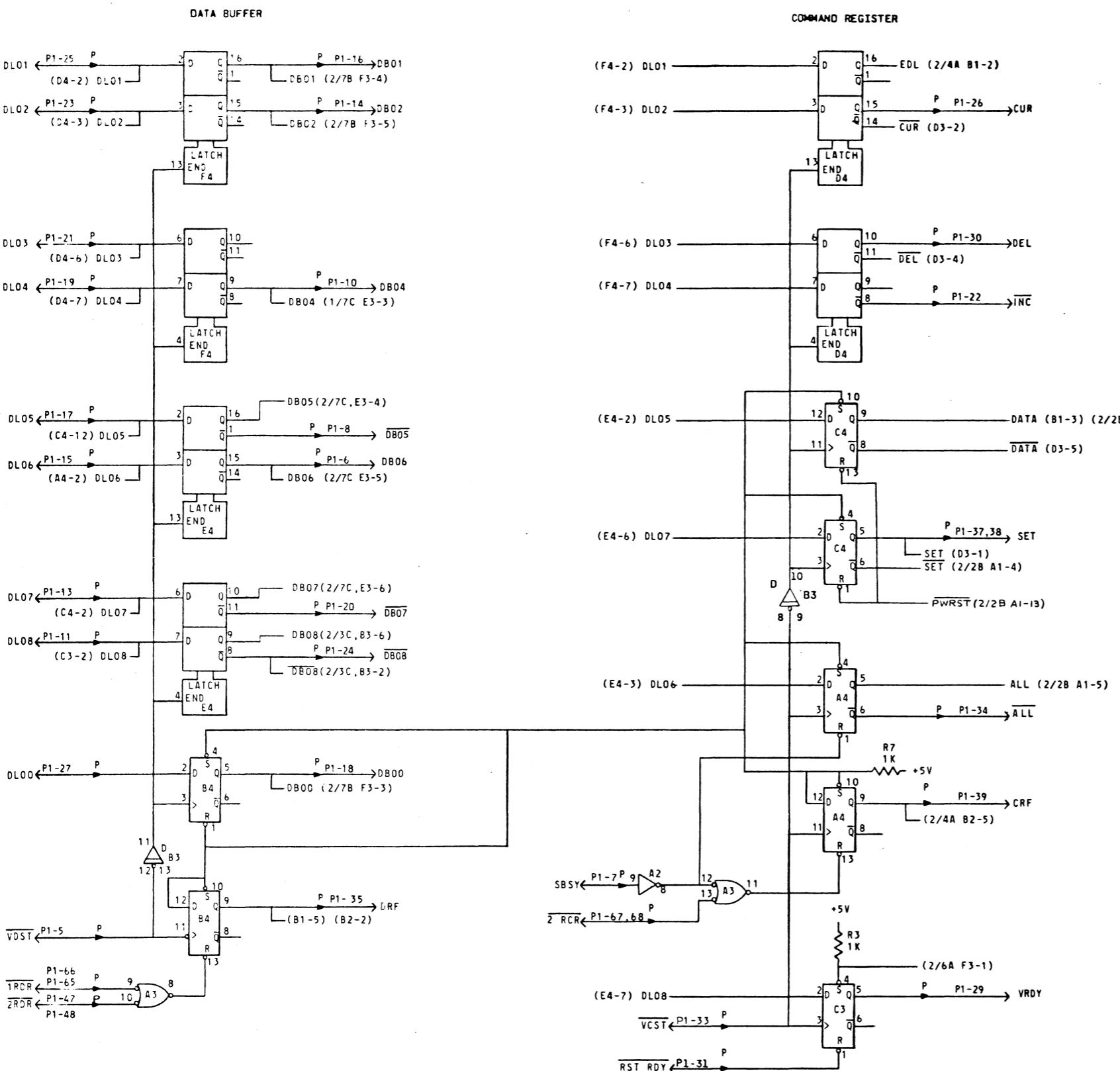

| 2A-36   | Figure 2A-23 | VDU Command Register Logic               |

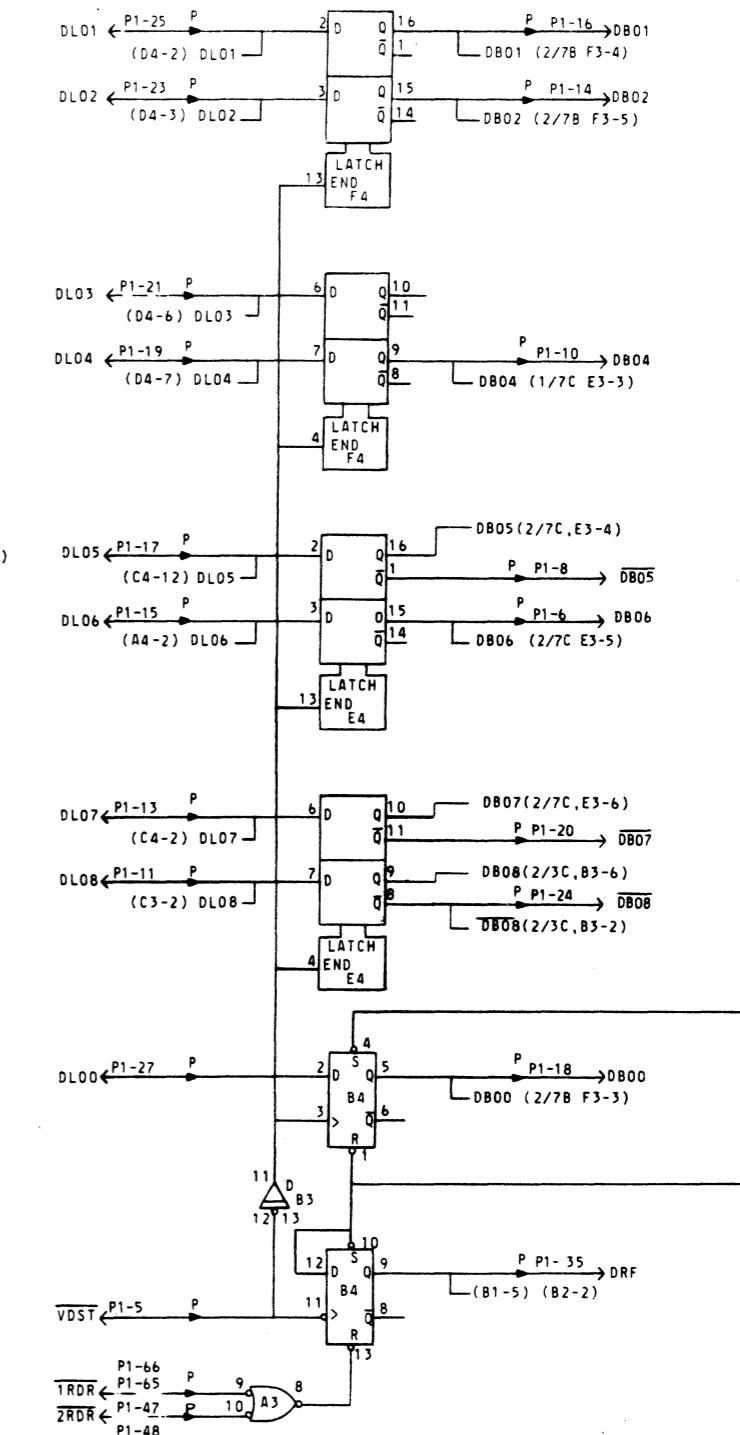

| 2A-36   | 2A-24        | Data Register Logic                      |

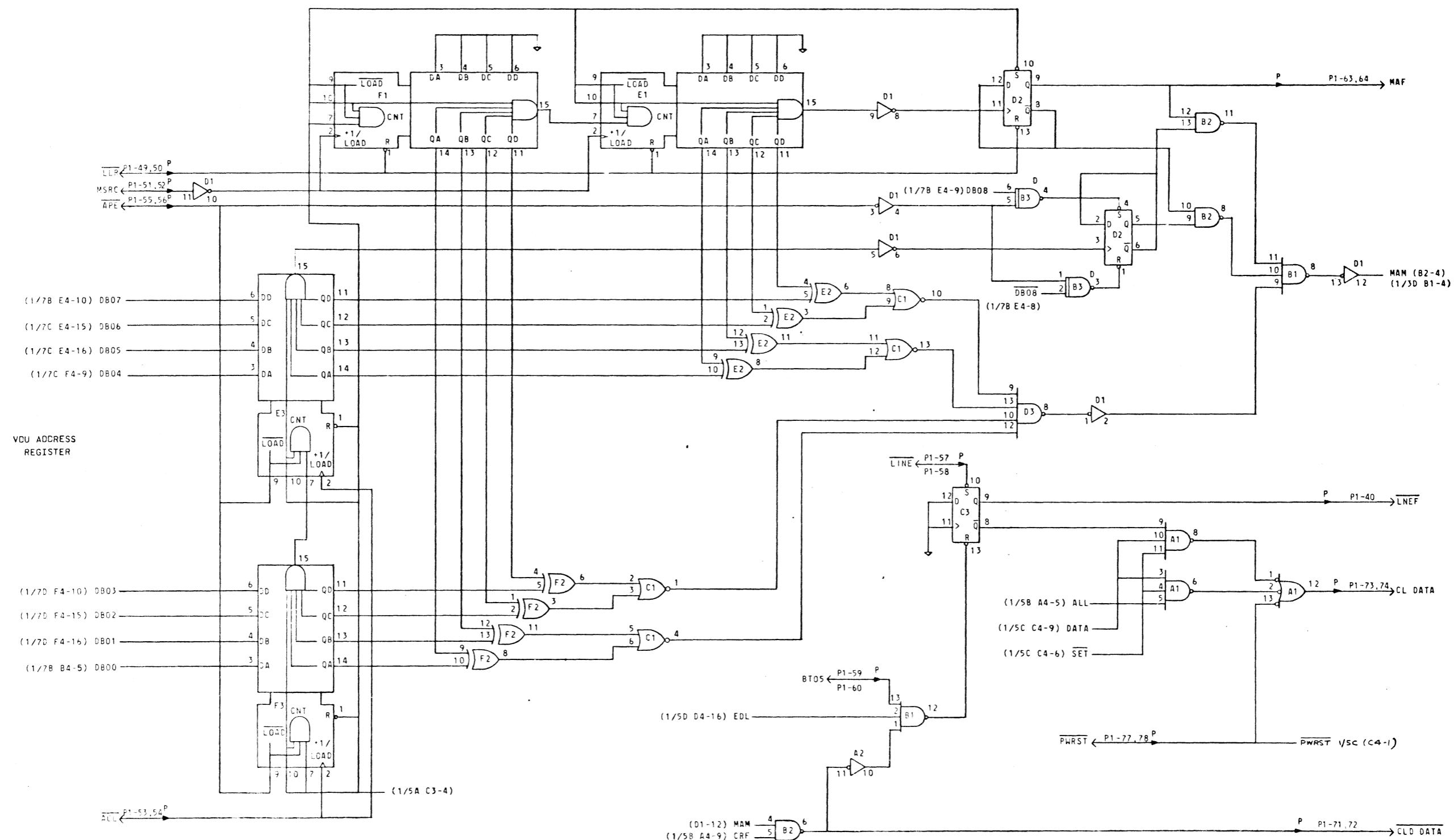

| 2A-37   | 2A-25        | Address Register Logic                   |

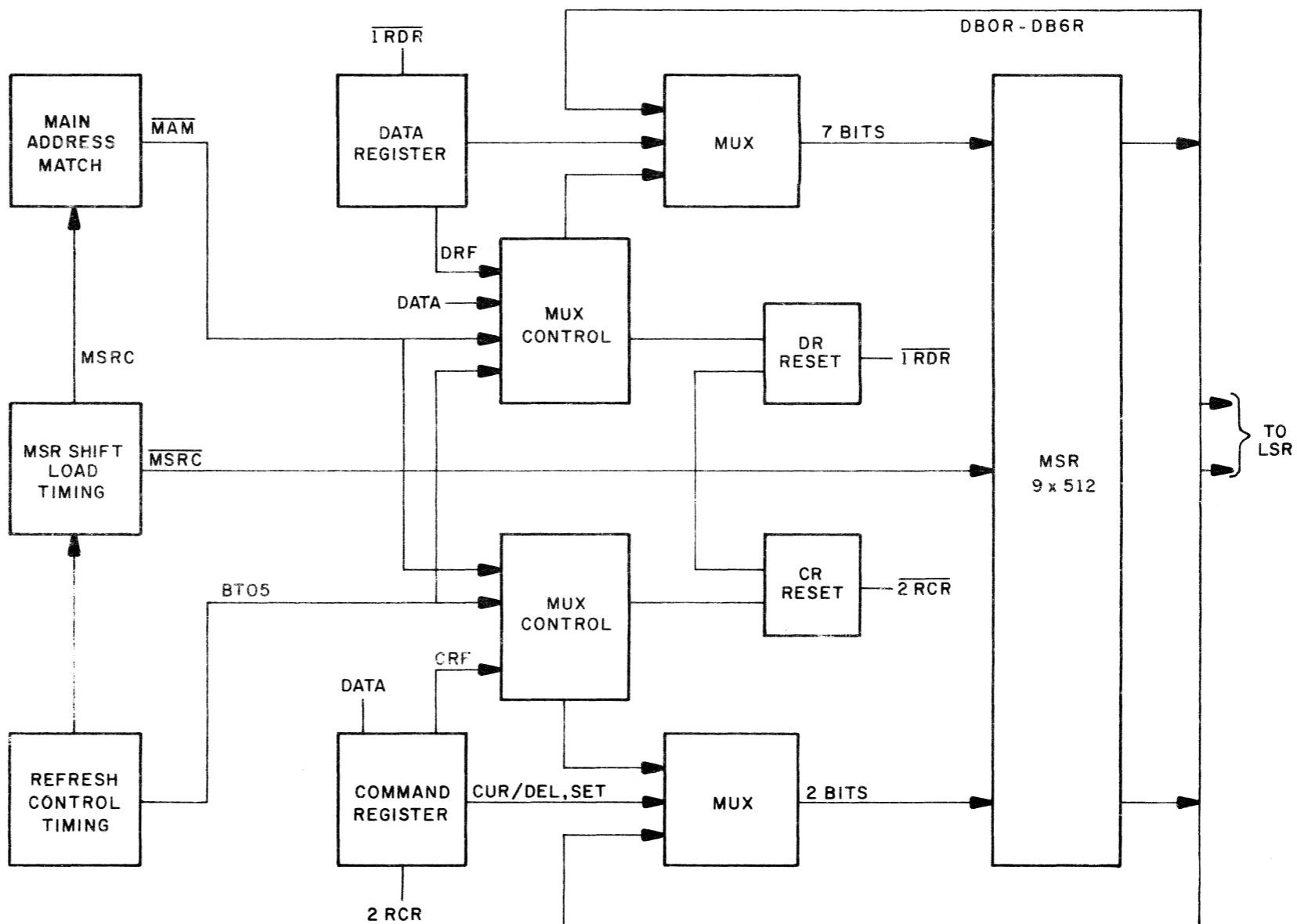

| 2A-38   | 2A-26        | MSR Control                              |

| (2A-41) | D13134 L     | VDU-1 PCB Logic (sheets 1 and 2)         |

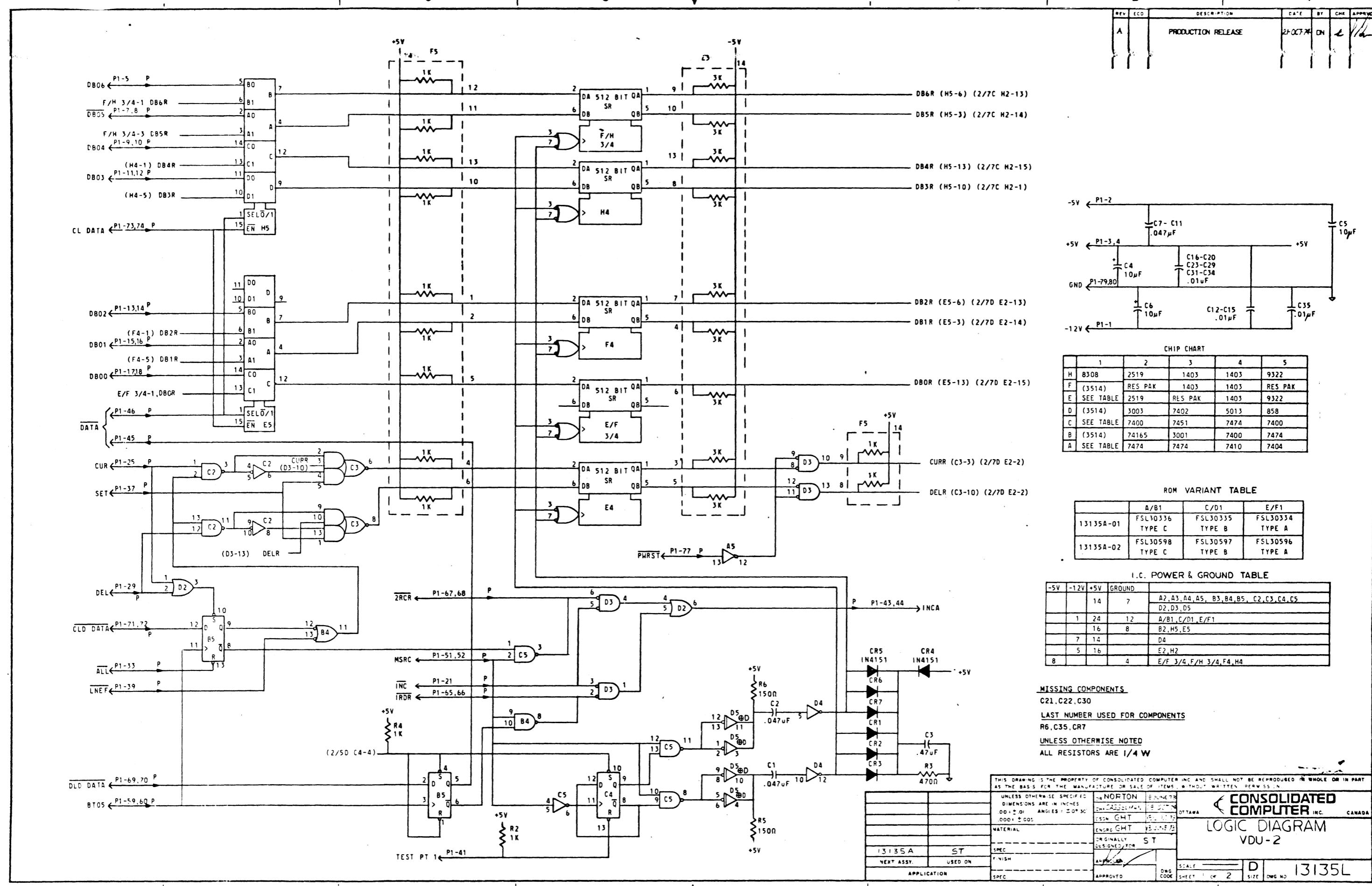

| (2A-43) | D13135 L     | VDU-2 PCB Logic (sheets 1 and 2)         |

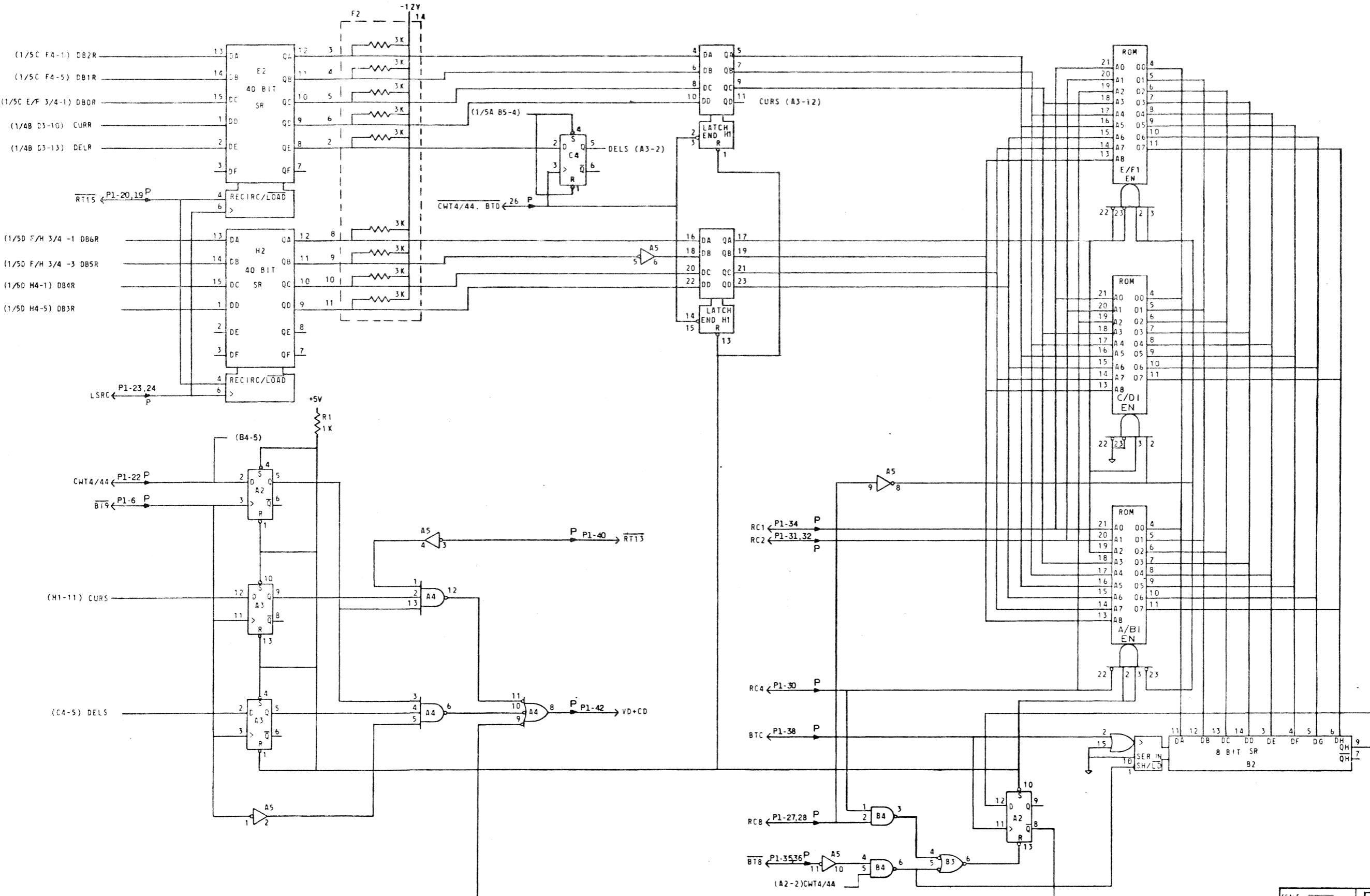

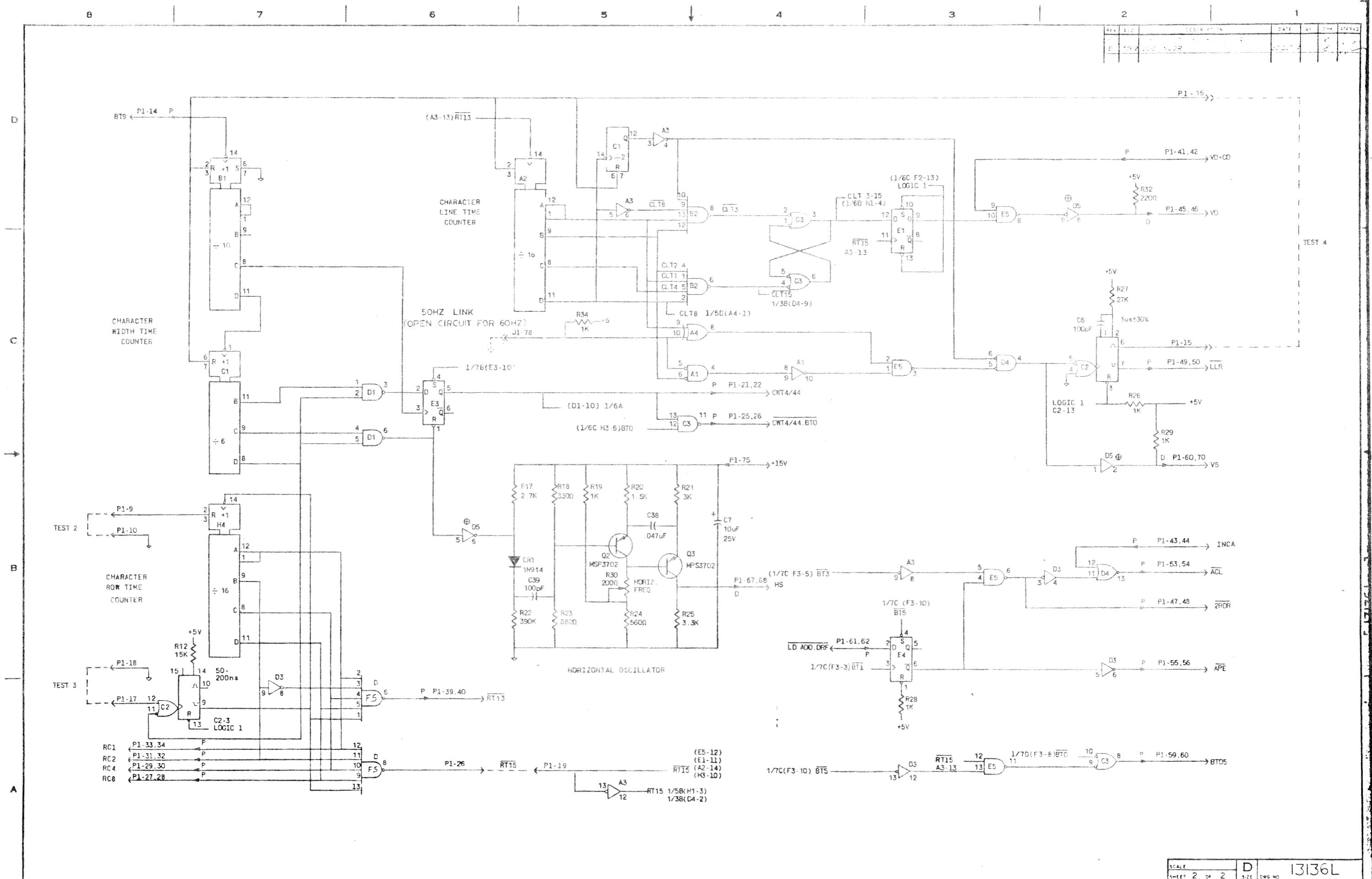

| (2A-45) | D13136 L     | VDU-3 PCB Logic (sheets 1 and 2)         |

| 2A-47   | 2A-27        | DT Internal Cabling                      |

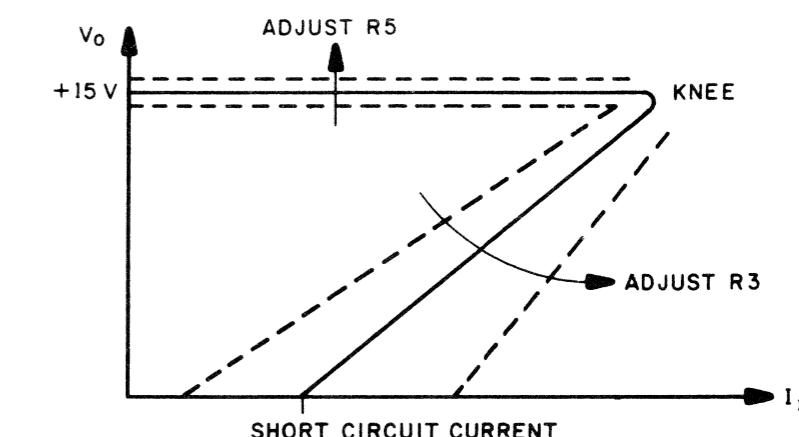

| 2A-48   | 2A-48        | +15 V Regulator Output Characteristics   |

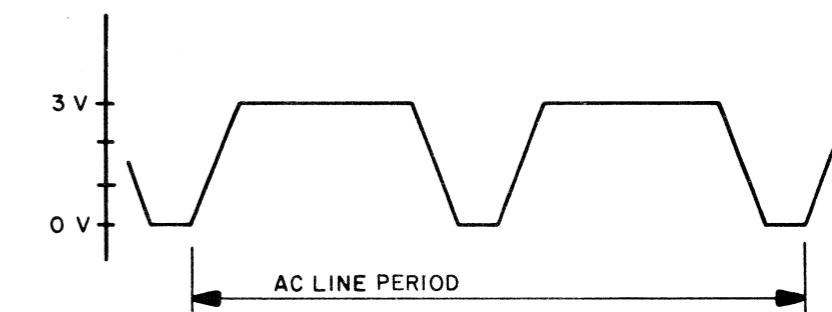

| 2A-48   | 2A-29        | AC Reference Waveform                    |

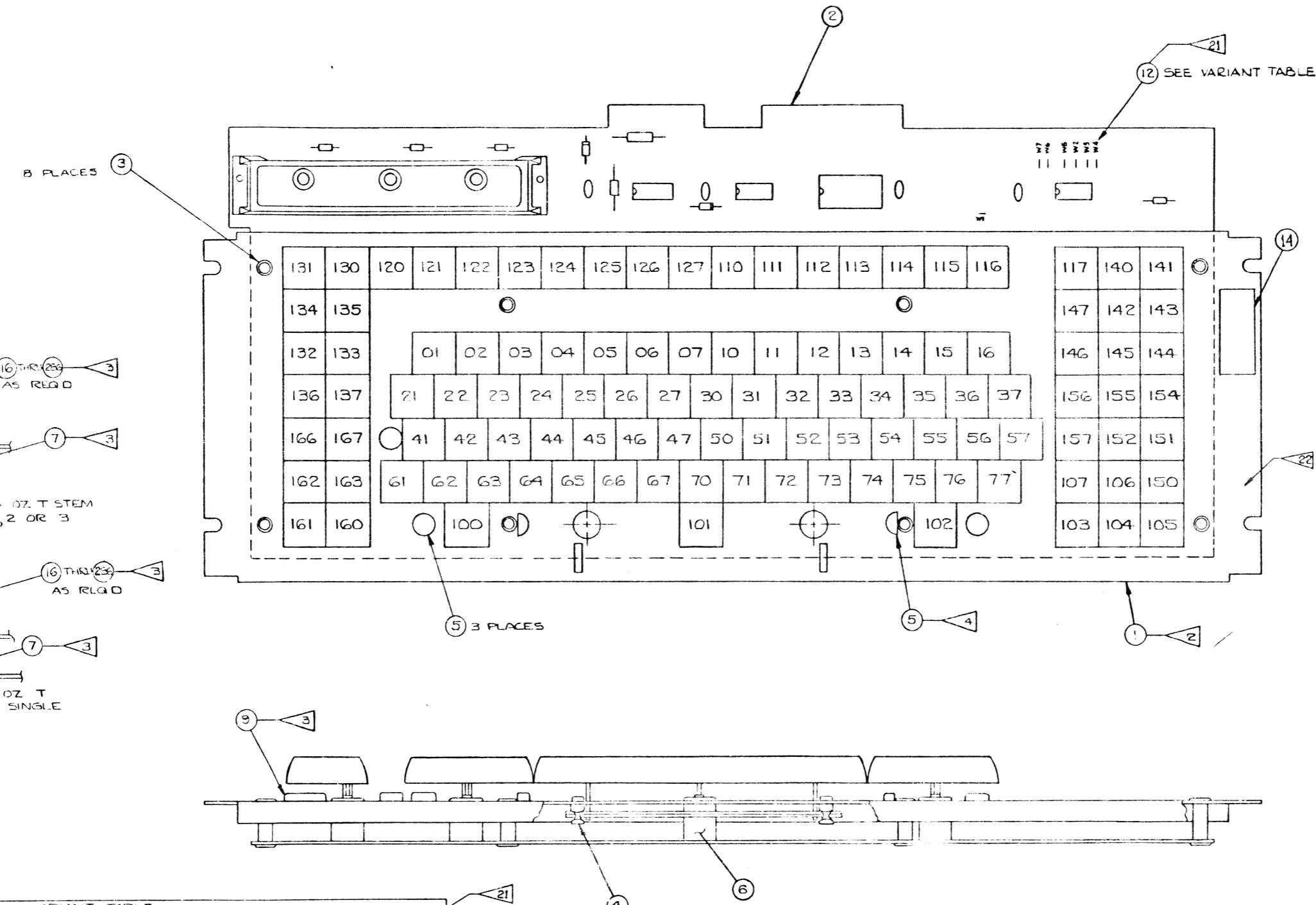

| 2A-50   | 2A-30        | Component Layout                         |

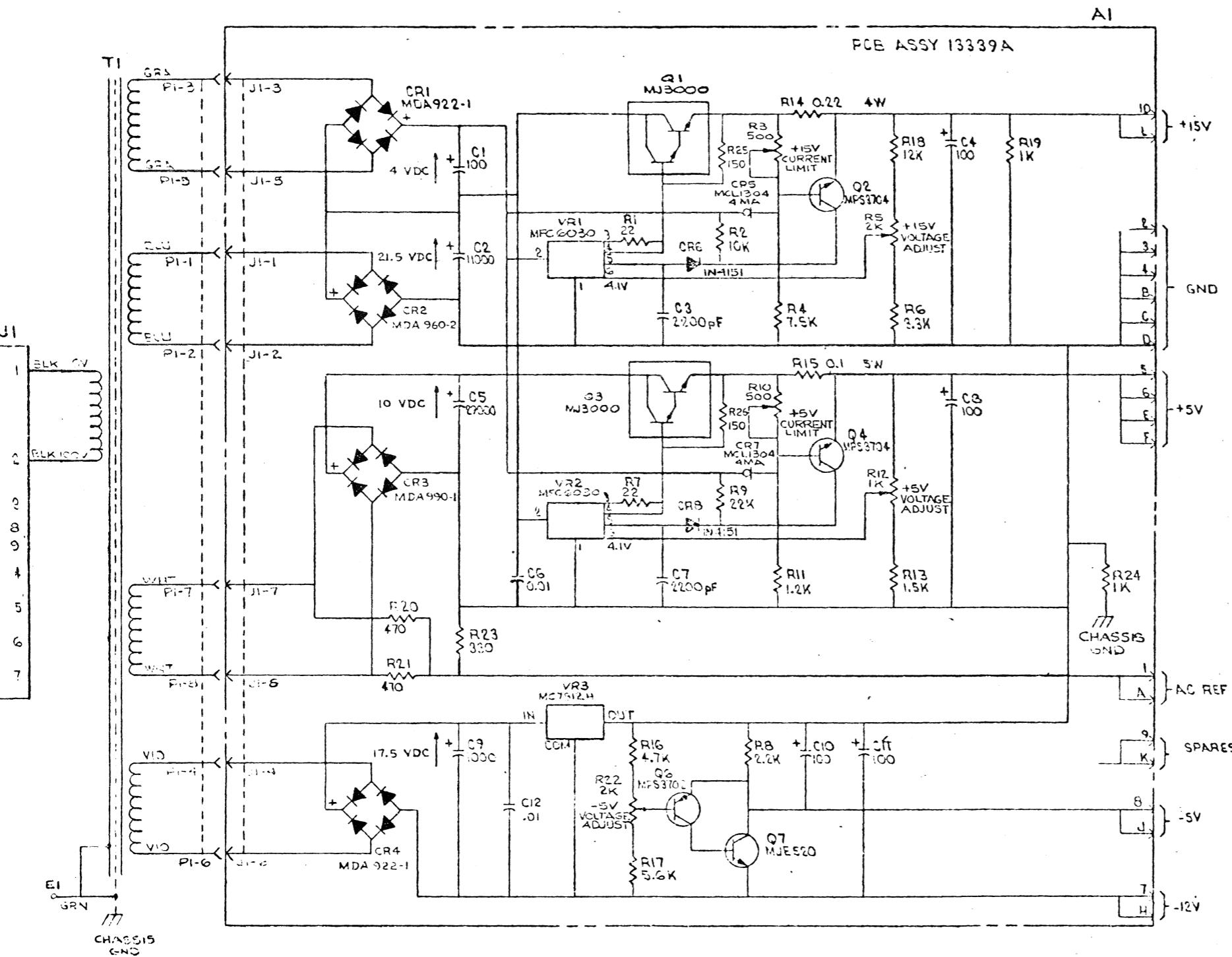

| (2A-51) | D13351 S/1   | Power Supply Schematic (115-250 V)       |

| (2A-52) | D13351 S/2   | Power Supply Schematic (100 V)           |

| (2A-54) | D13383 A     | Keyboard Assembly (sheets 1 and 4 to 11) |

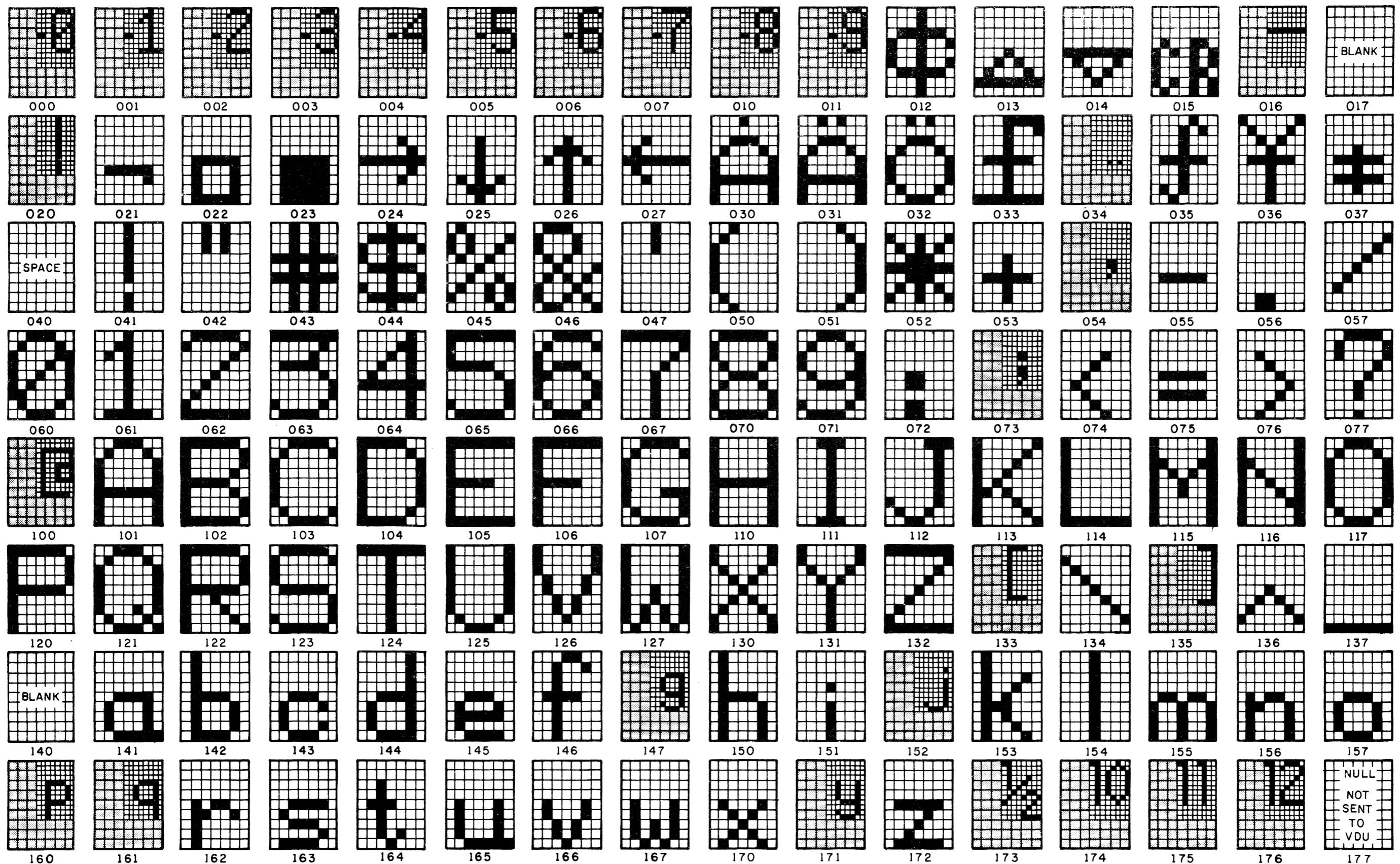

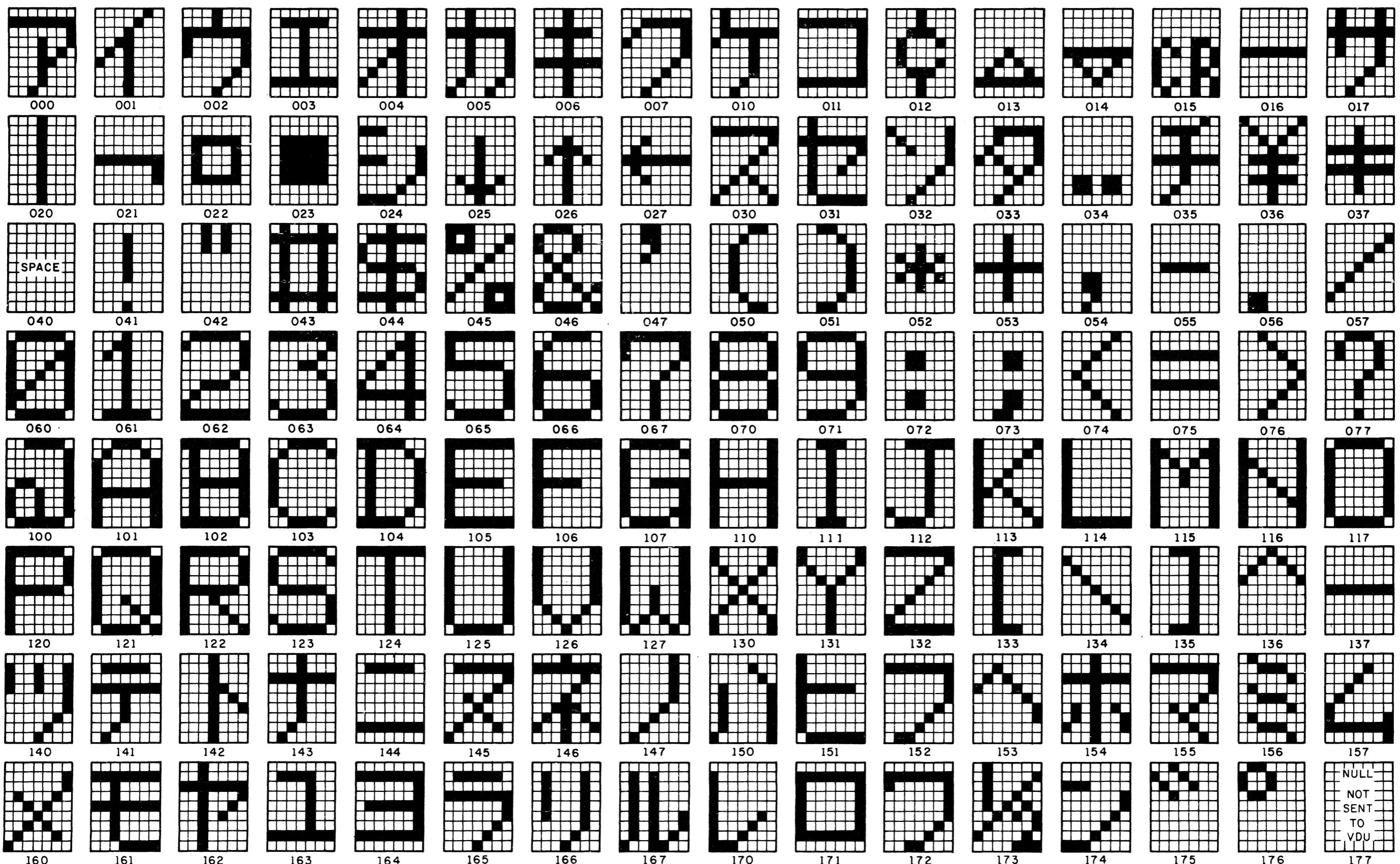

| 2A-64   |              | VDU Character Formats                    |

## TABLES

| PAGE  |            |                           |

|-------|------------|---------------------------|

| 2A-6  | Table 2A-1 | 12 BD SI Cable            |

| 2A-19 | 2A-2       | Keyboard Command Register |

| 2A-32 | 2A-3       | Display Pattern Control   |

| 2A-33 | 2A-4       | VDU Command Register      |

| 2A-34 | 2A-5       | VDU Commands              |

| 2A-49 | 2A-6       | DC Output Characters      |

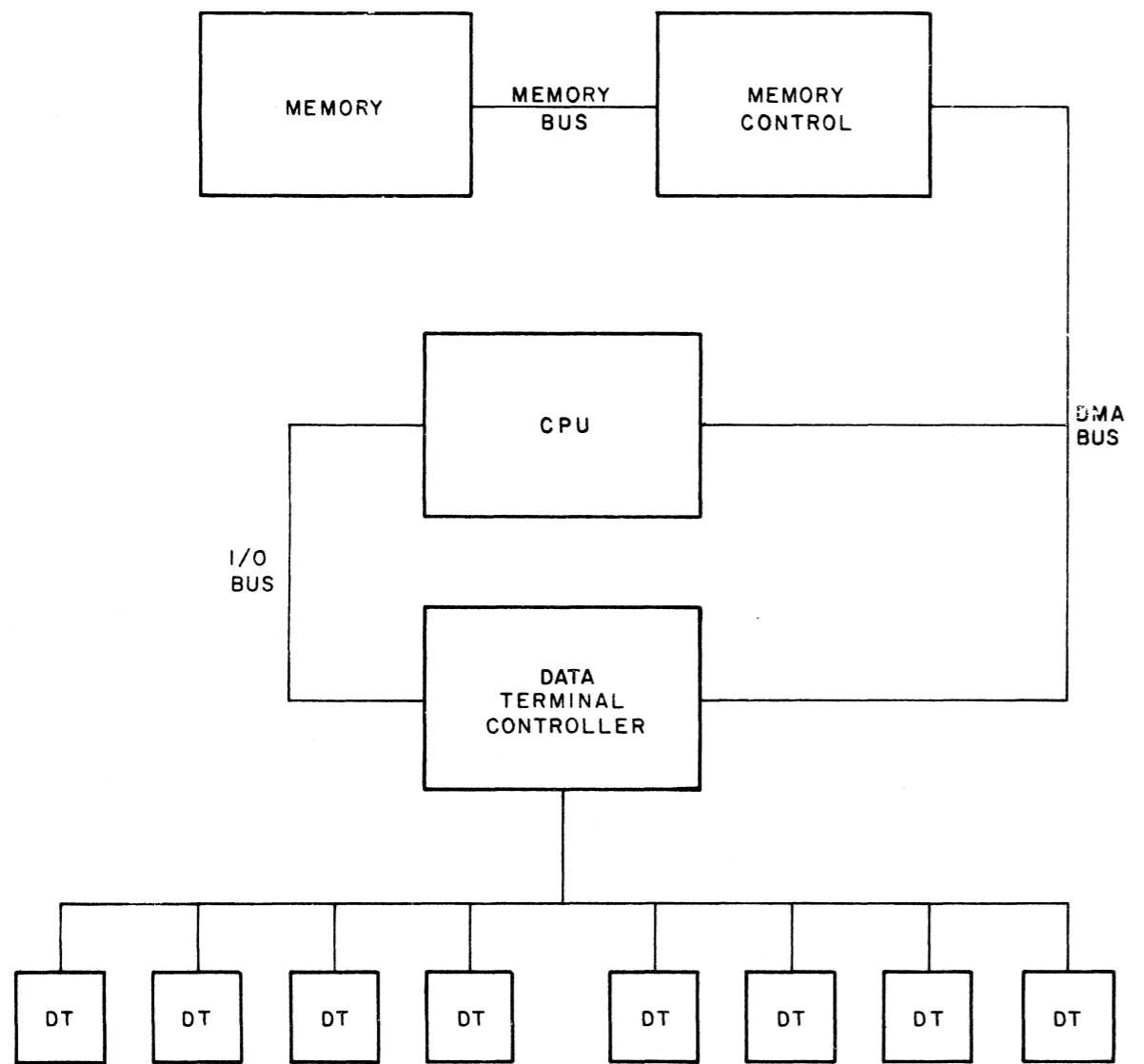

NOTE: ONE DATA TERMINAL CONTROL PCB

CONTROLS EIGHT DT (MAXIMUM OF

FOUR CONTROL PCB)

FIGURE 2A-1

KE 50 DT CONFIGURATION

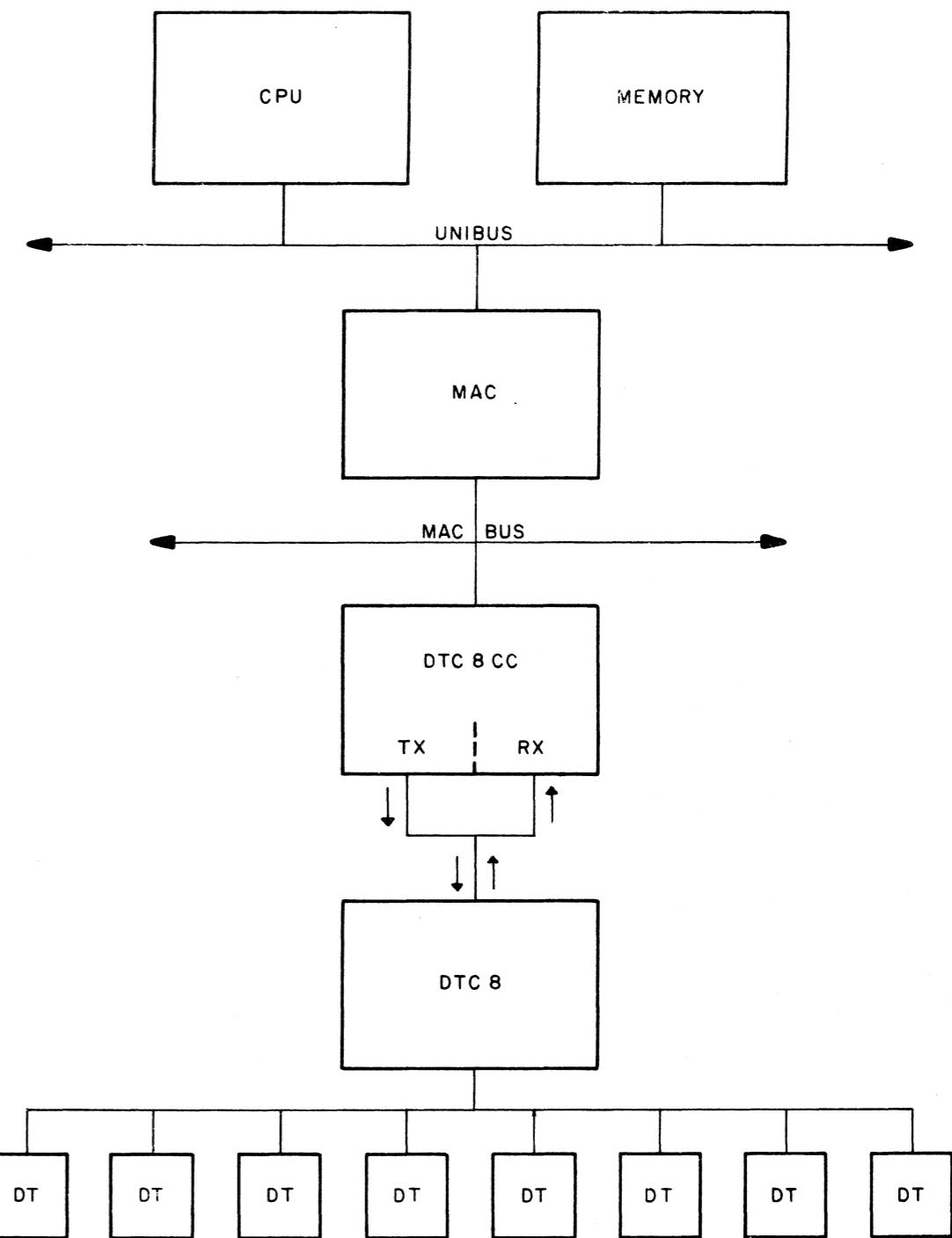

FIGURE 2A-2

KE 1000 DT CONFIGURATION

## INTRODUCTION

The Data Terminal is used in both the KEY-EDIT 50 and the KEY-EDIT 1000 systems. For the purpose of this document, the following abbreviations apply:

- KEY-EDIT 50 is designated KE 50

- KEY-EDIT 1000 is designated KE 1000.

Each system uses a different interface for the terminal: the KE 50 uses a serial bit interface, and the KE 1000 uses a parallel bit interface. Thus, the data terminal has two interchangeable interface adapters.

This description assumes that the reader understands the respective interface of each system and the data terminal controller of that system. Figures 2A-1 and 2A-2 illustrate the relative position of the data terminal in the systems.

## PURPOSE

The data terminal is the data entry and display station of the KEY-EDIT system, and comprises two independent devices: a Keyboard, and a Video Display Unit (VDU).

The Keyboard transfers data to memory via a 12 BD SI line, a DTC 8, a DTC 8 CC, and a MAC (KE 1000); or via a serial line and a Terminal Controller (KE 50). The VDU displays data messages sent to the data terminal by the software. These messages are explained in the KE 1000 Operator's Procedures Manual (1143) and the KE 50 Operator's Procedures Manual (5143).

## CAPABILITIES

The data terminal is a self-contained unit that comprises a keyboard, a VDU, an interface, and a power supply. The capabilities of the data terminal are described in relation to these components.

### KEYBOARD

The keyboard can have a maximum of 112 keys. The operation of the keyboard is controlled by its Command Register (CR). The software loads the Keyboard CR with a command word, causing the keyboard to perform any of the following operations:

- send status

- send data

- indicate operational status by tones and indicator lamps

- perform error checking.

When commanded by the program the keyboard sends a status word defining the keyboard address ( $7_8$ ), and the keyboard style (i.e., 029, or teletype).

Once placed on-line by a command word, the keyboard transfers a word when a key is depressed, or when a key that has been assigned a release code is released. One bit of the word distinguishes between a word generated by key depression and a word generated by key release. In either case, the word contains the address of the key that was depressed or released.

The software uses the key address to find a character in a look-up table in memory. The base address of the table is determined by the keyboard status (i.e., the keyboard layout used). Thus, by generating a key address instead of character code, the keyboard can be adapted to any keyboard layout simply by altering the look-up table.

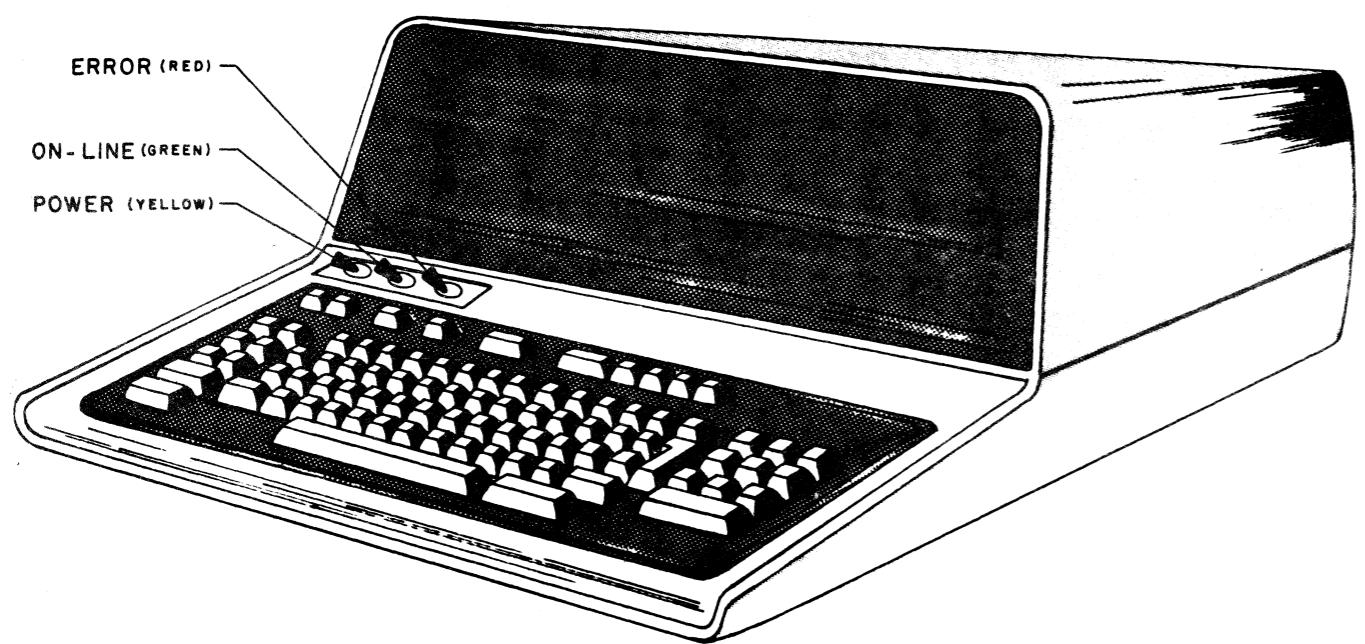

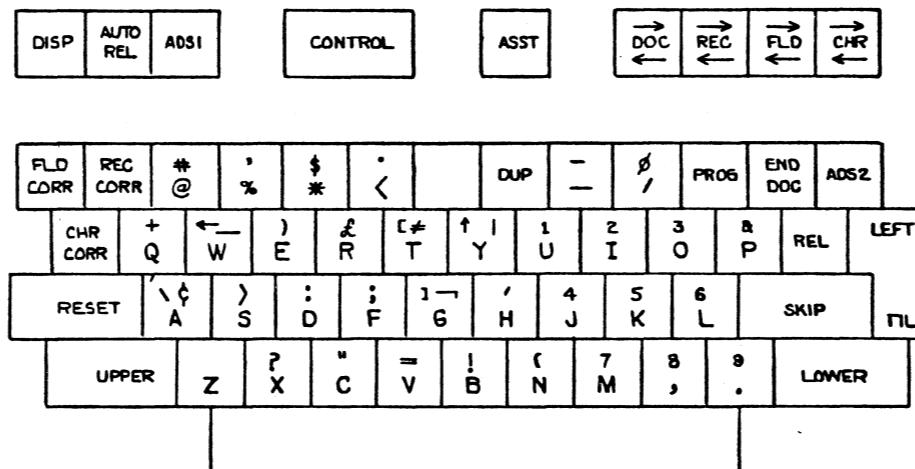

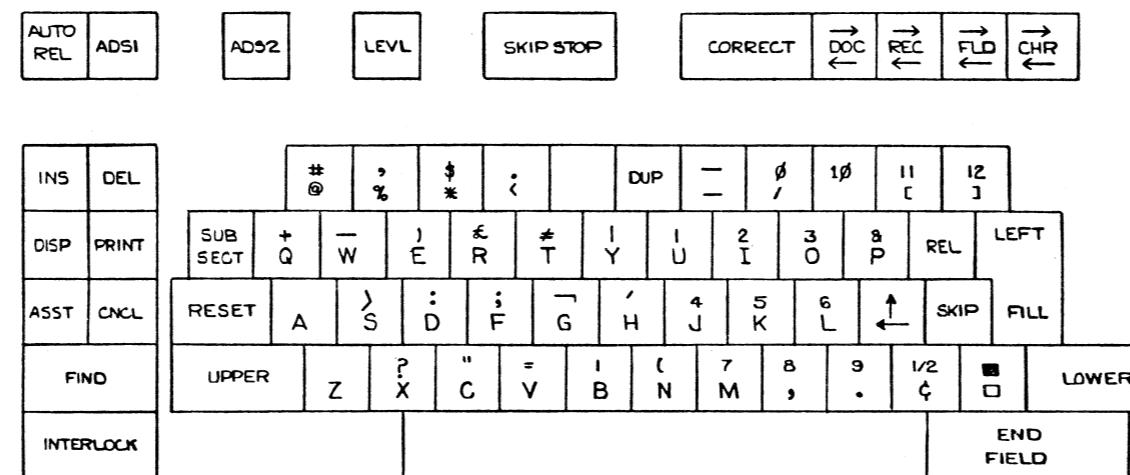

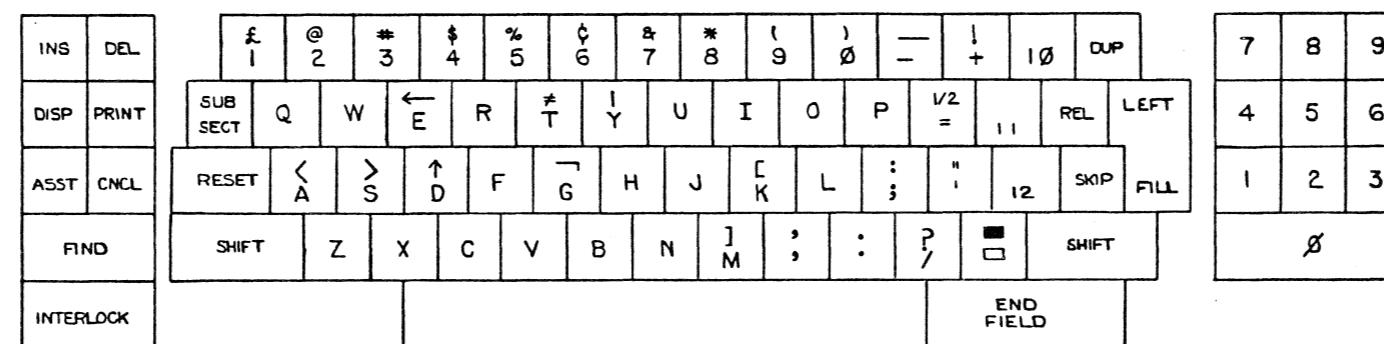

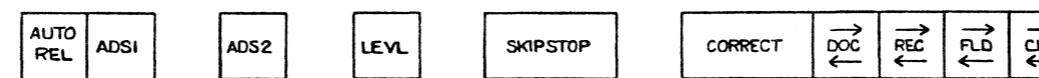

The keyboard indicates its operation status by using tones and indicator lamps. Figures 2A-3 and 2A-4 illustrate the data terminal indicators and controls.

When the terminal is powered up, the READY lamp (yellow) is lit. The ON-LINE lamp is lit when the keyboard is on-line. (When used with the KE 1000 system, the keyboard powers up off-line, and when used with the KE 50 system, the keyboard powers up on-line.) The ERROR lamp is lit when the keyboard detects an error or the software sets the error bit in the Command Register, and flashes to gain the operator's attention.

The keyboard can generate four tones. It generates a 50 ms, 430 Hz tone whenever a key is depressed. This tone is necessary because there is no mechanical noise (as in a keypunch) to inform the operator that she has operated a key.

The other three tones can be generated under control of the Command Register. The tones are:

- TONE 1 = 550 Hz

- TONE 2 = 830 Hz

- TONE 3 = 1320 Hz

FIGURE 2A-3

DATA TERMINAL INDICATORS

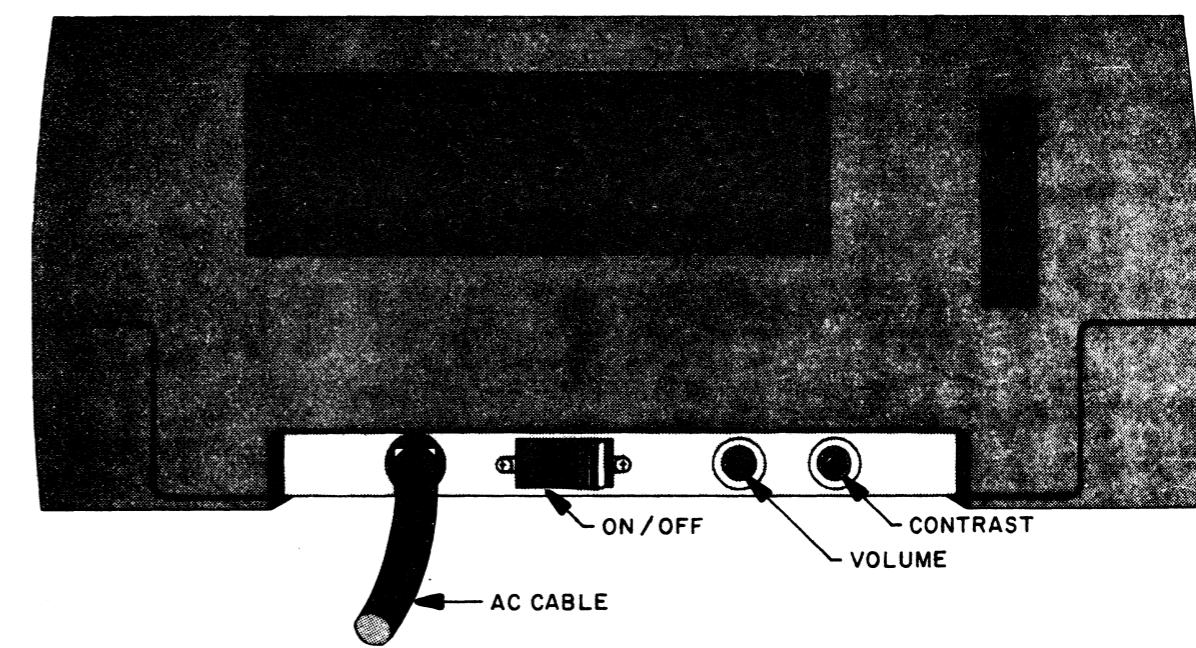

FIGURE 2A-4

DATA TERMINAL CONTROLS

## KEYBOARD

### COMMAND INITIATION

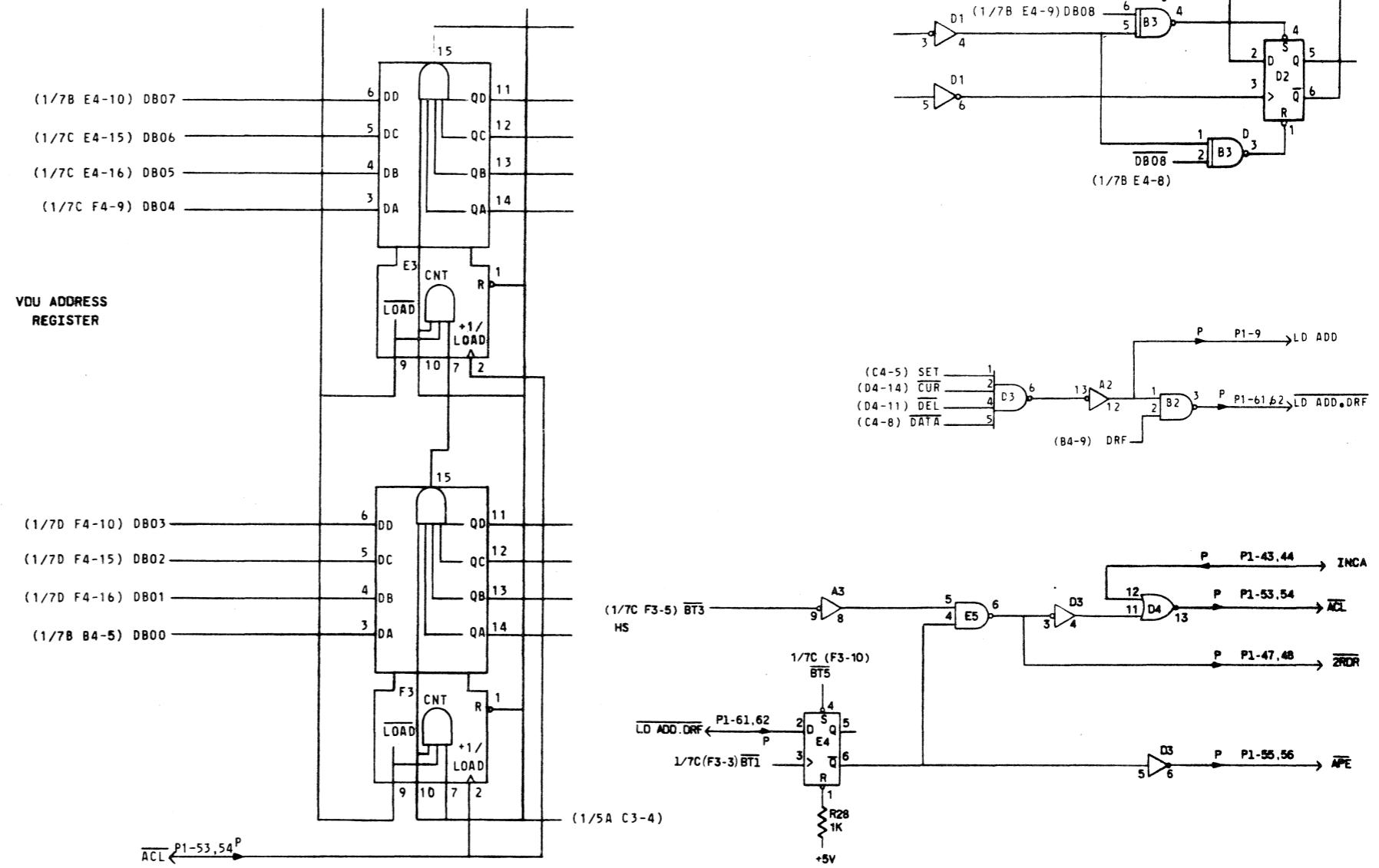

When a program sends a command word to the Keyboard, the Interface pcb (L/150 or 12 BD SI) generates KCST and gates the command bits onto DL00 - DL06. The Keyboard Command Register logic is illustrated in Figure 2A-15.

TABLE 2A-2

KEYBOARD COMMAND REGISTER

| BIT      | INPUT        | MNEMONIC             | FUNCTION                                                                                                                                                                             |

|----------|--------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06       | DL06         | KRDY                 | KEYBOARD READY is set when the keyboard is to be placed on-line, enabling the keyboard to transfer a data word when a key is depressed, or a status word when the status bit is set. |

| 05       | DL05         | FLASH                | This bit is set in conjunction with the tone bits to cause an interrupted tone.                                                                                                      |

| 04<br>03 | DL04<br>DL03 | TONE 2<br>TONE 1     | These bits control the tone generator, enabling it to generate one of three tones:<br><br>TONE 1 = 550 Hz<br>TONE 2 = 830 Hz<br>TONE 3 = 1320 Hz (TONE 1 + TONE 2).                  |

| 02       | DL02         | $\frac{1}{2}$ SECOND | This bit is set in conjunction with the tone bits to cause the tone to end after 0.5 second.                                                                                         |

| 01       | DL01         | STATUS               | When STATUS and KRDY are set, the keyboard transfers a status word. On completion of the transfer, STATUS is reset.                                                                  |

| 00       | DL00         | ERROR                | The ERROR bit is set by the program when it detects an error in the data received from the keyboard. When ERROR is set, the error lamp flashes.                                      |

The leading edge of KCST loads DL01 - DL04 and DL06 into the Keyboard CR, and the trailing edge loads in DL00 and DL05. Table 2A-2 defines the bit assignment of the Keyboard CR, and the function of each bit.

### COMMAND EXECUTION

#### INTRODUCTION

The keyboard can execute four operations:

- data word transfer to the Terminal Controller or DTC 8 when a key is depressed (the data sent is actually the address of the depressed key)

- status word transfer, when the STATUS bit is set in the CR, to define the keyboard address (7<sub>8</sub>) and the keyboard style (i.e., TTY or 029)

- tone generation

- indicator lamp illumination.

#### DATA TRANSFER

The keyswitches of the keyboard are connected at the crosspoints of a 15 by 8 line matrix on the Keyboard pcb. (The Keyboard pcb logic is shown on drawing 13132L.) The keyboard control logic addresses each key in sequence, stores the state of the key, and compares it to the previous state of the key. When a change is detected, the control logic initiates a data transfer if the change was caused by a depressed key, or if the change was caused by a released key that has been assigned a release code. Figure 2A-15 is a block diagram of the keyboard logic.

FIGURE 2A-15

KEYBOARD BLOCK DIAGRAM

DL11 STATUS INDICATOR      DL07-06 NOT USED

DL10-08 KYBD ADDRESS      DL05-00 KYBD STYLE CODE

FIGURE 2A-16

STATUS WORD

These tones are generated to inform the operator of various operational conditions. TONE 2 is also generated when the keyboard detects an error.

The keyboard detects two errors:

- a double keystroke error, which occurs when two keys are depressed within 8.5 ms of each other

- a data transfer error, which occurs when a key is depressed and a word is not transferred to the Data Terminal Controller within 4 ms.

When it detects either error, the keyboard flashes the ERROR lamp, generates TONE 2 (830 Hz), and sets an error bit in the next word transferred to memory.

#### VIDEO DISPLAY UNIT

The operation of the VDU is also controlled by its Command Register. The VDU CR is loaded by the program to turn it on-line or off-line and to control its operation when on-line.

The VDU can display a maximum of 480 characters (12 lines of 40 characters each). Each character can be cursoried (underlined) and/or delineated (vertically lined). The VDU uses an 8 x 12 matrix to display each character (this large matrix allows the terminal to display many different alphabets, such as Japanese).

The VDU can be commanded to update:

- any single character on the screen

- any line of characters

- any partial line of characters (from any point on the line to the end of the line only)

- all characters on the screen.

#### INTERFACE

The Data Terminal can adapt to either of the KEY-EDIT systems (KE 50, KE 1000) by using one of two interface pcb.

The internal operation of the Data Terminal is compatible to the 12 BD SI interface; that is, a parallel bit interface. Therefore, when used in a KE 1000 system, the Data Terminal uses a 12 BD SI Interface pcb that allows the Data Terminal and the DTC 8 to communicate via a 12 BD SI interface cable, which may be up to 100 feet long.

If the Data Terminal is used on a KE 50 system, the Data Terminal uses an L/150 Adapter pcb that allows the Data Terminal and Video Control Unit (VCU) to communicate via a serial interface cable which may be up to 500 feet long. The L/150 Adapter must convert data and commands from serial to parallel and vice versa.

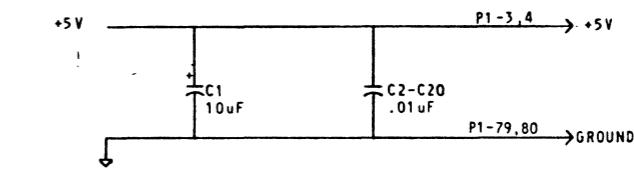

#### POWER

The Data Terminal has its own power supply that can operate on 100, 115, 220, 230 or 240 V ac, depending on the transformer used and how it is tapped. The power supply provides all the dc voltages required to operate the logic and the Cathode Ray Tube (CRT).

#### COMMAND SEQUENCE

There are three stages in a command sequence: Command Initiation, Command Execution, and Command Termination. A command is initiated when the program controlling that device loads a command word into the Keyboard or VDU Command Register. Command Execution is the operation performed by the device as a result of the Command Register loading. A command is terminated when:

- the device completes the required operation

- the program clears the command from the device CR.

The Data Terminal description is divided into four sections: Interface, Keyboard, VDU, and Power. The first section explains how data, status, and command words are transferred between the Data Terminal and the DTC 8 (KE 1000) or Terminal Controller (KE 50). The second section describes the operation of the Keyboard, and the third section describes the operation of the VDU. The fourth section describes the power supply.

#### INTERFACE

The Data Terminal uses one of two Interface pcb. In a KE 1000 system, it uses a 12 BD SI Interface pcb; an L/150 Adapter pcb is used in a KE 50 system.

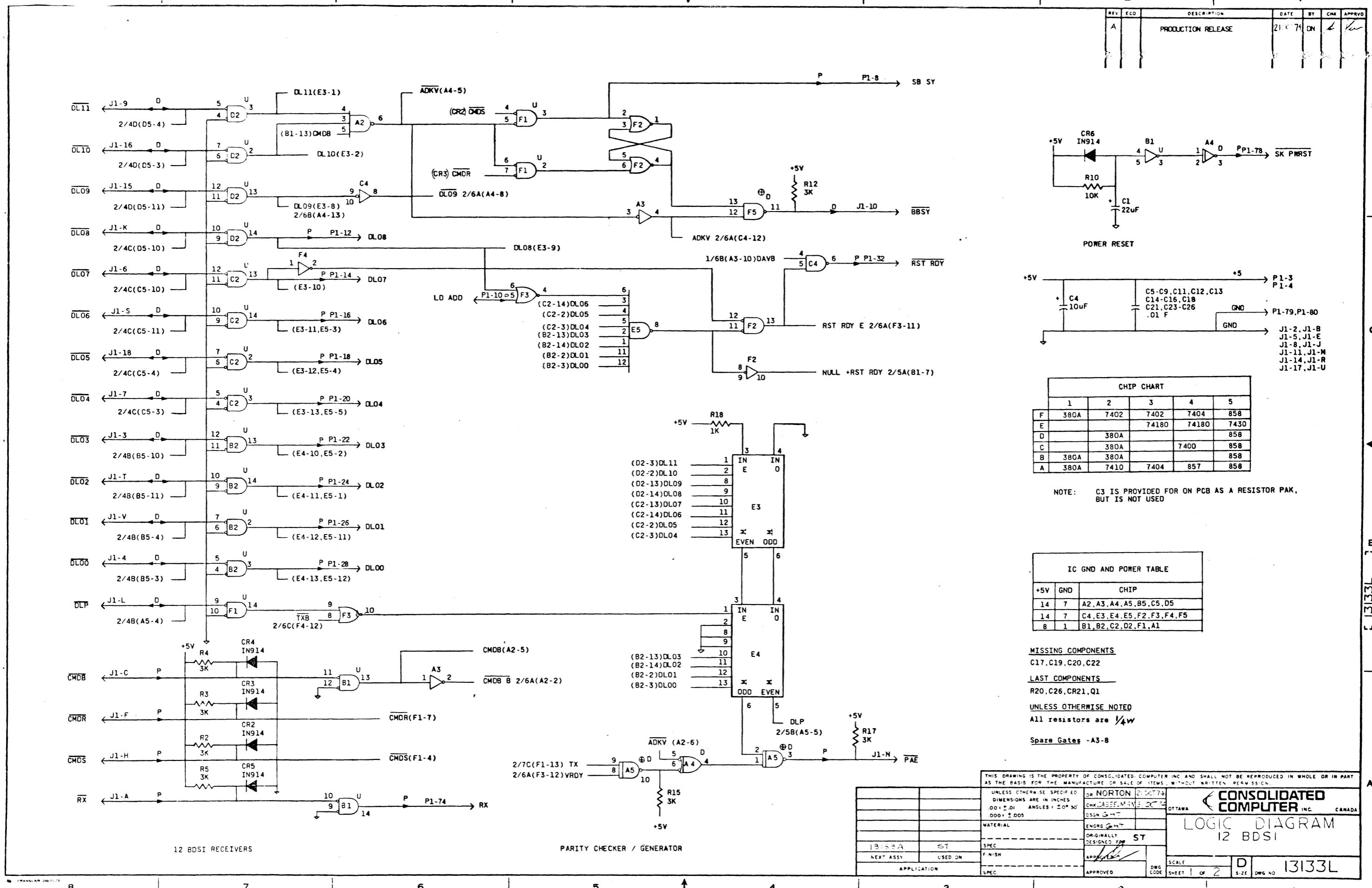

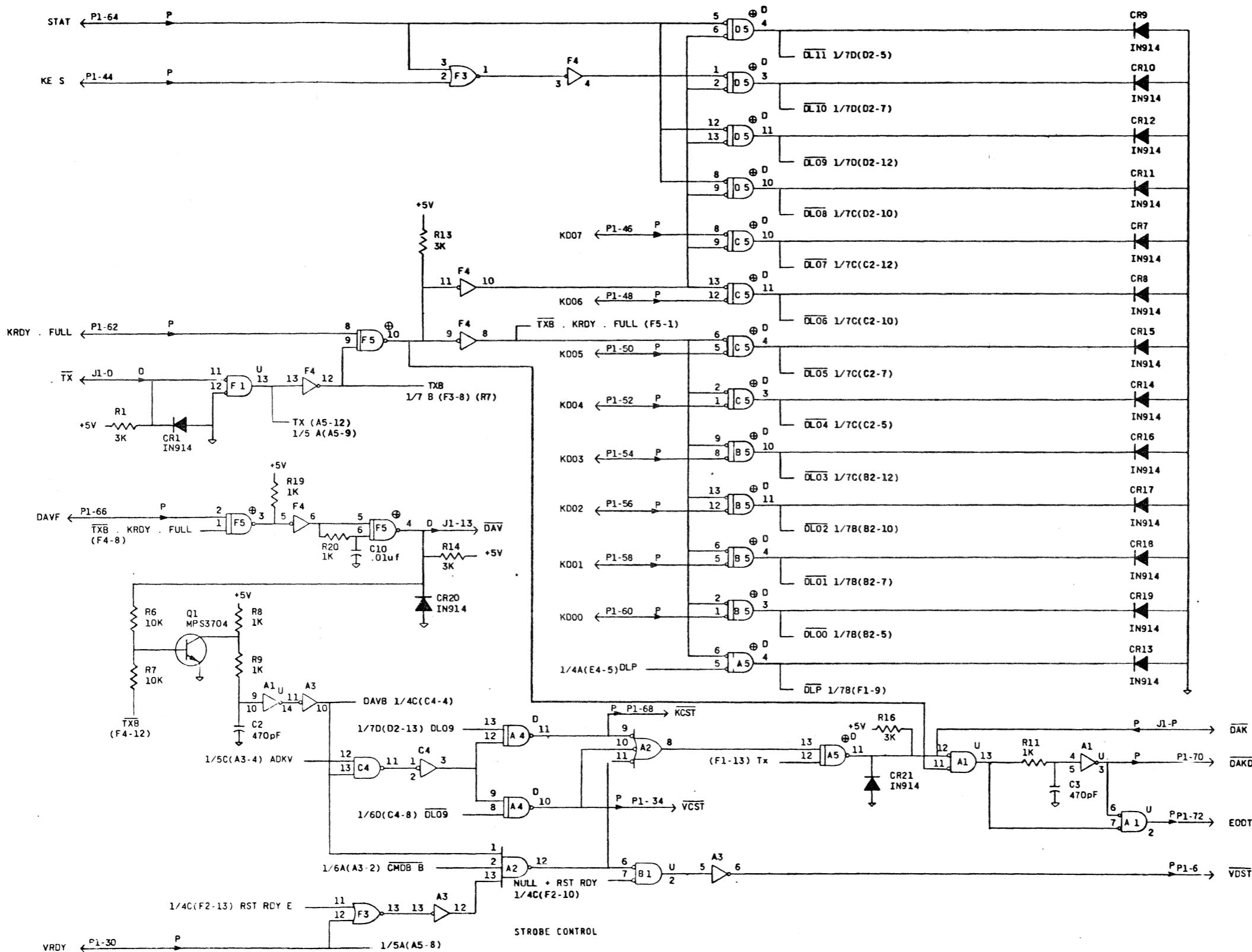

FIGURE 2A-5

12 BD SI DATA FLOW & CONTROL

FIGURE 2A-6

12 BD SI TRANSMIT WORD STRUCTURE

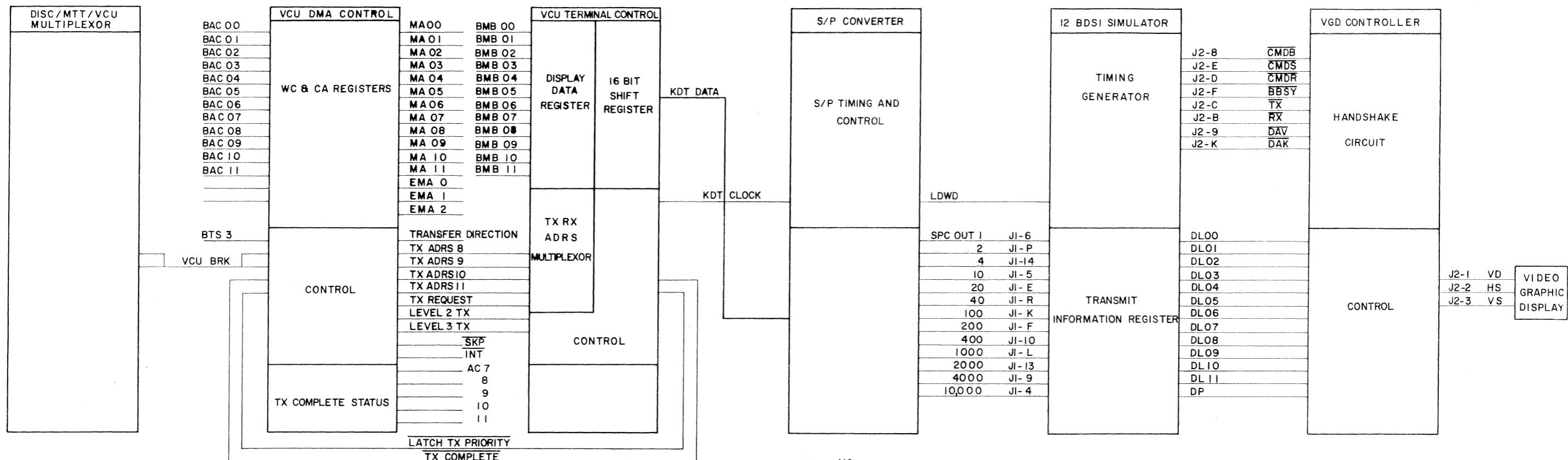

## 12 BD SI INTERFACE

In the KE 1000 system, the Data Terminal communicates with a Data Terminal Concentrator (DTC 8) via a 12-Bit Data Standard Interface (12 BD SI) cable. The cable has 11 control and 12 data lines. Table 2A-1 defines the function of each line.

### 12 BD SI PCB

#### FUNCTIONAL DESCRIPTION

The 12 BD SI PCB allows two-way word transfer between the Data Terminal and the DTC 8. Figure 2A-5 illustrates the data flow between the DTC 8, the Keyboard, and VDU.

The DTC 8 transmits words to either the Keyboard or the VDU, and receives words from the Keyboard only. When the DTC 8 transmits a word to the Data Terminal, the 12 BD SI pcb determines whether the word is a command for the Keyboard, a command for the VDU, or a data or address word for the VDU. Figure 2A-6 illustrates the four word structures.

When the DTC 8 transmits a command word to the Data Terminal, it asserts CMDB of the 12 BD SI line. CMDB enables the 12 BD SI pcb to decode DL11 - DL09. If DL11 - DL09 equal  $7_8$ , the pcb generates KEYBOARD COMMAND STROBE (KCST) when the DTC 8 asserts DAV. KCST loads DL00 - DL06 into the Keyboard CR. If DL11 - DL09 equal  $6_8$ , the 12 BD SI pcb generates VIDEO COMMAND STROBE (VCST) to load DL01 - DL08 into the VDU CR.

TABLE 2A-1

12 BD SI CABLE

| MNEMONIC                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>TX</u>                                                                                                                                                                        | The DTC 8 controls the <u>TRANSMIT</u> line; the line is asserted when the DTC 8 transmits a word to the Data Terminal.                                                                                                                                                                                                                                                                                       |

| <u>RX</u>                                                                                                                                                                        | The DTC 8 also controls the <u>RECEIVE</u> line. <u>RX</u> is false only when the DTC 8 is transmitting data on the 12 BD SI line. When <u>RX</u> is true, the Keyboard can initiate a word transfer to the DTC 8. NOTE: There is a period in the transmit sequence when both <u>RX</u> and <u>TX</u> are false. This time allows the Keyboard to complete a word transfer initiated when <u>RX</u> was true. |

| <u>CMDB</u>                                                                                                                                                                      | The DTC 8 asserts <u>COMMAND BIT</u> if it is transferring a command word for either the Keyboard or VDU. If <u>CMDB</u> is false, the word being transferred is a data or address word for the VDU.                                                                                                                                                                                                          |

| <u>CMDR</u>                                                                                                                                                                      | The DTC 8 asserts <u>COMMAND RESET</u> to reset the <u>BBSY</u> flop in the Data Terminal.                                                                                                                                                                                                                                                                                                                    |

| <u>CMDS</u>                                                                                                                                                                      | The DTC 8 asserts <u>COMMAND SET</u> to set the <u>BBSY</u> flop in the Data Terminal when transferring a command word to the Data Terminal.                                                                                                                                                                                                                                                                  |

| <u>BBSY</u>                                                                                                                                                                      | The DTC 8 checks the state of the <u>BUS BUSY</u> line after the <u>CMDR</u> and <u>CMDS</u> strobes. If <u>BBSY</u> is not in the correct state after each strobe, the DTC 8 terminates the transfer.                                                                                                                                                                                                        |

| <u>DAV</u>                                                                                                                                                                       | <u>DATA AVAILABLE</u> is asserted by the DTC 8 to transfer data into the terminal. The terminal asserts <u>DAV</u> when it transfers data to the DTC 8.                                                                                                                                                                                                                                                       |

| <u>DAK</u>                                                                                                                                                                       | The device receiving data asserts <u>DATA ACKNOWLEDGE</u> to acknowledge the data. On receipt of <u>DAK</u> , the transmitting device clears <u>DAV</u> .                                                                                                                                                                                                                                                     |

| <u>LINT</u>                                                                                                                                                                      | <u>LINE INTERRUPT</u> allows a device to initiate an interrupt; however, it is not used by the Data Terminal.                                                                                                                                                                                                                                                                                                 |

| <u>DL00</u><br><u>DL01</u><br><u>DL02</u><br><u>DL03</u><br><u>DL04</u><br><u>DL05</u><br><u>DL06</u><br><u>DL07</u><br><u>DL08</u><br><u>DL09</u><br><u>DL10</u><br><u>DL11</u> | If <u>CMDB</u> is true, <u>DATA LINES 00</u> - <u>11</u> represent a command word. <u>DL11</u> - <u>DL09</u> define the address of the device ( $7_8$ = Keyboard, $6_8$ = VDU). <u>DL08</u> - <u>DL00</u> define the command for that device. If <u>CMDB</u> is false, <u>DL00</u> - <u>DL11</u> represent a data (Keyboard or VDU), status (Keyboard), or address (VDU) word.                                |

| <u>DLP</u>                                                                                                                                                                       | <u>DATA LINE PARITY</u> is conditioned by the transmitting device (DTC 8 or Keyboard) to maintain odd data parity.                                                                                                                                                                                                                                                                                            |

| <u>PAE</u>                                                                                                                                                                       | When the DTC 8 transmits a word to the Data Terminal, the terminal checks word parity. If parity is incorrect (even), the Data Terminal asserts <u>PARTITY ERROR</u> , and the DTC 8 sets a parity error and terminates the transfer.                                                                                                                                                                         |

If the word transmitted is a data word, the 12 BD SI pcb generates VIDEO DATA STROBE (VDST), provided the VDU is on-line (VIDEO READY (VRDY) true). VDST loads DL00 - DL08 into the VDU Data Register.

The Keyboard can transfer a data, status, or error word to the DTC 8. Figure 2A-7 illustrates the three receive word structures. When the Keyboard has a word to transfer, it asserts KEYBOARD READY (KRDY) FULL and DAVF. If TX of the 12 BD SI line is false, the 12 BD SI pcb asserts DAV and gates the word onto the data lines DL11 - DL00. The DTC 8 responds by asserting DAK to terminate the transfer, and the 12 BD SI pcb generates END OF DATA TRANSFER (EODT) to clear KRDY • FULL.

#### DETAILED DESCRIPTION

Drawing 13133L illustrates the 12 BD SI Interface pcb logic. The pcb accepts words from the DTC 8 (transmit mode) or sends words to the DTC 8 (receive mode).

#### TRANSMIT MODE

##### Introduction

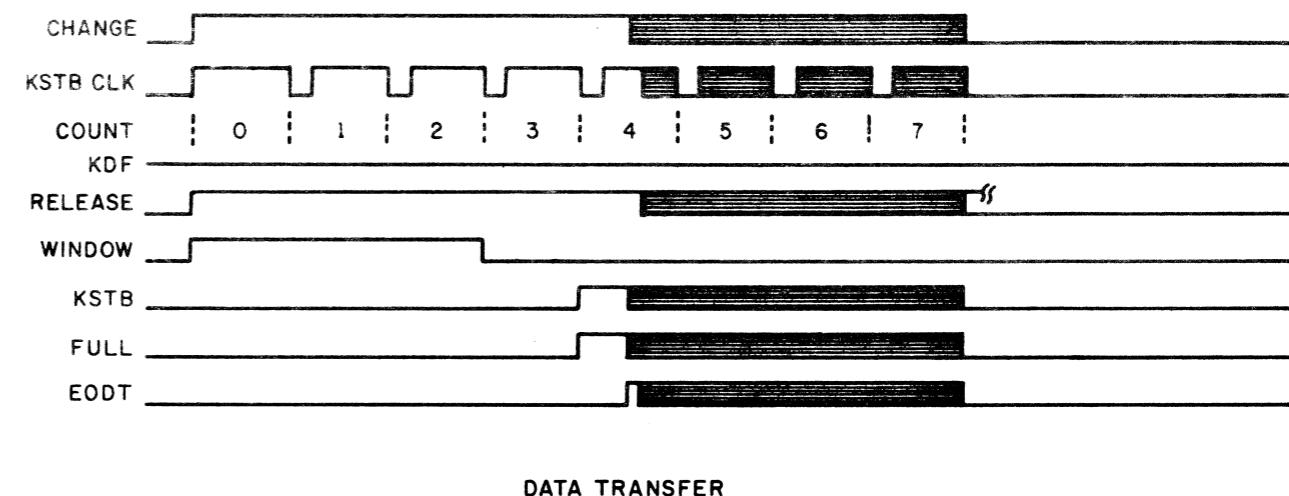

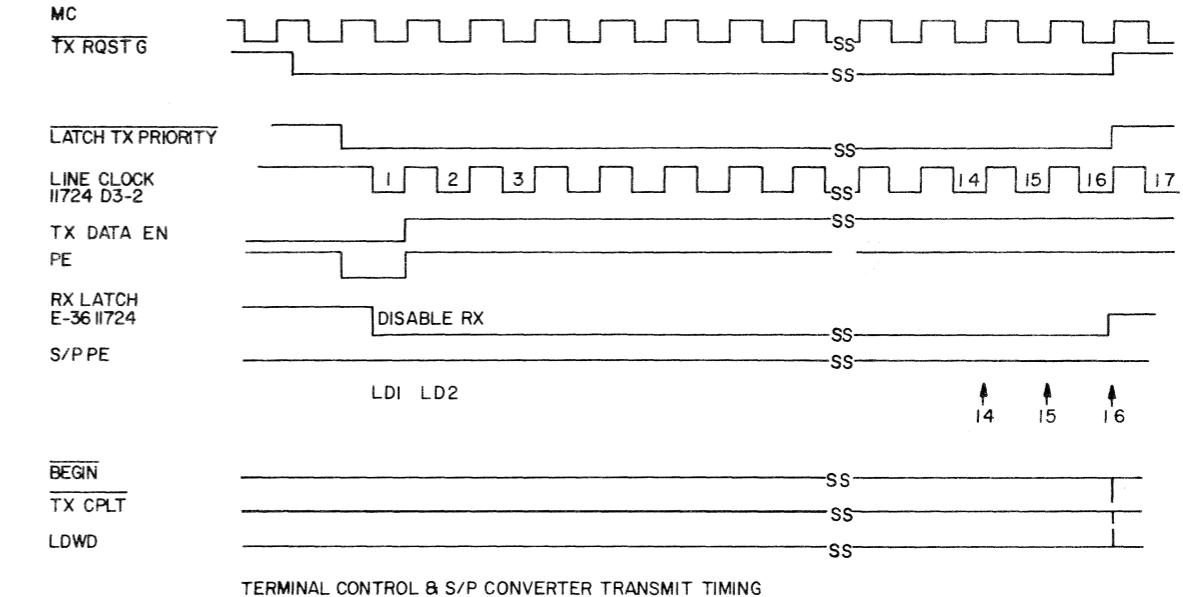

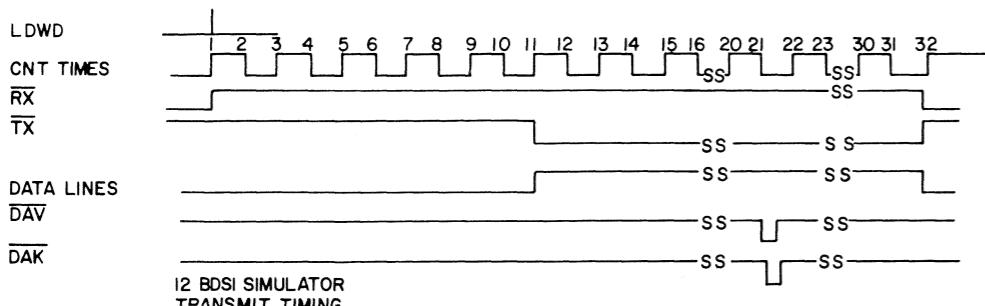

The transmit cycle of the DTC 8 has three periods, each serving a different purpose. Figure 2A-8 illustrates the transmit timing.

During the first period (T1) of the transmit cycle, the DTC 8 resets RX of the 12 BD SI line. This period allows the Keyboard to complete a word transfer initiated when RX was true.

During the second period (T2), the DTC 8 asserts TX and gates the word onto DL11 - DL00, and the 12 BD SI pcb checks data parity. If a parity error has occurred, the DTC 8 sets a parity error and terminates the transfer prematurely. When the DTC 8 transmits a command word, it performs a handshaking sequence with the 12 BD SI pcb by resetting and setting the BBSY flop with CMDR and CMDS. The DTC 8 checks the state of BBSY after each strobe, and if it is not correct, the DTC 8 sets a data transfer error and terminates the transfer prematurely.

During the third period (T3) of the transmit cycle, the DTC 8 asserts DAV, and the 12 BD SI pcb generates one of three strobes, VCST, BDST, or KCST. VCST is generated to load DL01 - DL08 into the VDU CR when the word is a command for the VDU. KCST is generated if the word is a command for the Keyboard; VDST is generated if the word is data for the VDU.

The 12 BD SI pcb asserts DAK approximately 0.5  $\mu$ s after DAV is asserted. DAK causes the DTC 8 to reset DAV, terminating the transfer.

#### Command Word

When a command word is transmitted to the Data Terminal, the DTC 8 asserts CMDB during T2 and T3. CMDB enables gate A2-6 (drawing 13133L, sheet 1) to decode DL11 and DL10. If the command is for either the Keyboard or VDU, DL11 and DL10 are true and ADDRESS KEYBOARD + VDU (ADKV) is asserted. ADKV and ADKV enable the handshaking logic (F1-3, F1-2, F5-11) and the command strobe logic (C4-11, sheet 2).

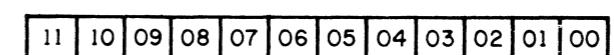

|                | DL 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----------------|-------|----|----|----|----|----|----|----|----|----|----|----|

| KYBD DATA WORD | 0     | 0  | 0  | 0  | x  | x  | x  | x  | x  | x  | x  | x  |

DL11-08 NOT USED

DL07-00 DATA

|                  |   |   |   |   |   |   |   |   |   |   |   |   |

|------------------|---|---|---|---|---|---|---|---|---|---|---|---|

| KYBD STATUS WORD | 1 | 1 | 1 | 1 | 0 | 0 | x | x | x | x | x | x |

|------------------|---|---|---|---|---|---|---|---|---|---|---|---|

DL11 STATUS INDICATOR

DL10-08 KYBD ADDRESS

DL07-06 NOT USED

DL05-00 STATUS

|                 |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------------|---|---|---|---|---|---|---|---|---|---|---|---|

| KYBD ERROR WORD | 0 | 1 | 0 | 0 | x | x | x | x | x | x | x | x |

|-----------------|---|---|---|---|---|---|---|---|---|---|---|---|

DL11 NOT USED

DL10 ERROR INDICATOR

DL09-08 NOT USED

DL07-00 INVALID DATA

**FIGURE 2A-7**

**12 BD SI RECEIVE WORD STRUCTURE**

At  $T_{2_2}$ , the DTC 8 asserts CMDR to reset the BBSY flop, F2-1, F2-4 (sheet 1). At  $T_{2_3}$ , the DTC 8 checks BBSY, and if it is not false, terminates the transfer immediately. If BBSY is false, the DTC 8 asserts CMDS at  $T_{2_4}$ . CMDS sets the BBSY flop, and at  $T_{2_5}$  the DTC 8 checks BBSY again. If BBSY is not true, the DTC 8 terminates the transfer immediately. If BBSY is true, the DTC 8 checks PAE at  $T_{2_6}$ . If it is true (incorrect parity), the DTC 8 terminates the transfer immediately. The 12 BD SI pcb checks DL11 - DL00 and DLP in E3 and E4. If the parity is not odd, E4-6 goes high and PAE (A5-3) is asserted.

If the parity is correct, the DTC 8 asserts DAV to turn Q1 off, allowing DAVB at A3-10 (sheet 2) to go high and enable gate C4-11. This gate conditions the two command strobe gates, A4-11 and A4-10. If DL09 is true (DL11 - DL09 = 7<sub>8</sub>), gate A4-11 is enabled to generate KCST and load the command word into the Keyboard CR. If DL09 is false (DL11 - DL09 = 6<sub>8</sub>), gate A4-11 is enabled to generate VCST and load the command word into the VDU CR. Either strobe causes DAK (A5-11) to be asserted. DAK resets DAV in the DTC 8, which in turn clears the command strobe (KCST, VCST) and DAK. If the DTC 8 does not receive DAK by  $T_{3_7}$ , it terminates the transfer immediately. Normal transmission terminates at the end of  $T_3$ , when DTC 8 resets TX, clears the data from the line, and asserts RX.

#### Data Word

The DTC 8 transmits a data word in the same way as a command word, except that CMDB is not asserted and therefore no handshaking sequence occurs during T2.

Parity is checked during T2 as it is for a command word transmission. If the parity is

correct, the DTC 8 asserts DAV at  $T_3$  and DAVB goes high to condition gate A2-12. As CMDB is false, gate A2-12 is enabled if VRDY or RESET READY ENABLE (RST RDY E) is true, to generate DAK via gates A2-8 and A5-11. VDST is generated at A3-6 only if NULL + RST RDY is false. NULL + RST RDY enables gate B1-2 to assert VDST and load DL00 - DL08 into the VDU Data Register.

FIGURE 2A-8

12 BD SI TRANSMIT MODE TIMING

NULL + RST RDY (F2-10, sheet 1) is generated when a NULL character ( $DL00 - DL08 = 177_8$ ) or a RST RDY character ( $DL00 - DL08 = 377_8$ ) is sent to the VDU. In either case, VDST should not be generated, as RST RDY (C4-6) clears VRDY in the VDU CR, and NULL is used as a filler character and should not be sent to the VDU Data Register. However, if either character is sent, the 12 BD SI pcb must still assert DAK. Normally, when NULL is sent to the VDU, VRDY is true to enable gate A2-12 via gates F3-13 and A3-12. If the character is RST RDY character, VRDY is reset; therefore, RST RDY E enables gate A2-12 to assert DAK.

#### RECEIVE MODE

##### DATA TRANSFER

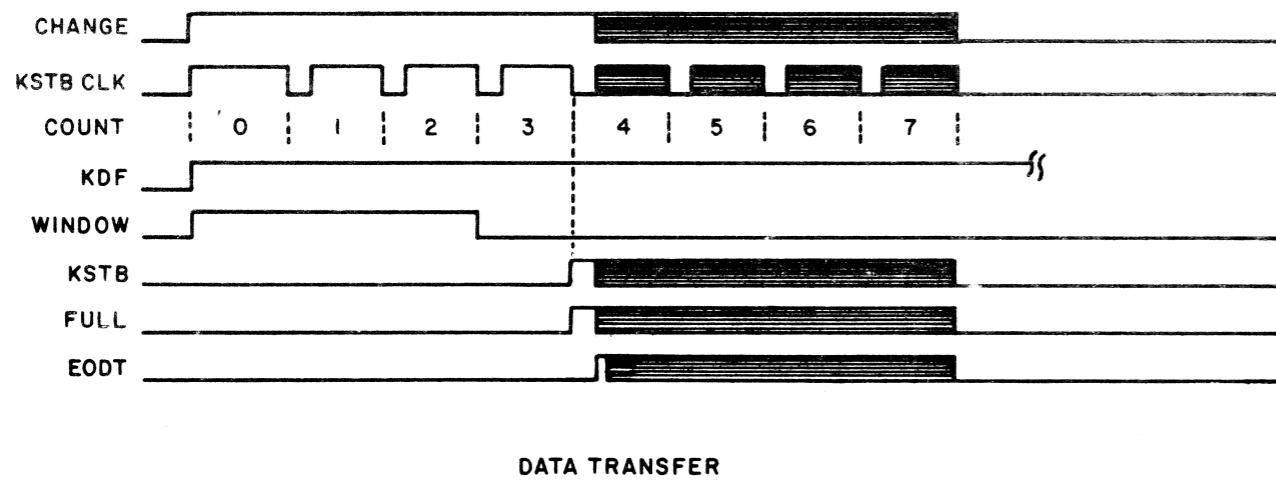

The Keyboard transfers a word to the DTC 8 when it is on-line and a key is depressed, or when the Keyboard is issued a send status command. Figure 2A-9 illustrates the receive mode timing.

When the Keyboard has a word to transfer, it asserts KRDY + FULL and DAVF (sheet 2) when RX is true. Provided TX is false, gate F5-10 is enabled and the signal TXB + KRDY + FULL is asserted. TXB + KRDY + FULL gates the word onto the 12 BD SI line ( $DL11 - DL00$ ) and the parity logic examines  $DL11 - DL00$  to create the parity bit, DLP.

TXB + KRDY + FULL also enables gate F5-3, and after a delay of approximately 5  $\mu$ s, gate F5-4 goes low to assert DAV. On receipt of DAV, the DTC 8 loads the word into the 12 BD SI line buffer and asserts DAK to acknowledge the transfer. When DAK becomes true, gate A1-13 is enabled and DAKD is asserted when capacitor C3 becomes fully charged. DAKD resets DAVF in the Keyboard, causing DAV to go false. When DAV goes false, the DTC 8 resets DAK and gate A1-13 goes low to assert END OF DATA TRANSFER (EODT) at A1-2. EODT remains true until capacitor C3 discharges and forces A1-3 high. EODT resets KRDY + FULL to end the transfer, and the 12 BD SI line is restored.

#### LINE DRIVER CONTROL

The line drivers (sheet 2) are enabled by TXB + KRDY + FULL. The drivers for  $DL07 - DL00$  are controlled by  $KD07 - KD00$  from the Keyboard logic.  $KD07 - KD00$  may represent a key address (data), or the Keyboard status or error status words. Figure 2A-5 illustrates the three different word structures.

The drivers for  $DL11 - DL08$  are controlled by STATUS (STAT) and KEYBOARD ERROR STROBE (KES). If the Keyboard is transferring the Keyboard status, it asserts STAT to force  $DL11 - DL08$  true. If the Keyboard is transferring data, STAT and KES are false, and  $DL11 - DL08$  are therefore false. If the Keyboard is transferring an error word, it asserts KES, forcing  $DL10$  true.

FIGURE 2A-9

12 BD SI RECEIVE MODE TIMING

## 12 BPSI DATA LINE DRIVERS

## L/150 ADAPTER

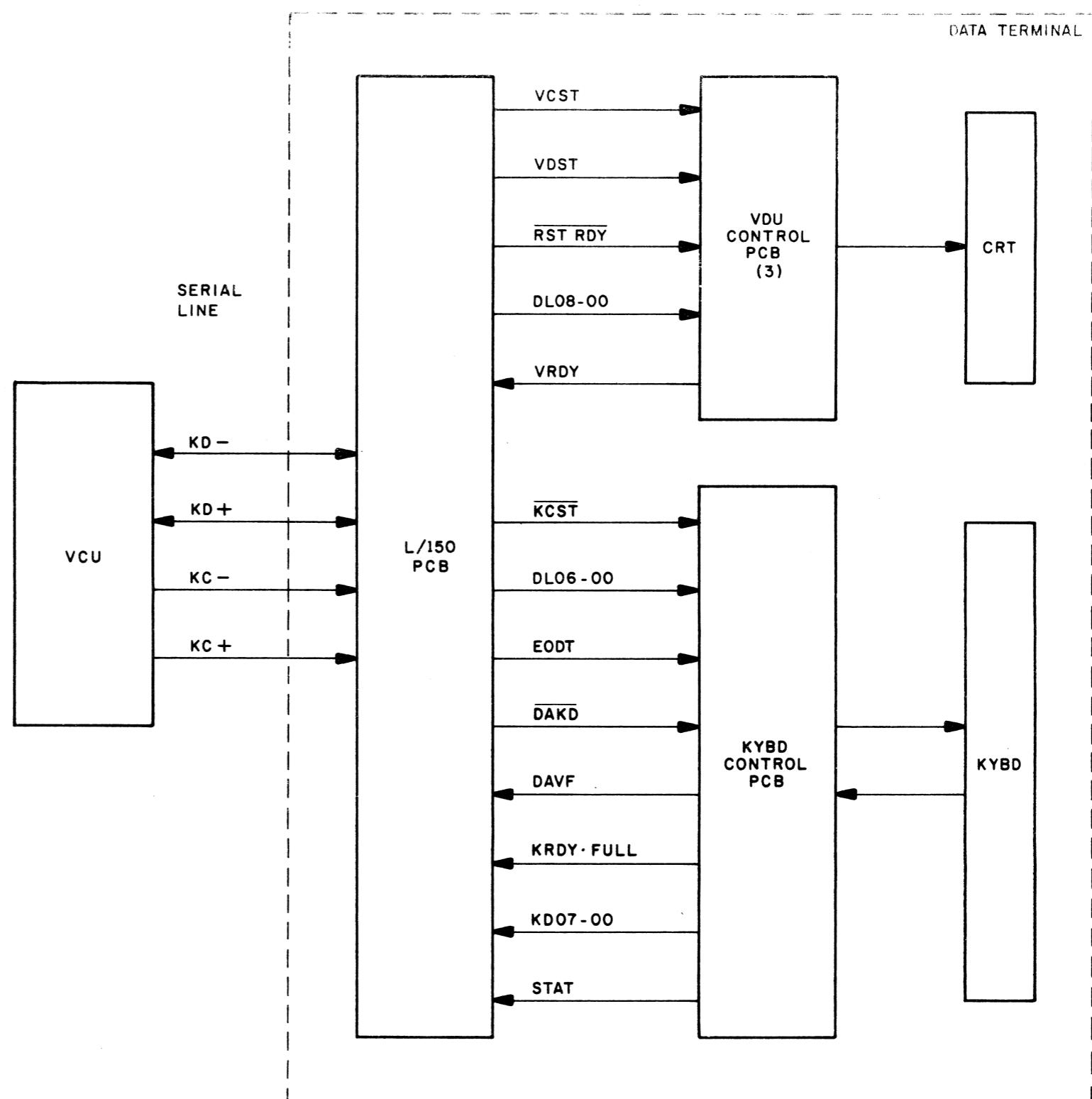

### INTRODUCTION

In a KE 50 system, the Data Terminal communicates with the Terminal Controller via a serial bit interface cable. The cable has two pair of wires, one for bi-directional data transfer, and one to supply the clock pulses for data transfer. Figure 2A-10 illustrates the data flow between the Terminal Controller and the Data Terminal.

When the Terminal Controller transmits a word to the Data Terminal in serial format, the L/150 pcb uses the accompanying clock pulses to load the data into a shift register. When all 16 bits are loaded into the register, the L/150 determines the purpose of the word, which may be either a Keyboard command, a VDU command, or VDU data. Figure 2A-11 illustrates the three word structures for the incoming 16-bit word. The L/150 simulates a 12 BD SI transfer to either the Keyboard or VDU by asserting either KCST to load the word into the Keyboard CR, VCST to load the word into the VDU CR, or VDST to load the word into the VDU Data Register.

Figure 2A-12 illustrates the three receive word structures. When the Keyboard transfers data, error, or status words to the Terminal Controller, it performs the same type of transfer operation as it does for a 12 BD SI interface, except that the word is first stored in the L/150 pcb. The L/150 then generates a transfer request, and the Terminal Controller responds by placing the clock signal on the KC- and KC+ lines. The L/150 then shifts the data, one bit at a time, onto data lines KD+ and KD-, and it is loaded into the Terminal Controller.

FIGURE 2A-10

L/150 DATA FLOW & CONTROL

| KYBD CMD WORD | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|               | 0  | 0  | X  | 1  | 1  | 1  | 1 | 0 | 0 | X | X | X | X | X | X | X |

DB15-14 NOT USED      DB11-09 KYDB ADDRESS

DB13 PARITY BIT      DB08-07 NOT USED

DB12 CMD BIT      DB06-00 KYDB CMD

| KYBD DATA WORD | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                | 0  | 0  | X  | 0  | 0  | 0  | 0 | 0 | 0 | X | X | X | X | X | X | X |

DB15-14 NOT USED      DB12-08 NOT USED

DB13 PARITY BIT      DB07-00 DATA

| VDU CMD WORD | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|              | 0  | 0  | X  | 1  | 1  | 1  | 0 | X | X | X | X | X | X | X | X | 0 |

DB15-14 NOT USED      DB11-09 VDU ADDRESS

DB13 PARITY BIT      DB08-01 VDU CMD

DB12 CMD BIT(1)      DB00 NOT USED

| KYBD ERROR WORD | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                 | 0  | 0  | X  | 0  | 0  | 1  | 0 | 0 | X | X | X | X | X | X | X | X |

DB15-14 NOT USED      DB10 ERROR INDICATOR

DB13 PARITY BIT      DB09-08 NOT USED

DB12-11 NOT USED      DB07-00 DATA

| VDU DATA WORD | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|               | 0  | 0  | X  | 0  | 0  | 0  | 0 | X | X | X | X | X | X | X | X | X |

DB15-14 NOT USED      DB11-09 ADDRESS (0<sub>8</sub>)

DB13 PARITY BIT      DB08-07 NOT USED

DB12 CMD BIT (0)      DB06-00 DATA

| KYBD STATUS WORD | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                  | 0  | 0  | X  | 0  | 1  | 1  | 1 | 0 | 0 | 0 | X | X | X | X | X | X |

DB15-14 NOT USED      DB11-09 KYBD ADDRESS (7<sub>8</sub>)

DB13 PARITY BIT      DB08-06 NOT USED

DB12 NOT USED      DB05-00 KYBD STATUS BITS

FIGURE 2A-11

L/150 TRANSMIT MODE WORDS

FIGURE 2A-12

L/150 RECEIVE MODE WORDS

## DETAILED DESCRIPTION

The KE 50 Terminal Controller transmits 16-bit serial command or data words to the Data Terminal, and receives 16-bit data, status, or error words. Drawing 13366L illustrates the L/150 pcb logic.

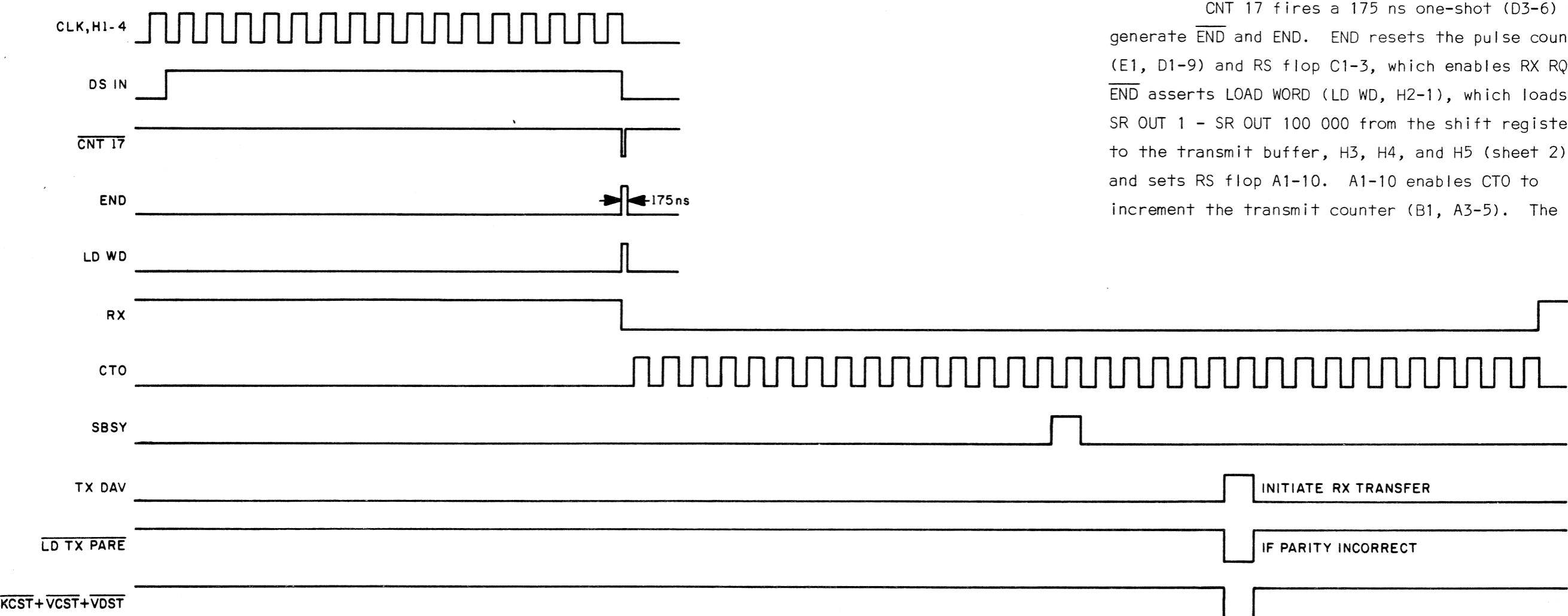

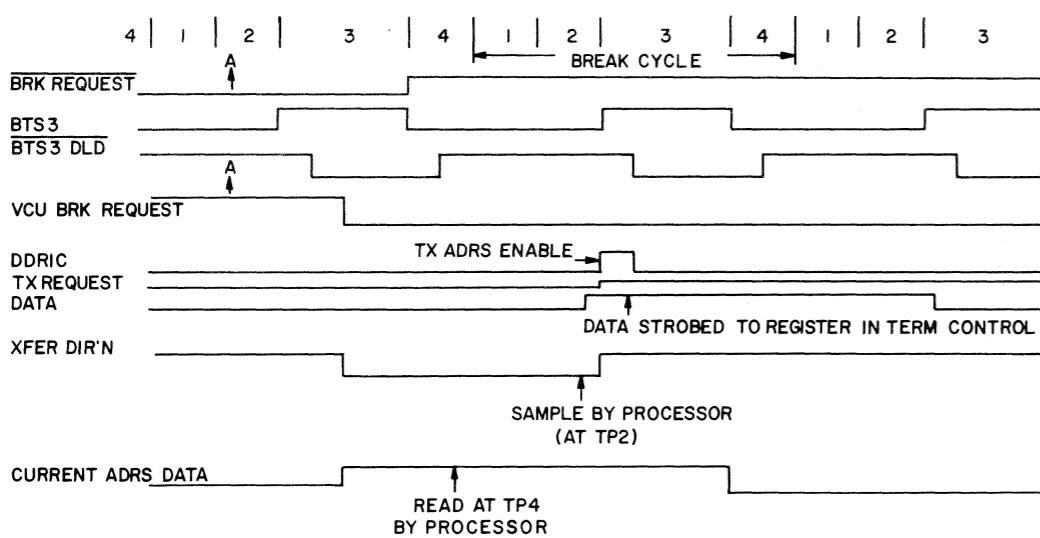

## TRANSMIT MODE

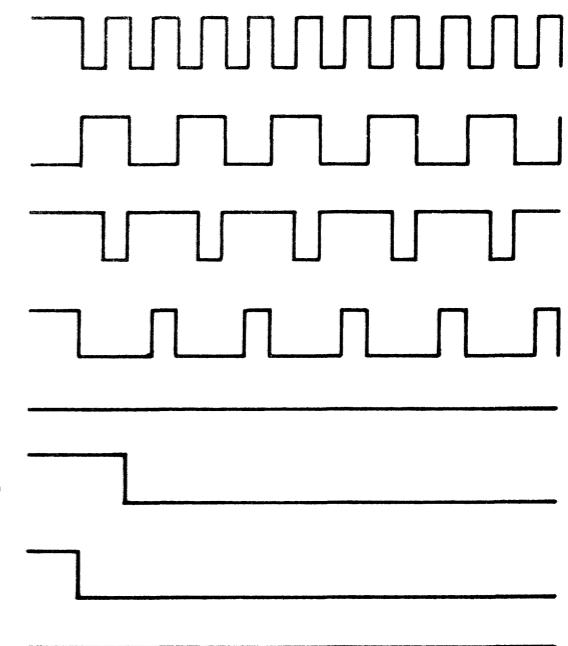

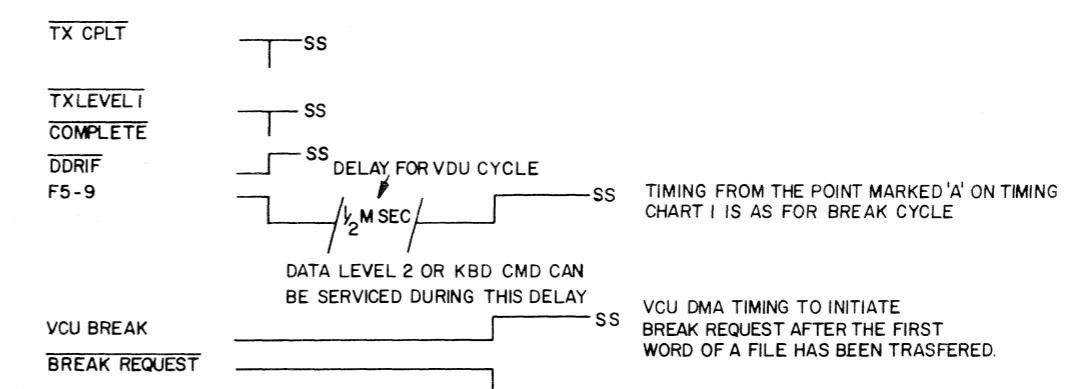

Figure 2A-13 illustrates the transmit timing. When the Terminal Controller has assembled a word, it begins transmission by generating a series of 17 clock pulses. The leading edge of the first clock pulse inhibits a Receive Request (RX RQST) by setting RS flop C1-3 to disable C2-13 (drawing 13366L, sheet 1).

The trailing edge of the first clock pulse gates the least significant bit of the word onto the data line (KD+, KD-), and increments the clock pulse counter (E1, D1-9). The leading edge of the second clock pulse loads the first data bit, DATA SERIAL IN (DS IN), into the 16-bit shift register (F2, F3, F4, F5). This process continues until the leading edge of the 17th clock pulse loads the 16th (final) bit into the shift register, and the trailing edge increments the pulse counter to assert COUNT 17 (CNT 17).

CNT 17 fires a 175 ns one-shot (D3-6) to generate END and END. END resets the pulse counter (E1, D1-9) and RS flop C1-3, which enables RX RQST. END asserts LOAD WORD (LD WD, H2-1), which loads SR OUT 1 - SR OUT 100 000 from the shift register to the transmit buffer, H3, H4, and H5 (sheet 2), and sets RS flop A1-10. A1-10 enables CTO to increment the transmit counter (B1, A3-5). The

FIGURE 2A-13

L/150 TRANSMIT MODE TIMING

FIGURE 2A-14

L/150 RECEIVE MODE TIMING

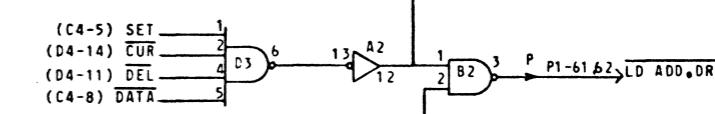

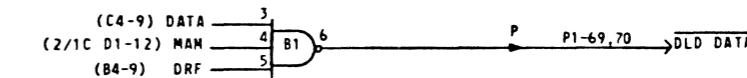

outputs of this counter are used to generate the strobes to transfer the word to the Keyboard CR, the VDU CR, or the VDU Data Register. Flop A1-10 also forces RX false to prevent further data transfer from the Keyboard.

If CMDB is true (H3-15), the L/150 asserts SBSY (E3-13) during the 16th count time (1, 2, 4, and 8 true; 16 false). SBSY is used to clear CMD REGISTER FULL (CRF) on the VDU-2 pcb. During the 21st count time (1, 16, and 4 true; 2 and 8 false), TX DAV is asserted at B3-10 to enable the strobe logic and the parity logic. If the parity is incorrect (TX PARE low), TX DAV asserts LD TX PARE, which asserts RX INITIATE to load TX PARE into the receive buffer (H3, E4, E5) and initiate a receive transfer.

The strobe logic may assert one of three strobes. If CMDB is true, the logic decodes DL11 - DL09. If DL11 - 09 equal 7<sub>8</sub>, the logic asserts KCST (C5-6) when TX DAV goes true. If DL11 - 09 equal 6<sub>8</sub>, the logic asserts VCST (C5-8). KCST loads SL06 - 00 into the Keyboard CR, and VCST loads DL08 - 01 into the VDU CR. If CMDB is false, the logic asserts VDST (D4-6) to load DL08 - DL00 into the VDU Data Register, provided:

- DL08 - DL00 ≠ 177<sub>8</sub> (NULL character)

- DL08 - DL00 ≠ 377<sub>8</sub> (RESET VDU CR)

- LOAD ADDRESS (LD ADD) is false.

If LD ADD is true, 177<sub>8</sub> or 377<sub>8</sub> may be a valid address.

At the end of the count of 32, the logic clears the transmit counter (B1, A3-5) and resets RS flop A1-10, allowing RX to go true, and inhibiting CTO from incrementing the counter.

#### RECEIVE MODE

Figure 2A-14 illustrates receive mode timing. The L/150 pcb initiates a receive mode transfer when:

- the Keyboard sends a data word

- the Keyboard sends a status word

- the Keyboard sends an error word

- the L/150 detects a parity error during a transmit sequence.

The Keyboard sends a word to the L/150 pcb by asserting KRDY • FULL and DAVF. If RX RQST is false, the logic asserts DAKD, which asserts RX INITIATE and resets DAVF in the Keyboard. DAVF goes false to force DAKD false, and B5-3 (sheet 2) asserts EODT for the time capacitor C6 takes to discharge through R22. EODT resets KRDY • FULL in the Keyboard.

RX INITIATE, whether asserted by DAKD or LD TX PARE, loads the receive buffer (H3, E4, E5) and sets the Receive Initiate flop, C3-13 (sheet 1). Provided the L/150 is not in a data transfer sequence (either RX or TX), gate C2-11 goes low to set:

- the RX REQUEST flop (D2-5), which forces a one bit onto the data lines (KD+, KD-) to initiate a receive transfer

- the shift register parallel load flop (D1-5)

- flop D1-9 to enable the clock pulse to the shift register via C2-8 and C2-6.

The Terminal Controller acknowledges the receive transfer request by supplying the clock pulses to shift the word onto the data lines, KD+ and KD-.

The first negative edge of CLK (H1-4) loads the word from the receive buffer (H3, E4, E5) to the shift register, as D1-6 has been set by RX INITIATE. D1-6 enables the shift register to be parallel-loaded. The first negative edge also resets RX RQST (D2-5), which enables the output of the shift register, DS OUT, to control the data line driver via C1-11, and the first data bit is put on the data line. On the next (second) positive edge, the Terminal Controller loads the bit into the receive buffer. This edge also resets the parallel load flop, D1-5. Each of the next fifteen negative edges of CLK shifts a new bit onto the data line, and also increments the clock counter (E1, D1-9). On the 17th (final) negative edge CNT 17 is asserted at C1-8 to trigger one-shot D3-6, which generates END and END. END resets the clock counter via E3-10, and the trailing edge of END resets flop D2-9 to disable gate C2-8, ending the receive mode transfer.

NOTE: Once RX RQST (D2-5) is reset, another word can be stored in the receive buffer.

The address counter is incremented by the scan clock ( $\phi 1$ ), and its output is gated onto KD00 - KD06, provided STATUS is false. KD00 - KD06 address a keyswitch by enabling a decoder driver (KD03 - KD06) and a multiplexor (KD00 - KD02). The outputs of the multiplexor, KEYD and KEYD, reflect the state of the addressed key. If the key is operated (depressed) the ground from the decoder line is shunted to the multiplexor input line and KEYD and KEYD are asserted. KD00 - KD06 also address a release code ROM. If a key has been assigned a release code, the ROM asserts RELEASE when that key is addressed.

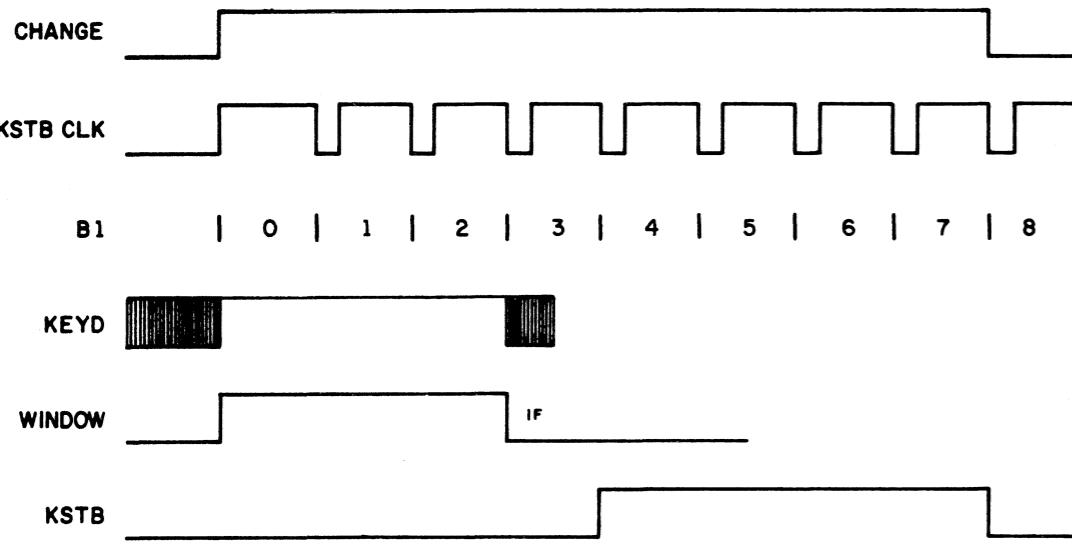

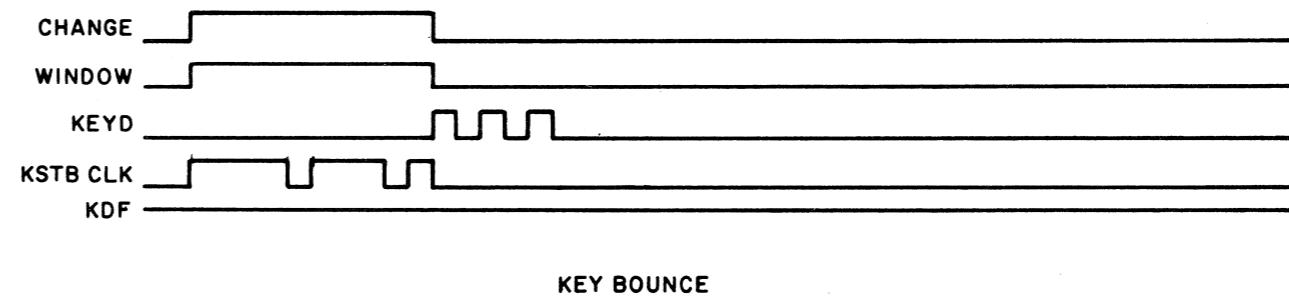

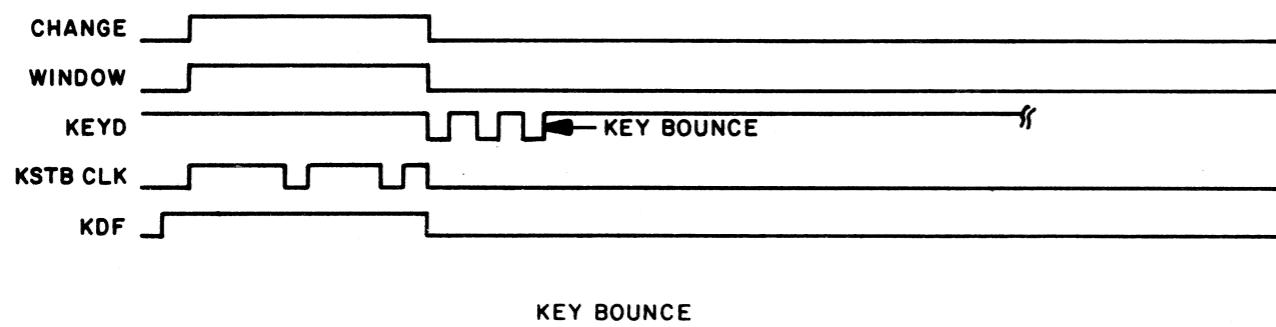

KEYD is stored in the key state detector, which compares it to its state for the previous scan of this key. If a change is detected, CHANGE is asserted when  $\phi 2$  is true. CHANGE halts the SCAN clock, enables the strobe clock, and sets WINDOW. If KEYD remains stable (no key bounce) while WINDOW is true, CHANGE remains true to keep the strobe clock running; otherwise, CHANGE goes false and the control logic returns to scanning the key switches. WINDOW is reset (if there is no key bounce) when the halt counter is incremented to 3. When the halt counter is incremented to 4, the logic generates KSTB if KDF or RELEASE is true. KDF is true if the change was caused by a depressed key; RELEASE is true if the change was caused by a released key that has a release code.

KSTB sets FULL if RX is true. RX is false only when a word is being transferred to the Data Terminal. If the keyboard is on-line (KRDY) and DAKD is false, the control logic asserts DAVF

and KRDY • FULL to initiate a word transfer. The interface pcb performs the transfer, and asserts DAKD and EODT when the transfer is completed. DAKD resets DAVF, and EODT resets FULL, KRDY • FULL, and CHANGE. When CHANGE goes false, the strobe clock is disabled, the scan clock is enabled, and the control logic continues scanning the keyswitches.

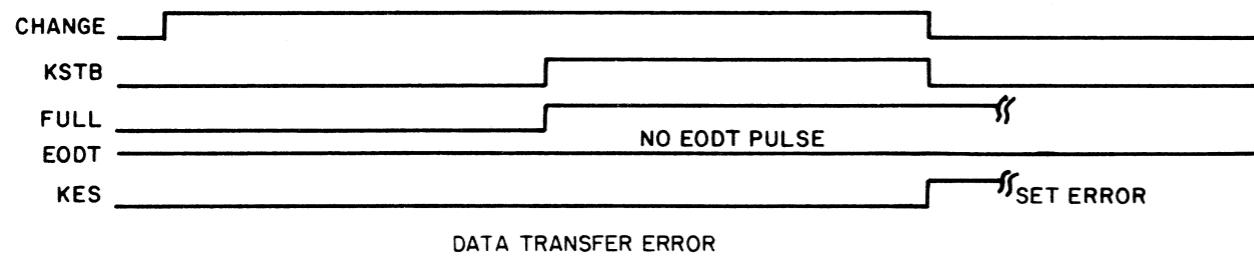

#### ERROR DETECTION

The error logic can detect two error conditions, a double keystroke error, and a data transfer error. A double keystroke error occurs when KSTB is asserted within 8.5 ms of the trailing edge of the last KSTB. A data transfer error occurs when KSTB is asserted to initiate a word transfer, but EODT is not asserted before the halt counter is incremented to an 8 count.

When either error is detected, KES is set. KES sets the ERROR and the TONE 2 bits in the CR, causing the error lamp to flash and an 830 Hz tone to sound. The tone may be interrupted if the FLASH bit is set in the CR.

KES also forces DL10 true when the next word is transferred to the Terminal Controller or DTC 8, and is reset by the next EODT.

#### STATUS TRANSFER

When STATUS (STAT) is set in the CR, the keyboard sends a status word to the DTC 8 or Terminal Controller. Figure 2A-16 defines the significance of each bit of the status word.

STAT inhibits the outputs of the address counter from KD00 - KD05, and STAT forces KD06 and KD07 false. STAT also asserts ENABLE STATUS (ENSTAT) and FULL. ENSTAT gates the keyboard status onto KD00 - KD05, and FULL asserts KRDY • FULL and DAVF to initiate a word transfer. When the transfer is completed, the interface pcb asserts EODT to reset STATUS and end the status transfer.

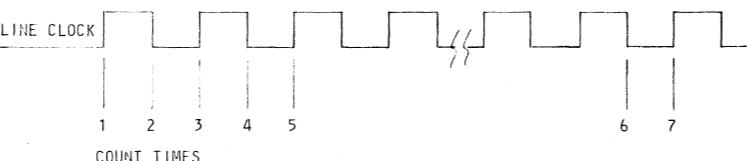

### DETAILED DESCRIPTION

#### KEYBOARD SCANNING

Drawing 13131L illustrates the logic that scans the keyswitch matrix. Drawing 13132L illustrates the Keyboard pcb logic. The scanning sequence is controlled by a scan clock (D5, B5-12, D1-3, B3-10, sheet 2) which generates two pulses,  $\overline{\phi 1}$  (D1-3) and  $\phi 2$  (B3-10). Figure 2A-17 illustrates the scan clock timing.

The leading edge of  $\overline{\phi 1}$  increments the address counter (B4, B5), whose outputs control KD00 - KD06 when STATUS is false. KD00 - KD06 address one of the keyswitches on the Keyboard pcb, and the trailing edge of  $\overline{\phi 1}$  clocks the key state (KEYD) into flop D4-5. The trailing edge of  $\overline{\phi 1}$  also clocks C2, a 128-bit shift register, to load the state of the previously addressed key (D4-9) into the shift register. Thus, the output of the shift register (C2-2) represents state of the key when last addressed, and KDF (D4-5) represents its present state.

HALT CYCLE

KEY

DEPRESSED

(FIGURE 2A-18)

HALT CYCLE

KEY

RELEASED

(FIGURE 2A-19)

NOTES:

1. POSITIVE EDGE OF B5-12 CLOCKS STATE OF KDF INTO D4-9

2. LEADING EDGE OF  $\overline{\varnothing 1}$  INCREMENTS KEYBOARD ADDRESS (KDO - KD6)

3. TRAILING EDGE OF  $\overline{\varnothing 1}$  CLOCKS STATE OF KEYD INTO KDF

4.  $\varnothing 2$  TESTS OLD KEYD STATE-SHIFT REGISTER OUTPUT (C2-2) TO NEW STATE (KDF)- IF DIFFERENT, CHANGE IS ASSERTED TO HALT SCANNER CLOCK (SC) ( $\overline{SC}$ ,  $\overline{\varnothing 1}$ ,  $\varnothing 2$  REMAIN HIGH, B5-12 REMAINS LOW).

5. CHANGE SETS WINDOW TO ALLOW BOUNCE TEST. IF THE STATUS OF KEYD CHANGES WHILE WINDOW IS TRUE, KDF IS RESET (CHANGE SET BECAUSE KEY DEPRESSED) OR SET (CHANGE SET BECAUSE KEY RELEASED) AND STATE OF KDF EQUALS STATE OF C2-2 TO FORCE CHANGE FALSE AND ENABLE THE SCANNER.

FIGURE 2A-17

SCAN CLOCK TIMING

If the states represented by KDF and the shift register output are the same, the scan clock continues to cycle and the next positive edge of B5-12 clocks KDF into flop D4-9. D4-9 is clocked into the shift register by the next trailing edge of  $\overline{\phi 1}$ .

NOTE: D4-9 is needed because the shift register is a CMOS IC that requires a longer set-up time.

If the states are different, neither gate D3-1 nor gate D3-4 become low, and gate E2-11 is enabled at pin 13. When  $\phi 2$  goes high, E2-11 asserts CHANGE to begin a scan HALT cycle by:

- halting the SCAN clock at  $\phi 2$

- setting WINDOW (A2-5)

- enabling the keystroke clock (A6).

During a halt cycle, the control logic determines whether the change of state was caused by a bouncing key, a depressed key, or a released key.

WINDOW (A2-6) enables gates B2-8 and B2-12, which check for key bounce. If the key bounces, KEYD changes state, and either gate B2-8 or B2-12 goes low. If the logic detects what seems to be a released key (KDF false, C2-2 true), but the key bounces, gate B2-8 sets KDF. If the logic detects a depressed key (KDF true, C2-2 false), but the key bounces, gate B2-12 resets KDF. Thus, KDF is restored to the same state as the shift register output (C2-2) when a bouncing key is detected. Where KDF and

the shift register output are the same, either gate D3-1 or D3-4 goes low to reset CHANGE (D2-2), which disables the key strobe clock (A6), and enables the scan clock to end the halt cycle. The next positive edge of B5-12 clocks the state of KDF into flop D4-9, and the flop output is clocked into the shift register by the next trailing edge of  $\overline{\phi 1}$ . Thus the key state stored (KDF) is the same as that stored during the previous scan of this key.

If the key does not bounce while WINDOW is true, the key strobe clock increments the halt counter B1 to a count of 3 and resets WINDOW. When the counter is incremented to 4, B1-8 enables gates C5-13 and E2-8. These gates, with C1-3 and A4-12, determine:

- whether a key strobe should be generated

- whether the halt cycle should be ended.

A keystroke ( $\overline{KSTB}$ ) is asserted by gate E2-8 if the halt occurred because a key that has a release code was released ( $\overline{RELEASED}$  true) or a key was depressed (KDF true).  $\overline{KSTB}$  initiates a word transfer and KD00 - KD07 are used on the interface pcb to form a word for transfer to the DTC 8 or Terminal Controller. KD00 - KD06 represent the key address, and KD07 (B3-4) is asserted only when the transfer is the result of a key that has a release code being released.

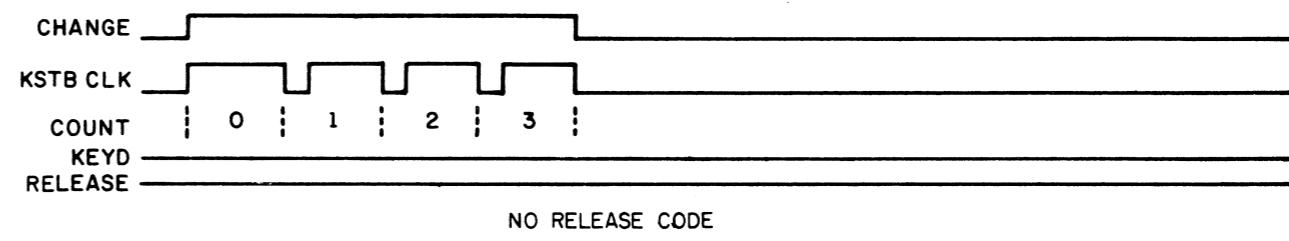

$\overline{KSTB}$  is not asserted if both  $\overline{RELEASED}$  and KDF are false, which occurs when a key is released but has no release code. In this case, gate C5-13 goes low, forcing CHANGE false to end the halt cycle. Figure 2A-18 illustrates the timing when a depressed key is detected, and Figure 2A-19 illustrates the timing when a released key is detected.

The keyboard transfers a word to the DTC 8 or Terminal Controller when  $\overline{KSTB}$  is asserted or STATUS is set in the CR.

$\overline{KSTB}$  asserts FULL (D3-10) by setting flop A3-5, provided RX (B2-6, pin 3 and STATUS (B2-6, pin 4) are false. FULL asserts DAVF (A5-6) if  $\overline{DAKD}$  is false, and asserts KRDY • FULL (B3-13, sheet 1) if the keyboard is on-line (KRDY true at F5-9).

DAVF and KRDY • FULL cause the interface pcb to initiate a word transfer and send the data, KD00 - KD07, to the Terminal Controller or DTC 8. On completion of the transfer, the interface pcb asserts  $\overline{DAKD}$  which resets DAVF. When DAVF goes false, the interface pcb resets DAKD and generates an END OF DATA TRANSFER (EODT) pulse. EODT resets flop A3-5, resetting FULL and KRDY • FULL. EODT also forces gate C5-10 low, which resets CHANGE (D2-2) and ends the halt cycle.

FIGURE 2A-18

DEPRESS HALT TIMING

FIGURE 2A-19

RELEASE HALT TIMING

When the program examines the status of the keyboard, it sends a command word to the keyboard that sets KRDY (F5-9, sheet 1) and STATUS (E4-5). STAT inhibits the output of the key address counter (B4, B5, sheet 2) to KD00 - 05, and STAT forces KD06 (B3-1) and KD07 (B3-4) false. Thus, while the keyboard is transferring a status word, the scanning logic cannot address the keyswitch matrix.

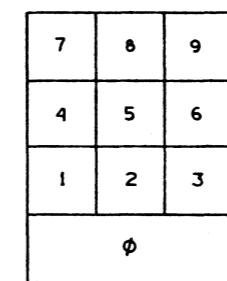

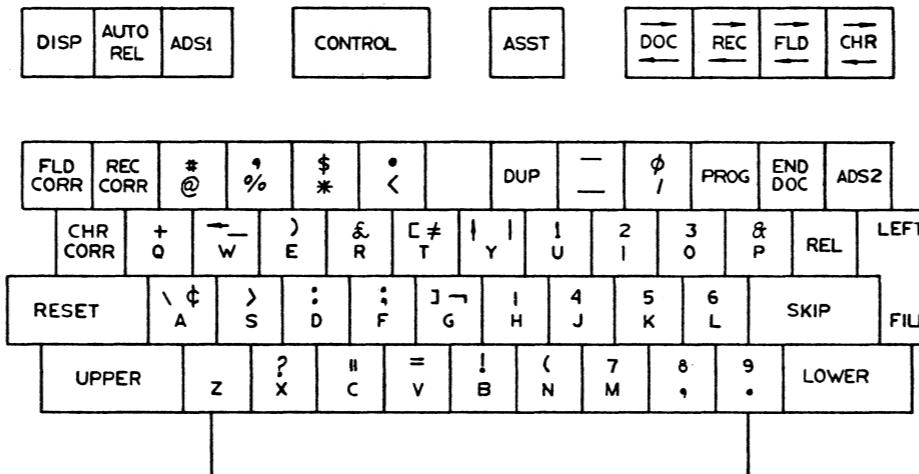

STAT also asserts ENSTAT (D2-8) and FULL (D3-10). ENSTAT enables a six-bit keyboard status code onto KD00 - KD05. FULL asserts DAVF and KRDY • FULL to initiate a data transfer. On completion of the transfer, the Interface pcb asserts DAKD and then EODT. EODT resets STATUS (E4-5, sheet 1) to end the transfer, and the scanning logic is able to address the keyboard. The six keyboard code bits are hardwired on the Keyboard pcb at the time of its manufacture. This code defines the type of keyboard layout. Appendix 2A-1 illustrates the different keyboard layouts and their status code.

#### ERROR DETECTION

The error logic can detect two errors: a data transfer error, and a double keystroke error. A data transfer error is detected when KSTB is asserted to initiate a transfer and EODT is not asserted before the halt counter reaches a count of 8. At this time, KSTB goes false and sets KES (A2-9, sheet 2) as A3-5 is not reset by EODT.

A double keystroke error is detected when a KSTB pulse is asserted with 8.5 ms of the previous KSTB. The trailing edge of KSTB triggers the 8.5 ms one-shot A1-9. If KSTB is asserted before the one-shot times out, KES is set.

KES sets TONE 2 (F5-5, sheet 1) and ERROR (E5-5) in the CR. TONE 2 enables the tone oscillator to generate an 830 Hz tone, and ERROR causes the ERROR lamp to flash.

#### TONE CONTROL

The tone oscillator (F1) generates a 430 Hz tone when the scanning logic detects a depressed key. KDF and KSTB (E2-3) trigger a 50 ms one-shot (F2-3). While the one-shot is active, it enables E1-2 to gate resistor R3 into the oscillator circuit, and a 430 Hz TONE (F3-4) is generated if KRDY is true.

The oscillator is also controlled by two bits of the Command Register, TONE 1 (E5-9) and TONE 2 (F5-5). These bits control gates E3-10 and E3-13. When E3-13 is high, it enables E1-3 to gate R5 into the oscillator circuit. Gate E3-10, when high, enables E1-9 to gate R2 into the oscillator circuit. Under the control of TONE 1 and TONE 2, the oscillator can generate three tones:

- TONE 1 = 550 Hz (R2)

- TONE 2 = 830 Hz (R5)

- TONE 3 = 1320 Hz (R5, R2).

The tone may be continuous, interrupted, or of  $\frac{1}{2}$ -second duration. If FLASH (A3-9) and  $\frac{1}{2}$  SECOND (E4-9) are reset, the tone is continuous. If FLASH is set, the tone is interrupted by the output of the flash oscillator (F2/3). If  $\frac{1}{2}$  SECOND is set, a  $\frac{1}{2}$ -second one-shot is triggered. When the one-shot times out, it fires a 100 ns one-shot (A1-6), which resets  $\frac{1}{2}$  SECOND, TONE 1, and TONE 2.

#### INDICATORS

The keyboard has three indicator lamps: POWER ON, ON-LINE, and ERROR.

The POWER ON lamp (yellow) is lit when the Data Terminal is powered-up; that is, when Vcc and ground are applied to CR3 on the Keyboard pcb. The ON-LINE lamp (green) is lit when KRDY (F5-9) is set in the Keyboard CR. KRDY asserts ON LINE, which grounds CR4. When the ERROR bit is set in the CR, gate F3-3 asserts ERROR, whenever the output of the flash oscillator (F2/3) is high, to cause the error lamp to flash.

THIS DRAWING IS THE PROPERTY OF CONSOLIDATED COMPUTER INC. AND SHALL NOT BE REPRODUCED IN WHOLE OR IN PART AS THE BASIS FOR THE MANUFACTURE OR SALE OF ITEMS, WITHOUT WRITTEN PERMISSION.

000 ± 005 ANGLES ± 0-30

000 ± 005 DSCH 247

**LOGIC DIAGRAM

KEYBOARD COUNTER**

# KEYBOARD CONTROL

|        |            |  |

|--------|------------|--|

| SPEC   | COPIED FOR |  |

| FINISH |            |  |

|          |       |   |       |

|----------|-------|---|-------|

| APPROVED | SCALE | D | 15 15 |

|----------|-------|---|-------|

SPEC APPROVED DWS CODE SHEET 1 OF 2 SIZE DWG NO. 131316

8

3. ALL SWITCHES ARE SHOWN,

AND ARE NOT NECESSARILY

INSTALLED IN ALL POSITIONS.

2. C6 (10, F) IS PROVISIONAL AND IS NOT USED.

MOUNTING HAS BEEN PROVIDED ON THE PWB

UNLESS OTHERWISE SPECIFIED:

PENSATORS = UHMS 1/4 WATT

CAPACITORS = 4E

## NOTES

| CHIP CHART |      |         |      |            |      |

|------------|------|---------|------|------------|------|

|            | 1    | 2       | 3    | 4          | 5    |

| A          | 8312 | RES PAK | 8311 | HMI-7311-5 | 7405 |

|             |         |                                                                                                                                                                                           |          |          |             |

|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------|

|             |         | THIS DRAWING IS THE PROPERTY OF CONSOLIDATED COMPUTER INC. AND SHALL NOT BE REPRODUCED IN WHOLE OR IN PART AS THE BASIS FOR THE MANUFACTURE OR SALE OF ITEMS, WITHOUT WRITTEN PERMISSION. |          |          |             |

|             |         | UNLESS OTHERWISE SPECIFIED,<br>DIMENSIONS ARE IN INCHES<br>001 ± 0.001 ANGLES ± 10°<br>0.0005 DOOR                                                                                        | 1.5000   | 1.0000   | 1.0000      |

|             |         | MATERIAL                                                                                                                                                                                  | ENTRANCE | 1.5000   | 1.0000      |

| 10132A      | ST      | SPEC                                                                                                                                                                                      | OR 1000  | ST       | 1.0000      |

| NEXT ASSY   | USED ON | FINISH                                                                                                                                                                                    | LES 1000 |          |             |

| APPLICATION |         | SPEC                                                                                                                                                                                      | APPROVED | DWG CODE | DATE        |

|             |         |                                                                                                                                                                                           |          |          | 5-57-1-14-1 |

|             |         |                                                                                                                                                                                           |          |          | D 13132L    |

|             |         |                                                                                                                                                                                           |          |          | SIZE DWG NO |

## VIDEO DISPLAY UNIT

### INTRODUCTION

The VDU comprises two elements: the control logic, and the video monitor. Figure 2A-20 is a block diagram of the VDU.

The control logic refreshes the display on the video screen using three signals:

- HORIZONTAL SYNC (HS), which controls the horizontal sweep of the CRT electron gun

- VERTICAL SYNC (VS), which controls the vertical sweep of the gun

- VIDEO DRIVE (VD), which turns the electron gun on or off to illuminate or darken the CRT display surface.

HS and VS are derivatives of the control timing and VD is derived from the timing and the display control logic. The display control logic stores enough information to control the display of the complete line (40 characters), and under timing control, it asserts VD to trace the required display on the screen display surface. When a complete line is displayed, a new line of information is loaded from the display storage.

The display storage logic can store enough information to display 12 lines (480 characters). The software can update this information by issuing commands and sending data. The storage control logic with the Command and Data Registers, controls the update process.

### VIDEO MONITOR

The VDU uses a Ball Brothers Video Monitor. Their Instruction Manual, CRT Data Displays, IM1003, explains monitor operation.

### CONTROL TIMING

This timing controls the refresh sequence of the VDU. Figure 2A-21 illustrates the control timing and its relationship to the display area on the VDU screen.

The master clock generates BIT TIME CLOCK (BTC). BTC is a 50 ns pulse with a period of 102 ns. The period of BTC is controlled by a phase comparator which compares the timing to the ac line frequency. The circuit automatically adjusts BTC if it becomes too long or too short. As the Data Terminal can use 50 Hz or 60 Hz, the phase comparator circuit must be adjusted to the line frequency (R7, VDU-3, pcb 13136). The purpose of this circuit is to eliminate any swimming effect.

BTC clocks the bit time generator, which produces BIT TIMES (BT) 0 - BT9. The trailing edge of BT9 clocks the character width time generator to produce CHARACTER WIDTH TIMES (CWT1, CWT2, CWT4, CWT8, CWT10, CWT20, and CWT30).

VD is disabled during CWT0 to CWT4 and CWT45 to CWT60. CWT0 to CWT4 provide a 5-character width space between the left edge of the screen and the left margin of the display area. CWT45 to CWT49 provide an identical spacing on the right of the screen. HS is asserted at CWT50 to enable the flyback action of the horizontal sweep. CWT50 - CWT60 allow the beam time to swing back to the

FIGURE 2A-20

VDU BLOCK DIAGRAM

left edge of the screen. HS is synchronized to  $\approx 16$  kHz by an astable multivibrator circuit to prevent damage to the video monitor.

One ROW TIME (RT) comprises 60 CWT. The RT generator is clocked by the trailing edge of CWT30 (60th CWT), and produces sixteen row times, RT0 - RT15.

One CHARACTER LINE TIME comprises 16 row times. The leading edge of RT15 clocks the CLT generator to produce CLT1, CLT2, CLT4, CLT8, and CLT16. The VDU displays one line of 40 characters during each CLT. At the end of the refresh cycle (CLT16, 60 Hz, or CLT19, 50 Hz), the control times assert VS to enable the vertical flyback action. At the end of CLT16 or CLT19, LAST LINE RESET (LLR) is generated to reset the CLT generator and CWT10, CWT20, and CWT30 of the CWT generator.

NOTE: The duration of VS depends on the line frequency used. If the source is 60 Hz ac, the vertical sweep is  $\approx 16.6$  ms. If the source is 50 Hz, the vertical sweep is 20 ms, slower than that of the 60 Hz source; therefore, to keep VS in sync with the line period, VS must be generated at a later time, CLT19.

During this time, the control logic can trace 16 character lines (CLT0 - CLT15). The 17th CLT (CLT16) allows time for the vertical flyback action.

FIGURE 2A-21

VDU TIMING PULSES

VD is only enabled between CLT3 and CLT14, the 12 character display lines. CLT0 to CLT2 provide a space between the top of the screen and the first display line. CLT15 (60 Hz) or CLT15 to CLT18 (50 Hz) provides a space at the bottom of the screen. CLT16 (60 Hz) or CLT19 (50 Hz) allows time for the vertical fly back action.

#### DISPLAY FORMAT

The display area on the screen is bounded by the 6th and 45th CWT (CWT5 - CWT44) and by the 4th and 15th CLT (CLT3 - CLT14) to create a display area of 12 lines of 40 characters each (480 characters).

Each character is displayed in a 10 x 16 dot matrix on the screen (Figure 2A-21). A character, a cursor, and a delineator can be displayed within this matrix. The character is displayed within an 8 x 12 matrix (BT0 - BT7 x RT0 - RT11). The cursor is displayed in the 14th row (CLT13) and the delineator is displayed in the 10th column (BT9 of RT0 - RT15). Appendix 2A-2 illustrates the display of each character.

#### VIDEO DRIVE

The control logic asserts VD to illuminate an area on the screen. VD is controlled by the character generation logic and control timing. As the electron gun swings horizontally, the beam is turned on and off to trace the desired image on the screen. To trace a complete character line (40 characters), 16 horizontal sweeps are required. Figure 2A-22 is a block diagram of the logic that controls the electron gun.

5180

The Main Shift Register (MSR) is a 9 x 512-bit register that stores all the data to be displayed on the screen. Seven bits control the character display (8 x 10 matrix), one controls the cursor display (row 14 of the 10 x 16 matrix), and one controls the delineator display (column 10 of the 10 x 16 matrix). Any location within the MSR can be updated under program control.

The Line Shift Register (LSR) is a 9 x 40-bit register that stores enough data to display one character line (40 characters). Forty characters are transferred from the MSR to the LSR during RT15 of each character line time. Thus, the LSR must be loaded 12 times during a refresh cycle, once for each display line.

When RT15 is true, it disables the recirculation (internal) of the LSR, and enables the output of the MSR to be loaded into the LSR when LSR CLOCK (LSRC) goes true. LSRC is asserted during BT1 - BT4 ( $\approx 408$  ns) when CWT4/44 is true (CWT4/44 is true from the beginning of CWT4 to the beginning of CWT44). Thus LSRC is asserted 40 times during RT15 to load 40 characters from the MSR.

As the data originates in the MSR, the MSR must also be shifted 40 times. LSRC asserts MAIN SHIFT REGISTER CLOCK (MSRC) when RT13 and CLT3/15 are true. However, MSRC lags LSRC by 100 ns, enabling LSRC to load the LSR before the MSR is shift-loaded. MSRC normally loads the MSR

FIGURE 2A-22

VIDEO DRIVE CONTROL

output (DB6R - DB0R) back into the MSR to recirculate the whole display field. However, input to the MSR is controlled by a multiplexor, which selects under program control as the input source, the MSR output, or the VDU Data Register. The latter is the source when the program issues a command to the VDU to update the MSR, and transfers data to the Data Register (refer to COMMAND EXECUTION).

During RT0 - RT14 (RT15 false), the LSR is allowed to recirculate, as its content controls the display of one character line (16 horizontal sweeps). LSR control of the display pattern during one character line time is described in Table 2A-3, in chronological order.

The cycle described in Table 3 repeats itself for each row time RT0 - RT13. As the row count increments, a different ROM location is addressed. After the 12th ROM time, the ROM and CSR are disabled. However, the delineator flop still controls VD at BT9 of these rows. During the 14th row time (RT13), the output of the cursor control flop controls VD. If the flop is set, VD is enabled during BT0 - BT9 of the character width time to trace cursor line.

The LSR is not recirculated during RT15 as it is being loaded with new data from the MSR. Thus, the data that was recirculated during RT0 - RT14 is clocked into the LSR latch for the last time. At the next RT0, the new data in the LSR controls the display pattern for the next character line.

The MSR is shifted 40 times during RT15 of each character line time CLT3 - CLT14, for a total of 480 shifts. However, as the MSR contains 512 locations, the MSR update control logic must shift the MSR 32 times more to bring it back into position for the next refresh cycle of the screen.

During RT0 - RT14 of every character line time, the MSR update logic asserts MSRC 1536 times to recirculate the MSR three complete times. Recirculation is provided so that new data can be loaded into the MSR as fast as the VDU receives it from the DTC 8 or VCU (2 k words/second maximum). Each time the MSR is shifted,

the MSR Address Register is incremented. When the MSR address matches the address in the VDU Address Register, the new data is loaded from the VDU Data Register (character codes) or the VDU Command Register (cursor, delineator), depending upon the command issued. Normally the MSR is loaded from its own output.

Data is transferred from the MSR to the LSR during CLT3 to CLT14 only. Therefore, during CLT15, the MSR update logic asserts MSRC 1568 times instead of the normal 1536 to bring the MSR back to its starting location (0) for the next refresh cycle.

TABLE 2A-3

DISPLAY PATTERN CONTROL

| CHARACTER<br>WIDTH TIME | BIT<br>TIME       | OPERATION                                                                                                                                                               |

|-------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CWT4                    | BT0               | The LSR output is loaded into the LSR latch. The upper seven bits, with the Row Counter outputs (RC1, RC2, RC4, RC8), address the character ROM.                        |

|                         | BT1 to BT4        | LSRC is asserted to shift-load the LSR (recirculate).                                                                                                                   |

|                         | BT8               | By this time, the content of the addressed ROM location is at the input of the Character Shift Register (CSR), and BT8 loads the data (8 bits) into the shift register. |

|                         | BT9               | The trailing edge of BT9 loads the cursor and delineator bits from the LSR into the cursor and delineator control flops.                                                |

|                         |                   | NOTE: At this time all data to be displayed during CWT5 is stored. CWT5 is the first character to be displayed.                                                         |

| CWT5                    | BT0               | 1. New data is loaded from the LSR to the LSR Latch and the ROM is addressed.                                                                                           |

|                         | BT1 to BT4        | 2. The first bit is shifted out of the CSR. If the bit is a one, VD is asserted and the screen is illuminated.                                                          |

|                         | BT5<br>BT6<br>BT7 | 1. LSRC is asserted to shift-load the LSR.                                                                                                                              |

|                         | BT9               | 2. The next four bits of the CSR are shifted out to control VD.                                                                                                         |

|                         |                   | The last three bits of the CSR are shifted to control VD.                                                                                                               |

|                         |                   | If the delineator control flop is set, the delineator bit is lit for this CWT.                                                                                          |

| CWT6<br>CWT43           | BT0 to BT7        | The same process as for CWT5 occurs.                                                                                                                                    |

| CWT44                   | BT0 to BT7        | The eight bits are shifted out of the CSR to control VD for the first 8 bit times.                                                                                      |

|                         | BT9               | If the delineator flop is set, the delineator bit for this CWT and row is lit.                                                                                          |

## COMMAND INITIATION

### INTRODUCTION

The program issues commands to the VDU to update the information stored in the MSR. The Command Initiation sequence occurs in three stages.

Firstly, the program sends a command word to the VDU, which is loaded into the Command Register. This first command word initiates a Load Address operation in the VDU, enabling the VDU to load the next data word into the VDU Address Register.

Secondly, the program sends a data word to the VDU. The VDU accepts the word and loads it from the VDU Data Register (DR) into the Address Register (AR). This address defines a location within the MSR that is to be updated. The AR may be incremented by the VDU after the update, provided the command so specifies. This allows multiple updates, to the end of a character line, or of the whole display, by issuing a single command.

Lastly, the program sends another command word to the VDU, to determine how the VDU is to update the MSR. The AR content specifies the location in the MSR at which the update sequence is to begin.

Table 2A-4 defines the function of each bit in the CR. Table 2A-5 lists all the legal command words.

TABLE 2A-4

VDU COMMAND REGISTER

| BIT | INPUT | MNEMONIC | FUNCTION                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01  | DL01  | EOL      | When set, END OF LINE inhibits the increment of the AR. It allows the VDU to update information in the VDU to the end of the character line which contains the address.                                                                                                                                                                                                   |

| 02  | DL02  | CUR      | When CURSOR is set, the VDU inserts a cursor bit into the MSR location addressed by the AR.                                                                                                                                                                                                                                                                               |

| 03  | DL03  | DEL      | When DELINEATOR is set, the VDU inserts a delineator bit into the MSR location addressed by the AR.                                                                                                                                                                                                                                                                       |

| 04  | DL04  | INC      | When INCREMENT is set, the VDU increments the AR after the addressed location is updated. INC, with EOL, enables the VDU to update locations in the MSR to the end of the character line which contains the loaded address. INC, with ALL, allows the VDU to update all locations in the MSR. If INC is reset, the VDU only updates the MSR location addressed by the AR. |

| 05  | DL05  | DATA     | When DATA is set, the VDU loads the data, as it is received from the DTC 8, into the MSR location addressed by the AR.                                                                                                                                                                                                                                                    |

| 06  | DL06  | ALL      | When ALL is set, the VDU updates or clears all locations in the MSR.                                                                                                                                                                                                                                                                                                      |

| 07  | DL07  | SET      | When SET is true, the VDU updates the location in the MSR addressed by the AR. When SET is false, the VDU clears the MSR location addressed by the AR.                                                                                                                                                                                                                    |

| 08  | DL08  | VRDY     | VDU READY must be set before the interface PCB can assert <u>VDST</u> to load data words into the Data Register.                                                                                                                                                                                                                                                          |

TABLE 2A-5

VDU COMMANDS

| CODE | COMMAND                                                                                                                                                                                                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 600  | LOAD ADDRESS preconditions the control logic so that it will load the next data word received into the Address Register. If more than one data word is sent, the last represents the address. The AR stores a 9-bit address, allowing 512 address locations; however, only 480 are displayed. |