Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 1

**FIG. 2.**

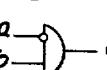

**FIG. 1a.**

**FIG. 1b.**

**FIG. 1c.**

**FIG. 1d.**

**FIG. 1e.**

INVENTOR.

STANLEY P. FRANKEL

By *Bray, Boston & Pavitt*

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 2

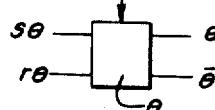

INVENTOR.

STANLEY P. FRANKEL

By *Smyth, Boston & Parrott*

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 3

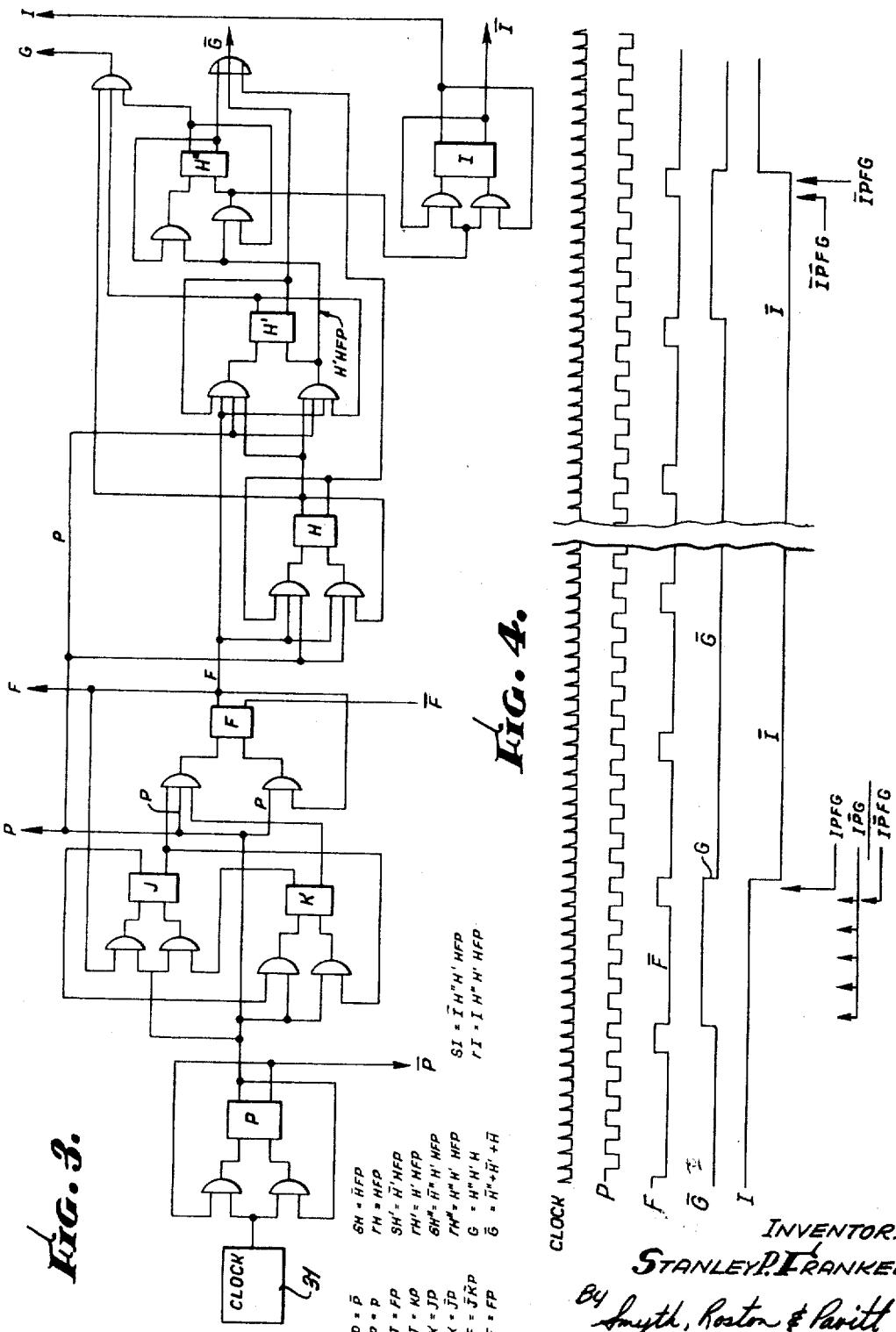

FIG. 5.

$$\left. \begin{array}{l} SV = R \\ RV = \bar{R} \\ GW = V \\ RW = \bar{V} \\ SX = W \\ RX = \bar{W} \\ SY = X \\ TY = \bar{X} \\ SZ = Y \\ RZ = \bar{Y} \end{array} \right\} \text{at } I\bar{P}\bar{E} \quad + \text{IGFP EA VW}$$

$$\left. \begin{array}{l} SE = \bar{E} V (W + X) \\ IE = EV \bar{W} X \\ SA = VW \bar{G} \\ RA = \bar{R} \bar{P} G \end{array} \right\} \text{at } IGFP \quad + AVWZ \text{ IGFP}$$

$$R'' = ZI\bar{P}\bar{E} + (R + A) \cdot IE\bar{P}GWV$$

INVENTOR.

STANLEY P. FRANKEL

By *Smyth, Roston & Pavitt*

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 4

**FIG. 6.**

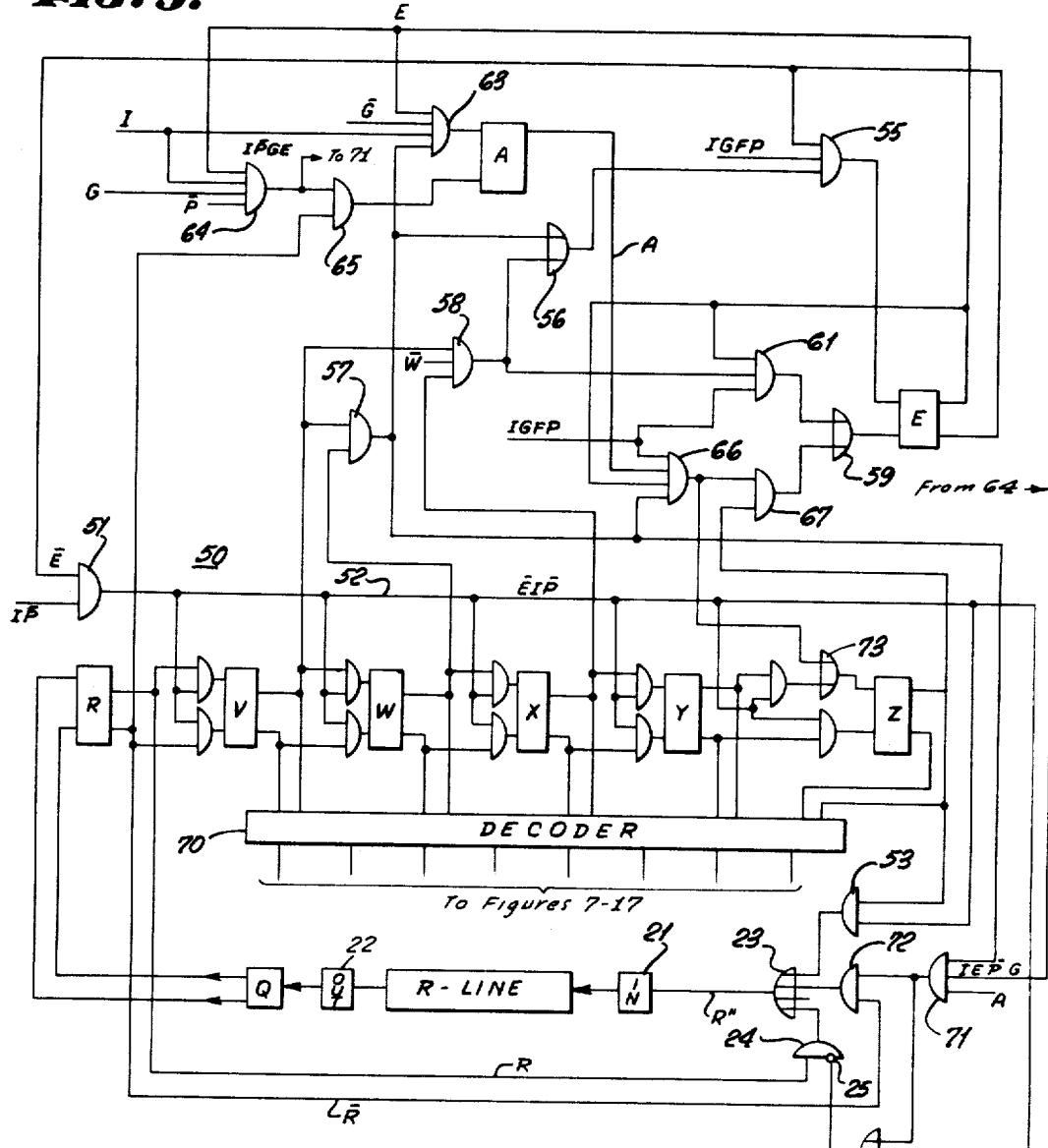

|                          |             | <u>STATE CODES</u>       |               |             |  |  |  |  |  |

|--------------------------|-------------|--------------------------|---------------|-------------|--|--|--|--|--|

| NAME                     | CODE        | NAME                     |               | CODE        |  |  |  |  |  |

|                          |             | <u>IVIWIXIYIZIE</u>      |               |             |  |  |  |  |  |

| TRANSFER ORDERS - SINGLE |             | INPUT OR TEST ORDERS     |               |             |  |  |  |  |  |

| BRING P                  | 0 0 1 1 0 0 | SWITCH                   | 411           | 0 0 0 0 1 0 |  |  |  |  |  |

| BRING $\bar{P}$          | 0 1 1 1 0 0 | "                        | 412           | 0 1 0 0 0 0 |  |  |  |  |  |

| RECORD P                 | 0 0 1 1 1 0 | "                        | 413           | 0 1 0 0 1 0 |  |  |  |  |  |

| RECORD $\bar{P}$         | 0 1 1 1 1 0 | "                        | 414           | 1 0 0 0 0 0 |  |  |  |  |  |

| EXCHANGE                 | 0 1 1 0 0 0 | "                        | 415           | 1 0 0 0 1 0 |  |  |  |  |  |

| TRANSFER - DOUBLE        |             | OUT PUT OR EFFECT ORDERS |               |             |  |  |  |  |  |

| BRING - P (dbl.)         | 1 0 1 1 0 1 | E1                       | 0 0 0 1 1 0   |             |  |  |  |  |  |

| RECORD - P (dbl.)        | 1 0 1 1 1 1 | E2                       | 0 1 0 1 0 0   |             |  |  |  |  |  |

| FILL                     | 1 0 1 0 1 1 | E3                       | 0 1 0 1 1 0   |             |  |  |  |  |  |

| CONDITION, FILL          | 1 0 1 0 0 1 | E4                       | 1 0 0 1 0 X   |             |  |  |  |  |  |

|                          |             | E5                       | 1 0 0 1 1 X   |             |  |  |  |  |  |

| SHIFT AND WAIT - SINGLE  |             | INTERNAL EFFECT ORDER    |               |             |  |  |  |  |  |

| SHIFT                    | 0 1 1 0 1 0 | OR RELOAD PHASE          |               |             |  |  |  |  |  |

| BLANK                    | 0 0 0 0 0 0 | RELOAD                   | 0 0 0 1 0 0+1 |             |  |  |  |  |  |

| SHIFT AND WAIT - LONG    |             | LOADING PHASES           |               |             |  |  |  |  |  |

| SHIFT LONG               |             | INITIAL                  | 0 0 1 0 0 1   |             |  |  |  |  |  |

| (1-32 R cycles)          |             | MARKER                   | 0 0 0 0 0 1   |             |  |  |  |  |  |

| (33-64 R cycles)         |             | DISCRIMINATE             | 0 0 0 0 1 1   |             |  |  |  |  |  |

| WAIT - LONG              |             | LOAD-R                   | 0 0 0 1 1 1   |             |  |  |  |  |  |

| (1-32 R cycles)          |             | CHECK-B                  | 0 0 1 1 1 1   |             |  |  |  |  |  |

| (33-64 R cycles)         |             | SEARCH-TAPE              | 0 0 1 0 1 1   |             |  |  |  |  |  |

|                          |             | SEARCH-M                 | 0 0 1 1 0 1   |             |  |  |  |  |  |

| ARITHMETIC ORDERS        |             |                          |               |             |  |  |  |  |  |

| SINGLE                   |             |                          |               |             |  |  |  |  |  |

| ADD                      | 0 0 1 0 0 0 |                          |               |             |  |  |  |  |  |

| SUBTRACT                 | 0 0 1 0 1 0 |                          |               |             |  |  |  |  |  |

| ARITHMETIC ORDERS, LONG  |             |                          |               |             |  |  |  |  |  |

| MULTIPLY                 |             |                          |               |             |  |  |  |  |  |

| (1-32 R-cycles)          | 1 1 1 1 1 1 |                          |               |             |  |  |  |  |  |

| (33-64 R-cycles)         | 1 1 1 1 0 1 |                          |               |             |  |  |  |  |  |

| DIVIDE                   |             |                          |               |             |  |  |  |  |  |

| (1-32 R-cycles)          | 1 1 1 0 1 1 |                          |               |             |  |  |  |  |  |

| (33-64 R-cycles)         | 1 1 1 0 0 1 |                          |               |             |  |  |  |  |  |

INVENTOR

STANLEY P. FRANKEL

By *Angoff, Boston & Ravitz*

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 5

FIG. 5a.

FIG. 5b.

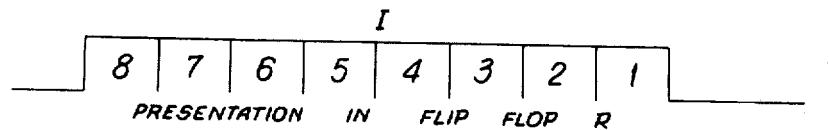

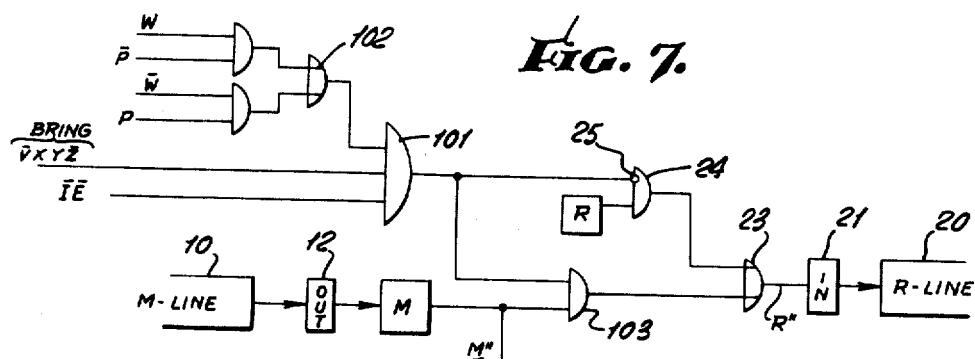

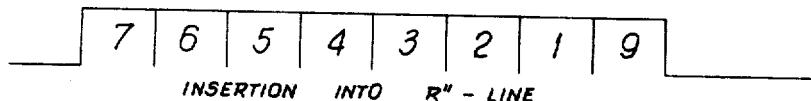

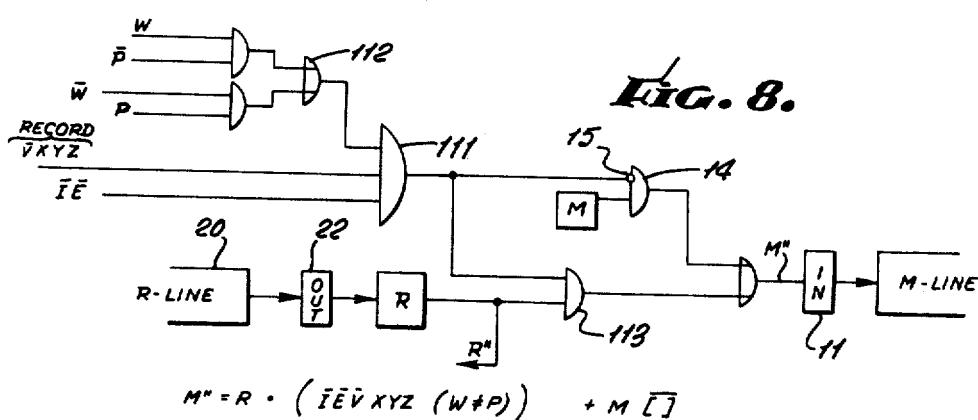

FIG. 7.

FIG. 8.

INVENTOR.

STANLEY P. FRANKEL

By

Smyth, Roaton & Parritt

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

## GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 5

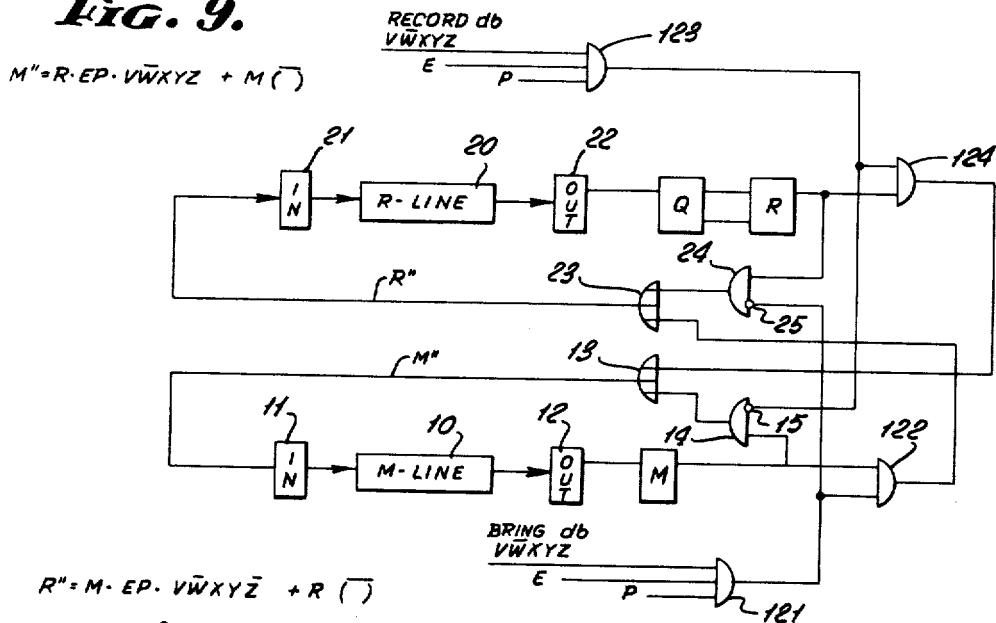

FIG. 9.

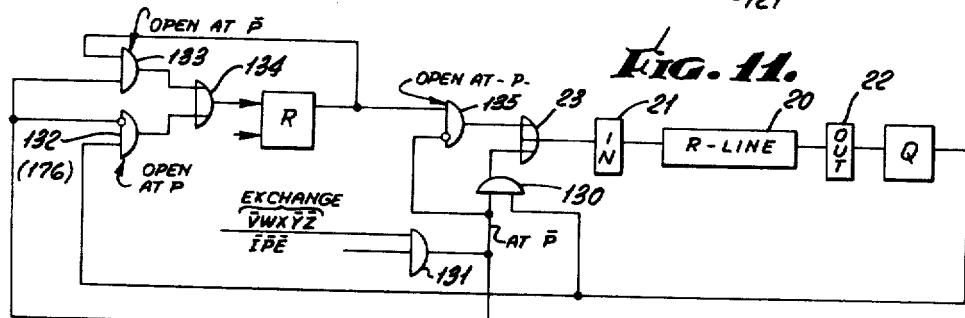

FIG. 11.

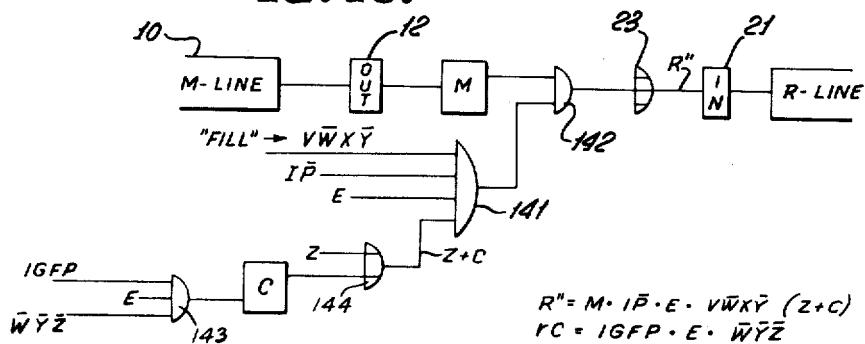

FIG. 11a.

| $\bar{P}$                |  |  |  |  |  |  |  |  |  | $\bar{P}$            |  |  |  |  |  |  |  |  |  |

|--------------------------|--|--|--|--|--|--|--|--|--|----------------------|--|--|--|--|--|--|--|--|--|

| Q 79 80 80 7 1 2 2 3 3   |  |  |  |  |  |  |  |  |  | 39 40 40 41 41 42 42 |  |  |  |  |  |  |  |  |  |

| R 79 79 80 80 7 7 2 2 3  |  |  |  |  |  |  |  |  |  | 39 39 40 40 41 41 42 |  |  |  |  |  |  |  |  |  |

| R" 79 79 80 80 1 1 2 2 3 |  |  |  |  |  |  |  |  |  | 39 39 40 40 76 41 77 |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |  |  |                      |  |  |  |  |  |  |  |  |  |

## TERMINATION DE EXCHANGE

INVENTOR.

STANLEY CONNELLY

STANLEY & RANKIN

By Smyth, Boston & Pavitt

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 7

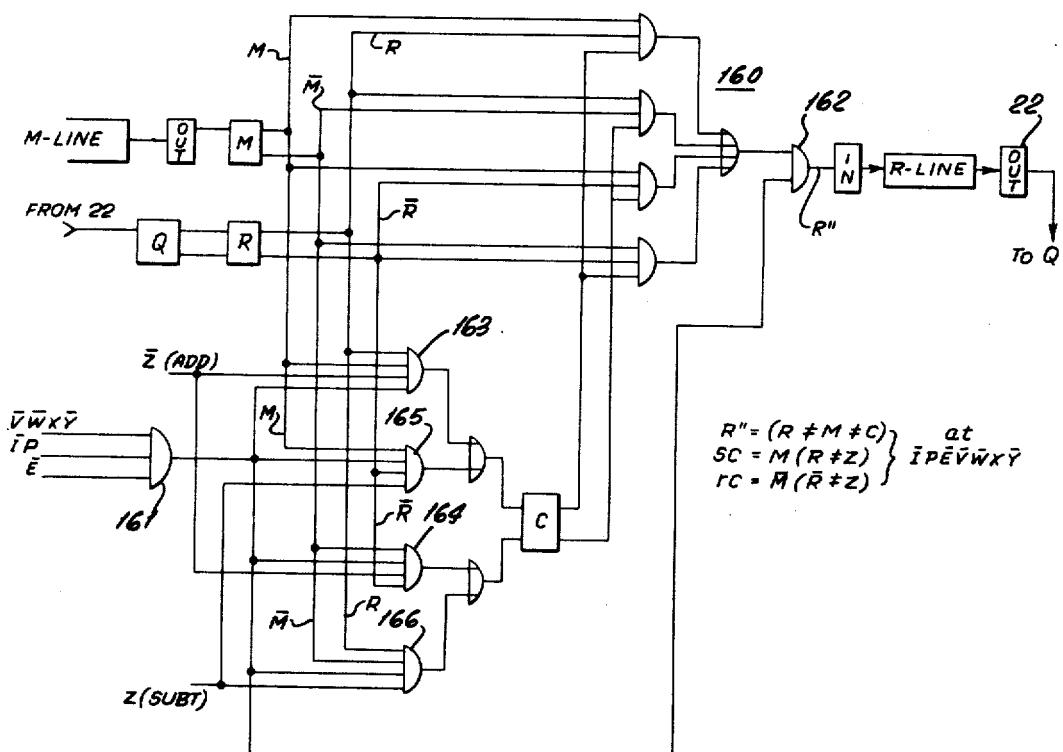

FIG. 10.

FIG. 14.

INVENTOR.

STANLEY P. FRANKEL

By *Smyth, Roston & Pavitt*

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 8

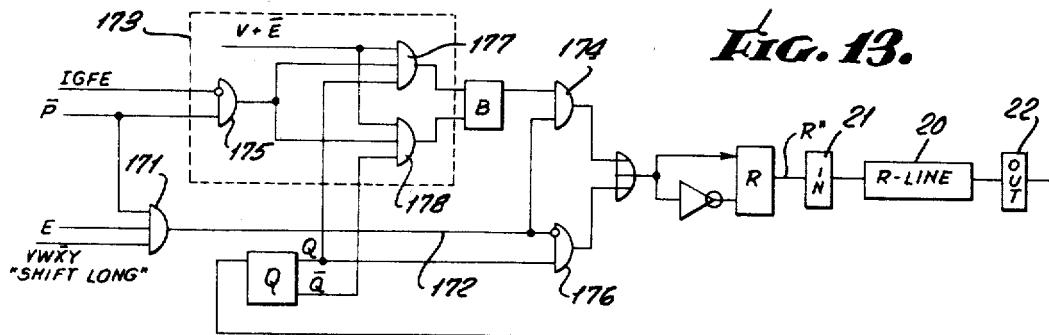

FIG. 13.

$$\begin{aligned} SR &= B \cdot \bar{P} \cdot E \quad VW\bar{X}Y \quad rR = \bar{B} \cdot ( ) \\ SB &= Q \\ rB &= \bar{Q} \end{aligned} \quad \text{at } \bar{P} \cdot (V + \bar{E}) \cdot (IFGE)$$

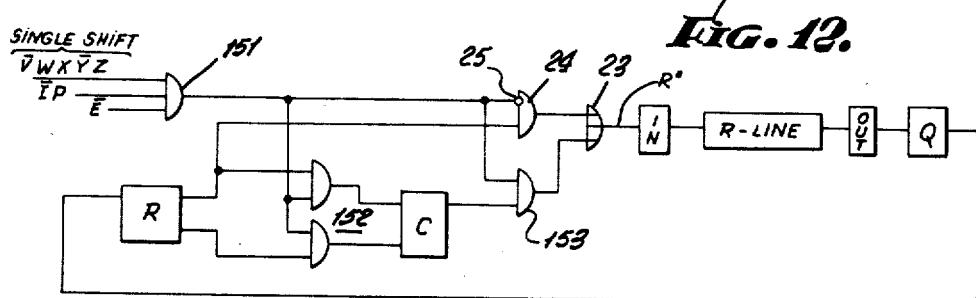

FIG. 12.

FIG. 13a.

INVENTOR.

STANLEY P. FRANKEL

By *Smyth, Rector & Pavitt*

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 9

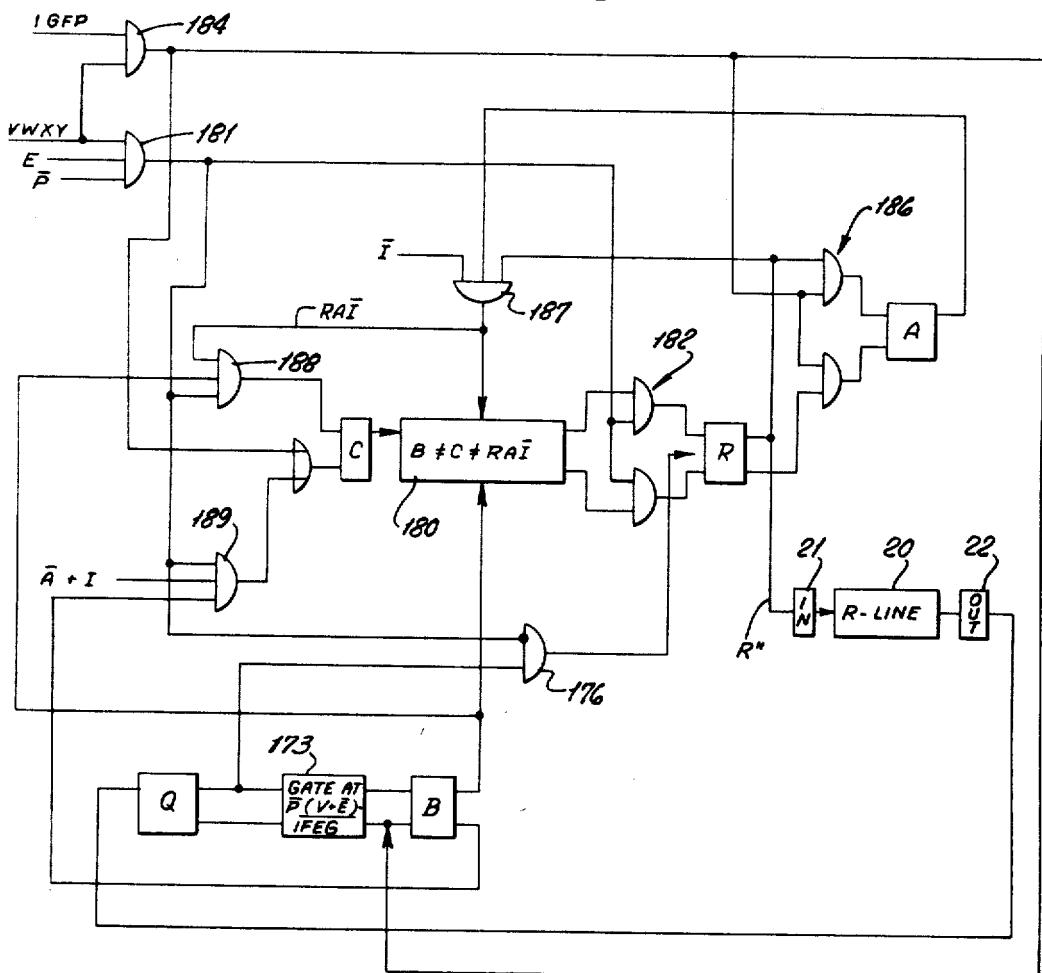

FIG. 15.

$$\begin{aligned} rB &= IGFP \cdot VWXY \\ SA &= R \\ rA &= R \quad \{ \text{at } IGFP \cdot VWXY \\ SR &= (B \neq C \neq RAI) \quad \} \\ rR &= (B \cdot RAI) \quad \} \\ SC &= B \cdot RAI \\ rC &= B(\bar{R} + I) \quad \} \end{aligned}$$

$E \bar{P} VWXY + Q \quad \} \text{at } P$

$+ IGFP \cdot VWXY$

INVENTOR.

STANLEY P. FRANKEL

By

Smyth, Foster & Parritt

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 10

FIG. 15a.

FIG. 15b.

FIG. 17.

SHIFT:  $\begin{cases} SC = R \\ rC = \bar{R} \\ R'' = C \end{cases}$  } at  $\bar{I}P \cdot E \cdot \bar{V}WXYZ$

INVENTOR:

STANLEY P. FRANKEL

By

Smyth, Boston & Parritt

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 11

FIG. 16.

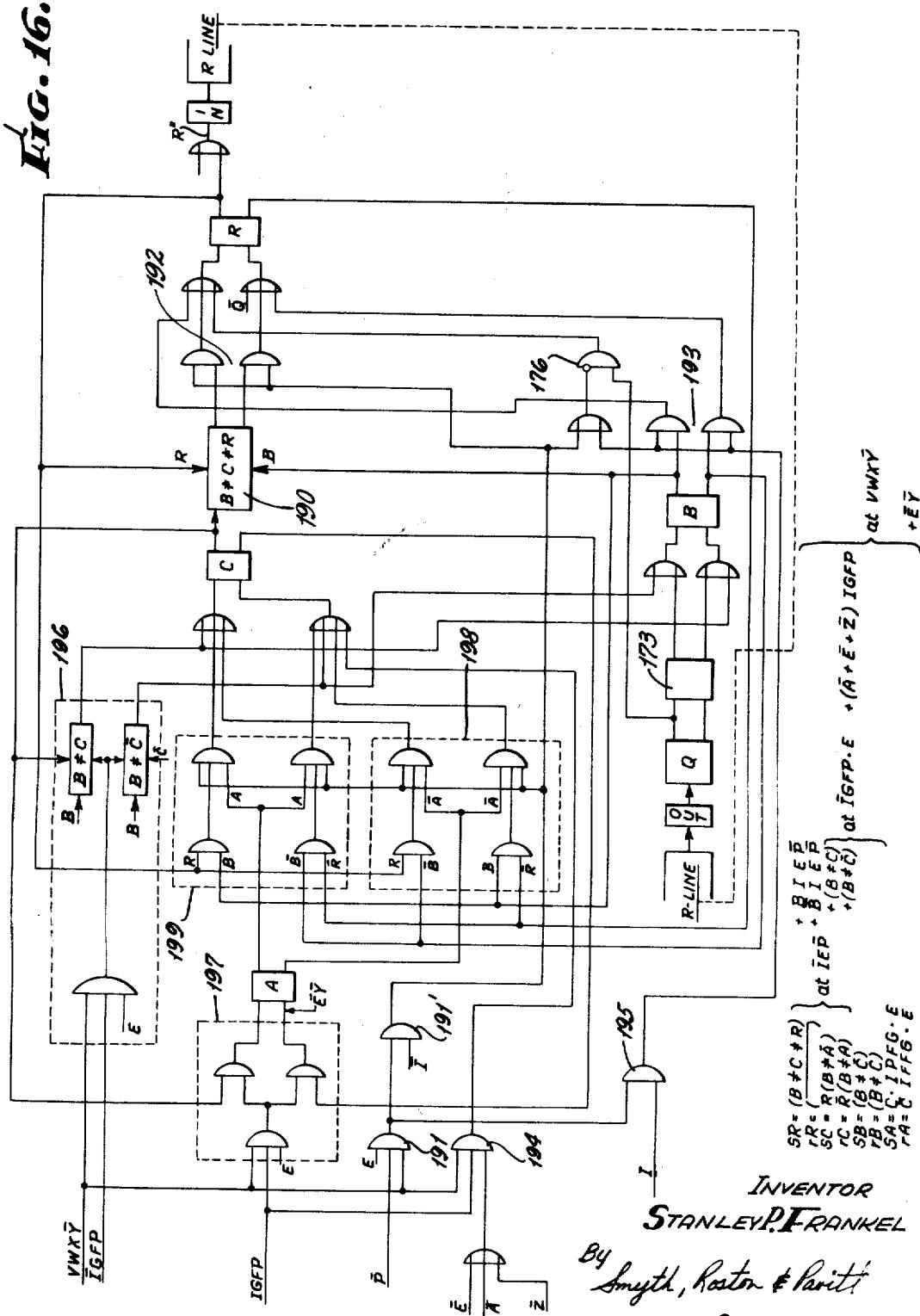

$$\left. \begin{array}{l} SR = (B \neq C * R) \\ R = \overline{R} \\ SC = R(B \neq \bar{A}) \\ RC = R(B \neq A) \\ SB = (B \neq C) \\ SA = C \cdot I PFG \cdot E \\ RA = C \cdot I FFG \cdot E \end{array} \right\} \text{at } \bar{I}GFP \quad \left. \begin{array}{l} B \cdot \bar{I}E \cdot \bar{P} \\ I \cdot \bar{I}E \cdot \bar{P} \\ + (B \neq C) \\ + (B \neq \bar{C}) \end{array} \right\} \text{at } \bar{I}GFP, E + (\bar{A} + \bar{E} + \bar{Z}) \cdot \bar{I}GFP \quad \left. \begin{array}{l} \text{at } VWXY \\ + E \bar{Y} \end{array} \right\}$$

INVENTOR

STANLEY P. FRANKEL

By

Smyth, Rector & Parritt

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

## GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 12

INVENTOR.

STANLEY P. FRANKEL

By Smyth, Roston & Pavitt

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 13

FIG. 18a.

INVENTOR.

STANLEY P. FRANKEL

By

Smyth, Roston & Pavitt

ATTORNEYS.

Oct. 1, 1968

S. P. FRANKEL

3,404,377

GENERAL PURPOSE DIGITAL COMPUTER

Filed Oct. 1, 1965

14 Sheets-Sheet 14

FIG. 21.

FIG. 22.

INVENTOR.

STANLEY P. FRANKEL

By

Smyth, Weston & Parritt

ATTORNEYS.

3,404,377

**GENERAL PURPOSE DIGITAL COMPUTER**

Stanley P. Frankel, 411 N. Martel,

Los Angeles, Calif. 90036

Filed Oct. 1, 1965, Ser. No. 491,953

63 Claims. (Cl. 340—172.5)

## ABSTRACT OF THE DISCLOSURE

A general purpose, stored program, digital computer is disclosed in which a recirculating register in form of a delay line is provided as principal storage unit and a short recirculating delay line serves for temporary storage for control information and data information and also as accumulator. Through interleaving of bits, the short circulating register can handle three different numbers simultaneously for multiplication and division. Control information in the short register is sequentially set into an order register. All information is stored in the principal memory register in interleaved format, and at times transferred to or from the short delay line. The principal register is addressed by counting cycles of the short delay line in between sequential couplings for data transfer between the long delay line (memory) and the short delay line (operating register). All data processing including arithmetic is handled on a serial-by-bit basis. Data are fed externally into the computer by asynchronous coupling of an external memory extension to the circulating operating register. Output operations are performed by timing the presentation of pulses which can be withdrawn externally.

The present invention relates to a general purpose, stored program digital computer.

The term general purpose computer has been applied to a variety of instruments having the following general characteristics. The instrument should have the ability to perform basic arithmetic operations on numbers presented in digital form. These operations usually include addition, subtraction, multiplication and division. The instrument includes a memory store which holds the numbers taking part in a calculation; the memory will also hold the result of such a calculation until the result is used either for additional calculations or externally. The memory, furthermore, must hold code signals representing the operational states of the instrument, whereby the ability of the instrument to perform these arithmetic operations is expressible in terms of its ability to respond to such codes and to conduct operations the results of which include such arithmetic operations.

The complexity of modern general purpose computers has many reasons. Among these reasons, operational speed, the quantity of data to be handled and mathematical complexity probably are the most dominant ones. As the quantity of data to be handled increases and as the total number of arithmetic processes to which such data are to be subjected increases, a proportionate increase in computing time can be prevented by an increase in the number of different codes to which the instrument can respond in a specific manner to perform well defined but restricted tasks.

Considering first the conceivable course of development in the opposite direction it should be remembered that any number handling can be reduced to the simple operation of subtraction. The simplest general purpose computer conceivable is thus an instrument handling all computations by way of subtractions coupled with result-dependent program branching, but naturally requiring an extremely long time for any arithmetic operation. A program of such a computer would require many different

subtracting steps involving many fixed numbers to be combined with input numbers by subtraction in many steps before any final result of, say, a multiplication can be obtained. Thus, the ultimate simplicity in "hardware" will necessarily require the largest amount of "software" and the largest number of processing steps before a final result is reached.

Basically, a more powerful computer obtains its sophistication from "short cuts," in that circuitry (hardware) is designed to respond to different operating codes each of which has the effect of combining predetermined groups of such subtracting operations into specific self-controlling machine operations of shorter duration; so that less "software" will be required. The introduction of multiplication and division operations are obvious "short cuts" of this type; others are shifting operations, large variations of conditioned program branching, and extensive communication systems between external data input and output devices. Hence, the trend here is to increase the amount of hardware so as to shorten the total number of operational steps required to obtain a desired result.

Here the general layout of a general purpose computer should be considered. It usually includes a memory section, holding all numbers as well as operational codes in what is usually called addressable locations. Operation codes and operand numbers are correlated by associating an operation code with a memory address which together form an instruction word, whereby the address defines the memory location holding the operand upon which such operation is performed. Such a system, in general, requires among others these two types of control systems: a first control system must respond to the address code in such an instruction and call on the thus specified memory address location to retrieve therefrom the operand upon which an operation has to be performed in accordance with the operation code portion of this instruction. The second control system must ensure that the system performs the various operational steps in a predetermined order, that is to say it must organize the sequence with which the instructions are executed. In many cases, this organization is performed by a program counter causing the sequential addressing of the memory locations which hold the instructions, or one can include the memory address code of the next instruction as part of the instruction word preceding. It will be explained below that the invention sets forth an entirely new way of such sequencing of operation codes.

A general purpose computer usually includes further a number of registers holding numbers, operation codes, and addresses for temporary storage including all data currently involved in specific operations performed by what is called the central processor. This latter circuit network basically includes all those operation code-responsive circuit networks which process the numbers currently held in one or more of these registers, whereby such processed numbers may be representative of true numbers or of addresses; often program branching is the result of computing one address out of others. The processing in general involves the shifting of data among the several registers as well as into or out of the memory, out of or into registers with or without data modification prior to, during, or subsequent to such transfer.

A high speed, highly powerful data processing system is extremely expensive and thus must be designed to perform a large variety of programs very rapidly, and either consecutively or on time sharing basis at different priority levels whereby the higher priority interrupts execution of lower priority programs to be resumed later. The reason for this requirement is predominantly one of economics so that, for example, a computer operating "on line" at

specific instants can perform unrelated operations in between. On the other hand, it has been found that many computing problems do not require the high speed of which electronic devices are capable. Hence a simplification of "hardware" and a corresponding increase in software may prove suitable as long as the total processing time due to extensive employment of software does not exceed tolerable limits.

To give a brief example, a general purpose computer programmed for use as a desk calculator with manual input keying and output printing is fast enough if, for example, the printing of the result begins, say, at the instant the operator takes his finger from the "go"-key, such as a key commanding the performance of a multiplication of numbers previously keyed into the device.

Time sharing of elements and careful consideration of inter-relationship between hardware and software can result in a reduction in hardware without increase in processing time. Here suitable selection of data format, the mode of storage of data and the sequencing of operation in a manner that permits synchronization with memory access play important roles. A distinction is to be made here between the time sharing of executing different programs and the time sharing of circuit elements. A very powerful computer must be equipped to operate on different programs on a time sharing basis permitting interruption of a program if a higher priority program demands execution. If this requirement can be dispensed with and if the time sharing of elements for executing a single stored program can be developed to the utmost, the cost reduction can be so extensive that the restriction to an exchangeable, but single, stored program does not render the computer uneconomical.

With the object of saving hardware, the computer in accordance with the present invention is so designed that an addressing control system for the general or main memory store can be dispensed with entirely, and a specific format of data representation, transfer and storage can be used to shorten and to simplify the execution of processing steps, while the sequencing of the processing steps themselves is used directly for memory addressing.

The computer in accordance with the preferred embodiment of the invention is comprised of the following features. The principal operating register is a recirculating delay line having a predetermined recirculating period. This delay line normally recirculates four data words each comprised of a similar plurality of bits. These four words circulate in pairs in that the bits of two words are interleaved or interlaced, and the other two words have their bits similarly interleaved and follow the first pair and vice versa in the course of the recirculation. The principal operations are performed by modifying one or more of the words as they emerge from or prior to re-entry into the delay line or by substituting entire new strings of bits.

For example, the bits of a word as they emerge from the delay line (as alternate bits, interleaved in another word) will normally be set again into the delay line for recirculation. Alternatively, these bits may be suppressed completely and replaced by another string of bits, or the bits as they emerge may be combined with another concurrently presented string of bits with the string of resulting bits being set into the delay line in substitution for the emerging bits. The additionally presented string of bits may, for example, be the respectively interleaved bits, or they may be drawn from a second delay line. In most instances, when bits of one word as they emerge are modified, the respectively interleaved bits are recirculated unmodified; however, in one type of operation two words as they emerge from the first, principal delay line are caused to exchange places prior to their re-entry to the delay line in which case either word is substituted for the other.

The second delay line mentioned above also permits recirculation and is the principal memory store; it has

a circulation period considerably in excess of that of the first, short, delay line but there is a definite number relation in the two circulating periods. Words also travel through the long delay line in pairs, with respectively interleaved bits. While, as mentioned above, the second delay line may at times furnish a word as a string of bits to be set into the first delay line, the reverse transfer of bits and words is also possible.

The various activities, involving principally the modification of recirculation of the first delay line, are controlled by codes held in a static register for periods commensurate with the time needed for executing the desired process. Such execution times are either half of the circulative period of the first, short, register or one full cycle thereof or an integral multiple of this cycle period. The description of the appended drawings is devoted basically to the activities as controlled by these various codes, also called order codes.

The static register receives order codes by temporary connection to the first day line. Only one particular word of this first delay line is involved; it is shifted through the static register with the effect that an order code previously held in the static register is exchanged for another order code which was previously part of this particular word. Hence, in this particular activity, one particular word as it emerges from the delay line is modified in that a part is taken out, other bits are substituted for the part that is taken out, and the remaining portion is changed in format.

This can be better understood if one considers this particular word as a mere assembly of code blocks. This assembly is enlarged by the code block currently held in the static register. These code blocks are sequentially exchanged by being shifted into the static register, one by one for a particular period of time, and then placed back into the first short delay line in a manner which does not interfere with the three other words which circulate in the short delay line. The duration of this changing of the order in the static register is half a circulation period of the short delay line and this bears a definite relationship in time to the execution period of any order. As a result of this relationship, the time from the placing of any order into the static register until the placement of the next order therein is always an integral multiple of the circulation period of the short delay line.

All code blocks that are shifted into the static register define order codes, but not all code blocks that are part of this particular code block assembly are order codes initially, because some of the code blocks represent numbers that are modified before they can be set into the static register to be interpreted as orders. The sequence of the code blocks as they circulate in the short register determines the sequence of their placement into the order register, and this in turn determines the sequence of the activities as controlled by the orders. The code of an order not only defines and controls specific activities but also the duration of such activities, i.e., the time span between the placement of such order code into the static register and its removal therefrom. For a certain class of orders this duration is additionally determined by a code block that is subject to modification before it is placed subsequently into the static register as an order.

As the second, long delay line is the main memory store, transfer of words between the two delay lines is frequently necessary. The selection (addressing) of any work in the main memory is exclusively controlled by pre-selecting (programming) the periods of execution of orders in between successive communications or word transfers between the two delay lines, and this timing, in turn, is controlled exclusively by selection of order codes other than communication order codes which require for execution as much time as is needed between different communication steps. Two basic aspects aid in this mode of addressing the memory as constituted by the second delay line; one is the fact that the length of the second delay line is not a fixed parameter in the system design, it may even

be made variable to be selected ultimately by the programmer for optimum results in programming. The other aspect is that there are order codes which, when in the static register, do not control any activity but simply cause unmodified recirculation of all words in the two delay lines. This permits the interpositioning of suitable waiting periods in between communication or transfer orders. However, a skillful programmer should be able to write a program, i.e., order code assemblies, in which he makes only a minimum use of these "wait orders."

The basic arithmetic operations which the machine is capable of performing are addition, subtraction, multiplication and division; described in detail below with reference to the appended drawing. However, as a general comment it should be mentioned that the chosen circulation format in either delay line, by interleaving the bits of pairs of words, permits multiplication and division operation to be carried out and completely exclusively with the aid of words held in the short delay line, without intervening data transfer between the two delay lines. Other orders permit selective rearrangement of bits or entire words as they are held in the short delay line.

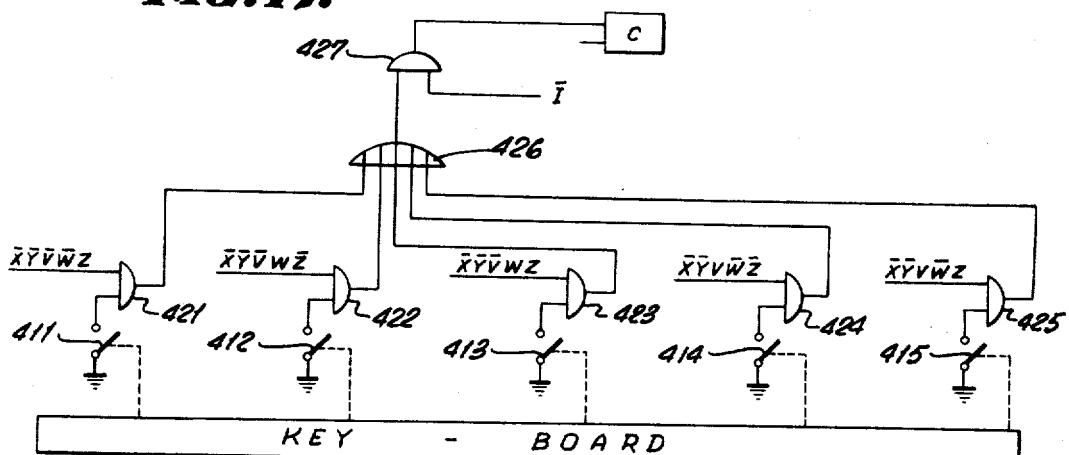

The inventive computer can communicate with external devices in various ways. A group of orders is set aside for this purpose so that this communication occurs as part of the sequence of processing steps as defined by the orders sequentially shifted into and out of the static register. Execution of these external communication orders causes either the testing of the state of an externally actuatable switch, or the delivery of a pulse to an external device to be used therein in combination with other such pulses as an expression of results obtained by the computer.

In a different mode of operation the static register is decoupled from the short delay line and phase code signals are simulated in the static register. Data is represented externally, in serial-by-bit format but asynchronously as far as the short delay line cycling is concerned. The phase code signals control the loading of such bits into the short delay line in synchronism with the short delay line recirculating period. According to a further aspect of the invention, as the short delay line is thus filled to capacity its content is then interpreted as four words, whereby one word is further interpreted as a control code assembly, the codes of which are sequentially loaded into the static register whenever interpretable as orders to cause the transfer of the three other words to the second, long, delay line (memory) at predeterminable instants of communication.

While the specification concludes with claims particularly pointing out and distinctly claiming the subject matter which is regarded as the invention, it is believed that the invention, the objects and features of the invention and further objects, features and advantages thereof will be better understood from the following description taken in connection with the accompanying drawing, in which:

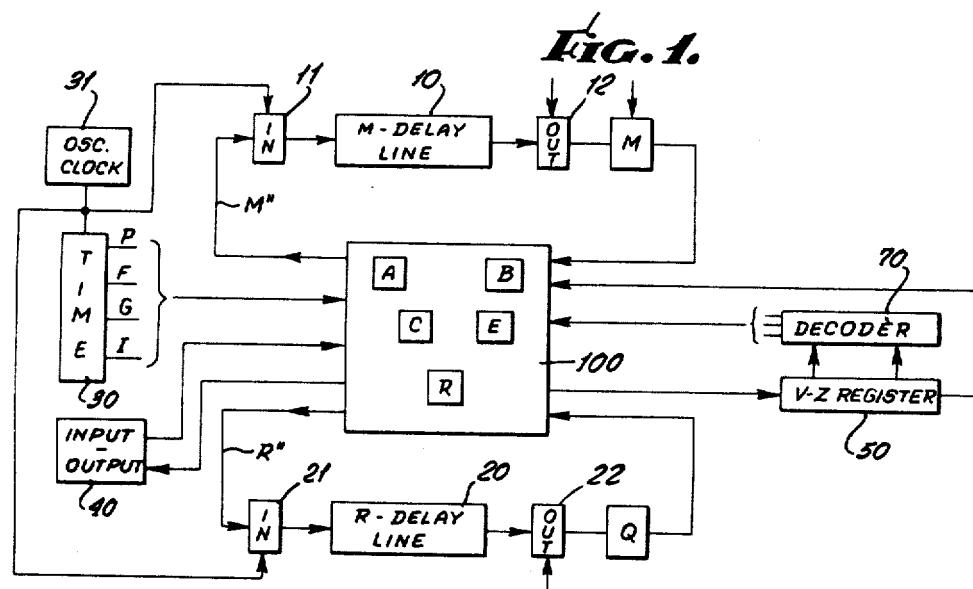

FIGURE 1 is a generalized schematic illustration of the principal components or building blocks of the computer in accordance with the present invention including a circulating memory register, a circulating operating register, a static register, connection logic, input-output devices and timing logic;

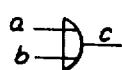

FIGURES 1a-1e illustrate logic symbols used in the following figures;

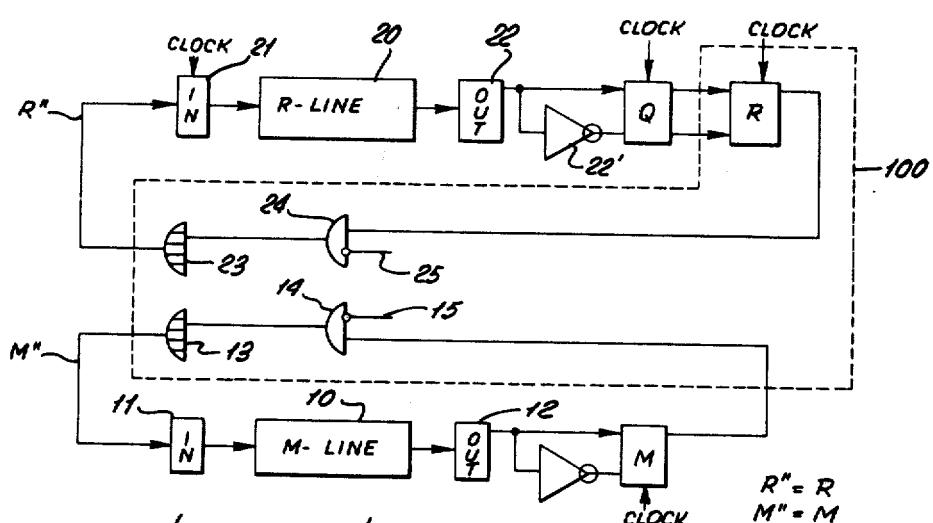

FIGURE 2 illustrates schematically the two circulating registers of the computer when decoupled;

FIGURE 3 illustrates schematically the timing circuit network used to distinguish between various phases of data circulation in the two circulating registers;

FIGURE 4 illustrates a timing diagram of various timing signals produced by the circuit shown in FIGURE 3;

FIGURE 5 illustrates schematically the circuit network used to control the commencement, duration and termination of setting orders into the static register, which orders in turn control the activities of the computer;

FIGURES 5a and 5b illustrate schematically the rearrangement of order codes as they circulate the operating register;

FIGURE 6 is a table illustrating the codes which control the activities of the computer;

FIGURE 7 illustrates schematically the circuit involved in the transfer of either one of two data words from the memory register to the operating register;

FIGURE 8 illustrates the circuit involved in the transfer of a data word from the operating register to the memory register;

FIGURE 9 illustrates schematically the circuit involved in the transfer of two data words between the two circulating registers in either direction of transfer;

FIGURE 10 illustrates schematically the circuit involved in the transfer of either one of two data words from the memory register to the operating register with the transfer involving data words which include order codes;

FIGURE 11 illustrates schematically the circuit involved to rearrange the order of words in the operating register;

FIGURE 11a is a table illustrating the rearrangement of individual data bits as carried out by the several components shown in FIGURE 11;

FIGURE 12 illustrates schematically the circuit involved in shifting (delaying) the bits of a word as it circulates in the operating register, by one bit position;

FIGURE 13 illustrates schematically the circuit involved in shifting (delaying) the bits of two words as they circulate in the operating register by a variable number of bit positions;

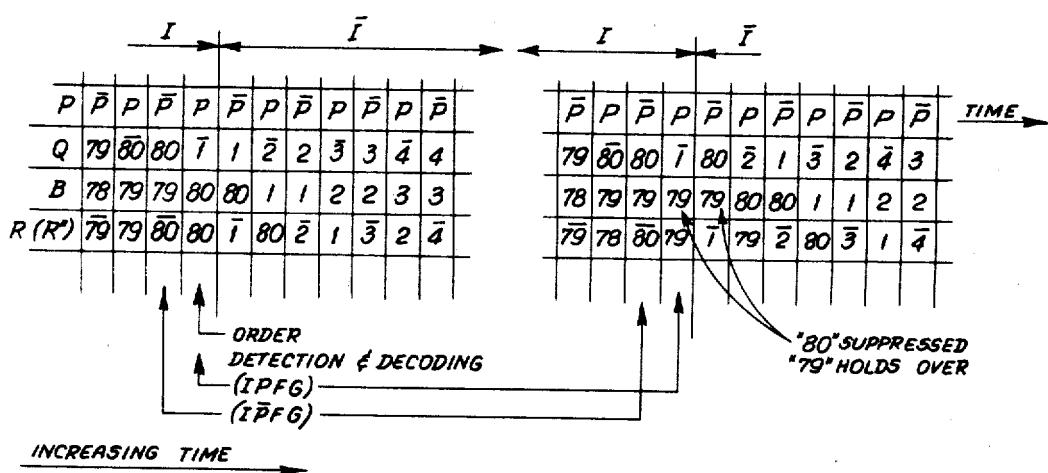

FIGURE 13a is a table identifying several individual bits as they are delayed by operation of the circuit shown in FIGURE 13;

FIGURE 14 illustrates schematically the circuit involved for serially adding or subtracting two numbers represented by data words concurrently presented by the two circulating registers, with the resulting word being set into the operating register;

FIGURE 15 illustrates schematically the circuit involved for multiplying two numbers represented by data words;

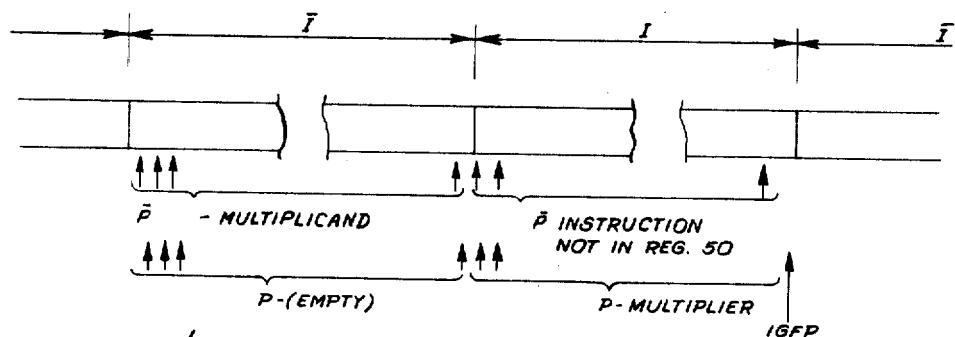

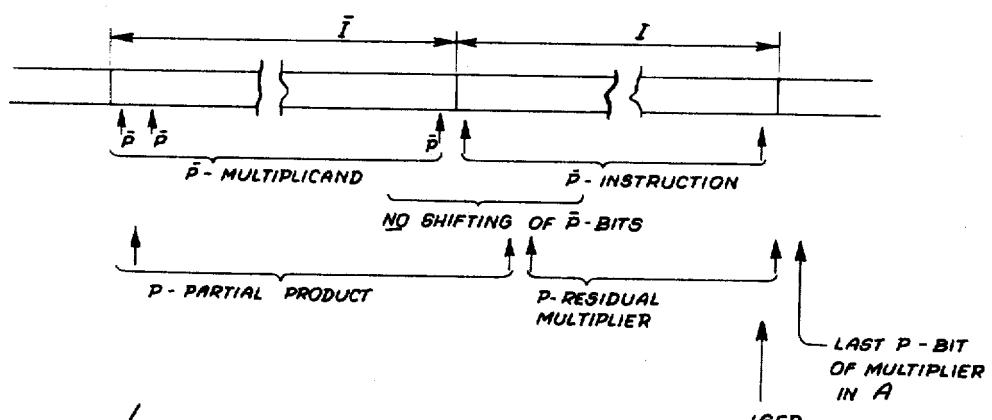

FIGURES 15a and 15b illustrate schematically the sequence of circulation of multiplier, multiplicand, the step-wise destruction of the multiplier and the build-up of the product in the operating register during multiplication;

FIGURE 16 illustrates schematically the circuit involved for carrying out a division;

FIGURE 17 illustrates schematically the circuit involved for transferring individual data bits presented externally, into the computer;

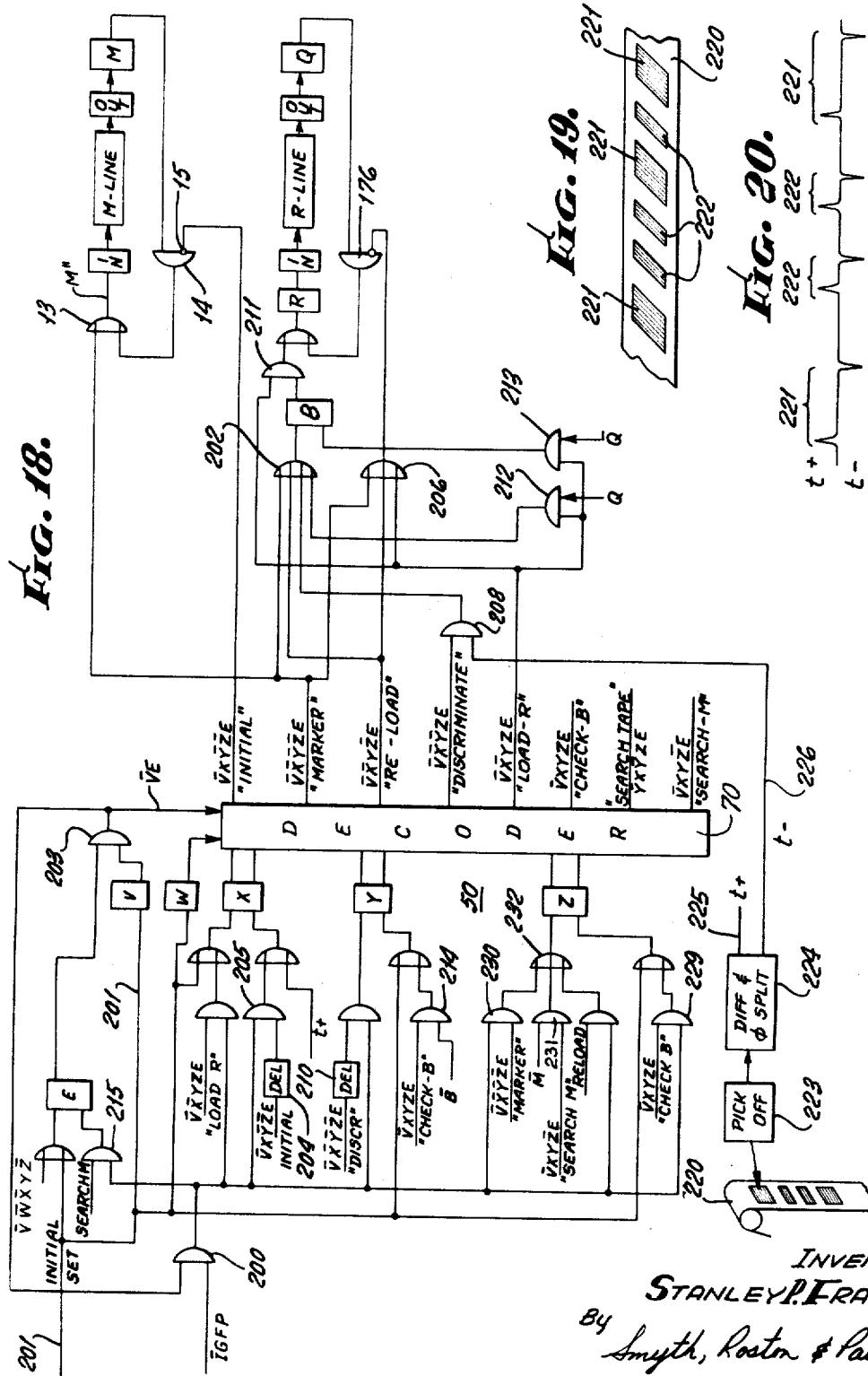

FIGURE 18 illustrates schematically the circuit involved for transferring sequentially a plurality of externally presented data bits into the operating register;

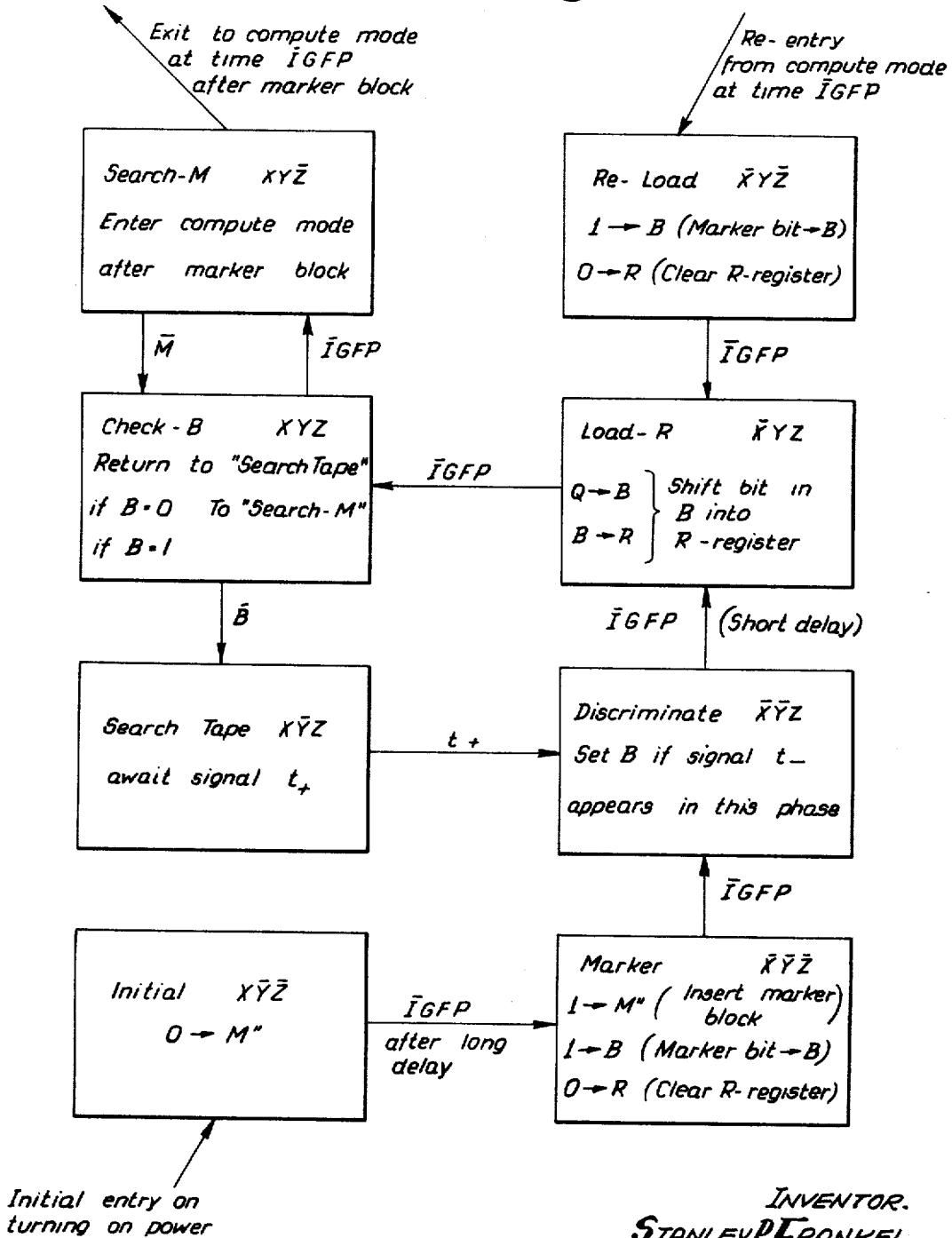

FIGURE 18a illustrates a flow chart of the operational phases as established in predetermined sequence in the circuit shown in FIGURE 18, to synchronize the external presentation of data bits and the circulation of the operating register;

FIGURE 19 illustrates in isometric view a portion of a record carrier used for external data presentation for use in the circuit shown in FIGURE 18;

FIGURE 20 illustrates a pulse sequence as they appear in the circuit shown in FIGURE 18;

FIGURE 21 illustrates schematically a circuit which can be used for presenting data bits by the computer for external use in an electric typewriter; and

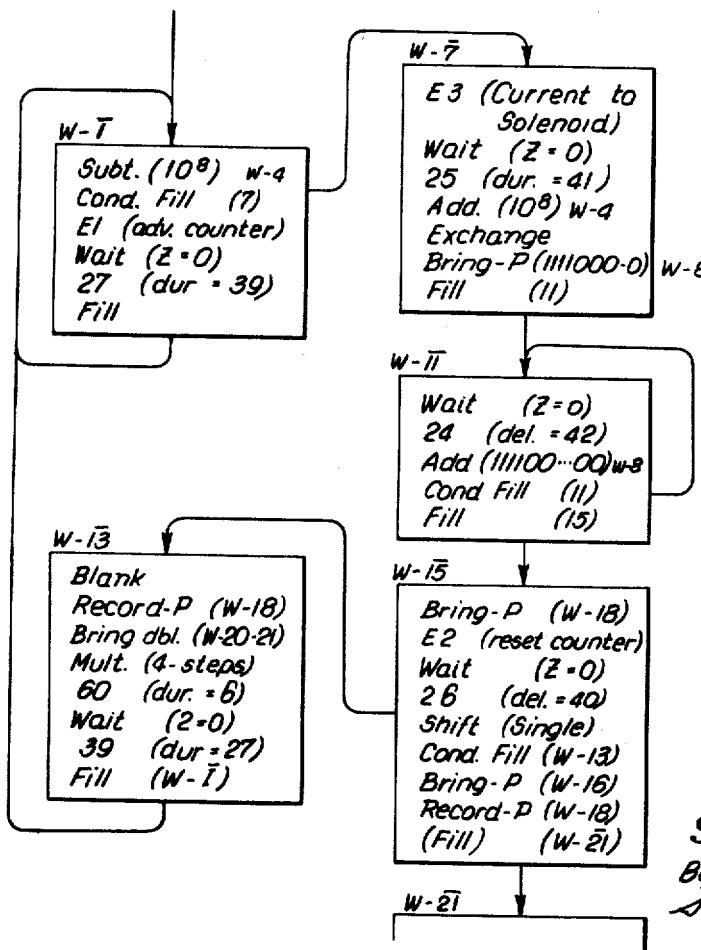

FIGURE 22 illustrates a flow chart and a subprogram for operating the typewriter of FIGURE 21.

#### GENERAL DESCRIPTION

FIGURE 1 illustrates schematically the principal elements employed in the design of the general purpose

computer which is the subject of the present invention. The basic elements thereof are two delay lines **10** and **20**, respectively, called M delay line and R delay line. Each one of these delay lines is comprised of substances or components which permit substantially unattenuated travelling of discrete signals at a rather high signal-to-noise ratio.

For example, each one of these delay lines may be comprised of a mechanical device which permits the transmission of vibration waves over its extension without material attenuation while maintaining a satisfactory signal-to-noise ratio. Sound waves, of course, are to be understood in the general sense since the frequencies employed are, as is well known, in the ultrasonic range. The basic frequency of the signals employed is, for example, 1 megacycle.

The M delay line **10** will also occasionally be called the long delay line and serves as principal storage unit or memory register. The R delay line **20** will be called the short delay line serving as a temporary storage and operating register. Their relationship as far as inherent time delay constants are concerned will be described by way of example more fully below. Each one of these delay lines has an input transducer, such as transducers **11** and **21**, coupled to one side of the delay lines **10** and **20** respectively, and being comprised of an electromechanical transducer to issue discrete "sound" pulses upon individual input energization. The respective output ends of the two delay lines are equipped with pickup or output transducers **12** and **22** respectively, to respond to the pulses which have travelled through the respective delay lines to produce electrical output pulses accordingly.

The specific configuration of these delay lines and their respective input and output transducers is not critical. Each of these delay lines may also be comprised of a magnetic recording medium such as a tape or a disc or a drum, cooperating with magnetic input and output transducers capable of magnetizing the magnetizable storage medium and of responding to magnetized surface portions of the medium when passing under it. Various types of delay lines are, for example, described by R. K. Richards, "Digital Computer Components and Circuits," D. Van Nostrand & Co., 1959, page 282 et seq.

The principal function of the computer is to couple inputs and outputs of the two delay lines together in an organized manner and/or to recirculate the contents of a delay line derived from its respective output transducer back into its respective input transducer with or without processing of the signal prior to recirculation thereof. In order to permit proper processing, the signals emerging from the delay lines and after having stimulated the respective output transducers (**12** or **22**) are set into flip-flops. A flip-flop Q has its input side always coupled to output transducer **22** of the R-line. Bit signals emerging from the respective lines can thus be distinguished in binary code as Q or  $\bar{Q}$  and M or  $\bar{M}$  signals.

The flip-flop M has in most instances but not always its output side coupled to the input transducer **11** for the M-delay line. Thus, the flip-flop M is the principal source for signals passing into the input line M" for the input transducer **11**.

The control logic **100** is basically comprised of five flip-flops, R, A, C, B and E.

The flip-flop R of control logic **100** is the principal but not the exclusive control flip-flop for the input transducer **21** of the R-delay line **20**. Thus, in many but not in all instances, the output of flip-flop R will determine the content for a line R" which is the input line for input transducer **21** of R-delay line **20**.

The flip-flop A in the control logic **100** is the principal control flip-flop for some arithmetic operations. Its principal function is the controlled modification of data circulating in the R-line, amounting to an arithmetic operation on such data.

The flip-flop C is a general control flip-flop which modifies arithmetic operations in accordance with "carry" and "borrow" procedures necessary for adding, subtracting, multiplying and dividing operations. Additionally, flip-flop C will signal "overflow" in case of arithmetic operations, and it is used for "sign" bit representation and program branching.

The flip-flop B has as its basic function the introduction of a fixed, limited delay of the shortest order possible within the computer of the present invention. Additionally, flip-flops B and C participate in the data communication between the computer and external devices.

The flip-flop E is the "execute order" control flip-flop, basically separating during operation of the computer periods of time in which a new "order" to be executed is searched or provided for, from periods of time during which certain "orders" are being executed. For the meaning of the word "order," see the discussion below; presently it suffices to state, that each "order" is a combination of bits which defines a unique operational state or sequence of logic operations within the computer. The control logic **100** includes, of course, a large number of logic "and" and "or" gates to be discussed in detail below.

As symbolic representation of the logic "and" and "or" functions, the symbols shown in FIGURES 1a, 1b and 1c are used. The implementation of these functions by means of gates is well known and does not require elaboration. FIGURE 1a represents the relation  $c=a+b$ , FIGURE 1b represents  $d=ab$ , FIGURE 1c represents  $e=\bar{a}b$ . More than two inputs may at times be used, if necessary. Occasionally, an inverter as shown in FIGURE 1d is used. As in many instances, the same signal is used at several different locations, amplification may be required. Amplifiers have been omitted in the several circuits, because they are well known in the art. As inverters often can be provided with a positive gain, the logic representation may advantageously be modified due to the well-known relations  $\bar{ab}=\bar{a}+\bar{b}$  and  $\bar{ab}=\bar{a}+\bar{b}$ . For example,  $ab=\bar{\bar{a}}+\bar{\bar{b}}$ , which means that input signals  $a$  and  $b$ , individually, as well as the output signal of an "or" gate are subjected to inversion permitting gain increase of the signal.

FIGURE 1e illustrates the symbolic representation and terms used for describing flip-flops. A flip-flop  $\theta$  when set provides at its set side output a true signal of like designation;  $\bar{\theta}$  is true when the flip-flop is reset, while set and reset input signals are designated respectively with  $s\theta$  and  $r\theta$ . All flip-flops are of the clocked input type changing states at a clock signal derived from a clock pulse source 31 (FIG. 1) provided there was a change from "false" to "true" or vice versa at its input sides. It should be mentioned that often the input side of a flip-flop ( $\theta_1$ ) is to be controlled from the output side of another flip-flop ( $\theta_2$ ) particularly if a bit held in the latter is to be transferred into the former. In this case,  $s\theta_1=\theta_2$  and  $r\theta_1=\bar{\theta}_2$ . It is apparent that these relations can be realized in different ways. For example, the output set side of flip-flop  $\theta_2$  can be connected directly to the input set side of flip-flop  $\theta_1$  and, additionally, via an inverter to the input reset side of flip-flop  $\theta_1$ . Alternatively set and reset output sides of flip-flop  $\theta_2$  can be connected respectively to set and reset input sides of flip-flop  $\theta_1$ . In the drawings these connections have often been simplified by a single line connection between flip-flops.

Next, there is provided a V-Z register **50** comprised of five flip-flops V, W, X, Y and Z which as far as the computer is concerned, is the only static register in contrast to the "dynamic" registers established by the delay lines M and R. Its principal function is to hold a "state" code for the duration of its execution. As "state" codes, there are available "order" codes which can circulate through the delay lines and can be assembled in sequences. Other types of "state" codes are "phases" set into the register **50** during loading of the computer from an external data source.

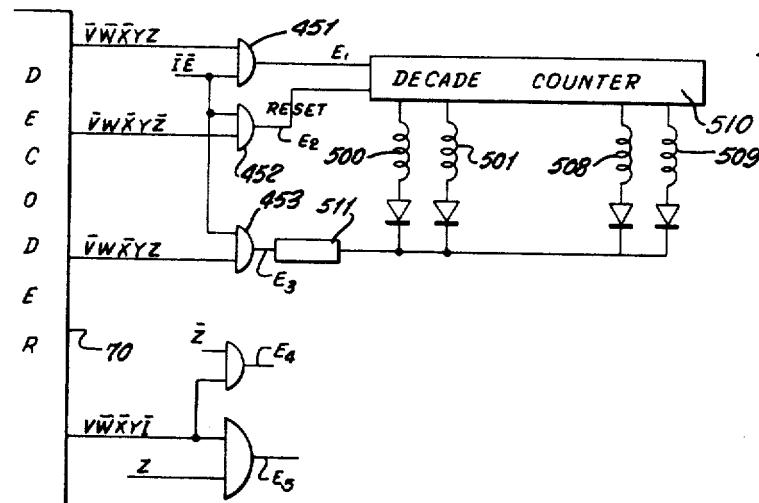

As will be described more fully in the chapter "Order Cycling," this register 50 is operated as a serial shift register, having its input side connected through the control logic 100 to the output side of the R-delay line, specifically through the flip-flops Q and R, while the output side of register 50 feeds back into the R-delay line, particularly into the line R'', also via the control logic 100. A state code decoder 70 is provided in the form of a plurality of "and" gates to produce individual output signals in response to the order or phase code presented at specific times by the V-Z register 50.

The entire computer is phased by the oscillator 31 serving as local clock and constituting the primary input source for a timing chain logic circuit 30 producing output timing signals, specifically the signals identified as P, F, G and I signal and their respective complements  $\bar{P}$ ,  $\bar{F}$ ,  $\bar{G}$  and  $\bar{I}$ , which will be described more fully below and particularly with reference to FIGURE 3. The computer is completed by an input-output device 40 which includes elements to be described more fully below with reference to FIGURES 18, 19, 20, 21 and 22. Basically, unit 40 is comprised of means permitting the feeding of data into the computer and deriving data from the computer.

#### IDLE STATE

As an initial orientation, there shall be described with reference to FIGURE 2 how the two delay lines 10 and 20 are connected to form recirculating registers, thereby defining the idle state of the computer; particularly the R-delay line and the M-delay line are mutually disconnected when no arithmetic operations are in progress. Thus, the output transducer 22 of the R-delay line feeds whatever output signal it receives into the flip-flop Q.

More specifically, if the output signal of transducer 22 is at any given instant regarded as a "true" signal, such signal is effective at the set side input for flip-flop Q and at the next following clock pulse flip-flop Q will be set (if it was already set, there will be no change). When the output signal of transducer 22 at any instant is a "false" signal, such signal is inverted (inverter 22') and applied as gating signal to the reset input side of flip-flop Q, and at the next following clock pulse flip-flop Q will be reset; if it was already reset, no change in state occurs. The mode of coupling transducer 22 to flip-flop Q is a permanent one and no change in it occurs during operation of the computer.

The two output sides of the flip-flop Q, i.e., the set side output and the reset side output, are respectively connected to the set and reset input sides of the flip-flop R. The alternative mode of connecting flip-flops Q and R for such bit transfer was described above. The flip-flop R has particularly its set side output connected to the input line R'' which control the input transducer 21.

The connecting path between flip-flop R, and the transducer input runs through a multiple "or" gate 23. This "or" gate has as many inputs as are needed to feed different signals into the input line R'' of transducer 21 of the R-delay line. Gate 23 is thus connected by one input terminal to the output side of the R flip-flop as stated. However, there is interposed a gate illustrated symbolically as an "and" gate 24 having an inhibitor input terminal 25 which will receive an inhibiting input whenever the recirculation of the data bits in the R-line is not desired. In other words, recirculation of data through the R-line is always established unless the inhibitor input 25 receives a signal for interrupting this normal circulation. If we call a data bit that is set into the R-delay line, R'' and if we call a data bit held in the flip-flop R with the same symbol R, then the normal circulation in the idle state is represented in the equation  $R''=R$ .

Whenever in the description below there are described situations in which the input transducer 21 of the R-delay line is not directly controlled from the content of flip-flop R, then it is to be understood that for each and every one of these situations an inhibiting input for the gating termi-

nal 25 of gate 24 is produced so as to block the path of normal data bit circulation as between the output of flip-flop R and input transducer 21. Conversely, it is understood that whenever an inhibiting input is not applied to terminal 25 and whenever gate 23 does not receive any other bit, the bit then in flip-flop R will be set into transducer 21. It should be noted that this general rule applies to periods of time of any length down to the period of the shortest order used here and introduced in the next chapter. Thus, the input for transducer 21 can be controlled that any two succeeding bits come from different sources; and this includes the recirculation of bits by opening gate 24 as well as inhibiting recirculation and substituting bits via alternative inputs of gate 23. It will be noted that the line R can be emptied simply by blocking gate 24 for the total delay period of the delay line without applying any bits to any of the input terminals of "or" gate 23.

In a similar manner, the M-delay line also recirculates its content during the idle state. For this purpose, the output transducer 12 of the M-delay line 10 feeds its signals to the M flip-flop. The connection between transducer 12 and flip-flop M is analogous to the input circuit of flip-flop Q. The set side output of flip-flop M connects through an "or" gate 13 and via an "and" gate 14 to the input line M'' of the M register or M delay line. Gate 14 is kept open whenever such recirculation is desired in an analogous manner. The equation  $M''=M$  describes normal circulation of bits in the M line, with M'' used to designate a bit set into line M'', and M is a bit held in flip-flop M.

In specific situations and in a manner similar to that outlined above with reference to the R-delay line, other input signals are applied to the "or" gate 13 for the purpose of introducing such input signals into the M-delay line. It will be understood that concurrently with such an alternative operation a signal is developed operating as an inhibiting input for the input terminal 15 of the "and" gate 14 so as to inhibit such normal circulation of signals back into the M-delay line after their emergence, to be replaced by the alternative signals.

#### TIMING CHAIN

Before going into details with regard to interpretation of the operation of the general purpose computer which is the object of the present invention, it is necessary to describe briefly FIGURE 3 which illustrates the production of the several timing signals which have been briefly introduced above, namely, the signals P, F, G and I. The diagram of FIGURE 4 shows the durations of and relationships among these signals.

The timing chain is basically controlled by the oscillator 31 which, for example, may be an astable multivibrator or a conventional tuning fork type oscillator or quartz crystal, tuned to a frequency, for example, of 1 megacycle. The output of this oscillator 31 is connected to a toggle flip-flop P. Thus, with each oscillation of clock 31, the flip-flop P changes in state. Accordingly, at sequential clock pulses from the clock 31, the flip-flop P produces a signal P or the signal  $\bar{P}$ . The "bit periods" in which the P flip-flop is in its on state are called P bit periods, while those time periods in which the P flip-flop is off are designated  $\bar{P}$ .

The oscillator 31 provides a signal which occurs at the end of each bit period, and which causes the changes of the state of flip-flop P. The distinction between P and  $\bar{P}$  bit periods is of vital importance for understanding the operation of the computer in accordance with the invention. In the following, a  $\bar{P}$ -bit period and the immediately succeeding P-bit period will also be called a P cycle.

The set side output of flip-flop P controls two flip-flops J and K interconnected in such a manner that the control of another flip-flop F causes division of the frequency of the train of P signals in the ratio of 1:5. FIGURE 4 illustrates the sequence of states of flip-flop F. Specifically, the signal F is true for one  $\bar{P}$  and the succeeding P bit

period. The flip-flop F is in the off state, i.e., the signal  $\bar{F}$  is true, for four succeeding  $\bar{P}$  bit periods and the respectively succeeding four P bit periods. In other words, the signal  $\bar{F}$  is true for eight bit periods or four P-cycles, and the signal F is true for the succeeding two bit periods or one P-cycle. The four P-cycles in which  $\bar{F}$  is true and the following one P-cycle in which F is true we call one F-cycle. The duration of an F-cycle is thus ten bit periods or five P-cycles.

The progression and states of these three flip-flops J, K and F can briefly be described as follows: K is set after J is on, J is turned off after K is on, K is turned off after J is off, F is turned on after both J and K are off, after F is on J is turned on and F is turned off. Of course, all of these operations are phased by the flip-flop P and clocked from clock 31.

The flip-flop F could be an asymmetrical, astable multivibrator which is driven by the falling edge of the flip-flop P output signals; such multivibrator has to have two different recovery times so that it spends four cycles of flip-flop P, for example, 8 microseconds, in its off state, while the other recovery time covers two bit periods in the on state. In this case, the flip-flops J, K could be omitted.

Next, there is provided a flip-flop I which is to be true for forty P-cycles, i.e., for altogether eighty bit periods which include forty P bit periods and forty interleaved  $\bar{P}$  bit periods. The flip-flop I is subsequently to be false for the same period of time so that there is a true division in frequency as between the P and I in the ratio of 1:80.

Each change of state of flip-flop I takes place at the end of an F-cycle; i.e., at the end of a bit period in which both P and F are true. In the embodiment of the instant invention described here, the eighty bit periods during which I is true, or during which I is true, constitute eight F-cycles. This choice of the number of F-cycles over which flip-flop I maintains either state is a plausible and convenient one, but it is not essential to the practice of the invention. Other values for this number, either larger than or smaller than eight, may prove more convenient for particular uses. Nevertheless, for the sake of definiteness and simplicity of discussion, only the value eight will be considered here.

This frequency division is carried out by means of three flip-flops H, H', and H'' interconnected and connected to the flip-flops P and F in such a manner that they turn the flip-flop I on at a falling edge of a particular P signal and then the flip-flop I is turned off at the respectively succeeding fortieth P pulse. FIGURE 4 illustrates one complete cycle for the flip-flop I, covering altogether eighty P-cycles or one hundred and sixty bit periods. The flip-flops H, H' and H'', in addition are used to define the signal G. G is true when all of the flip-flops H, H' and H'' are in the on state while the signal  $\bar{G}$  is true as long as at least one of the flip-flops H, H' and H'' is turned off.

Looking at FIGURE 4, it can be seen that the signal G is thus true for five P-cycles, specifically for the last five P-cycles of an I or of an  $\bar{I}$  time period.

FIGURE 3 illustrates the realization of the equations written next to the figure whereby conventional symbols for logic "and" or "or" functions have been used which do not require detailed description. The circuit of FIGURE 3 is logically identical with the content of table next to it, and it is apparent to one skilled in the art in what way these equations can be implemented. At this point, it should be mentioned that whenever in the following description signals such as I,  $\bar{I}$ , P and  $\bar{P}$ , G and  $\bar{G}$ , and F and  $\bar{F}$  are needed, it will be understood that the signals can be derived from the timing chain shown in FIGURE 3, particularly from the appropriate and corresponding output terminals of the flip-flops P, F, I, and of the gate assembly G and  $\bar{G}$ .

After having explained the salient periods of time involved and to be employed in the present invention, it shall be explained in the following in what way data bit signals are grouped and organized for meaningful use. For this purpose, the following definitions are helpful and will be used. The terms "bit period" (determined by the output of oscillator 31), "P-cycle" (two bit periods) and "F-cycle" (ten bit periods) were introduced above. The bit periods are distinguished as P-bit periods and  $\bar{P}$  bit periods.

The duration of each of the signals I and  $\bar{I}$ , these being of equal length is called a word period. Thus, each word period includes eighty bit periods and forty P-cycles. Restated, each word period includes forty P-bit periods, and forty respectively interleaved  $\bar{P}$ -bit periods. It is thus meaningful to distinguish among IP,  $\bar{I}P$ ,  $\bar{I}\bar{P}$ , and  $\bar{P}\bar{P}$ -bit periods, there are forty bit periods in each such group of bit periods; each group falling within either an I or an  $\bar{I}$  word period.

The period of circulation of the R-line is called an "R-cycle." It is the period of time which elapses from inserting a bit into line R" (transducer 21) until the same bit is again held in flip-flop R, by way of normal circulation as shown in FIGURE 2. The total duration of the R-cycle is exactly two word periods, i.e., 160 bit periods. Since at any instant, the flip-flops Q and R each hold one bit, the R-delay line together with its associated circuits has a delay period of 158 bit periods.

The period of time for circulating any one bit in the M-line when connected for recirculation as shown in FIGURE 2 is called an "M-cycle." For reasons discussed below, one M-cycle is an integral but odd number of word periods. The most convenient number of word periods in one M-cycle is not critical and may differ from one application to another. Moreover, the length of the delay line M may be adjustable. For a given clock, the length of the M-line; i.e., the duration of an M-cycle, basically determines the operational speed of the computer. On the other hand, this length determines the storage capacity of the M-line. Thus, selection of this length will result primarily as a compromise between speed and storage capacity, whereby the length of a program determines the minimum storage capacity. For definiteness and simplicity in the present description, one M-cycle is taken to be 22½ R-cycles, which is equal to forty-five word periods or 3,600 bit periods, or 1,800 P-cycles, or 360 F-cycles.

Up to this point, only periods of time have been defined. Next, it shall be described how these periods of time: bit period, P-cycle, word period, R-cycle and M-cycle are used to organize the flow of data bits. Data handled and processed by this digital computer are organized in "words" with each word being comprised of forty bits. This number is not critical per se but is convenient, and it is strictly related to the fact that according to the choice given above, each word period has forty P-bit periods and forty  $\bar{P}$ -bit periods.

It is now stipulated that at any location such as input and output sides of the delay lines, one data bit is present per bit period. Thus, 3,600 bits are circulated in the M register and 160 bits circulate in the R register. Forty bits are serially presented at any location at or in the delay lines during, for example, the  $\bar{P}$ -bit periods of an I word period while an additional forty bits are presented during the same I word period in the interleaved P-bit periods thereof. It follows that it is thus possible to select a specific location and to stipulate that all bits presented at that location during one word period as defined by an I or an  $\bar{I}$  timing signal pertain to two distinct words. The bits of one word appear at that location during the P-bit periods, the bits of the other word appear thereat during the  $\bar{P}$ -bit periods.

Thus, data is organized in that at a specific and selected location all forty bits presented thereat during forty IP-bit periods pertain to one word, while bits presented interleaved during the  $\bar{P}$  bit periods of the same I word period pertain to a second word. The 80 bits present at that location in a word period are to be called  $\bar{P}$  bits and P bits depending on the time of presentation. The 40  $\bar{P}$  bits presented thereat during a word period I are collectively called an  $\bar{IP}$  word, and the 40 P bits interleaved in the  $\bar{P}$  bits constitute the IP word. During an I word period, the location presents forty P bits, defining an  $\bar{IP}$  word, and forty interleaved  $\bar{P}$  bits defining an IP word.

It will now be necessary to find at least one specific location which permits a meaningful correlation between data bits and bit periods in such a manner that any such forty bits defined at that location as constituting one data word can be traced subsequently throughout the computer. More specifically, once a train of forty bits has been identified at the selected location, it must be possible to detect or retrieve these bits subsequently at the same or other locations in terms of bit-appearances at P,  $\bar{P}$ , I and  $\bar{I}$  time periods. In view of the employment of delay lines and of the serial presentation of data bits at various locations for purposes of processing, it must be possible to control any processing of the bits of any word by phasing and timing signals I,  $\bar{I}$ , P and  $\bar{P}$  regardless of the time that has elapsed since the initial identification of any word at that reference point.

It is apparent that the selection of R and M cycles as integral multiples of word periods greatly facilitates the selection of this reference point. As one such location or reference point, the input line  $R''$  is selected, and all bits presented to line  $R''$  during the time periods identifiable in terms of P,  $\bar{P}$ , I and  $\bar{I}$  are identified in like terms. That this selection is meaningful is not self-evident, but has to be developed by considering the results. Particularly, it has to be determined that any data word so identified can readily be traced unambiguously throughout the computer.

Reference is thus made first to FIGURE 2 showing normal circulation. By using the definition above, it appears that the flip-flop R controls the content of what is fed to line  $R''$  during normal circulation. For example, a bit presented during the 10th P-bit period of an I word period is the 10th P bit of an IP word. Considering now that the R register has a recirculation time of 80 P-cycles (or 160 bit periods), it is apparent that during the 10th P-bit period of the next I word period the same bit is stored in the R flip-flop and applied to line  $R''$ . Of course, the same consideration will be true for any bit circulating in the R-register. Thus, as far as the content of the R register is concerned, this correlation of bit periods and data bits is meaningful, since it reproduces the same bit during the same bit periods at the periodic R cycle rate which is precisely the I-I oscillating rate. Hence, a word held in flip-flop R is readily traceable regardless of the duration of circulation.

In the following, it will thus be necessary to observe carefully these distinctions: There are time periods, in general identified by timing signals IP,  $\bar{IP}$ , etc.; and there are bits such as P-bits or  $\bar{P}$  bits, etc., deriving their designation solely from the time of actual or possible presentation at line  $R''$ . Whenever we speak of a P-bit held, for example, in flip-flop Q, or travelling in the R-delay line, etc., this always will mean that such a bit will normally be presented in line  $R''$  during a P-bit period.

In view of the fact that bits are often modified before being recirculated (doing nothing but recirculating is, of course, senseless), the following points though possibly apparent are emphasized.

Any bit presented in the  $R''$  line will be set into flip-flop Q after 159 bit periods. Thus, a specific P bit, for example, will be in flip-flop Q during the  $\bar{P}$  bit period which precedes the P bit period during which, in the case of normal

circulation, said bit would appear in flip-flop R and line  $R''$ . Thus, any bit once set into the R-delay line will reappear in flip-flop Q 159 bit periods later regardless of whether or not it is recirculated subsequently. This is important for bit and word tracing particularly because any data modification will occur either as bits are set into input line  $R''$  or as they are drawn from flip-flop Q.

The primary storage device of the computer is the M register. The word definitions given above can be transferred here by stipulating that in case a word is to be transferred from the M register to the R register, flip-flop M will be coupled to line  $R''$  so that the word then flowing into the line  $R''$  is an IP or an  $\bar{IP}$ , etc. word depending upon the time of presentation of such bits at line  $R''$ . Conversely forty P bits, for example, presented during an I word period and at a time when flip-flops Q and R are connected to each other as shown in FIGURE 2, can be transferred into the M' line as an IP word.

As was mentioned above, an M-cycle has an odd number of word periods, while an R-cycle has an even number of word periods, namely two. This means that any word which at any instant emerges from the M-register/M flip-flop during, for example, an I-word period, will after a complete M-cycle appear serially in flip-flop M during an  $\bar{I}$ -word period, and after another M-cycle it will appear again as an IP- or  $\bar{IP}$ -word. Also, a word set into the M line during an I-word period, will emerge from the M line after one M-cycle during an  $\bar{I}$ -word period. If recirculated, the word will again emerge during an I-word period after another M-cycle.

This change of word type does not break the association of data bits and bit periods, but it is simply being stated that an IP- or  $\bar{IP}$ -word is presented as an  $\bar{IP}$ - or  $\bar{IP}$ -word after one M-cycle. This change is not only not confusing but convenient since it permits any word in the M-register to be transferred as an I or as an  $\bar{I}$  word to the R-register if the programmer so desired. Thus, tracing of a word as it circulates through the M-register is not impeded. As will be described below, waiting periods can easily be established, permitting presentation of any word by the M-register as an I or an  $\bar{I}$  word.

No change in word type occurs during circulation in the R-register, and it remains meaningful to speak here of IP,  $\bar{IP}$ - and/or  $\bar{IP}$ - $\bar{IP}$ -words for as long as any such word remains in the R-register. Any word passing at the same time periods through the M-flip-flop will be designated in the like manner regardless of the fact that after one M-cycle there will be a change.

Looking at the timing diagram shown in FIGURE 4, it can be seen that, for example, during an I-word period the last bit period is a P-bit period, so that the last bit presented in flip-flop R during the I-word period is the last bit of IP word. This is established specifically by a coincident signal IGFP defining in time presentation of this last bit of the IP word in flip-flop R. This bit (a P-bit) was in the Q flip-flop during the preceding  $\bar{P}$ -bit period. The last bit of the IP word is in flip-flop R during the time IGFP, provided there is normal circulation. The same bit was in flip-flop Q during the preceding  $\bar{P}$ -bit period. The first bit held in flip-flop R during the  $\bar{I}$  period is the first bit of the  $\bar{IP}$  word, and the immediately succeeding bit is the first bit of the  $\bar{IP}$  word.

#### WORD FORMAT

It is convenient to think of the words used as divided into two classes: number-words and instruction-words. Those words which are intended for use in arithmetic processes and have some numerical significance are number-words; those intended to be set into the instruction register are instruction words. This is not an inflexible distinction, since here—as in other stored program digital computers—it is possible and often convenient to use arithmetic operations to modify a word which is later

used as an instruction word. This distinction, moreover, has to do only with the intention of the programmer and not with any "physical" difference. We consider here only numbers which are intended for use in quite simple ways.

A number word may be used to present a positive integer as a simple integral binary expansion. The least significant bit has the "position value" of unity, the second least significant has the position value 2, the next 4, etc. Finally, the most significant bit has the position  $2^{39}$ . Any integer from zero up to  $2^{40}-1$  may be represented in this way. It may be noted that  $2^{40}$  is slightly (about 10%) larger than  $10^{12}$ , thus the 40 bits of a word are sufficient to represent all of the integers which could be written in the decimal system with twelve digits, or fewer. A number word of this kind will be written as a series of 40 binary digits (bits), each of which may have either of the values 0 or 1. As an example, the number one-thousand ( $10^3$ ) takes the form:

$$10^3 \text{ (dec.)} = 00000 \ 00000 \ 00000 \ 00000 \ 00000 \ 00000$$

1111 01000 20

(successive groups of five bits are separated by a space for ease of reading). The most significant bit has been written on the left, the least significant bit on the right, in agreement with the customary way of writing numbers in the decimal system. In agreement with that custom, we will speak of the leftmost (most significant) bit as the "first" bit of the number, the rightmost (least significant) bit as the "last." It should be noted, however, that the actual order of circulation of the bits of a word is from least to most significant.

If it were desired to emphasize the fact that a number word represents an integer, it might be written with a "binary point" to the right of the least significant bit. It should be remembered, however, that the binary point does not represent any physical occurrence within the computer; it is merely a written reminder of the interpretation which the programmer has chosen to place on that number.

A number-word may also be used to represent a positive proper fraction; that is a number smaller than unity. It is then convenient to assign the position-value  $\frac{1}{2}$  to the leftmost (most significant) bit (first time),  $\frac{1}{4}$  to the second bit from the left, etc., to the last (least significant) bit with the position value  $2^{-40}$ . If it is desired to emphasize the fact that this interpretation is being placed on the number, a binary point may be placed to the left of the first bit, as in the following example:

$$10^{-1} = .00011 \ 00110 \ 01100 \ 11001 \ 10011 \ 00110 \ 01100 \ 11001 \ 50$$

Many other positions may be assigned to the binary point, and other interpretations of a number word may be used, as will be discussed further in connection with the arithmetic operation.

Before proceeding with the description of the invention, it is necessary to describe why (1) the instant computer can be regarded as falling in the class of general purpose computers and (2) what is meant by an "instruction" word. Without attempting to give any general definition of the term "general purpose computer," the present computer is of the type that requires storing of a program. The program is a sequence or group of code signals externally compiled and suitably fed into and stored in the computer. Each code signal causes the computer to perform a specific operation such as shifting of data (number words) into or out of a specific register or adding the content of one register to another register, etc.

Computers with core memories often have a portion of the core memory used for storing this program, i.e., this plurality of codes. The program in the computer is usually presented by a plurality of what are called "instruction words." Each instruction word consists of a plurality of bits and basically comprises two portions. One is the instruction or operation code, i.e., the code mentioned above

and which when detected and decoded enables the computer to perform a specific task well defined by the code. The other portion of the instruction word is often the code for the address location in the core memory which contains the operand upon which the operation as defined by the respectively associated instruction or operation code is to be performed. Upon executing the program, the computer with such core memory executes these instructions in a particular sequence.

For the instant computer, the "instruction" word is used in the different manner. The instruction word can be considered as consisting of eight groups of five bits each. Such a five-bit group will in the following be called "syllable."