**dietz 621**

**Adressierungsmodul

Hardwarebeschreibung 621/X3**

**ANMERKUNG:**

Der Nachdruck, auch auszugsweise, ist nur mit Genehmigung der Firma DIETZ-Computer-Systeme gestattet.

Diese Beschreibung hat lediglich Informationscharakter, Gewährleistungsansprüche daraus sind ausgeschlossen.

Die Sachverhalte können jederzeit ohne Ankündigung geändert werden. Diese Beschreibung ist nicht Gegenstand eines Vertrages.

# **dietz 621**

## **Adressierungsmodul Hardwarebeschreibung 621/X3**

Heinrich Dietz

Solinger Straße 9

4330 Mülheim-Ruhr

Tel.: (0208) 44 34-1

Telex 856770

**DIETZ Computer

SYSTEME**

1-8007-01-121 Schutzgebühr DM 7,50

|        |                                                  |    |

|--------|--------------------------------------------------|----|

| 1.     | Allgemeines                                      | 3  |

| 1.1.   | Einsatzzweck                                     | 3  |

| 1.2.   | Aufbau                                           | 3  |

| 1.3.   | Funktionsbeschreibung                            | 3  |

| 1.3.1. | Adreßtransformation                              | 3  |

| 1.3.2. | Adreßbereiche                                    | 5  |

| 1.3.3. | Adressierungsarten und Modus-Umschaltung         | 7  |

| 1.3.4. | Speicherschutz                                   | 11 |

| 1.3.5. | Fehlerunterbrechungen                            | 11 |

| 2.     | Schnittstelle Software                           | 12 |

| 2.1.   | Adressen und Registerverwendung                  | 12 |

| 2.1.1. | Kachelbasisregister                              | 12 |

| 2.1.2. | AM-Statusregister                                | 13 |

| 2.2.   | Besonderheiten zur Schnittstelle                 | 16 |

| 2.2.1. | Systemzustand nach Nullstellung                  | 16 |

| 2.2.2. | Ein- und Ausschalten des Adressierungsmoduls     | 16 |

| 2.2.3. | Pufferungen von Registern bei Netzausfall        | 16 |

| 2.3.   | Verhalten im Fehlerfall                          | 17 |

| 2.3.1. | Falsche Registermarkierung                       | 17 |

| 2.3.2. | Speicherschutzkachel angesprochen                | 17 |

| 2.3.3. | Befehle der Gruppe '3X                           | 17 |

| 2.3.4. | Fehlerhafte Aktivierung des Arithmetikprozessors | 18 |

| 2.3.5. | Zeitverhalten der Fehlermeldungen                | 18 |

## **Einleitung**

---

Die vorliegende Beschreibung ist eine Ergänzung der Dokumentation "Minicomputer-Familie X".

Der Minicomputer 621/X3 weist dieselben strukturellen Merkmale der Computerfamilie 621 auf. Der Aufbau ist identisch mit dem der Zentraleinheit 621/X2. Im 621/X3 wird ein geänderter Mechanismus zur Erweiterung des Adreßraums auf 1 MByte benutzt. Das Adressierungsmodul AM, das den im 621/X2 benutzten Memory Manager PMM ersetzt, ermöglicht es, jedem Benutzer mehr Adreßraum zur Verfügung zu stellen.

Die wichtigsten Merkmale des X3 sind:

- Maximaler Adreßraum 1024 KByte.

- Jedem Benutzer steht ein Speicherbereich von max. 128 KB zur Verfügung. 64 KB Programm- und 64 KB Datenbereich.

- Register, Peripherieadressen und Systemprogramme liegen im physikalischen Adreßraum von '00000-0FFF; im folgenden Kern-Bereich K genannt.

- Die CPU erlaubt eine lineare Adressierung von 64 KByte. Die Anzahl der Register pro Ebene ist auf 128 Byte festgelegt.

- Increment-Branch-Befehle mit vorgeschaltetem DO-Befehl berücksichtigen Überträge.

- Zur Erweiterung der Adressierungsmöglichkeiten für die Benutzerdaten und Programmberäiche wird das höchstwertige Bit der 8 bit Registeradressen benutzt.

- Die Benutzerberäiche sind in je 16 Kacheln zu 4 KByte unterteilt. In einer Tabelle sind die Anfangsadressen der Kacheln, Kachelbasisadressen, abgelegt.

- Ein Speicherschutzkonzept verhindert Zugriffe auf Speicherbereiche anderer Benutzer.

- Fehlerzustände der CPU führen zur Programmunterbrechung (Trap-Funktionen).

- Spezifikationen:

Hauptspeicher: '04000-'FFFFF

POOL: '00000-'007FF 2 KByte

Kachelbasisreg.: '00800-'009FF 512 Byte

Statusreg. AM: '00A00 und '00A01

Uhradresse: '01FFF

Bootstrap ROM: 1 KByte

Urstart nach Einschalten der Zentraleinheit

oder nach Netzwiederkehr: Ebene der höchsten

Priorität Ebene '15

Rückmeldeebenen der Operatorkonsole und der

Lochstreifenperipherie auf Ebene 13

Die folgenden Kapitel beschreiben die Funktion und

die Hardware des Adressierungsmoduls AM.

Informationen über Aufbau, Bedienung, Struktur und

Ausführungszeiten der Maschinenbefehle können der

"Systembeschreibung Hardware - Minicomputerfamilie X"

entnommen werden.

1. Allgemeines

---

1.1. Einsatzzweck

---

Das Adressierungsmodul, im folgenden AM genannt, dient zur Adreßraumerweiterung des 621/X3 auf 1 MByte.

1.2. Aufbau

---

Das Adressierungsmodul ist auf einer Leiterplatte im DIETZ KS-Format (392x299 mm) aufgebaut. Steckplatz in der Zentraleinheit ist der Platz PMM. Voraussetzung für den Einbau des AM sind: CPU vom Typ 690660, IOB 690665 und Busdurchschaltung 690614. Der AM enthält den bipolaren Register-Pool und die Logik zur Adreßtransformation.

1.3. Funktionsbeschreibung

---

1.3.1. Adreßtransformation

---

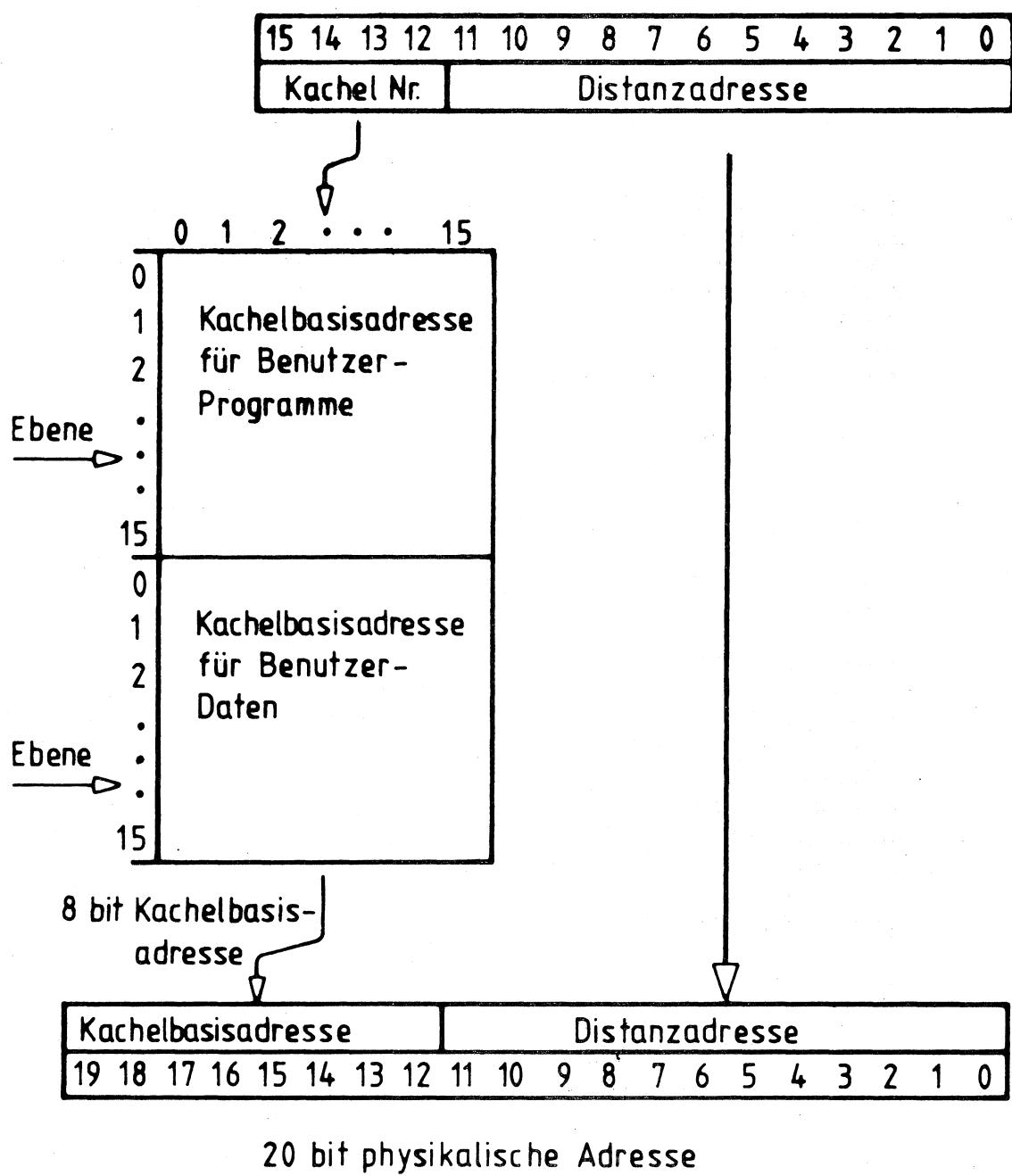

Die Umsetzung der virtuellen 16 bit-Adresse in eine physikalische 20 bit-Adresse ist aus Abb. 1 ersichtlich. Die virtuelle Adresse wird in eine 12 bit Distanzadresse und in eine 4 bit Kachelnummer aufgeteilt. Die Distanzadresse adressiert eine Speicherzelle in einer 4 KByte Kachel. Aus der Kachelnummer und der laufenden Ebene wird über eine Tabelle eine 8 bit Kachelbasisadresse generiert. Die Tabelle der Kachelbasisadressen, Kachelbasisregister genannt, sind per Software setz- und abfragbar.

Aus der Kachelbasisadresse und der Distanzadresse wird die physikalische 20 bit Adresse zusammengesetzt.

Abb. 1 Adreßtransformation 621/X3

**virtuelle Adresse ( CPU-Adresse 16 bit )**

Für jede Ebene sind in der Tabelle je 16 Kachelbasisregister für Programm und Daten vorhanden. Bei einer Kachelgröße von 4 KByte kann so jeder Ebene ein Adressraum von je maximal 64 KByte Daten- und Programmbereich im Hauptspeicher zugeordnet werden.

### 1.3.2. Adressbereiche

---

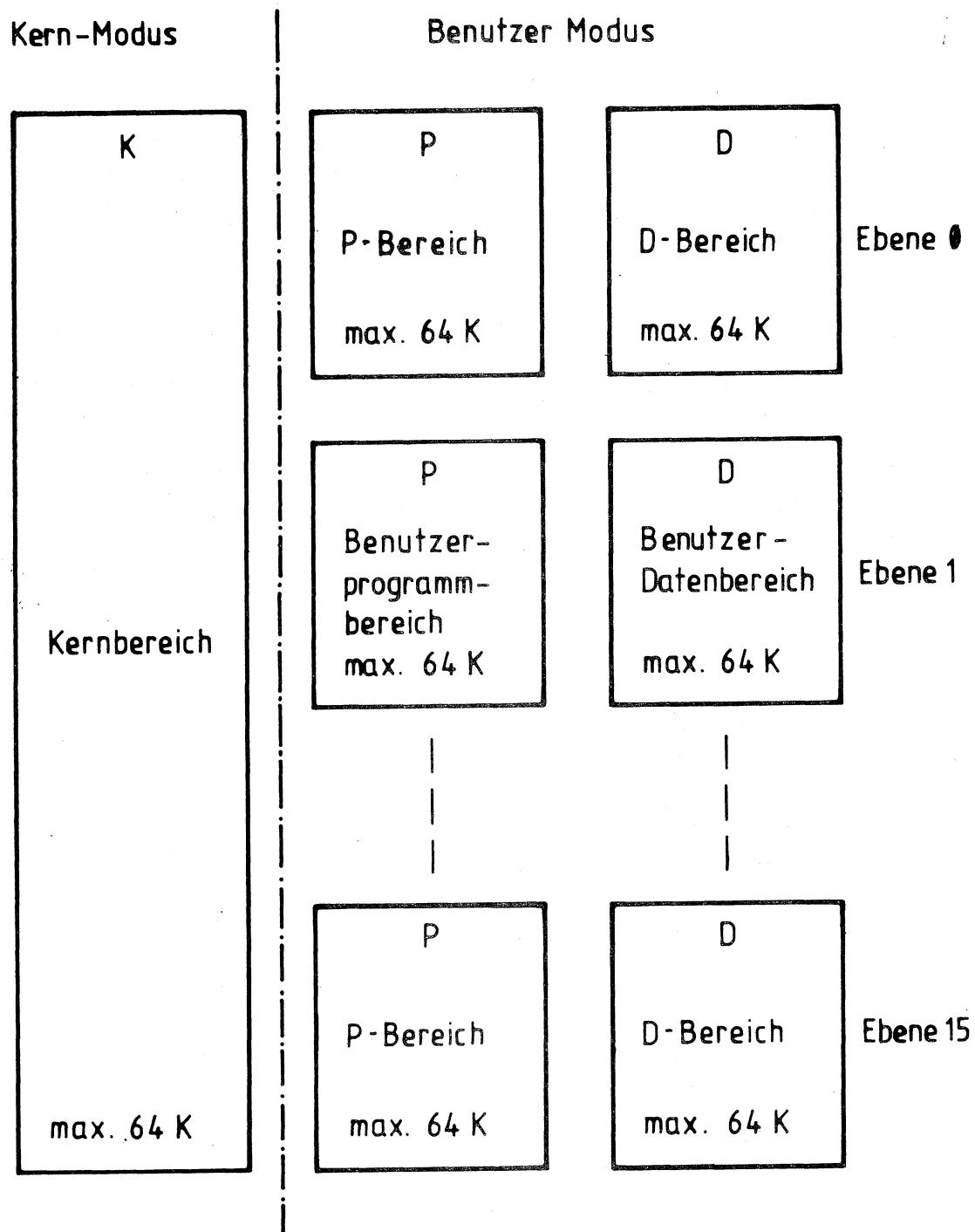

Der physikalische Adressraum von '00000 bis '0FFFF mit den Pool-, Peripherie- und Hauptspeicheradressen kann von der CPU ohne Benutzung der Adresstransformation direkt adressiert werden. Dieser Adressraum wird Kernbereich genannt.

Erfolgt eine Adresstransformation über die Kachelbasisadressen für Programme, so wird der Benutzerprogrammbereich angesprochen (P-Bereich). Der P-Bereich kann in 4 KByte Stufen bis maximal 64 KByte groß sein. Seine Lage im physikalischen Adressraum wird durch den Inhalt der Kachelbasisregister bestimmt. Im P-Bereich können Benutzerprogramme und Daten liegen.

Erfolgt eine Adresstransformation über die Kachelbasisregister für Daten, so wird der Benutzerdatenbereich (D-Bereich) angesprochen. Die maximale Größe des D-Bereichs ist 64 KByte. Die Abbildung des D-Bereichs auf den Hauptspeicher erfolgt wie beim P-Bereich über die Kachelbasisregister. Der D-Bereich ist reiner Datenbereich.

Um Programme im K-Bereich und P-Bereich zur Ausführung bringen zu können, sind zwei CPU Modi erforderlich.

a) Kern-Modus:

Programm läuft im Kernbereich. Eine Adresstransformation erfolgt nicht.

b) Benutzer-Modus:

Programm läuft im Benutzerprogrammbereich. Die 16 bit Befehlszähleradresse wird durch die Adresstransformation in eine 20 bit Adresse umgewandelt. Zur Transformation werden die P-Kachelbasisregister benutzt.

Abb. 2 Adressierungsbereiche 621/X3

### 1.3.3. Adressierungsarten und Modus-Umschaltung

---

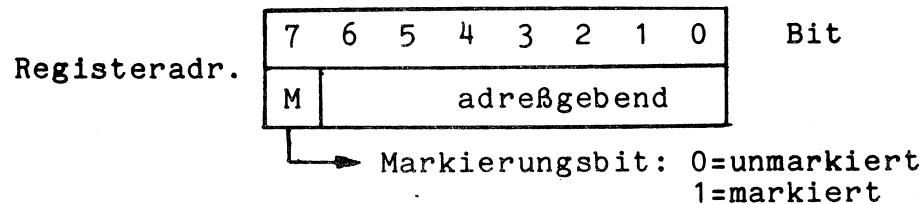

Um die verschiedenen Adressierungsbereiche ansprechen zu können, sind zusätzliche Adressierungsarten erforderlich. Dazu ist es notwendig, die Maschinenbefehle entsprechend zu kennzeichnen. Zu diesem Zweck wird die Registermarkierung benutzt. Ein Arbeits- oder Indexregister gilt als markiert, wenn seine Registeradresse größer '80 ist. Das höchstwertige Bit einer Registeradresse ist für die Adressierung irrelevant und wird nur zur Markierung von Registern benutzt. Diese Zuordnung ist möglich, da 128 Register pro Ebene zur Verfügung stehen.

Registermarkierungen sind beim Arbeitsregister (S) und beim Indexregister (X) möglich.

Abb. 3 Adressierungsarten 621/X3

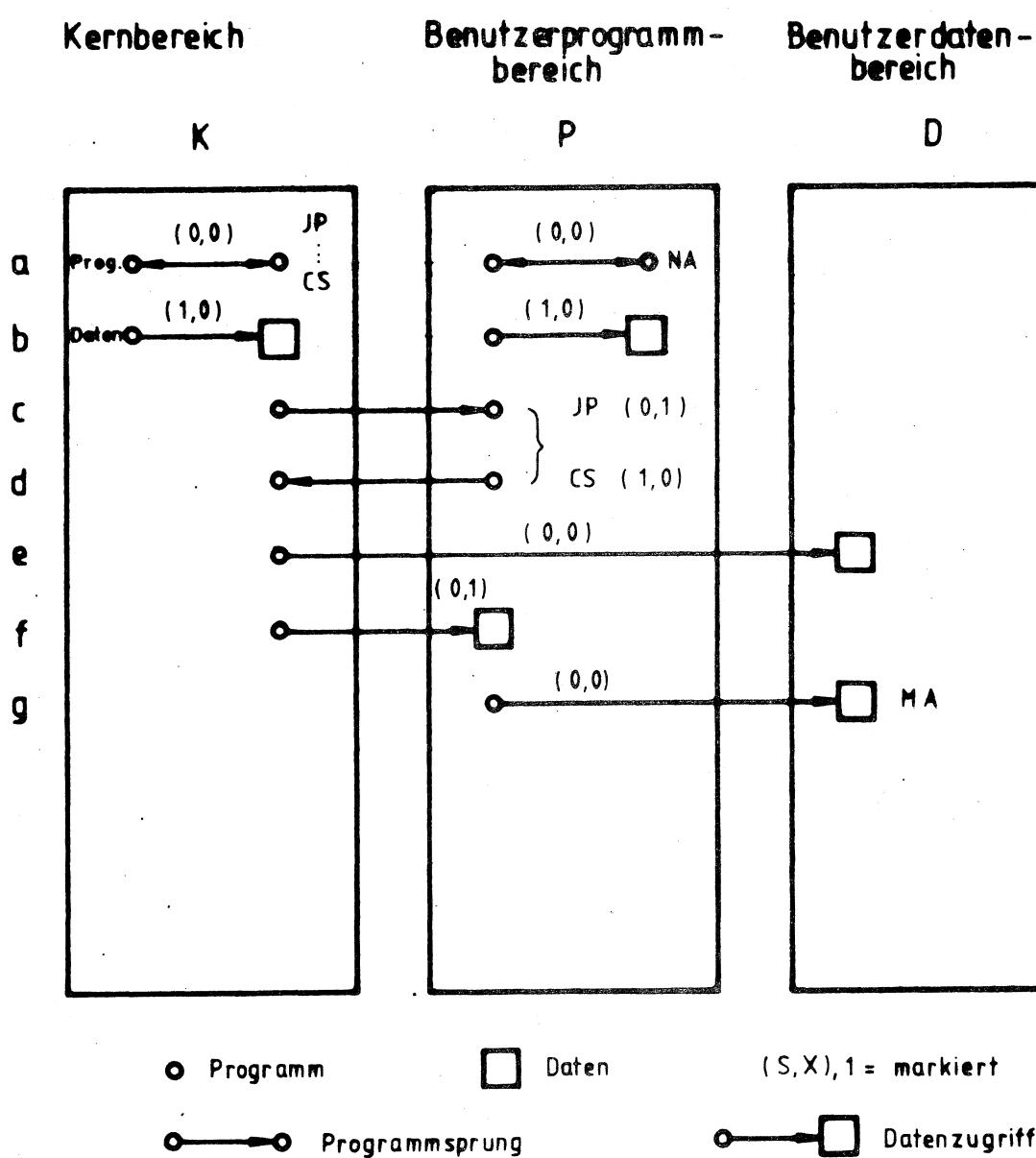

Aus Abb. 3 sind die möglichen Adressierungsarten ersichtlich.

- a) Programmsprung im gleichen Adressierungsbereich.

- b) Datenzugriffe innerhalb des gleichen Adressierungsbereichs.

- c) Sprung in den Benutzerprogrammbereich. Der CPU-Modus wird in den Benutzer-Mode umgeschaltet. Als Sprungbefehle sind der JPX und der CS.. möglich.

- d) Sprung vom Benutzerprogrammbereich in den Kernbereich. Der CPU-Modus wird in den Kern-Mode umgeschaltet. Als Sprungbefehle sind JPX und CS.. möglich.

- e) Operandenzugriff auf den Benutzerdatenbereich.

- f) Operandenzugriff auf den Benutzerprogrammbereich. Nur indirekte oder indizierte Adressierung möglich.

- g) Operandenzugriff auf den Benutzerdatenbereich. Die CPU arbeitet im Benutzer-Modus.

Markierte Sprungbefehle (JPX, CS..) bewirken eine Modusumschaltung. Markierte Befehle vom Typ LD.., AD.., SB.., AN.., OR.., EO.., ST.., im folgenden LD/ST Befehle genannt, erlauben Operandenzugriffe auf die Adressierungsbereiche K, P und D.

Die Zuordnung der Registermarkierungen zu ihren Funktionen in Abhängigkeit vom Befehlstyp ist aus folgender Tabelle ersichtlich.

| S | X | JP                  | CS                  | LD/ST                   |

|---|---|---------------------|---------------------|-------------------------|

| 0 | 0 | laufend.<br>Bereich | laufend.<br>Bereich | Operand in<br>D-Bereich |

| 0 | 1 | Modeum-<br>schaltg. | X                   | Operand in<br>P-Bereich |

| 1 | 0 | X                   | Modeum-<br>schaltg. | laufend.<br>Bereich     |

| 1 | 1 | X                   | X                   | X                       |

X : Markierung nicht erlaubt. Führt zu Fehlerunterbrechung.

#### 1.3.4. Speicherschutz

---

Sind allen Benutzerprogrammen unterschiedliche Kachelbasisadressen als ganzzahlige Vielfache von 4096 zugewiesen, kann kein Programm auf den Bereich eines anderen Programms zugreifen.

Zusätzlich ist eine Kachel im physikalischen Adressraum von 1 MByte als Speicherschutzkachel definiert. Die Speicherschutzkachel liegt im Adressbereich 'FF000-'FFFFF. Benötigt ein Benutzer nicht alle Kacheln, so wird die Kachelbasisadresse der nicht benutzten Kacheln auf 'FF gesetzt. Wird die Speicherschutzkachel angesprochen, so erfolgt eine Fehlerunterbrechung.

#### 1.3.5. Fehlerunterbrechungen

---

Das Adressierungsmodul AM erzeugt bei bestimmten Fehlerzuständen Fehlerunterbrechungen. Eine Fehlerunterbrechung (TRAP) startet die CNP-Ebene. Die beiden Statusregister des AM zeigen dabei die Ursache des Traps an.

Folgende Fehlerunterbrechungen sind möglich:

- Falsche Registermarkierung

- Speicherschutzkachel angesprochen

- Befehl aus der '30-Gruppe wurde ausgeführt

- Arithmetikprozessor wurde angesprochen, Hardware ist jedoch nicht vorhanden.

2. Schnittstelle Software

---

2.1. Adressen und Registerverwendung

---

2.1.1. Kachelbasisregister

---

Die Tabelle der Kachelbasisadressen für P- und D-Bereich sowie aller Ebenen, liegen im physikalischen Adressraum von '00800 bis '009FF. Dabei gilt folgende Adresszuordnung:

- |               |                                                      |

|---------------|------------------------------------------------------|

| '00800-'0080F | Kachelbasisadresse der Ebene 0<br>für den P-Bereich  |

| '00810-'0081F | Kachelbasisadressen der Ebene 0<br>für den D-Bereich |

| '00820-'0082F | Kachelbasisadressen P-Bereich Ebene 1                |

| '00830-'0083F | Kachelbasisadressen D-Bereich Ebene 1                |

| usw.          |                                                      |

Zuordnung der Adressbits:

|    |    |    |    |    |    |    |    |    |    |   |       |   |            |   |   |   |   |   |   |

|----|----|----|----|----|----|----|----|----|----|---|-------|---|------------|---|---|---|---|---|---|

| 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8     | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0 | Ebene | D | Kachel-Nr. |   |   |   |   |   |   |

1 = Kachelbasisadr. D-Bereich

### 2.1.2. AM-Statusregister

---

Zur Statusanzeige des AM sind zwei Statusregister vorhanden. Die Register erfüllen folgende Funktionen:

- Aktivieren des Adressierungsmoduls

- Anzeige des aktuellen Status

- Statusanzeige bei Fehlerunterbrechung

Die Registeradressen sind '00A00 und '00A01.

Register '00A00:

Bitzuordnung:

| Bit | 7    | 6  | 5 | 4  | 3 | 2 | 1 | 0     |

|-----|------|----|---|----|---|---|---|-------|

|     | TRAP | AM | M | FM |   |   |   | Ebene |

- Bit 0-3 Level

Der Inhalt ist bei aufgetretener Fehlerunterbrechung gültig (Bit 7 des Registers muß 1 sein) und zeigt die Ebene an, die den Fehler verursacht hat.

- Bit 4 FM

Fehlermodus ist ebenfalls nur bei gesetztem Bit 7 relevant und zeigt den CPU-Modus zum Zeitpunkt der Unterbrechung an. 1 = Kern-Modus

- Bit 5 M

Modus zeigt den aktuellen CPU-Modus an.

M=1 Kern-Modus; M=0 Benutzer-Modus

- Bit 6 AM

Durch Bit 6 wird der AM aktiviert. Das Bit ist von der Software setzbar. Nach einer Nullstellung ist das Bit zurückgesetzt. AM=0: AM nicht aktiviert; AM=1: AM aktiviert.

- Bit 7 Trap

Fehlerunterbrechung wird durch Bit 7 erzeugt. Trap startet die CNP-Ebene. Der Start erfolgt bis Trap zurückgesetzt wird. Bit 0-3 zeigt die Ebene an, die den Trap verursacht hat und Bit 4 zeigt an, in welchem Modus die Ebene lief.

Das Register '00A00 wird nach Abfrage durch die Software zurückgesetzt. Das Abfragen über die Bedienungskonsole setzt das Register nicht zurück. Diese Rücksetzfunktion gilt nicht für Bit 5 und 6.

Register '00A01

Das Register zeigt die Art der Fehlerunterbrechung an.

Bitzuordnung:

| Bit | 7 | 6 | 5 | 4 | 3  | 2  | 1  | 0  |

|-----|---|---|---|---|----|----|----|----|

|     | 1 | 0 | 0 | 0 | AP | 3X | SK | RM |

- Bit 0 RM:

Ein Befehl mit nicht definierter Registermarkierung wurde ausgeführt.

- Bit 1 SK:

Es erfolgte ein Zugriff auf die Speicherschutzkachel. Kachelbasisadresse war 'FF'.

- Bit 2 3X:

Ein Befehl mit Maschinencode '30-'3F wurde ausgeführt.

- Bit 3 AP:

Arithmetikprozessor ist nicht vorhanden. Versuchte Aktivierung durch den Befehl '0C'.

Das Register '00A01' wird nach Abfrage durch die Software gelöscht. Das Abfragen über die Bedienungskonsole setzt das Register nicht zurück.

2.2. **Besonderheiten zur Schnittstelle**

---

2.2.1. **Systemzustand nach Nullstellung**

---

Nach Nullstellung ist der AM nicht aktiviert. Eine Adreßtransformation findet nicht statt. Die Zentraleinheit verhält sich adreßmäßig wie ein 621 X1. Registermarkierungen führen nicht zu Modusumschaltungen. Falsche Registermarkierungen werden jedoch gemeldet. Alle Ebenen werden in den Kern-Modus geschaltet.

2.2.2. **Ein- und Ausschalten des Adressierungsmoduls**

---

Beim Ausschalten des AM (Rücksetzen Bit 6 Reg. '00A00) bleiben die Modusinformationen der Ebenen erhalten. Der Modus-Speicher wird nicht verändert. Wird der AM wieder aktiviert, so befinden sich die Ebenen im gleichen Modus wie vor dem Ausschalten.

2.2.3. **Pufferungen von Registern bei Netzausfall**

---

Zur Zeit ist nur eine Pufferung der Pool-Register möglich. Kachelbasisregister und Modus-Speicher verlieren ihren Inhalt. Nach Netzwiederkehr erfolgt eine Nullstellung des Systems (s. Punkt 2.2.1).

2.3. **Verhalten im Fehlerfall**

---

Von der Hardware werden folgende Fehlerfälle abgefangen:

2.3.1. **Falsche Registermarkierung**

---

Es erfolgt eine Fehlerunterbrechung (s. Punkt 1.3.5). Die Registermarkierungen haben keine Auswirkung auf die AM-Steuerung. Der Befehl wird vollständig abgearbeitet. Es erfolgt keine Modusumschaltung, Operanden liegen im laufenden Adressierungsbereich.

2.3.2. **Speicherschutzkachel angesprochen**

---

Es erfolgt eine Fehlerunterbrechung (s. Punkt 1.3.5). Meldung des Fehlers über die Register '00A00 und '00A01. Ist der Speicher nicht bis 1 MByte ausgebaut, wird zusätzlich ein Bus-Fehler gemeldet.

2.3.3. **Befehle der Gruppe '3X**

---

Es erfolgt eine Fehlerunterbrechung (s. Punkt 1.3.5). Bedingt durch die Mikroschnittsteuerung der CPU kann ein 3X Befehl eine Länge von 1 Byte oder 2 Byte haben.

Ungerader Befehlscode (z.B. '31) 2 Byte Befehl

Gerader Befehlscode (z.B. '30) 1 Byte Befehl.

2.3.4. Fehlerhafte Aktivierung des Arithmetikprozessors

---

Es erfolgt eine Fehlerunterbrechung (s. Punkt 1.3.5). Wird der Maschinenbefehl 'OC ausgeführt und es ist kein Arithmetikprozessor vorhanden, so wird der Fehler im AM Statusregister gemeldet. Durch die Befehlsausführung werden keine Register verändert.

2.3.5. Zeitverhalten der Fehlermeldungen

---

- Alle in Punkt 2.3.1 bis 2.3.4 aufgeführten Fehler führen zu einem Ebenenwechsel nach Ausführung des fehlerhaften Befehls.

- Gleichzeitig können die Fehlermeldungen SK und RM auftreten.

- Der vor Abfrage der Register zuletzt aufgetretene Fehler wird gemeldet.

Heinrich Dietz

Solinger Straße 9

4330 Mülheim-Ruhr

Tel.: (0208) 44 34-1

Telex 856770

**DIETZ** Computer

SYSTEME