# RTE Assembler

## Reference Manual

# RTE Assembler

## Reference Manual

---

HEWLETT-PACKARD COMPANY

11000 WOLFE ROAD, CUPERTINO, CALIFORNIA, 95014

## LIST OF EFFECTIVE PAGES

| Pages             | Effective Date |

|-------------------|----------------|

| Title .....       | May 1975       |

| ii to vi .....    | May 1975       |

| 1-1 to 1-6 .....  | May 1975       |

| 2-1 to 2-7 .....  | May 1975       |

| 3-1 to 3-18 ..... | May 1975       |

| 4-1 to 4-22 ..... | May 1975       |

| A-1 to A-3 .....  | May 1975       |

| B-1 to B-10 ..... | May 1975       |

| C-1 to C-3 .....  | May 1975       |

| D-1 to D-5 .....  | May 1975       |

| E-1 to E-2 .....  | May 1975       |

| F-1 to F-12 ..... | May 1975       |

| G-1 to G-3 .....  | May 1975       |

| H-1 to H-6 .....  | May 1975       |

| I-1 to I-5 .....  | May 1975       |

This manual describes the Assembler which is designed to operate under control of the RTE-III Operating System. (Refer to the *Real-Time Executive-III Software System Programming and Operating Manual*, 92060-90001.)

This manual assumes that the reader is an experienced assembly language programmer who is familiar with operating systems.

The Assembler permits the programmer to use all supported machine instructions for the HP 21MX Computer and it is assumed that object programs produced by the Assembler will be executed on an HP 21MX Computer. However, the object program may be executed on other HP 2100 Series computers (2114, 2115, 2116, or 2100) if the following machine and pseudo instructions are *not* used:

- Word Processing (described in paragraph 3-5)

- Byte Processing (paragraph 3-6)

- Bit Processing (paragraph 3-7)

- Index Register Group (paragraph 3-11)

- Floating Point (paragraph 3-18)

- Dynamic Mapping System (paragraph 3-19)

- DBL and DBR: Define Left Byte and Define Right Byte (paragraph 4-3)

- BYT: Define Octal Byte Constants (paragraph 4-4)

- MIC: Define User Instruction (paragraph 4-8)

If the object programs produced by the Assembler are relocated and executed under control of an operating system other than the RTE Operating System, the following restrictions apply:

- ENT pseudo instructions with absolute or common symbols as operands must *not* be used.

- I/O instructions using externally-defined selection codes must *not* be used.

- I/O select codes must *not* be defined via the ENT pseudo instruction.

- Memory reference instructions must *not* refer to *external* symbols with *offset* values.

When assembling programs to be run under control of the Basic Control System (BCS) (see the *Basic Control System Manual*, part no. 02116-90017), the following restrictions also apply:

Absolute operands greater than  $77_8$  are illegal in relocatable programs. However, such usage will *not* be diagnosed as errors by the loader; instead, it will result in errors during execution of the object program.

The content of this manual is as follows:

- Section I      discusses the assembly process in general, program relocation, assembly options, and assembler input and output.

- Section II     describes the source statement format.

- Section III    describes all of the available machine instructions.

- Section IV    describes all of the available assembler pseudo instructions.

In addition, nine appendices are supplied, as follows:

- Appendix A describes the Hewlett-Packard character set.

- Appendix B summarizes all of the available machine and pseudo instructions (including instruction formats).

- Appendix C presents a one-sentence definition of all available machine and pseudo instructions, arranged alphabetically by mnemonic.

- Appendix D presents a tabular summary of the binary format of all available machine instructions.

- Appendix E describes how to run an assembly.

- Appendix F lists and describes all of the assembler error messages.

- Appendix G describes the error messages.

- Appendix H presents relocatable formats.

- Appendix I discusses the RTE Cross Reference Table Generator.

For the programmer's convenience, a table of the powers of two is contained on the back cover.

# CONTENTS

|                                            |             |                                          |             |

|--------------------------------------------|-------------|------------------------------------------|-------------|

| <b>Section I</b>                           | <b>Page</b> |                                          |             |

| <b>INTRODUCING THE ASSEMBLER</b>           |             |                                          |             |

| Assembly Processing .....                  | 1-1         | Input/Output .....                       | 3-8         |

| Symbolic Addressing .....                  | 1-1         | Overflow .....                           | 3-9         |

| Memory Addressing .....                    | 1-1         | Halt .....                               | 3-9         |

| Paging .....                               | 1-1         | Extended Arithmetic Unit (EAU) .....     | 3-9         |

| Indirect Addressing .....                  | 1-2         | Floating Point .....                     | 3-10        |

| Program Relocation .....                   | 1-2         | Dynamic Mapping System (21MX Only) ..... | 3-10        |

| Program Location Counter .....             | 1-3         | Memory Addressing .....                  | 3-11        |

| Source Program .....                       | 1-3         | Status and Violation Registers .....     | 3-11        |

| Assembly Options .....                     | 1-3         | Map Segmentation .....                   | 3-11        |

| Binary Output .....                        | 1-3         | Power Fail Characteristics .....         | 3-12        |

| Symbol Table .....                         | 1-3         | Protected Mode .....                     | 3-12        |

| List Output .....                          | 1-6         | MEM Violation .....                      | 3-12        |

| Dynamic Mapping System Instructions .....  | 3-12        |                                          |             |

| <b>Section II</b>                          | <b>Page</b> |                                          |             |

| <b>SOURCE STATEMENT FORMAT</b>             |             |                                          |             |

| Statement of Characteristics .....         | 2-1         | <b>Section IV</b>                        | <b>Page</b> |

| Field Delimiters .....                     | 2-1         | <b>PSEUDO INSTRUCTIONS</b>               |             |

| Character Set .....                        | 2-1         | Assembler Control .....                  | 4-1         |

| Statement Length .....                     | 2-1         | Object Program Linkage .....             | 4-5         |

| Label Field .....                          | 2-1         | Address and Symbol Definition .....      | 4-11        |

| Label Symbol .....                         | 2-1         | Constant Definition .....                | 4-14        |

| Asterisk .....                             | 2-2         | Storage Allocation .....                 | 4-19        |

| Opcode Field .....                         | 2-2         | Assembly Listing Control .....           | 4-19        |

| Operand Field .....                        | 2-2         | Arithmetic Subroutine Calls .....        | 4-20        |

| Symbolic Terms .....                       | 2-2         | "Jump to Microprogram" .....             | 4-21        |

| Numeric Terms .....                        | 2-4         | Example .....                            | 4-21        |

| Asterisk .....                             | 2-4         | Combining Multiple Mnemonics .....       | 4-21        |

| Expression Operators .....                 | 2-4         | Example .....                            | 4-21        |

| Evaluation of Expressions .....            | 2-4         | Defining Constants .....                 | 4-21        |

| Expression Terms .....                     | 2-4         | Example .....                            | 4-22        |

| Absolute and Relocatable Expressions ..... | 2-4         |                                          |             |

| Absolute Expressions .....                 | 2-4         |                                          |             |

| Relocatable Expressions .....              | 2-6         |                                          |             |

| Literals .....                             | 2-6         | <b>Appendix A</b>                        | <b>Page</b> |

| Indirect Addressing .....                  | 2-6         | <b>CHARACTER CODES</b> .....             | A-1         |

| Clear Flag Indicator .....                 | 2-7         |                                          |             |

| Comments Field .....                       | 2-7         | <b>Appendix B</b>                        | <b>Page</b> |

| <b>Section III</b>                         | <b>Page</b> |                                          |             |

| <b>MACHINE INSTRUCTIONS</b>                |             |                                          |             |

| Memory Reference .....                     | 3-1         | <b>SUMMARY OF INSTRUCTIONS</b>           |             |

| Jump and Increment-Skip .....              | 3-1         | Machine Instructions .....               | B-2         |

| Add, Load and Store .....                  | 3-1         | Memory Reference .....                   | B-2         |

| Logical Operations .....                   | 3-2         | Jump and Increment-Skip .....            | B-2         |

| Word Processing (21MX Only) .....          | 3-2         | Add, Load and Store .....                | B-2         |

| Byte Processing (21MX Only) .....          | 3-2         | Logical .....                            | B-2         |

| Bit Processing (21MX Only) .....           | 3-3         | Word Processing .....                    | B-2         |

| Register Reference .....                   | 3-4         | Byte Processing .....                    | B-3         |

| Shift-Rotate Group .....                   | 3-4         | Bit Processing .....                     | B-3         |

| Alter-Skip Group .....                     | 3-4         | Register Reference .....                 | B-3         |

| Index Register Group (21MX Only) .....     | 3-5         | Shift-Rotate .....                       | B-3         |

| No-Operation .....                         | 3-7         | No-Operation .....                       | B-4         |

| Alter-Skip .....                           | 3-4         | Alter-Skip .....                         | B-4         |

| Index Register .....                       | 3-5         | Index Register .....                     | B-5         |

| Input/Output, Overflow, and Halt .....     | 3-7         | Input/Output, Overflow, and Halt .....   | B-6         |

# CONTENTS (continued)

|                                              |      |                                                  |      |

|----------------------------------------------|------|--------------------------------------------------|------|

| Memory Expansion .....                       | B-7  | Input .....                                      | F-7  |

| Pseudo Instructions .....                    | B-9  | X Specification .....                            | F-7  |

| Assembler Control .....                      | B-9  | Output .....                                     | F-7  |

| Object Program Linkage .....                 | B-9  | Input .....                                      | F-7  |

| Address and Symbol Definition .....          | B-9  | H and " " Specifications (Literal Strings) ..... | F-7  |

| Constant Definition .....                    | B-10 | Output .....                                     | F-7  |

| Storage Allocation .....                     | B-10 | Input .....                                      | F-8  |

| Assembly Listing Control .....               | B-10 | /Specification .....                             | F-8  |

| Define User Instruction .....                | B-10 | How to Put Formats Together .....                | F-8  |

| Appendix C                                   | Page | Free-Field Input .....                           | F-9  |

| <b>ALPHABETIC LIST OF INSTRUCTIONS</b> ..... | C-1  | Data Item Delimiters .....                       | F-9  |

| Appendix D                                   | Page | Floating-Point Input .....                       | F-9  |

| <b>CONSOLIDATED CODING SHEETS</b> .....      | D-1  | Octal Input .....                                | F-9  |

| Appendix E                                   | Page | Record Terminator .....                          | F-10 |

| <b>RUNNING ASSEMBLIES</b>                    |      | Comments Within Input .....                      | F-10 |

| Assembler I/O .....                          | E-1  | Example Calling Sequences .....                  | F-10 |

| Assembler Operation .....                    | E-1  | Internal Conversion .....                        | F-10 |

| Messages During Assembly .....               | E-2  | Buffered I/O with the Formatter .....            | F-11 |

| Appendix F                                   | Page | Appendix G                                       | Page |

| <b>THE FORMATTER</b>                         |      | <b>ASSEMBLER ERROR MESSAGES</b> .....            | G-1  |

| Input and Output .....                       | F-1  | Appendix H                                       | Page |

| Records .....                                | F-1  | <b>RELOCATABLE FORMATS</b>                       |      |

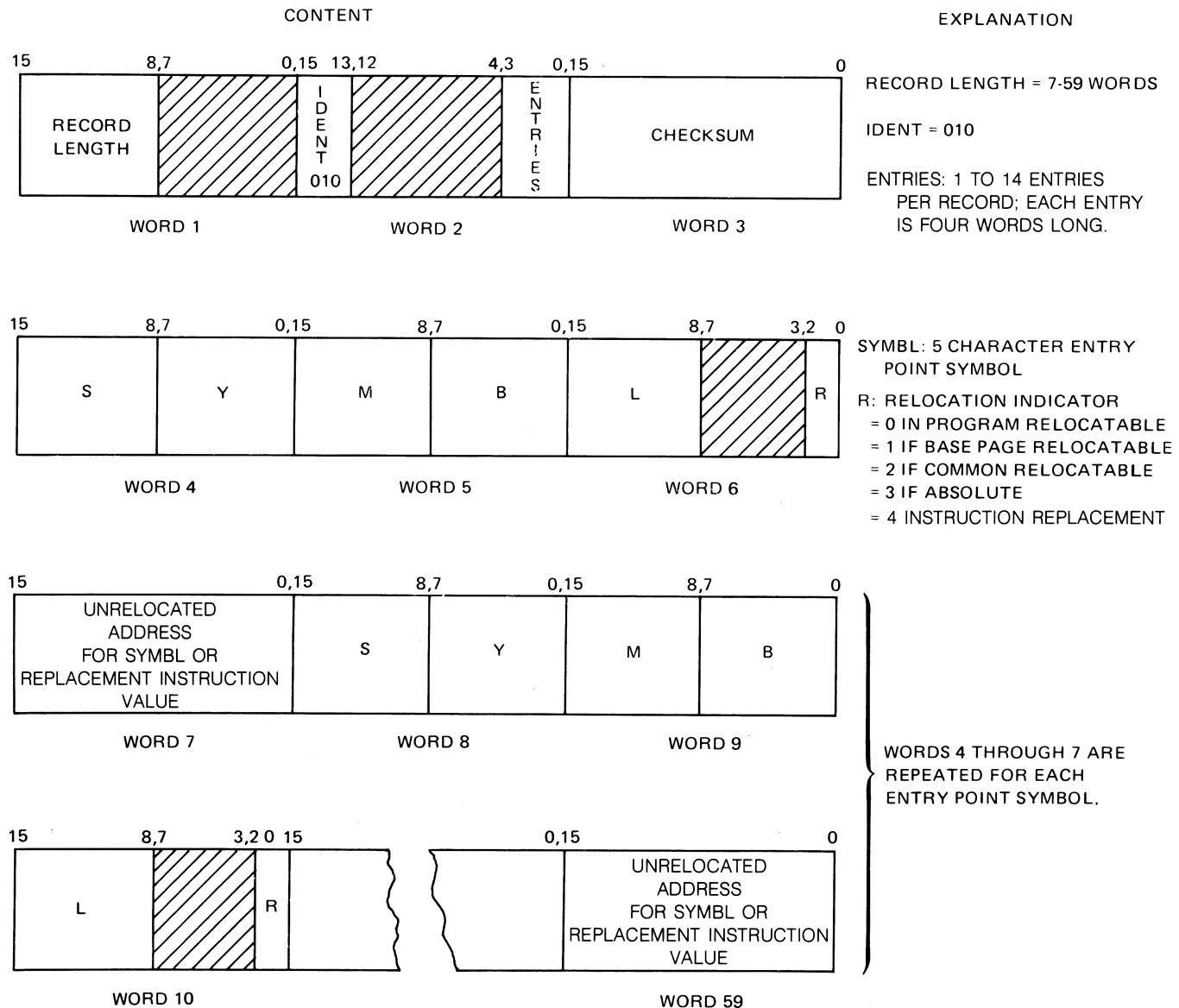

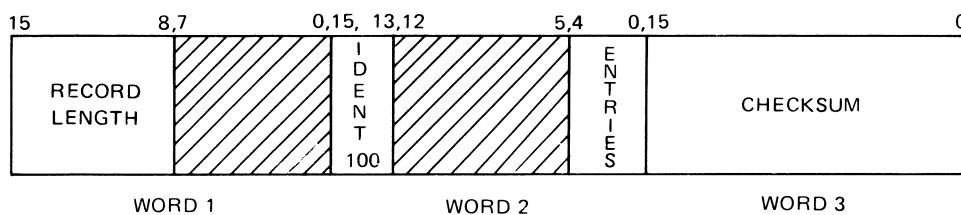

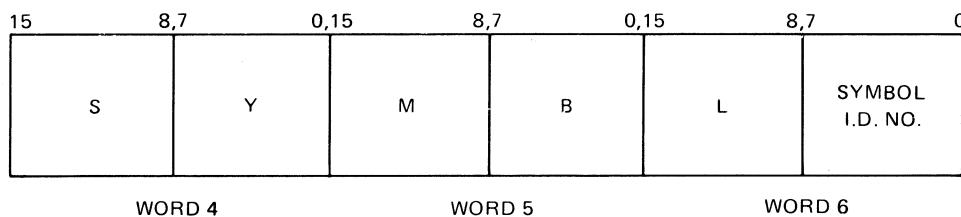

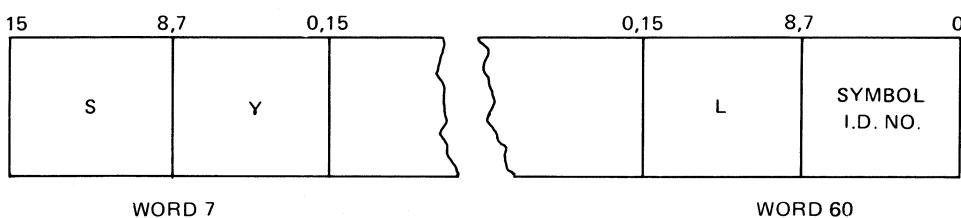

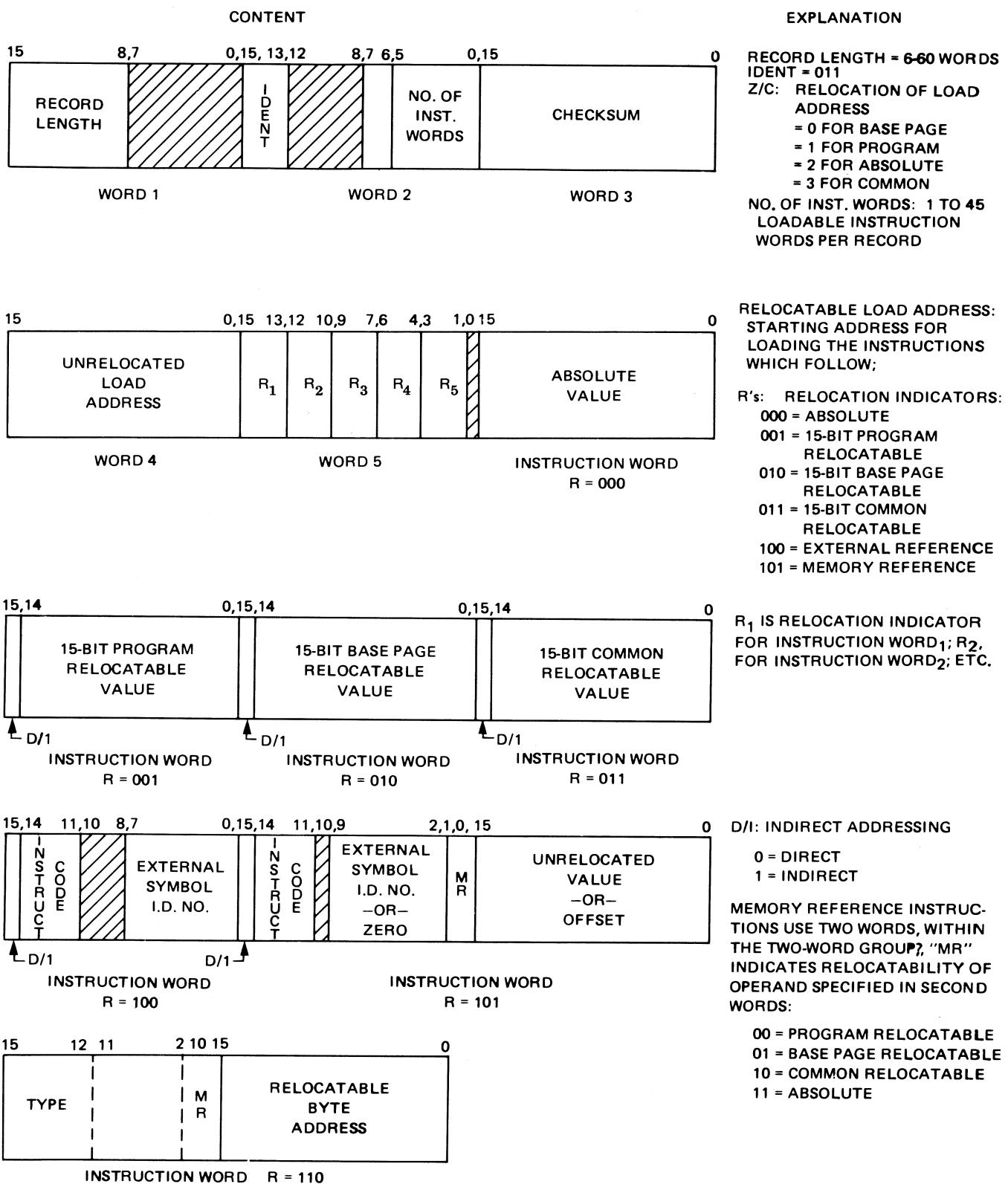

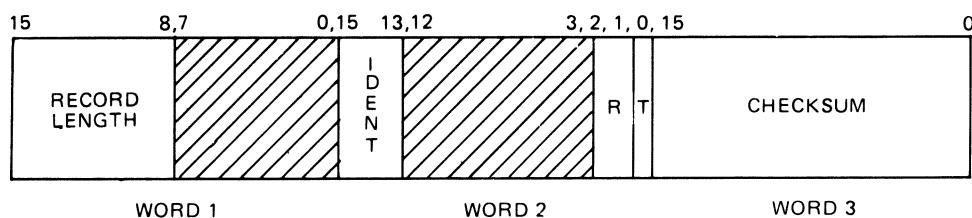

| Formatted Input/Output .....                 | F-1  | NAM Record .....                                 | H-1  |

| Format Specifications .....                  | F-4  | ENT Record .....                                 | H-2  |

| Conversion Specifications .....              | F-4  | EXT Record .....                                 | H-3  |

| Editing Specifications .....                 | F-4  | DBL Record .....                                 | H-4  |

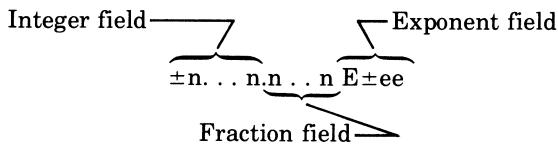

| E Specification .....                        | F-4  | END Record .....                                 | H-5  |

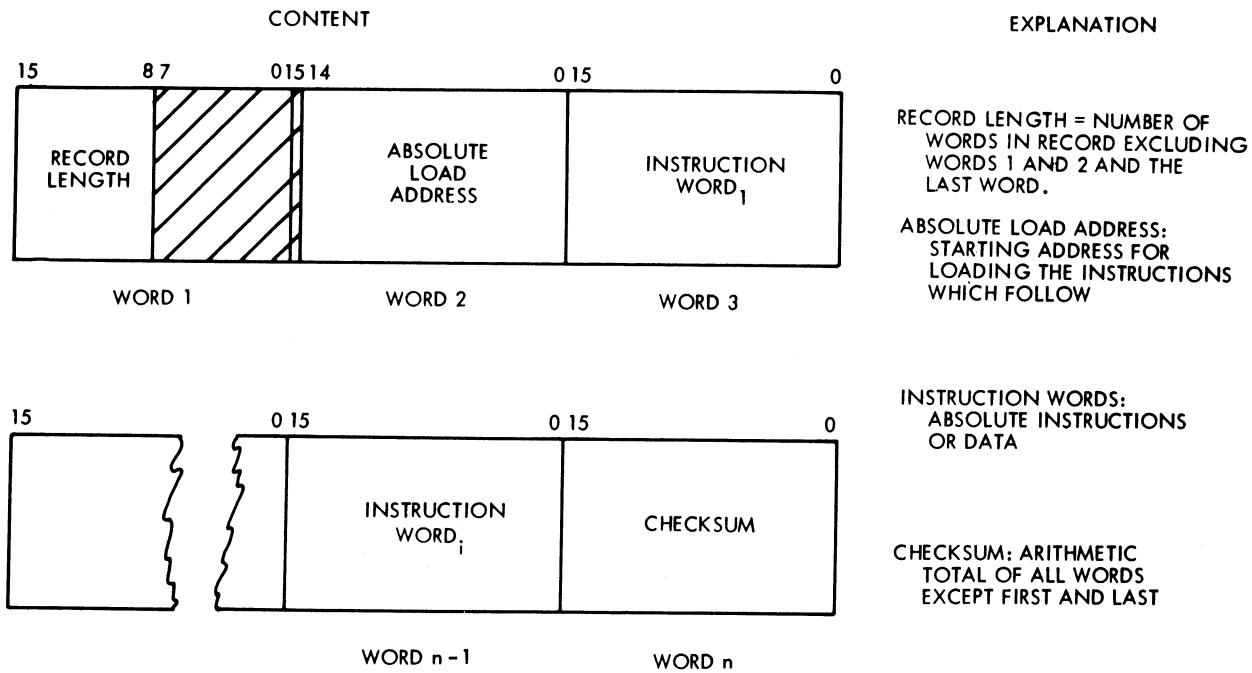

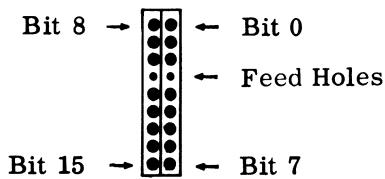

| Output .....                                 | F-4  | Absolute Tape Format .....                       | H-6  |

| Input .....                                  | F-5  | Appendix I                                       | Page |

| Rules for E Field Input .....                | F-5  | <b>RTE CROSS REFERENCE TABLE</b>                 |      |

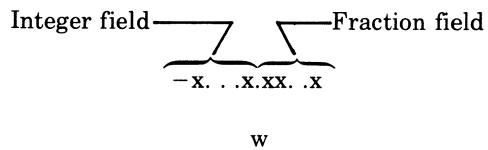

| F Specification .....                        | F-5  | <b>GENERATOR</b>                                 |      |

| Output .....                                 | F-5  | Computer Configuration .....                     | I-1  |

| Input .....                                  | F-5  | Functional and Operational Characteristics ..... | I-1  |

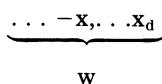

| I Specification .....                        | F-5  | Output Format .....                              | I-1  |

| Output .....                                 | F-5  | Pseudo Processing .....                          | I-1  |

| Input .....                                  | F-6  | Double Defined Processing .....                  | I-1  |

| O, K, and @ Specifications .....             | F-6  | Undefined Label Processing .....                 | I-1  |

| Output .....                                 | F-6  | Unused Label Processing .....                    | I-2  |

| Input .....                                  | F-6  | Literal Processing .....                         | I-2  |

| A and R Specifications .....                 | F-6  | Operation Directive .....                        | I-2  |

| Output .....                                 | F-6  | Bounds .....                                     | I-2  |

|                                              |      | Sample Cross-Reference Generation .....          | I-3  |

## ILLUSTRATIONS

| Title                                                             | Page |

|-------------------------------------------------------------------|------|

| Source Program .....                                              | 1-4  |

| Symbol Table Listing .....                                        | 1-5  |

| Label Examples .....                                              | 2-3  |

| Label Usage Examples .....                                        | 2-3  |

| Symbolic Operand Examples .....                                   | 2-5  |

| Expression Operator Examples .....                                | 2-5  |

| Indirect Addressing Example .....                                 | 2-7  |

| Clear Flag Examples .....                                         | 2-7  |

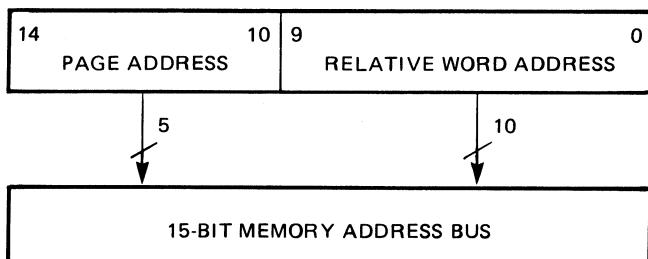

| Basic Memory Addressing Scheme .....                              | 3-11 |

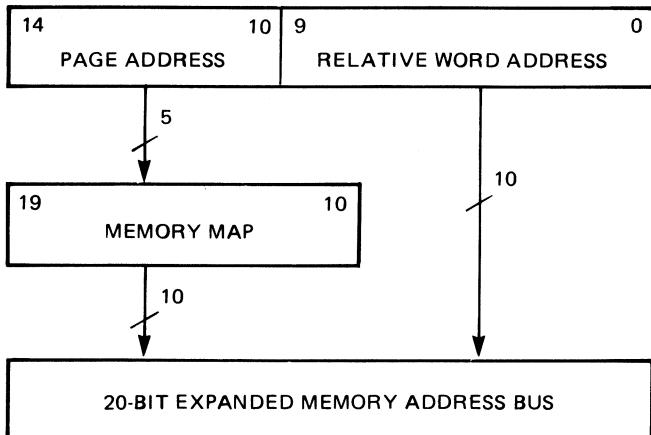

| Expanded Memory Addressing Scheme .....                           | 3-11 |

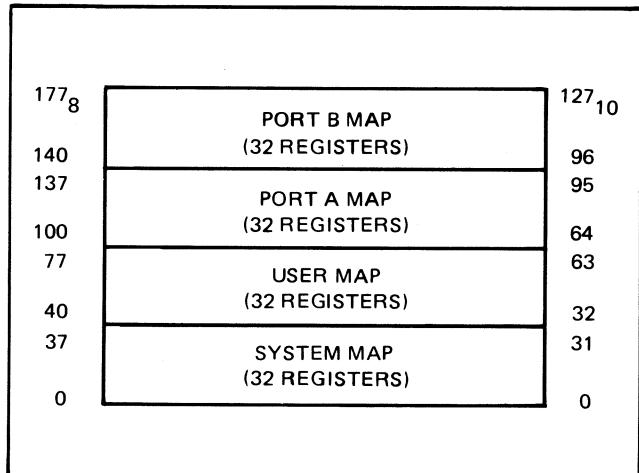

| Map Segmentation .....                                            | 3-12 |

| ORB Example .....                                                 | 4-2  |

| ORR Example (with Single ORG) .....                               | 4-3  |

| ORR Example (with Multiple ORG's) .....                           | 4-3  |

| IFN/XIF and IFZ/XIF Example .....                                 | 4-4  |

| IFZ/XIF Example .....                                             | 4-4  |

| COM Examples .....                                                | 4-6  |

| ENT/EXT Examples .....                                            | 4-7  |

| EXT with Offset .....                                             | 4-8  |

| ENT in COMmon and ENT<br>Defining An External I/O Reference ..... | 4-8  |

| EXT, ENT for I/O Channel .....                                    | 4-9  |

| Label RPL Octal Value .....                                       | 4-10 |

| DEF Examples .....                                                | 4-11 |

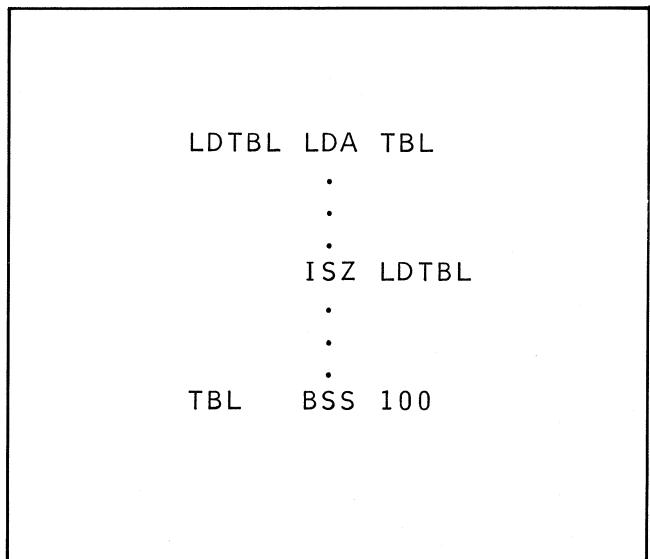

| Example of Incorrect Address Modification .....                   | 4-11 |

| Loader-Assigned Locations for Figure 4-8 .....                    | 4-12 |

| Example of Correct Address<br>Modification .....                  | 4-12 |

| Loader-Assigned Locations for Figure 4-10 .....                   | 4-12 |

| ABS Examples .....                                                | 4-13 |

| EQU Example .....                                                 | 4-13 |

| EQU Examples .....                                                | 4-14 |

| ASC Example .....                                                 | 4-15 |

| DEC Examples (Integer) .....                                      | 4-16 |

| DEC Examples (Floating Point) .....                               | 4-16 |

| DEC Examples (Floating Point) .....                               | 4-16 |

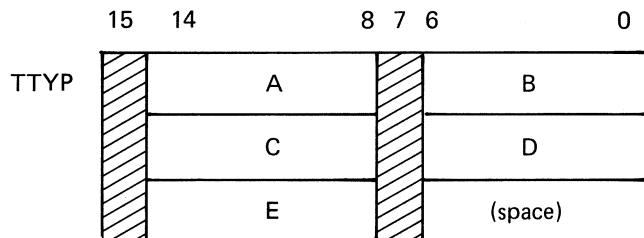

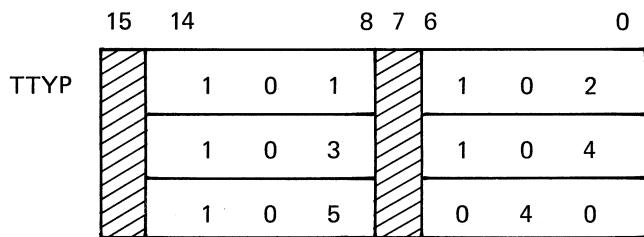

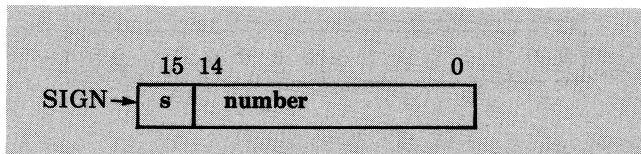

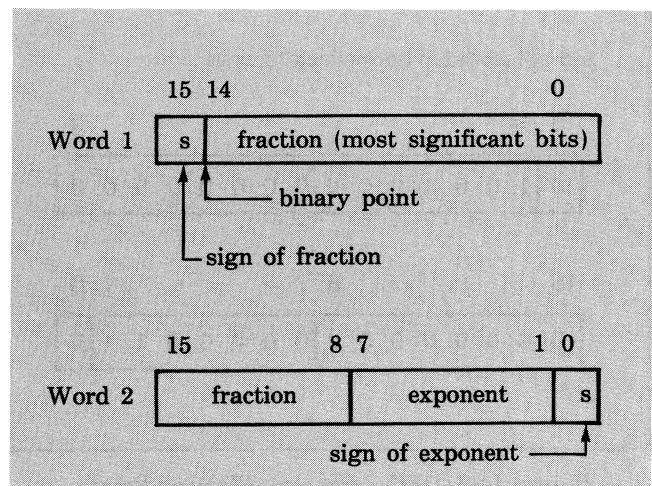

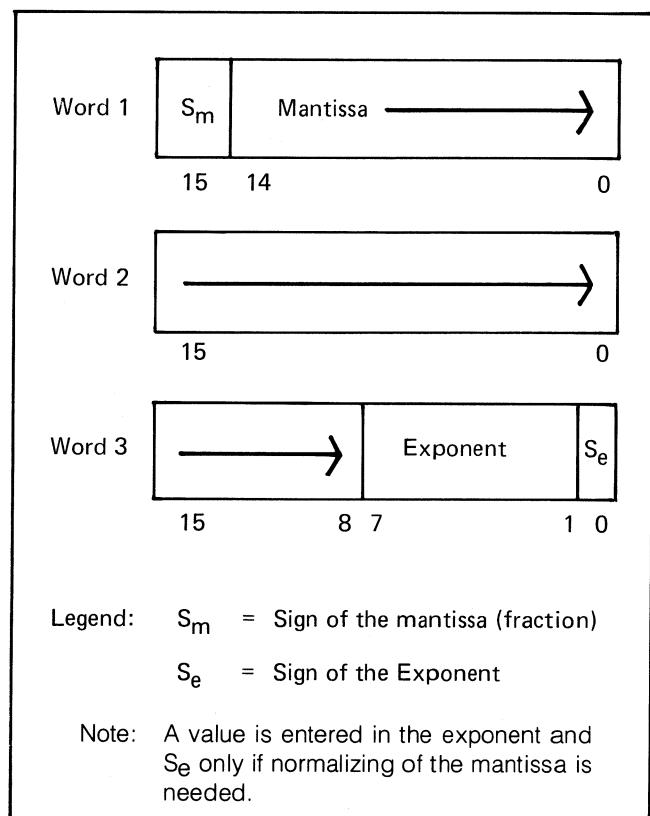

| DEX Memory Format .....                                           | 4-17 |

| DEX Examples .....                                                | 4-17 |

| OCT Examples .....                                                | 4-18 |

| BYT Examples .....                                                | 4-19 |

| ASCII Character Codes .....                                       | A-1  |

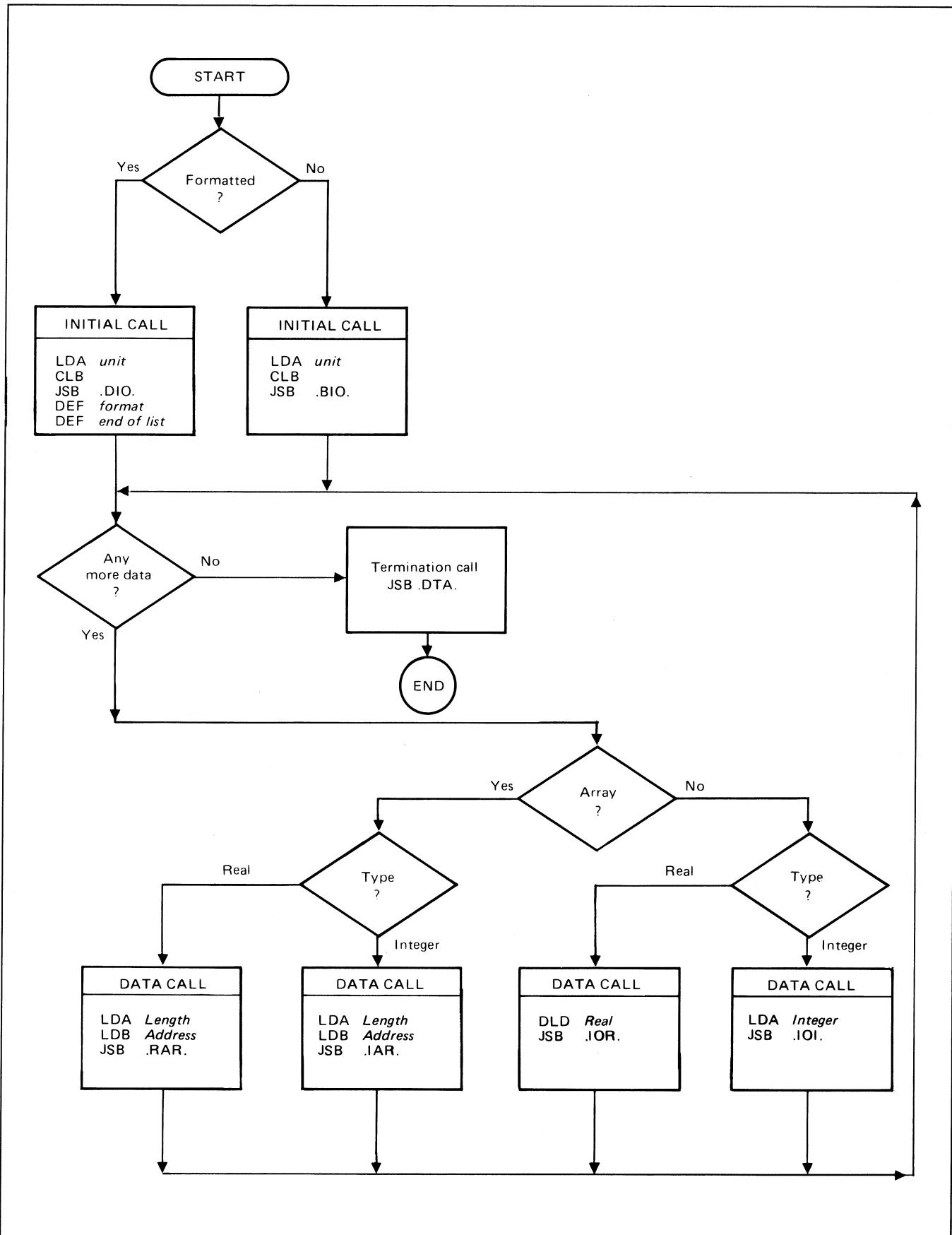

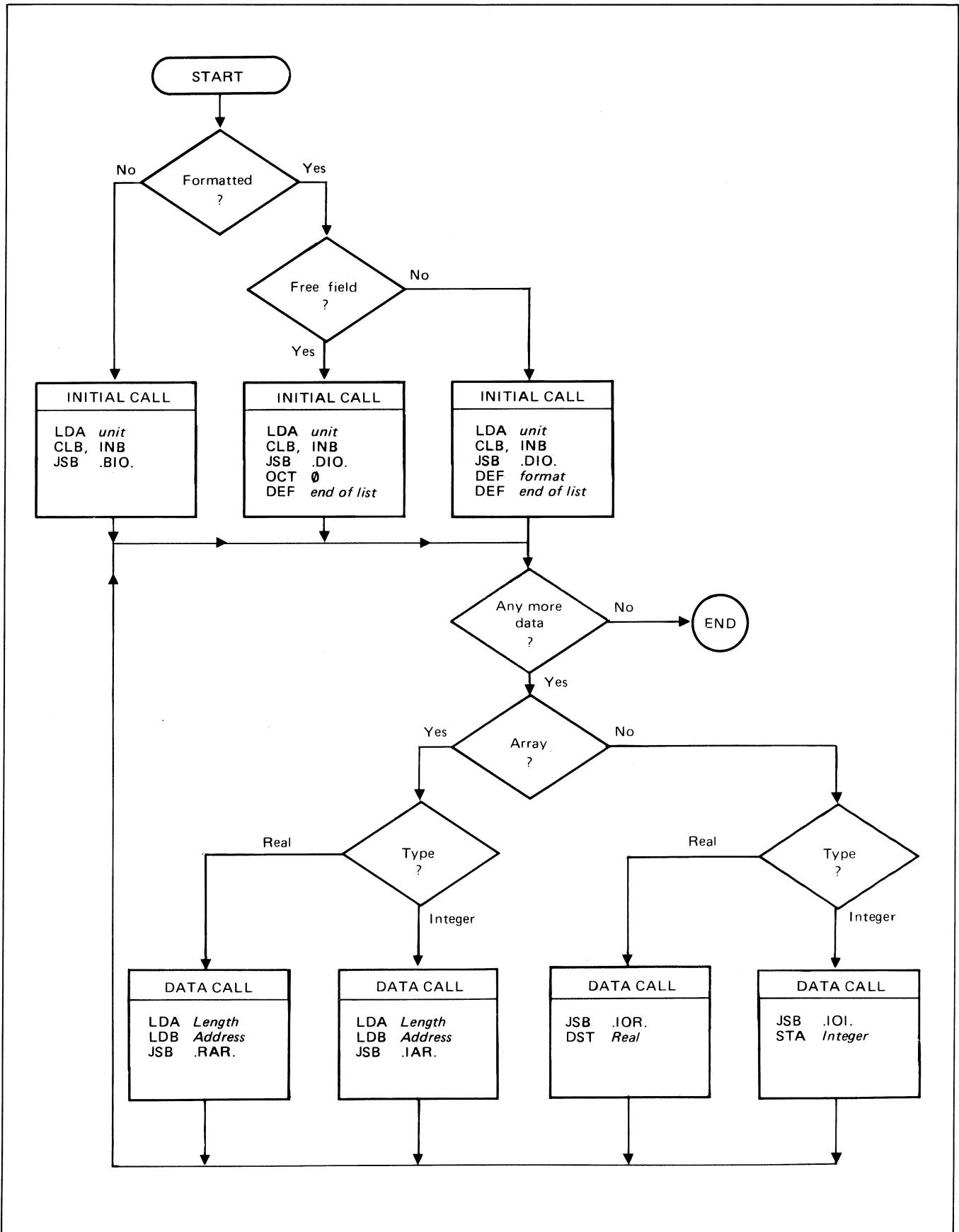

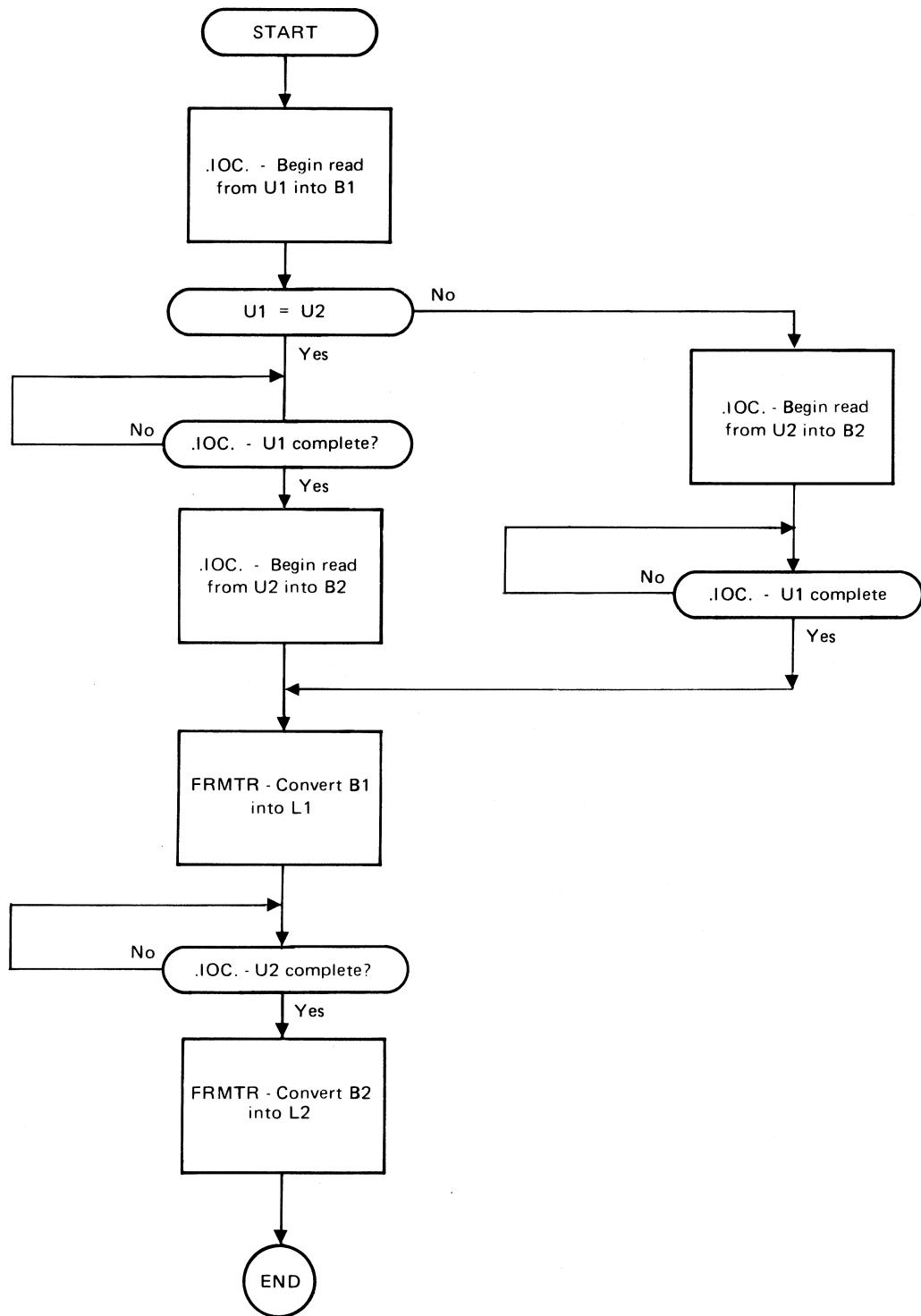

| Input Calling Sequence Selection .....                            | F-2  |

| Output Calling Sequence Selection .....                           | F-3  |

| Buffered I/O with the Formatter .....                             | F-12 |

## TABLES

| Title                                            | Page |

|--------------------------------------------------|------|

| Logical Memory Addresses/Pages .....             | 1-2  |

| Control Statement Parameters .....               | 1-5  |

| MEM Status Register Format .....                 | 3-11 |

| MEM Violation Register Format .....              | 3-12 |

| Legend for Figure A-1 .....                      | A-2  |

| HP 7970B BCD-ASCII Conversion .....              | A-3  |

| Base Set Instruction Codes in Binary .....       | D-2  |

| Extended Instruction Group Codes in Binary ..... | D-3  |

# INTRODUCING THE ASSEMBLER

SECTION

I

The Assembler translates symbolic source language instructions into an object program for execution on the computer. The source language provides mnemonic machine operation codes, assembler-directing pseudo instructions, and symbolic addressing. The assembled program may be absolute or relocatable.

The source program may be assembled as a complete entity or it may be subdivided into several relocatable subprograms (or a main program and several subroutines), each of which may be assembled separately. When relocatable object programs and subprograms are desired to be executed, they are relocated and linked to one another by the relocating loader.

Absolute object programs may be loaded by the Basic Binary Loader or the Basic Binary Disc Loader. There are no intermediate steps needed to prepare the code before it is executed.

The Assembler can read the source input from paper tape, punched cards, magnetic tape or the LS Area of the disc. The Assembler outputs the resultant object program on the standard punch output device and/or to the LG Area of the disc in a format acceptable to the RTE Relocating Loader.

## 1-1. ASSEMBLY PROCESSING

The Assembler is a two pass system. A *pass* is defined as a processing cycle of the source program input.

In the first pass, the Assembler creates a symbol table from the names used in the source statements and (if requested) prints a symbol table listing on the standard list output device. It also checks for certain possible error conditions and prints error messages on the console device if necessary.

During pass two, the Assembler again examines each statement in the source program along with the symbol table and produces the binary object program. It outputs the object program to the standard punch output device and/or to the LG Area of the disc. If requested, the Assembler also prints the object program listing on the standard list output device. Additional error messages may also be printed on the console device.

If the source input is being read from a non-disc device, it is written on the disc at the start of pass 1; for pass 2, the source is then read from the disc. However, if there is not sufficient space available on the disc to do this, the source input will have to be read through the non-disc device at the start of pass 2. In such a case, the Assembler prints \$END ASMB PASS on the console device at the end of pass 1. The operator responds by reloading the source input into the non-disc device and then entering GO, ASMB through the console device.

## 1-2. SYMBOLIC ADDRESSING

Symbols may be used for referring to machine instructions, data, constants, and certain other pseudo operations. A symbol represents the address for a computer word in memory. A symbol is defined when it is used as a label for a location in the program, a name of a common storage segment, the label of a data storage area or constant, the label of an absolute or relocatable value, or a location external to the program.

Through use of simple arithmetic operators, symbols may be combined with other symbols or numbers to form an expression which may identify a location other than that specifically named by a symbol. Symbols appearing in operand expressions, but not specifically defined, and symbols that are defined more than once are considered to be in error by the Assembler.

## 1-3. MEMORY ADDRESSING

### 1-4. PAGING

The computer memory is logically divided into pages of 1024 words each. A page is defined as the largest block of memory which can be addressed directly by the memory address bits of a memory reference instruction (single-length). These memory reference instructions have 10 bits to specify a memory address, and thus the page size is 1024 locations (2000 octal). Octal addresses for each page, up to the maximum memory size, are shown in table 1-1.

Provision is made to address directly one of two pages: page zero (the base page, consisting of locations 00000 through 01777), and the current page (the page in which the instruction itself is located). Memory reference instructions include a bit (bit 10) reserved to specify one or the other of

these two pages. To address locations in any other page, indirect addressing is used. Page references are specified by bit 10 as follows:

Logic 0 = page zero (Z)

Logic 1 = current page (C)

### 1-5. INDIRECT ADDRESSING

All memory reference instructions reserve a bit to specify direct or indirect addressing. For single-length memory reference instructions, bit 15 of the instruction word is used; for extended arithmetic memory reference instructions, bit 15 of the address word is used. Indirect addressing uses the address part of the instruction to access another word in memory, which is taken as a new memory reference for the same instruction. This new address word is a full 16 bits long, 15 bits of address plus another direct-indirect bit. The 15-bit length of the address permits access to any location in memory. If bit 15 again specifies indirect addressing, still another address is obtained. This multiple-step indirect addressing may be done to any number of levels. The first address obtained in the indirect phase which does not specify another indirect level becomes the effective address for the instruction. Direct or indirect addressing is specified by bit 15 as follows:

Logic 0 = direct

Logic 1 = indirect

### 1-6. PROGRAM RELOCATION

Relocatable programs are relocated at absolute addresses by the relocating loader.

Relocatable code assumes a starting location of 00000, and this location is termed the relative, or *relocatable* origin. The absolute origin (termed the relocation base) of a relocatable program is determined by the loader. The value of the absolute origin is added to the zero-relative value of each operand address to obtain the absolute operand address. The absolute origin, and thus the values of every operand address, may vary each time the program is loaded.

A relocatable program may be composed of several independently assembled or compiled subprograms. Each of the subprograms will have a relative origin of 00000. Each subprogram is then assigned a unique absolute origin upon being loaded.

The operand values produced by the Assembler may be *program* relocatable, *base page* relocatable, or *common* relocatable. Each of these segments of the program has a

separate relocation base or origin. Operands that are references to locations in the main portion of the program are incremented by the program relocation base; those referring to the base page, by the base page relocation base; and those referring to common storage, by the common relocation base.

If the loader or system generator encounters an operand that is a reference to a location in a page other than the current page or base page, a link is established. A link is a word in the base page or current page which is allocated to contain the full 15-bit address of the referenced location. The address of the link is then substituted as an indirect address in the instruction in the current page. If other similar references are made to the same location, they are linked through the same link.

Table 1-1. Logical Memory Address/Pages

| MEMORY SIZE | PAGE | OCTAL ADDRESSES |

|-------------|------|-----------------|

| 4K          | 0    | 00000 to 01777  |

|             | 1    | 02000 to 03777  |

|             | 2    | 04000 to 05777  |

|             | 3    | 06000 to 07777  |

| 8K          | 4    | 10000 to 11777  |

|             | 5    | 12000 to 13777  |

|             | 6    | 14000 to 15777  |

|             | 7    | 16000 to 17777  |

| 12K         | 8    | 20000 to 21777  |

|             | 9    | 22000 to 23777  |

|             | 10   | 24000 to 25777  |

|             | 11   | 26000 to 27777  |

| 16K         | 12   | 30000 to 31777  |

|             | 13   | 32000 to 33777  |

|             | 14   | 34000 to 35777  |

|             | 15   | 36000 to 37777  |

| 24K         | 16   | 40000 to 41777  |

|             | 17   | 42000 to 43777  |

|             | 18   | 44000 to 45777  |

|             | 19   | 46000 to 47777  |

| 32K         | 20   | 50000 to 51777  |

|             | 21   | 52000 to 53777  |

|             | 22   | 54000 to 55777  |

|             | 23   | 56000 to 57777  |

|             | 24   | 60000 to 61777  |

|             | 25   | 62000 to 63777  |

|             | 26   | 64000 to 65777  |

|             | 27   | 66000 to 67777  |

|             | 28   | 70000 to 71777  |

|             | 29   | 72000 to 73777  |

|             | 30   | 74000 to 75777  |

|             | 31   | 76000 to 77777  |

## 1-7. PROGRAM LOCATION COUNTER

The Assembler maintains a counter, called the program location counter, that assigns consecutive memory addresses to source statements.

The initial value of the program location counter is established according to the use of either the NAM or ORG pseudo operation at the start of the program. The NAM operation causes the program location counter to be set to zero for a relocatable program; the ORG operation specifies the absolute starting location for an absolute program.

Through use of the ORB pseudo operation a relocatable program may specify that certain operations or data areas be allocated to the base page. If so, a separate counter, called the base page location counter, is used in assigning these locations.

"ASMB," is in positions 1-5 of the statement. Following the comma are one or more parameters, in any order: The parameters are shown in table 1-2. If output to the LG Area is specified in the ON,ASMB directive (ON,ASMB, . . . ,99), the control statement does not require the B parameter for relocatable output to be generated onto the LG Area. (Only specify B if punched form required.)

Since they contradict one another, F and X must never appear in the control statement for the same source program. If neither A nor R is specified, R is assumed. If T is omitted, the symbol table listing will *not* be printed. If B is omitted, the object program will *not* be punched on the standard punch output device (it may, however, be retained in the LG Area of the disc if so specified in the ON,ASMB RTE directive).

## 1-8. SOURCE PROGRAM

Figure 1-1 shows an assembler coding form and the code for a simple program which counts the number of 1's and 0's in the A-register. The first statement is the control statement, and contains the assembly options R (for a relocatable source program), B (the program is to be punched on the standard punch device in binary form), L (a program listing is to be printed on the standard list device), and T (a listing of the symbol table is to be printed on the standard list device). See paragraph 1-9 and table 1-2 for a further discussion of control statement parameters.

Following the control statement, the first statement of the program (other than remarks or a HED statement) must be a NAM statement for a relocatable program or an ORG statement to indicate the origin of an absolute program. The last statement must be an END statement and may contain a transfer address for the start of a relocatable program. Each statement is terminated by an end-of-statement or end-of-record mark if not on cards.

## 1-9. ASSEMBLY OPTIONS

The control statement must be the first statement in the source program and it specifies the desired assembly options:

ASMB, $p_1, p_2, \dots, p_n$

## 1-10. BINARY OUTPUT

The binary output is defined by the ASMB control statement. The binary output includes the instructions translated from the source program. It does not include system subroutines referenced within the source program (arithmetic subroutine calls, IOC., DIO., ENTR, etc.).

## 1-11. SYMBOL TABLE

Figure 1-2 shows the symbol table listing produced when the source program was assembled. Columns 1 through 5 contain the name of the label. The R in column 7 specifies that the source program is relocatable and columns 9 through 14 contain the location (in octal) where the label symbol is stored. (In the example shown in figure 1-2, the locations are relative because the source program is relocatable.)

The characters that designate an external symbol or type of relocation for the Operand field or the symbol are as follows:

| Character | Relocation Base       |

|-----------|-----------------------|

| Blank     | Absolute              |

| R         | Program relocatable   |

| C         | Common relocatable    |

| X         | External symbol       |

| B         | Base page relocatable |

| S         | Substitution code     |

Figure 1-1. Source Program

Table 1-2. Control Statement Parameters

| PARAMETER | MEANING                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A         | Absolute assembly. The addresses generated by the Assembler are to be interpreted as absolute locations in memory. The program is a complete entity; external symbols, common storage references and entry points are not permitted. Note that an absolute program <i>cannot</i> be executed on RTE.                                                                                                                                            |

| R         | Relocatable assembly. The object program may be loaded anywhere in memory. All operands which refer to memory locations are automatically adjusted as the program is loaded. Operands referring to memory locations greater than 1777 <sub>8</sub> must be relocatable expressions. Programs may contain external symbols and entry points, and may refer to common storage.                                                                    |

| B         | Binary output. An absolute or relocatable object program is to be output on the standard punch device.                                                                                                                                                                                                                                                                                                                                          |

| L         | List output. A program listing is to be printed on the standard list device. Error messages will still be printed if "L" is not specified.                                                                                                                                                                                                                                                                                                      |

| T         | Symbol table print. A listing of the symbol table is to be printed on the standard list output device.                                                                                                                                                                                                                                                                                                                                          |

| N,Z       | Selective assembly. Sections of the program are to be included or excluded at assembly time depending upon the option specified. See the descriptions of the IFN and IFZ pseudo instructions in Section IV of this manual.                                                                                                                                                                                                                      |

| C         | Cross reference table print. All references to statement labels, external symbols, and user-defined opcodes are to be listed on the standard list output device after the end of the assembly.                                                                                                                                                                                                                                                  |

| F         | Floating point instructions. The floating point machine instructions are to be used instead of the software simulation routines for the following floating point operations: FIX, FLT, FDV, FMP, FAD, and FSB.                                                                                                                                                                                                                                  |

| X         | No EAU hardware. Signifies that the object program will be executed on a machine which does <i>not</i> have the Extended Arithmetic Unit (EAU) hardware. This parameter prevents the use of the following EAU instructions: ASR, ASL, RRR, RRL, LSR, LSL, and SWP. In addition, it causes all occurrences of the MPY, DIV, DLD, and DST instructions to be substituted with a call to the appropriate subroutine in the floating point library. |

PAGE 0001

Relocat

```

0001  b

LOOP  R 000001

COUNT R 000005

BIT0  R 000010

BIT1  R 000013

BIT2  R 000016

MORE  R 000022

BIT3  R 000023

LESS1 R 000024

LESS2 R 000026

EVEN  R 000027

** NO ERRORS*

```

ASMB,R,B,L,T

Figure 1-2. Symbol Table Listing

## 1-12. LIST OUTPUT

| Columns | Content                                                     |

|---------|-------------------------------------------------------------|

| 1-4     | Source statement sequence number generated by the Assembler |

| 5-6     | Blank                                                       |

| 7-11    | Location (octal)                                            |

| 13-18   | Object code word in octal                                   |

| 19      | Relocation or external symbol indicator                     |

| 20      | Blank                                                       |

| 21-80   | First 60 characters of source statement                     |

Lines consisting entirely of comments (i.e., \* in column 1) are printed as follows:

| Columns | Content                          |

|---------|----------------------------------|

| 1-4     | Source statement sequence number |

| 5-80    | Up to 76 characters of comments  |

At the end of each pass, the following is printed on the list device:

```

Pass 1 =

** NO ERRORS PASS#1 **RTE ASMB YYMMDD**

or

**nnnn ERRORS PASS#1 **RTE ASMB YYMMDD**

Pass 2 =

** NO ERRORS *TOTAL **RTE ASMB YYMMDD**

or

**nnnn ERRORS *TOTAL **RTE ASMB YYMMDD**

```

The value *nnnn* indicates the number of errors. Pass 2 error count includes the total error count of pass 1 and pass 2. YYMMDD is the year, month, and day of the current revision of the software.

If there are errors, the message PG *xxx* is printed on the list device immediately preceding the \*\*nnnn ERRORS\* message, where *xxx* is the page number where the final error was detected. The same message appears in the listing following each error and it points to the page number where the previous error was detected. The backwards pointer following the first error in the program is PG 000.

# SOURCE STATEMENT FORMAT

SECTION

II

A source language statement consists of a label, an operation code, an operand (or operands) and comments. The label is used when needed as a reference by other statements. The operation code may be a mnemonic machine operation or an assembly directing pseudo code. An operand may be an expression consisting of an alphanumeric symbol, a number, a special character, or any of these combined by arithmetic operators. An operand may also be a literal. Indicators may be appended to an operand to specify certain functions such as indirect addressing. The comments portion of the statement is optional.

## 2-1. STATEMENT OF CHARACTERISTICS

The fields of the source statement appear in the following order:

1. Label

2. Opcode

3. Operands

4. Comments

## 2-2. FIELD DELIMITERS

One or more spaces separate the fields of a statement. A single space as the first character of a statement signifies that there is no label for this statement.

## 2-3. CHARACTER SET

The characters that may appear in a statement are as follows:

- A through Z

- 0 through 9

- . (period)

- \* (asterisk)

- + (plus)

- (minus)

- , (comma)

- = (equals)

- () (parentheses)

- (space)

Any other ASCII characters may appear in the Comments field. (See Appendix A.)

The letters A through Z, the numbers 0 through 9, and the period may be used in an alphanumeric symbol. In the first position in the Label field, an asterisk indicates a comment; in the Operand field, it represents the value of the program location counter for the current instruction. The plus and minus are used as operators in arithmetic address expressions. The comma separates several operation codes, or an expression and an indicator in the Operand field. An equals sign indicates a literal value. The parentheses are used only in the COM pseudo instruction.

Spaces separate fields of a statement and operands in a multi-operand field. They may also be used to enhance the appearance of the listing. Within a field they may be used freely when following +, -, ., or (.

## 2-4. STATEMENT LENGTH

A statement may contain up to 80 characters including blanks, but excluding the end-of-statement mark.

## 2-5. LABEL FIELD

The Label field identifies the statement and may be used as a reference point by other statements in the program.

The field starts in position one of the statement. It is terminated by space. A space in position one signifies that the statement is unlabeled.

## 2-6. LABEL SYMBOL

A label may have one to five characters consisting of A through Z, 0 through 9, and the period.

Note: The Assembler allows the use of certain other characters in the Label field. However, they are reserved for use in Hewlett-Packard programs.

The first character must be alphabetic or a period. A label of more than five characters could be entered on the source statement, but the Assembler flags this condition as an error and truncates the label from the right to five characters. Some examples are shown in figure 2-1.

Each label must be unique within the program; two or more statements may not have the same symbolic name. Names which appear in the Operand field of an EXT or COM pseudo instruction may not also be used as statement labels

in the same subprogram. However, names appearing in a COM pseudo instruction may be defined as entry points in an ENT pseudo instruction. Some examples are shown in figure 2-2.

## 2-7. ASTERISK

An asterisk in position one indicates that the entire statement is a comment. Positions 2 through 80 are available; however, positions 1 through 76 only are printed as part of the assembly listing. An asterisk within a label is illegal in any position

## 2-8 OPCODE FIELD

The operation code defines an operation to be performed by the computer or the Assembler. The Opcode field follows the Label field and is separated from it by at least one space. If there is no label, the operation code may begin anywhere after position one. The Opcode field is terminated by a space immediately following an operation code. Operation codes are organized in the following categories:

### Machine operation codes:

- Memory Reference

- Register Reference

- Input/Output, Overflow, and Halt

- Extended Arithmetic Unit

- Floating Point

- Memory Mapping

- Decimal Arithmetic

### Pseudo operation codes:

- Assembler control

- Object program linkage

- Address and symbol definition

- Constant definition

- Storage allocation

- Arithmetic subroutine calls

- Assembly Listing Control

- Define User Opcodes

- Code-replacement definition

Operation codes are discussed in detail in Sections III and IV.

## 2-9. OPERAND FIELD

The meaning and format of the Operand field depend on the type of operation code used in the source statement. The

field follows the Opcode field and is separated from it by at least one space. If more than one operand is required, they are separated from one another by at least one space.

An Operand may contain an expression consisting of one of the following:

- Single symbolic term

- Single numeric term

- Asterisk

- Combination of symbolic terms, numeric terms, and the asterisk joined by the arithmetic operators + and -.

An expression may be followed by a comma, an indirect addressing indicator (see paragraph 2-20), and a Clear Flag indicator (see paragraph 2-21). Programs may also contain a literal value in the Operand field. (See paragraph 2-19.)

## 2-10. SYMBOLIC TERMS

A symbolic term may be one to five characters consisting of A through Z, 0 through 9, and the period. The first character must be alphabetic or a period. Some examples are shown in figure 2-3.

A symbol used in the Operand field must be a symbol that is defined elsewhere in the program in one of the following ways:

- As a label in the Label field of a machine operation or a user-defined instruction

- As a label in the Label field of a BSS, ASC, DEC, DEX, OCT, DEF, BYT, ABS, EQU, DBL, DBR or REP pseudo operation

- As a name in the Operand field of a COM or EXT pseudo operation

- As a label in the Label field of an arithmetic subroutine pseudo operation

The value of a symbol is absolute or relocatable depending on the assembly option selected by the user. The Assembler assigns a value to a symbol as it appears in one of the above fields of a statement. If a program is to be loaded in absolute form, the values assigned by the Assembler remain fixed. If the program is to be relocated, the actual value of a symbol is established on loading. A symbol may be assigned an absolute value through use of the EQU pseudo instruction.

A symbolic term may be preceded by a plus or minus sign. If preceded by a plus or no sign, the symbol refers to its associated value. If preceded by a minus sign, the symbol refers to the two's complement of its associated value. A single negative symbolic operand may be used only with the ABS pseudo operation.

| PROGRAMMER |           | DATE    |  | PROGRAM   |             |    |    |    |                                                                                       |    |    |    |    |    |  |

|------------|-----------|---------|--|-----------|-------------|----|----|----|---------------------------------------------------------------------------------------|----|----|----|----|----|--|

|            |           |         |  | STATEMENT |             |    |    |    |                                                                                       |    |    |    |    |    |  |

| Label      | Operation | Operand |  | 20        | 25          | 30 | 35 | 40 | Comments                                                                              | 45 | 50 | 55 | 60 | 65 |  |

|            | LDA       |         |  |           | NO LABEL    |    |    |    |                                                                                       |    |    |    |    |    |  |

| .ABCD      |           |         |  |           | VALID LABEL |    |    |    |                                                                                       |    |    |    |    |    |  |

| .1234      |           |         |  |           | VALID LABEL |    |    |    |                                                                                       |    |    |    |    |    |  |

| A.123      |           |         |  |           | VALID LABEL |    |    |    |                                                                                       |    |    |    |    |    |  |

| .          |           |         |  |           | VALID LABEL |    |    |    |                                                                                       |    |    |    |    |    |  |

|            |           |         |  |           |             |    |    |    |                                                                                       |    |    |    |    |    |  |

| 1.ABC      |           |         |  |           |             |    |    |    | ILLEGAL LABEL - FIRST CHARACTER NUMERIC                                               |    |    |    |    |    |  |

| ABC123     |           |         |  |           |             |    |    |    | ILLEGAL LABEL - TOO LONG TRUNCATED TO ABC12                                           |    |    |    |    |    |  |

| A*BC       |           |         |  |           |             |    |    |    | ILLEGAL LABEL - ASTERISK NOT ALLOWED IN LABEL                                         |    |    |    |    |    |  |

| ABC        |           |         |  |           |             |    |    |    | NO LABEL - SPACE IN FIRST POSITION - ASSEMBLER ATTEMPTS TO INTERPRET ABC AS AN OPCODE |    |    |    |    |    |  |

Figure 2-1. Label Examples

| PROGRAMMER |           | DATE             |  | PROGRAM   |             |    |    |    |                                    |    |    |    |    |    |  |

|------------|-----------|------------------|--|-----------|-------------|----|----|----|------------------------------------|----|----|----|----|----|--|

|            |           |                  |  | STATEMENT |             |    |    |    |                                    |    |    |    |    |    |  |

| Label      | Operation | Operand          |  | 20        | 25          | 30 | 35 | 40 | Comments                           | 45 | 50 | 55 | 60 | 65 |  |

|            | COM       | ACOM(20), BC(30) |  |           |             |    |    |    |                                    |    |    |    |    |    |  |

| LB         | EQU       | 160              |  |           | VALID LABEL |    |    |    |                                    |    |    |    |    |    |  |

|            | ENT       | ABC              |  |           |             |    |    |    |                                    |    |    |    |    |    |  |

|            | EXT       | XLI, XL2         |  |           |             |    |    |    |                                    |    |    |    |    |    |  |

| START      | LDA       | LB               |  |           | VALID LABEL |    |    |    |                                    |    |    |    |    |    |  |

| N25        |           |                  |  |           | VALID LABEL |    |    |    |                                    |    |    |    |    |    |  |

|            |           |                  |  |           |             |    |    |    |                                    |    |    |    |    |    |  |

| XL2        |           |                  |  |           |             |    |    |    | ILLEGAL LABEL - USED IN EXT        |    |    |    |    |    |  |

| BC         |           |                  |  |           |             |    |    |    | ILLEGAL LABEL - USED IN COM        |    |    |    |    |    |  |

| N25        |           |                  |  |           |             |    |    |    | ILLEGAL LABEL - PREVIOUSLY DEFINED |    |    |    |    |    |  |

Figure 2-2. Label Usage Examples

## 2-11. NUMERIC TERMS

A numeric term may be decimal or octal. A decimal number is represented by one to five digits within the range 0 to 32767. An octal number is represented by one to six octal digits followed by the letter B (0 to 177777B).

If a numeric term is preceded by a plus or no sign, the binary equivalent of the number is used in the object code. If preceded by a minus sign, the two's complement of the binary equivalent is used. A negative numeric operand may be used only with the DEX, DEC, OCT, BYT and ABS pseudo operations.

For a memory reference instruction in an absolute program, the maximum value of a numeric operand depends on the type of machine or pseudo instruction. In a relocatable program, the value of a numeric operand may not exceed 1777<sub>8</sub>. Numeric operands are absolute. Their value is not altered by the assembler or the loader.

## 2-12. ASTERISK

An asterisk in the Operand field refers to the value in the program location counter at the time the source program statement is encountered. The asterisk is considered a relocatable term in a relocatable program.

## 2-13. EXPRESSION OPERATORS

The asterisk, symbols, and numbers may be joined by the arithmetic operators + and - to form arithmetic address expressions. The Assembler evaluates an expression and produces an absolute or relocatable value in the object code. Some examples are shown in figure 2-4.

## 2-14. EVALUATION OF EXPRESSIONS

An expression consisting of more than one operand is reduced to a single value. In expressions containing more than one operator, evaluation of the expression proceeds from left to right. The algebraic expression A-(B-C+5) must be represented in the Operand field as A-B+C-5. Parentheses are not permitted in operand expressions.

The range of values that may result from an operand expression depends on the type of operation. The Assembler evaluates expressions as follows:<sup>†</sup>

Pseudo Operations: modulo  $2^{15}$ -1

Memory Reference: modulo  $2^{10}$ -1

Input/Output:  $2^6$  - 1 (maximum value)

## 2-15. EXPRESSION TERMS

The terms of an expression are the numbers and the symbols appearing in it. Decimal and octal integers, and sym-

bols defined as being absolute in an EQU pseudo operation are absolute terms. The asterisk and all symbols that are defined in the program are relocatable or absolute depending on the type of assembly. (RTE Assembler allows externals with offset and indirect external references.)

Within a relocatable program, terms may be program relocatable or common relocatable or base page relocatable. A symbol that names an area of common storage is a common relocatable term. A symbol that is defined in any statement other than COM or EQU is a relocatable term. Within one expression all relocatable terms must be program relocatable, common relocatable or base page relocatable; the types may not be mixed.

## 2-16. ABSOLUTE AND RELOCATABLE EXPRESSIONS

An expression is absolute if its value is unaffected by program relocation. An expression is relocatable if its value changes according to the location into which the program is loaded. In an absolute program, all expressions are absolute. In a relocatable program, an expression may be program relocatable, common relocatable, base page relocatable, or absolute (if less than 2000<sub>8</sub>) depending on the definition of the terms composing it.

**2-17. ABSOLUTE EXPRESSIONS.** An absolute expression may be any arithmetic combination of absolute terms. It may contain relocatable terms alone, or in combination with absolute terms. If relocatable terms appear, there must be an even number of them; they must be of the same type; and they must be paired by sign (a negative term for each positive term). The paired terms do not have to be contiguous in the expression. The pairing of terms by type cancels the effect of relocation; the value represented by a pair remains constant.

An absolute expression reduces to a single absolute value. The value of an absolute multi-term expression may be negative only for ABS pseudo operations. A single numeric term also may be negative in an OCT, DEX, BYT, or DEC pseudo instruction. In a relocatable program the value of an absolute expression must be less than 2000<sub>8</sub> for instructions that reference memory locations (Memory Reference, DEF, Arithmetic subroutine calls, etc.).

If  $P_1$  and  $P_2$  are program relocatable terms;  $C_1$  and  $C_2$ , common relocatable; and  $A$ , an absolute term; then the following are absolute terms:

|                 |                 |                  |

|-----------------|-----------------|------------------|

| $A - C_1 + C_2$ | $A - P_1 + P_2$ | $C_1 - C_2 + A$  |

| $A + A$         | $P_1 - P_2$     | $-C_1 + C_2 + A$ |

| $* - P_1$       | $-P_1 + P_2$    | $-A - P_1 + P_2$ |

<sup>†</sup>The evaluation of expressions by the Assembler is compatible with the addressing capability of the hardware instructions (e.g., up to 32K words through Indirect Addressing). The user must take care not to create addresses which exceed the memory size of the particular configuration.

Figure 2-3. Symbolic Operand Examples

|            |                                                                     |

|------------|---------------------------------------------------------------------|

| LDA SYM+6  | ADD 6 TO THE VALUE OF SYM                                           |

| ADA SYM-3  | SUBTRACT 3 FROM THE VALUE OF SYM                                    |

| .          |                                                                     |

| .          |                                                                     |

| JMP x+5    | ADD 5 TO THE CONTENTS OF THE<br>PROGRAM LOCATION COUNTER.           |

| .          |                                                                     |

| .          |                                                                     |

| STB -A+C-4 | ADD - VALUE OF A, THE VALUE OF C<br>AND SUBTRACT 4.                 |

| .          |                                                                     |

| .          |                                                                     |

| STA XTA-x  | SUBTRACT VALUE OF PROGRAM<br>LOCATION COUNTER FROM VALUE OF<br>XTA. |

Figure 2-4. Expression Operator Examples

The asterisk is program relocatable.

**2-18. RELOCATABLE EXPRESSIONS.** A relocatable expression is one whose value is changed by the loader. All relocatable expressions must have a positive value.

A relocatable expression may contain an odd number of relocatable terms, alone, or in combination with absolute terms. All relocatable terms must be of the same type. Terms must be paired by sign with the odd term being positive.

A relocatable expression reduces to a single positive relocatable term, adjusted by the values represented by the absolute terms and paired relocatable terms associated with it.

If  $P_1$ ,  $P_2$ , and  $P_3$  are program relocatable terms;  $C_1$ ,  $C_2$  and  $C_3$ , common relocatable; and  $A$ , an absolute term; then the following are relocatable terms:

|                   |                       |                         |

|-------------------|-----------------------|-------------------------|

| $P_1 - A$         | $C_1 - A$             | $P_1 - P_2 + *$         |

| $P_1 - P_2 + P_3$ | $C_1 - C_2 + C_3$     | $C_1 + A$               |

| $* + A$           | $* - P_1 + P_2$       | $* - A$                 |

| $P_2 + A$         | $A + C_1$             | $- A - P_1 + P_2 + P_3$ |

| $P_1 - *$         | $C_1 - C_2 + C_3 - A$ | $A + *$                 |

|                   |                       | $- C_1 + C_2 + C_3$     |

## 2-19. LITERALS

Literal values may be specified as operands in relocatable programs. (Literals are not allowed in absolute programs.) The Assembler converts the literal to its binary value, assigns an address to it, and substitutes this address as the operand. Locations assigned to literals are those immediately following the last location used by the program.

A literal is specified by using an equal sign and a one-character identifier defining the type of literal. The actual literal value is specified immediately following this identifier; no spaces may intervene.

The identifiers are:

- =D a decimal integer, in the range -32767 to 32767, including zero.†

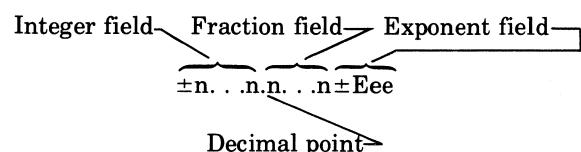

- =F a floating point number; any positive or negative real number in the range  $10^{-38}$  to  $10^{38}$ , including zero.†

- =B an octal integer, one to six digits,  $b_1 b_2 b_3 b_4 b_5 b_6$ , where  $b_1$  may be 0 or 1, and  $b_2 - b_6$  may be 0 to 7.†

- =A two ASCII characters.†

- =L an expression which, when evaluated, will result in an absolute value. All symbols appearing in the expression must be previously defined.

†See CONSTANT DEFINITION, Section IV.

If the same literal is used in more than one instruction or if different literals have the same value (e.g., =B100 and =D64), only one value is generated, and all instructions using these literals refer to the same location.

Literals may be specified only in the following memory reference, register reference, EAU, and pseudo instructions:

|     |     |     |                        |

|-----|-----|-----|------------------------|

| ADA | CPA | MBT | may use =D, =B, =A, =L |

| ADB | CPB | MDB |                        |

| ADX | DIV | MPY |                        |

| ADY | IOR | MVW |                        |

| AND | LDA | SBS |                        |

| CBS | LDB | TBS |                        |

| CBT | LDX | XOR |                        |

| CMW | LDY |     |                        |

| DLD | FDV | FSB | may use =F             |

| FMP | FAD |     |                        |

Examples are as follows:

|                    |                                                                             |

|--------------------|-----------------------------------------------------------------------------|

| LDA =D7980         | A-Register is loaded with the binary equivalent of $7980_{10}$ .            |

| IOR =B777          | Inclusive OR is performed with contents of A-Register and $777_8$ .         |

| LDA =ANO           | A-Register is loaded with binary representation of ASCII characters NO.     |

| LDB =LZETZ-ZOOM+68 | B-Register is loaded with the absolute value resulting from the expression. |

| FMP =F39.75        | Contents of A- and B-Registers multiplied by floating point constant 39.75. |

## 2-20. INDIRECT ADDRESSING

The HP computers provide an indirect addressing capability for memory reference instructions. The operand portion of an indirect instruction contains the address of another location. The secondary location may be the operand or it may be indirect also and give yet another location, and so forth. The chaining ceases when a location is encountered that does not contain an indirect address. Indirect addressing provides a simplified method of address modifications as well as allowing access to any location in core. See Section I, paragraph 1-5 for a further discussion of indirect addressing.

The Assembler allows specification of indirect addressing by appending a comma and the letter I to any memory

reference operand other than one referring to an external symbol. The actual address of the instruction may be given in a DEF pseudo operation; this pseudo operation may also be used to indicate further levels of indirect addressing. An example is shown in figure 2-5.

A relocatable assembly language program, however, may be designed without concern for the pages in which it will be stored; indirect addressing is not required in the source language. When the program is being loaded, the loader provides indirect addressing whenever it detects an operand which does not fall in the current page or the base page. The loader substitutes a reference to a program link location (established by the loader in either the base page or the current page) and then stores an indirect address in the particular program link location. If the program link location is in the base page, all references to the same operand from other pages will be via the same link location.

**Note:** The Basic Control System provides program links to the base page only (not the current page).

## 2-21. CLEAR FLAG INDICATOR

The majority of the input/output instructions can alter the status of the input/output interrupt flag after execution or

after the particular test is performed. In source language, this function is selected by appending a comma and a letter C to the Operand field. Some examples are shown in figure 2-6.

## 2-22. COMMENTS FIELD

The Comments field allows the user to transcribe notes on the program that will be listed with source language coding on the output produced by the Assembler. The field follows the Operand field and is separated from it by at least one space. The end-of-record mark, the end-of-statement mark,

(CR) (LF), or the 80th character of a statement terminates the field. The statement length should not exceed 60 characters, the width of the source language portion of the listing. A whole line (up to 76 characters), however, can be specified as a comment by inserting an asterisk in the first position. On the list output, statements consisting entirely of comments begin in position 5 rather than 21 as with other source statements. Any characters beyond the above limits will not appear on the listing.

If there is no operand present, the Comments field should be omitted in the NAM and END pseudo operations and in the input/output statements, SOC, SOS, and HLT. If a comment is used, the Assembler attempts to interpret it as an operand. This limitation applies also to multi-operand instructions.

|     |            |                                 |

|-----|------------|---------------------------------|

| AB  | LDA SAM, I | EACH TIME THE ISZ IS EXECUTED,  |

| AC  | ADA SAM, I | THE EFFECTIVE OPERAND OF AB AND |

| AD  | ISZ SAM    | AC CHANGE ACCORDINGLY.          |

| .   |            |                                 |

| .   |            |                                 |

| .   |            |                                 |

| SAM | DEF ROGER  |                                 |

Figure 2-5. Indirect Addressing Example

|            |                                                                  |

|------------|------------------------------------------------------------------|

| STC 13B, C | SET CONTROL AND CLEAR THE FLAG OF SELECT CODE 13 (OCTAL)         |

| OTB 16B, C | CLEAR FLAG OF SELECT CODE 16 (OCTAL) ALONG WITH OUTPUT TO DEVICE |

Figure 2-6. Clear Flag Examples

# MACHINE INSTRUCTIONS

The Assembler language machine instruction codes take the form of three-letter mnemonics. Each source statement corresponds to a machine operation in the object program produced by the Assembler.

Notation used in representing source language instruction is as follows:

|          |                                                                  |

|----------|------------------------------------------------------------------|

| label    | Optional statement label                                         |

| m        | Memory location — an expression                                  |

| I        | Indirect addressing indicator                                    |

| sc       | Select code — an expression                                      |

| C        | Clear interrupt flag indicator                                   |

| comments | Optional comments                                                |

| [ ]      | Brackets defining a field or portion of a field that is optional |

| { }      | Brackets indicating that one of the set may be selected.         |

| lit      | literal                                                          |

## 3-1. MEMORY REFERENCE

The memory reference instructions perform arithmetic, logical, jump, word manipulation, byte manipulation, and bit manipulation operations on the contents of memory locations and the registers. An instruction may directly address the  $2048_{10}$  words of the current and base pages. If required, indirect addressing may be used to refer to all  $32,768_{10}$  words of memory. Expressions in the Operand field are evaluated modulo  $2^{10}$ .

External memory references may be made with + or - offsets, with indirects or both.

If the program is to be assembled in relocatable form, the Operand field may contain relocatable or absolute expressions; however, absolute expressions must be less than  $2000_8$  in value. If the program is to be assembled in absolute form, the Operand field may contain any expression which is consistent with the location of the program. Literals may not be used in absolute programs. Absolute programs must be complete entities; they may not refer to external subroutines or to common storage.

## 3-2. JUMP AND INCREMENT-SKIP

Jump and Increment-Skip instructions may alter the normal sequence of program execution.

|       |     |       |          |

|-------|-----|-------|----------|

| label | JMP | m [I] | comments |

|-------|-----|-------|----------|

Jump to m. Jump indirect inhibits interrupt until the transfer of control is complete, or three levels of indirecting have occurred.

|       |     |       |          |

|-------|-----|-------|----------|

| label | JSB | m [I] | comments |

|-------|-----|-------|----------|

Jump to subroutine. The address for label+1 is placed into the location represented by m and control transfers to m+1. On completion of the subroutine, control may be returned to the normal sequence by performing a JMP m,I.

|       |     |       |          |

|-------|-----|-------|----------|

| label | ISZ | m [I] | comments |

|-------|-----|-------|----------|

Increment, then skip if zero. ISZ adds 1 to the contents of m. If m then equals zero, the next instruction in memory is skipped.

## 3-3. ADD, LOAD AND STORE

Add, Load, and Store instructions transmit and alter the contents of memory and of the A- and B-Registers. A litera, indicated by "lit", may be either =D, =B, =A, or =L type. See Section II, paragraph 2-19 for a further discussion of literals.

|       |     |                  |          |

|-------|-----|------------------|----------|

| label | ADA | { m [I] }<br>lit | comments |

|-------|-----|------------------|----------|

Add the contents of m to A.

|       |     |                  |          |

|-------|-----|------------------|----------|

| label | ADB | { m [I] }<br>lit | comments |

|-------|-----|------------------|----------|

Add the contents of m to B.

|       |     |                  |          |

|-------|-----|------------------|----------|

| label | LDA | { m [I] }<br>lit | comments |

|-------|-----|------------------|----------|

Load A with the contents of m.

|       |     |                  |          |

|-------|-----|------------------|----------|

| label | LDB | { m [I] }<br>lit | comments |

|-------|-----|------------------|----------|

Load B with the contents of m.

|       |     |        |          |

|-------|-----|--------|----------|

| label | STA | m [,I] | comments |

|-------|-----|--------|----------|

Store contents of A in m.

|       |     |        |          |

|-------|-----|--------|----------|

| label | STB | m [,I] | comments |

|-------|-----|--------|----------|

Store contents of B in m.

In each instruction, the contents of the sending location is unchanged after execution.

### 3-4. LOGICAL OPERATIONS

The logical instructions allow bit manipulation and the comparison of two computer words.

|       |     |                   |          |

|-------|-----|-------------------|----------|

| label | AND | { m [,I]<br>lit } | comments |

|-------|-----|-------------------|----------|

The logical product ("AND") of the contents of m and the contents of A are placed in A.

|       |     |                   |          |

|-------|-----|-------------------|----------|

| label | XOR | { m [,I]<br>lit } | comments |

|-------|-----|-------------------|----------|

The modulo-two sum (exclusive "or") of the bits in m and the bits in A is placed in A.

|       |     |                   |          |

|-------|-----|-------------------|----------|

| label | IOR | { m [,I]<br>lit } | comments |

|-------|-----|-------------------|----------|

The logical sum (inclusive "or") of the bits in m and the bits in A is placed in A.

|       |     |                   |          |

|-------|-----|-------------------|----------|

| label | CPA | { m [,I]<br>lit } | comments |

|-------|-----|-------------------|----------|

Compare the contents of m with the contents of A. If they differ, skip the next instruction; otherwise, continue.

|       |     |                   |          |

|-------|-----|-------------------|----------|

| label | CPB | { m [,I]<br>lit } | comments |

|-------|-----|-------------------|----------|

Compare the contents of m with the contents of B. If they differ, skip the next instruction; otherwise, continue.

### 3-5. WORD PROCESSING (21MX ONLY)

The word processing instructions allow the user to move a series of data words from one array in memory to another or to compare (word-by-word) the contents of two arrays in memory.

|       |     |                       |          |

|-------|-----|-----------------------|----------|

| label | MVW | { literal<br>m [,I] } | comments |

|-------|-----|-----------------------|----------|

Move words. The A-register contains the starting (lowest) word address of the source array. The B-register contains the starting (lowest) word address of the destination array. The number of words to be moved is specified by *literal* or by the value contained in *m [,I]*. The specified number of words are moved from the source array into the destination array. As each word is moved, the A- and B-registers are incremented by one. The source array is not altered.

|       |     |                       |          |

|-------|-----|-----------------------|----------|

| label | CMW | { literal<br>m [,I] } | comments |

|-------|-----|-----------------------|----------|

Compare words. The A-register contains the starting (lowest) word address of array #1. The B-register contains the starting (lowest) word address of array #2. The number of word comparisons to be performed is specified by *literal* or by the value contained in *m [,I]*. The two arrays are compared word-by-word beginning at the specified addresses. The operation is finished when an inequality is detected or when the specified number of word comparisons have been performed. When the operation is finished, the A-register contains the word address of the last word in array #1 which was compared; the B-register contains the starting address of array #2 incremented by the "count" parameter (*literal* or the value in *m [,I]*). If the two arrays are equal, execution proceeds at the next sequential source language instruction (P+3). If array #1 is "less than" #2, execution proceeds at instruction P+4. If array #1 is "greater than" array #2, execution proceeds at instruction P+5. The two arrays are not altered.

### 3-6. BYTE PROCESSING (21MX ONLY)

The byte processing instructions allow the user to copy a data byte from memory into the A- or B-register, copy a data byte from the A- or B-register into memory, copy a series of data bytes from one array in memory to another, compare (byte-by-byte) the contents of two arrays in memory, or scan an array in memory for particular data bytes.

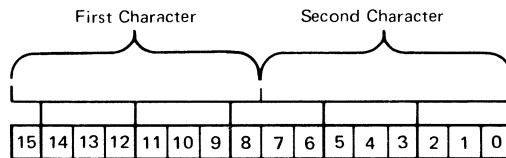

A *byte address* is defined as two times the word address of the memory location containing the particular data byte. If the byte location is the low order half of the memory location (bits 0-7), bit 0 of the byte address is set; if the byte location is the high order half of the memory location (bits 8-15), bit 0 of the byte address is clear.

| label | LBT | comments |

|-------|-----|----------|

|-------|-----|----------|

Load byte. The B-register contains the byte address of the byte to be loaded. The specified byte is copied from memory into bits 0-7 of the A-register (bits 8-15 of the A-register are set to zeros). The B-register is then incremented by one. The memory location is not altered.

| label | SBT | comments |

|-------|-----|----------|

|-------|-----|----------|