Die HP Precision Architecture ist eine Rechnerarchitektur mit vereinfachtem Befehlssatz, die den Rahmen bildet für die Hewlett-Packard-Systeme der neunziger Jahre und darüber hinaus. Die HP Precision Architecture bedient sich der RISC-Technologie, erweitert jedoch die Möglichkeiten dieses Prinzips noch beträchtlich. Die Prozessor-Hardware ist für die Ausführung der einfachen, häufig benötigten Funktionen optimiert, die Ausführung komplexer Funktionen fällt der Software zu. Befehle werden direkt aus der Hardware in einem einzigen, schnellen Zyklus ausgeführt. Dadurch entfällt der die Zentraleinheit belastende, komplizierte Umweg über einen Microcode. Der vereinfachte Befehlssatz ermöglicht es, HP-Systeme mit komplexem Befehlssatz auf den neuen Rechnern mit RISC-Architektur sehr effektiv zu emulieren; das bedeutet volle Softwarekompatibilität und somit bequeme Aufrüstung zu Systemen der neuen Technologie. Die HP Precision Architecture arbeitet mit voller 48- und virtueller 64-Bit-Adressierung, wodurch die Adressierbarkeit im Vergleich zu herkömmlichen Systemen mit 32-Bit-Adressierung wesentlich erweitert wird. Ein vorrangiges Ziel bei der Konzipierung der neuen Rechnerarchitektur war eine anwendungsgerechte Größenstaffelung zu erreichen, die es ermöglicht, kostengünstige Lösungen vom Tischcomputer bis hin zu Systemen mit der Leistung moderner Großrechner anzubieten. Die Möglichkeit des Mehrprozessorbetriebs, die Einbeziehung von Sonderfunktions-Coprozessoren, und die Unterstützung sehr schneller Gleitkommaberechnungen prädestinieren die HP Precision Architecture für kostengünstige und hochleistungsfähige Rechnerlösungen im kommerziellen und technischen Bereich.

## Merkmale

- Vereinfachter Befehlssatz

- 32-Bit-Befehle mit festem Format

- 48-Bit- oder virtuelle 64-Bit-Adressierung

- Befehlsausführung in einem einzigen Zyklus direkt aus der Hardware

- Mehrzweckregister

- 32 Steuerregister

- 8 Spaceregister

- Hauptspeicherzugriff nur bei Lade- oder Speichervorgängen

- Hardwareunterstützung für Gleitkomma- und Dezimalarithmetik

- Speicherverwaltung mit bedarfsorientierter seitenweiser Verlagerungsmöglichkeit

- Mehrprozessorbetrieb und Sonderfunktions-Coprozessoren

- Im Arbeitsspeicher abgebildetes Eingabe/Ausgabe-System

## Warum RISC?

Bei der Entwicklung von Rechnerarchitekturen ergaben sich in den letzten 20 Jahren immer komplexere Systeme. Diese Systeme mit umfangreichen und komplexen Befehlssätzen werden kurz CISC-Systeme (Complex Instruction Set Computer) genannt. Alle nach dem CISC-Prinzip konstruierten Rechner arbeiten normalerweise mit Mikrocode, in den die Befehle und komplexen Funktionen der höheren Programmiersprachen entschlüsselt werden müssen. Deshalb benötigen sie zur Befehlsausführung eine Vielzahl von Rechenzyklen.

Umfangreiche Untersuchungen in der Industrie und an führenden Universitäten haben jedoch ergeben, daß Rechner mit komplexem Befehlssatz während des größten Teils der Zeit einfache Addier-, Lade-, Speicher- und Verzweigungsbefehle ausführen. Komplexere Befehle, für die ein komplizierterer Prozessoraufbau nötig ist, werden relativ selten eingesetzt. Ergebnis: Leistungsverlust durch den Aufwand an Systemzeit für die Entschlüsselung der mikrocodierten Befehle und für die Steuerung durch die Hardware sogar bei einfachen und häufig ausgeführten Befehlen. Zur Ausführung eines Befehls werden dadurch mehr Rechenzyklen benötigt und alle Vorteile, die sich aus der direkten Unterstützung komplexer Funktionen durch einen komplexen Befehlssatz ergeben, zunichte gemacht.

Diese Erkenntnisse führten schließlich zum Prinzip des Rechnens mit vereinfachtem Befehlssatz (RISC = Reduced Instruction Set Computing) und zur Vereinfachung der Rechnerarchitektur. Die Grundidee des RISC-Prinzips ist, das System zu optimieren, indem einfache, häufig benutzte Befehle direkt in der Hardware in einem einzigen, schnellen Rechenzyklus ausgeführt werden. Die Weiterentwicklung dieses Prinzips wurde in die HP Precision Architecture eingebbracht. Hewlett-Packard ist somit in der Lage, eine flexible, ausbaufähige Architektur anzubieten, die die Rechnerleistung der jeweils eingesetzte Halbleitertechnologie maximiert. Außerdem kann das Preis-Leistungsverhältnis erheblich verbessert werden.

## Befehlsverzeichnis

Die HP Precision Architecture verwendet 140 Befehle mit festem Format und je 32 Bit Länge. Um einen möglichst einfachen Aufbau des Prozessors zu ermöglichen, werden direkt aus dem Befehlssatz nur einfache Operationen ausgeführt.

## Speicheransteuer-Befehle

Speicherzugriffe können nur über Lade- und Speicherbefehle erfolgen. Mit Ladebefehlen werden die für eine bestimmte Operation benötigten Operanden in ein Register der Zentraleinheit geladen; mit Speicherbefehlen werden die Ergebnisse in den Arbeitsspeicher übertragen. Die Ausschließlichkeit des Speicherzugriffs über Lade- und Speicherbefehle in Verbindung mit einer relativ großen Zahl von Registern in der Zentraleinheit ermöglichen es, daß häufig benötigte Operanden in der Zentraleinheit verbleiben. Die Anzahl der erforderlichen Zugriffe auf Cache- und Arbeitsspeicher wird dadurch auf ein Minimum reduziert und die Leistung des Rechners erheblich gesteigert.

## Arithmetische und logische Befehle

Die aus dem Befehlssatz verfügbaren arithmetischen und logischen Funktionen sind relativ einfach. Shift- und Addiere-Befehle beschleunigen zum Beispiel die Multiplikation von ganzen Zahlen, Lese-/Schreib-Befehle unterstützen wirksam die von den höheren Programmiersprachen verwendeten Bit-Verarbeitungsfunktionen. Kompliziertere Funktionen werden durch die Kombination einer Folge einfacher Befehle ermöglicht.

## Unterstützung von Dezimalrechnungen

Funktionen wie »Decimal Correct« und »Unit Add Complement« für die Addition gepackter und ungepackter Dezimalzahlen können mit dem binären »Add«-

Befehl durchgeführt werden. Rechenoperationen mit gepackten und ungepackten Dezimalzahlen werden problemlos von den Compilern unterstützt.

## Gleitkommabefehle

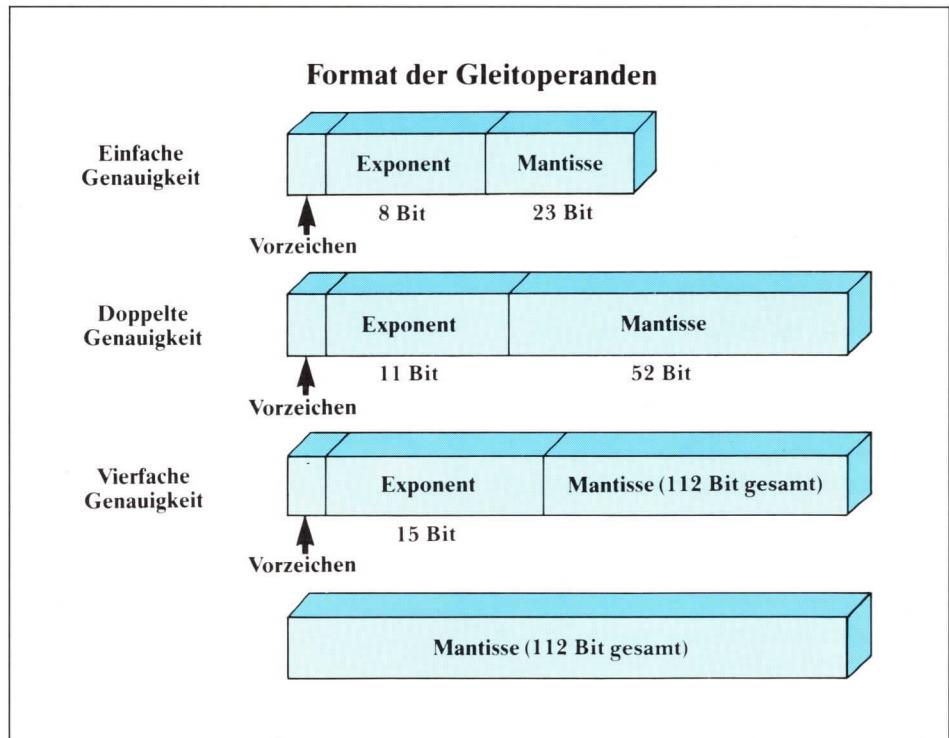

Mit den verfügbaren Gleitkommabefehlen können Rechenoperationen mit einfacher (32 Bit), doppelter (64 Bit) und vierfacher (128 Bit) Genauigkeit durchgeführt werden. Gleitkommabefehle können entweder direkt in der Hardware durch einen Gleitkomma-Coprozessor ausgeführt werden oder per Emulation in der Software. Mit einem Gleitkomma-Coprozessor können Gleitkommarechnungen ausgeführt werden, während parallel dazu der Hauptprozessor normal weiterarbeitet.

## Verzweigungsbefehle

Die bedingten Verzweigungsbefehle ermöglichen die Ausführung einer Opera-

tion, die Prüfung der Verzweigungsbedingung und die Durchführung der Verzweigung (wenn die Bedingungen erfüllt ist) in einem einzigen Befehl. Bestimmte Verzweigungsfolgen können völlig entfallen, da die meisten Rechenbefehle die Möglichkeit bieten, die Ausführung des folgenden Befehls von einer Bedingung abhängig zu machen; dadurch können einfache Funktionen wie zum Beispiel die Ermittlung eines Wahrheitswerts in einer einfachen Befehlsfolge ohne Verzweigung durchgeführt werden.

## Ein Befehl – ein Zyklus

Durch die Verwendung eines direkt in der Hardware verfügbaren Befehlssatzes kann im Normalfall ein Befehl pro Maschinenzyklus ausgeführt werden. Für die Durchführung von Lade-, Speicher- und Verzweigungsbefehlen kann mehr als ein Zyklus erforderlich sein, die Befehle sind

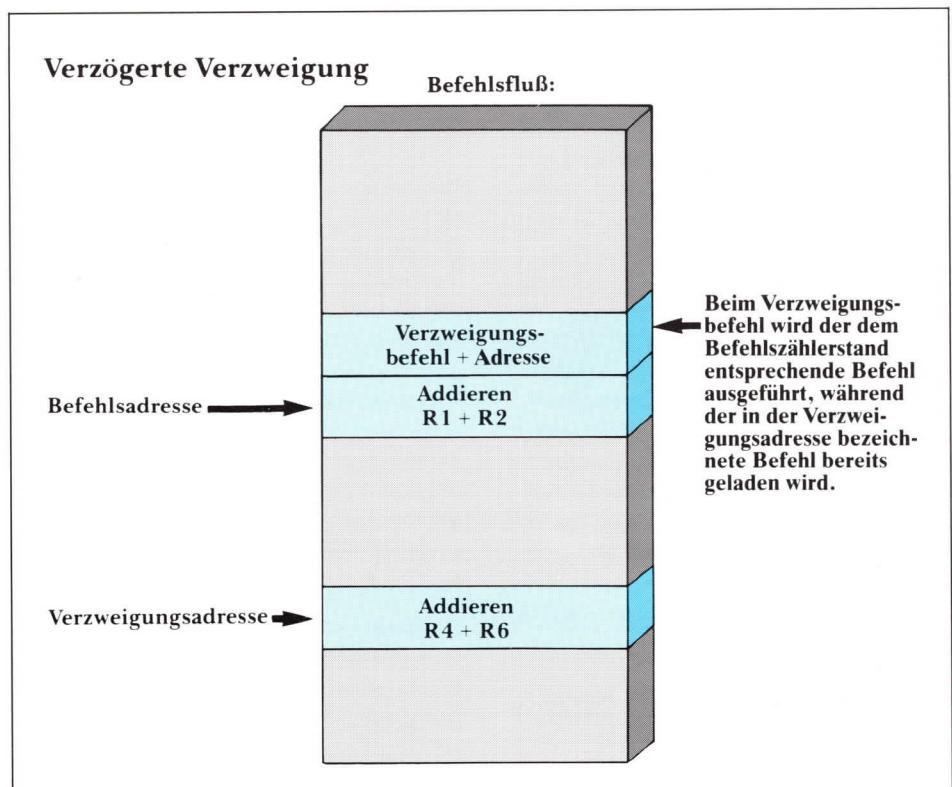

jedoch so implementiert und gesteuert, daß effektiv eine Abarbeitungsrate von annähernd einem Befehl pro Zyklus erreicht wird. Bei einer verzögerten Verzweigung bestimmt der Verzweigungsbefehl, daß noch während des Verzweigungsvorgangs der nächstfolgende Befehl ausgeführt werden kann, wobei der Compiler möglichst die Befehle so ordnet, daß davon häufig Gebrauch gemacht wird. Der für andere Systeme typische Verlust eines Maschinenzyklus bei der Durchführung einer Verzweigung kann dadurch oft vermieden werden. Ähnlich können Ladebefehle in eine Reihenfolge gebracht werden, die es ermöglicht, andere Befehle abzuarbeiten, während die Daten aus dem Speicher geholt werden. Um Verzögerungen bei der segmentweisen Parallelverarbeitung zu vermeiden, werden Befehle, zu deren Ausführung Daten geladen werden müssen, erst zur Ausführung freigegeben, wenn die Daten in einem Register der Zentraleinheit zur Verfügung stehen.

## Datenarten

### Ganze Zahlen

Die HP Precision Architecture unterstützt ganze Zahlen von 16 und 32 Bit Länge mit oder ohne Vorzeichen; ganze Zahlen mit Vorzeichen werden in Zweier-Komplementform dargestellt. Um den Aufbau des Prozessors so weit wie möglich vereinfachen zu können, müssen Halbwort-Ganzzahlen (16 Bit) bei geraden Byte-Adressen beginnen und Ganzzahlen (32 Bit) an einer Wortgrenze ausgerichtet werden.

### Zeichen

Zeichen werden als 8-Bit-Größen gespeichert, entsprechend dem ASCII-Standard für die Werte 0 bis 127 und dem erweiterten 8-Bit-Zeichensatz Roman-8 von Hewlett-Packard für die Werte 128 bis 255.

## Dezimalzahlen

Dezimalzahlen können sowohl in gepackter als auch in ungepackter Form dargestellt werden. Gepackte Dezimalzahlen werden grundsätzlich an einer Wortgrenze ausgerichtet und bestehen aus 7, 15, 23 oder 31 Ziffern im BCD-Code.

## Gleitkommaoperanden

Gleitkommaoperanden mit einfacher, doppelter und vierfacher Genauigkeit werden gemäß dem ANSI/IEEE-754-1985-Standard dargestellt. Gleitkommazahlen mit einfacher Genauigkeit müssen an Wortgrenzen, Gleitkommazahlen mit doppelter und vierfacher Genauigkeit an Doppelwortgrenzen ausgerichtet werden.

## Die Register der Zentraleinheit

Die HP Precision Architecture erfordert registerintensiven Betrieb, das heißt, Rechenoperationen werden nur zwischen den Hochgeschwindigkeitsregistern der Zentraleinheit oder zwischen einem Register und einer im Befehl enthaltenen Konstanten durchgeführt. Durch diese registerintensive Arbeitsweise kann der Schaltungsaufbau für die Datenübertragung und für die Steuerungs- und Überwachungsfunktionen vereinfacht und die Prozessorleistung erheblich gesteigert werden. Optimierende Compiler ordnen den am häufigsten benutzten Daten Registern zu und minimieren dadurch die Zahl der Hauptspeicherzugriffe.

## Mehrzweckregister

Zur Aufnahme der Operanden und der Ergebnisse der Rechenoperationen stehen 32 Mehrzweckregister à 32 Bit zur Verfügung.

## Steuer- und Statusregister

Die Zentraleinheit verfügt über 32 Steuer- und Statusregister zur Unterbrechungsverarbeitung, zur Regelung des Zugriffs auf den virtuellen Speicher und für andere Systemfunktionen. Der Zustand der Zentraleinheit wird in einem 32-Bit langen Prozessorstatuswort wiedergegeben, das den Zustand der wichtigsten Flags und Statusbits anzeigt.

## Speicherabschnittsregister

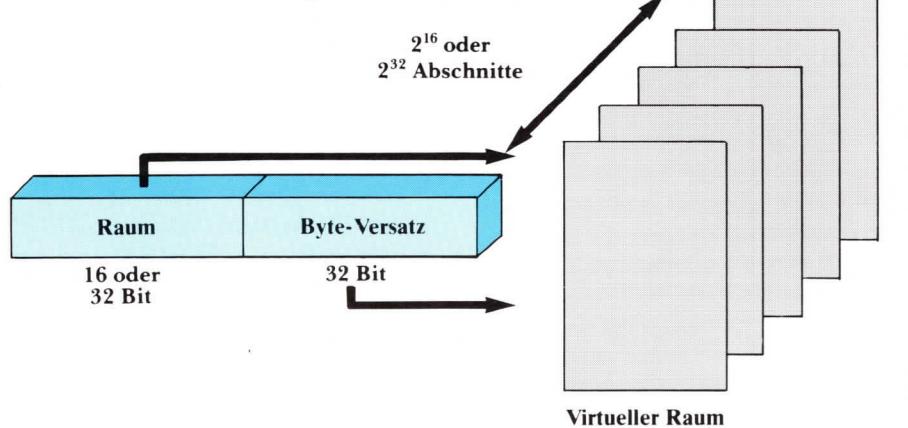

Acht Speicherabschnittsregister in der Zentraleinheit ermöglichen die Festlegung von maximal 8, gegebenenfalls verschiedenen, virtuellen Abschnitten von 4GByte Umfang für bestimmte Operationen. Die Abschnittserkennung sind 16 bzw. 32 Bit lang, ihre Länge richtet sich nach der Adressierungskapazität des jeweiligen Systems. Auf fünf dieser Register können Anwendungsprogramme direkt zugreifen.

## Befehlsadressenregister

Zwei Register der Zentraleinheit verweisen auf den nächsten auszuführenden Befehl: Das Basisadressenregister (IA Space) bezeichnet den 4 GByte großen Speicherabschnitt, der den nächsten Befehl enthält, das Adressenversatzregister (IA Offset) gibt die Stelle innerhalb dieses Speicherabschnitts an, an der der Befehl steht. Jedes Register ist praktisch eine zweiteilige Warteschlange: beide zusammen reflektieren die durch die spezielle Rechnerarchitektur gegebene Möglichkeit, die beiden nächsten, zur Bearbeitung anstehenden Befehle jederzeit zu bestimmen.

## Aufbau des virtuellen Speichers

## Virtuelle Adressierung

Die durch die HP Precision Architecture ermöglichte 48- bzw. virtuelle 64-Bit-Adressierung bedeutet eine wesentliche Kapazitätssteigerung gegenüber den herkömmlichen Systemen mit 32-Bit-Adressierung. Darüber hinaus ermöglicht der Befehlssatz direkten Zugriff auf physikalische Speicherstellen, und Systeme der unteren Preisklasse können, auf Wunsch, ausschließlich mit physikalischer Adressierung ausgestattet werden. Die kleinste adressierbare Einheit ist ein Byte.

## Virtuelle Speicherverwaltung

Der virtuelle Speicher ist als eine Menge linear angeordneter Bereiche von je 4 GByte aufgebaut. Die Bereiche sind in Seiten fester Länge von 2 kByte aufgeteilt, wobei jede Seite Programmcode, Daten oder beides enthalten kann. Speicherabschnittsregister geben den virtuellen Speicherabschnitt an, auf den ein Zugriff erfolgen soll: auf die genaue Stelle des betreffenden Abschnitts verweist eine 32-Bit-Größe, der Byte-Versatz. Es können mehrere Speicherabschnitte gleichzeitig angesprochen werden. Der Programmcode kann abschnittüberschreitend angeordnet sein und eine einzelne Datenstruktur kann volle 4 GByte Länge haben.

## Im Arbeitsspeicher abgebildetes Eingabe/Ausgabesystem

Die HP Precision Architecture verwendet ein im Arbeitsspeicher abgebildetes E/A-System, das heißt, für E/A-Operationen, die über eine Reihe von Lade- und Speicherbefehlen abgewickelt werden, sind bestimmte Bereiche in einem virtuellen oder physikalischen Speicher reserviert. Leistungssteigernd wirkt sich dabei aus, daß die E/A-Geräte mit denselben Zugriffsbeschränkungsmechanismen wie Programmcode und Daten arbeiten. Für die Durchführung von E/A-Operationen sind keinerlei Sonderbefehle erforderlich. Zusammen mit weiteren E/A-Subsystemfunktionen (zum Beispiel verkettete direkte Speicherzugriffe, mit denen eine Vielzahl von Transaktionen direkt, d.h. ohne Beteiligung der Zentraleinheit ausgeführt werden können) trägt das E/A-System der HP Precision Architecture zur Verringerung der Systemzeit bei und steigert die Leistungsfähigkeit bei E/A-Prozessen.

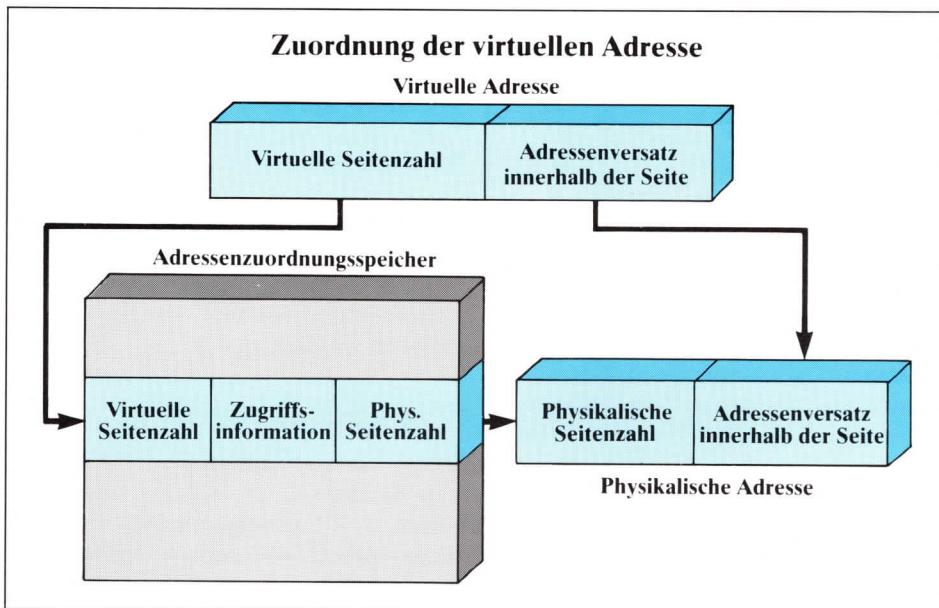

## Zuordnung der virtuellen Adressen

Die Konvertierung von virtuellen in physikalische Adressen erfolgt hardwaremäßig in Adresszuordnungsspeichern (TLB), in denen die Zuordnung der virtuellen Seiten gespeichert ist, auf die zuletzt zugegriffen wurde. Ein Adresszuordnungsspeicher kann entweder aus zwei logischen Speichern bestehen, von denen einer Programmcode und der andere Daten enthält, oder aus einem einzigen Speicher, der beide enthält.

## Zugriffsbeschränkung im virtuellen Speicher

Die Hardware des Adresszuordnungsspeichers unterstützt Sicherheitsvorkehrungen, die gewährleisten, daß eine Operation bei ihrer Ausführung nur auf den Programmcode, auf die Daten oder die E/A-Geräte zugreifen kann, für die sie zugriffsberechtigt ist. Zu diesen Sicherheitsvorkehrungen gehören unter ande-

rem vier Berechtigungsstufen: Jeder Speicherseite werden Schutzparameter zugeordnet, die festlegen, welche Benutzer oder Programme welcher Berechtigungsstufe auf diese Seite zugreifen dürfen und welche Zugriffsarten zugelassen sind. Bei jedem Datenaufzugriff werden diese Schutzparameter mit der Zugriffsberechtigung der gerade ablaufenden Operation verglichen, um sicherzustellen, daß diese Operation zur Ausführung eines bestimmten Zugriffs berechtigt ist.

## Cache-Speicher

Daten und Befehle werden entweder gemeinsam in einem oder getrennt in verschiedenen Cache-Speichern abgestellt. Um die Zykluszeit der Zentraleinheit so klein wie möglich zu halten, greifen die E/A-Subsysteme nicht auf den Cache-Speicher zu, und es ist Aufgabe der Software, vor einer E/A-Operation mit direktem Zugriff auf den Arbeitsspeicher Änderungen des Cache-Speicherinhalts an den Arbeitsspeicher weiterzugeben. Cache-Speicher, die nur Befehle enthalten, sind reine Lesespeicher, da Programmcode normalerweise nicht verändert werden kann.

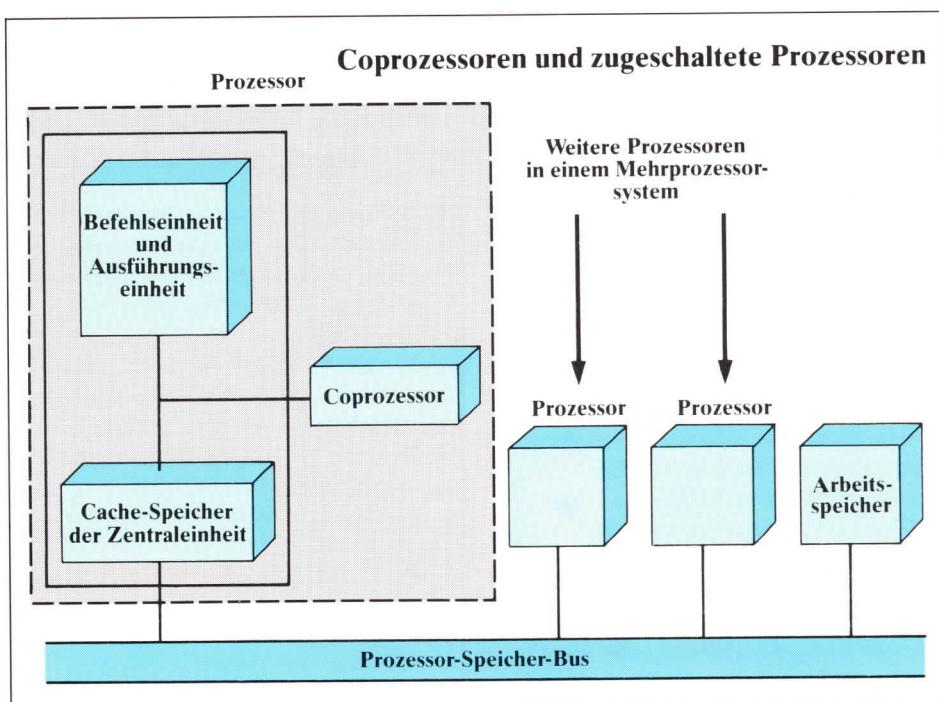

## Coprozessoren

Die HP Precision Architecture ermöglicht die Einbeziehung von Coprozessoren, die dieselben Cache-Speicher benutzen wie der Hauptprozessor. Coprozessoren optimieren die Leistungsfähigkeit besonderer Funktionen (zum Beispiel schnelle Gleitkommarechnung) und werden durch eine Untermenge des Befehlssatzes gesteuert. Sie verfügen über eigene Register mit direktem Cache-Speicherzugriff.

## Zugeschaltete Prozessoren

Die HP Precision Architecture bietet die Möglichkeit, zusätzliche Prozessoren zuzuschalten, die auf Speicherbusebene in die Systemhierarchie eingebunden sind und im Normalfall mit eigenen Registern und einem oder mehreren Cache-Speichern ausgestattet sind. Diese zugeschalteten Prozessoren arbeiten entweder mit demselben oder mit einem anderen Befehlssatz als der Hauptprozessor und führen zum Beispiel Vektorrechnungen und E/A-Operationen durch.

## Mehrprozessorbetrieb

Beim Mehrprozessorbetrieb werden bau gleiche Prozessoren zugeschaltet. In paralleler Anordnung wird die Arbeitslast des Systems aufgeteilt und somit die Leistungsfähigkeit erhöht, in redundanter Anordnung dienen Multiprozessoren der Ausfallsicherung und der Erhöhung der Fehlertoleranz. Jeder Prozessor verfügt

über eigene Register und einen eigenen Cache-Speicher und arbeitet mit dem gesamten Befehlssatz. Vorgesehen ist die Entwicklung eng gekoppelter, symmetrischer Mehrprozessorsysteme.

## Optimierende Compiler

Rechnerarchitekturen, die mit einfachem Befehlssatz arbeiten, eignen sich nicht nur ideal für den Einsatz optimierender Compiler, diese stellen vielmehr eine grund sätzliche Voraussetzung für die volle Ausnutzung des Leistungspotentials solcher Rechner dar. Der optimierende Compiler sorgt z.B. durch eine rationale Anordnung der Befehle für eine möglichst vollständige Ausnutzung des während einer Ver zweigung zur Verfügung stehenden Maschinenzyklus. Er weist den Mehrzweckregistern der Zentraleinheit die Operanden zu, auf die in einer Befehlsfolge am häufigsten zugegriffen wird, und reduziert dadurch Cache- und Arbeits speicherzugriffe auf ein Minimum. Die in

Verbindung mit der HP Precision Architecture eingesetzten Compiler sind auch in der Lage, wenig wirkungsvolle Programmierungstechniken zu korrigieren. Zum Beispiel werden Berechnungen innerhalb einer Schleife, bei denen jede Iteration als Resultat den gleichen Wert ergibt, im Maschinencode außerhalb der Schleife untergebracht. Auch andere redundante Berechnungen in einem Programm können bei der Compilierung beseitigt werden.

## VLSI-Schaltungen

Eine weitere Besonderheit der HP Precision Architecture ist, daß die Computersysteme, die mit ihr arbeiten, in den verschiedensten Halbleitertechniken realisiert werden können. Da für die Ausführung von Prozessorfunktionen hier eine geringere Zahl an Schaltkreisen erforderlich ist, können Komponenten mit Höchstintegration (VLSI = Very Large Scale Integrated) optimal eingesetzt werden. Aufgrund des vereinfachten Aufbaus des Prozessors kann man eine ganze Zentraleinheit auf einem Chip unterbringen, damit den Signaldurchsatz erhöhen und die Zykluszeit reduzieren. Erhöht man die Integration noch weiter, indem man zum Beispiel Zentraleinheit, Cache- und Adressenzuordnungsspeicher auf einen Chip unterbringt, können auch Zugriffszeiten zu Programmcode und Daten mini miert und die Rechnerleistungen noch weiter gesteigert werden. Die Leistungsvorteile und die niedrigen Kosten der VLSI-Technik ermöglichen die Konstruktion von kostengünstigen Hochleistungssystemen im technisch-wissenschaftlichen und kommerziellen Bereich.

## Der Befehlssatz

### Speicheransteuerungsbefehle

Load Word

Load Halfword

Load Byte

Load Word Indexed

Load Halfword Indexed

Load Byte Indexed

Load Word Short

Load Halfword Short

Load Byte Short

Load Word and Modify

Load Word Absolute

Load Word Absolute Short

Load Offset

Load and Clear Word Indexed

Load and Clear Word Short

Store Word

Store Halfword

Store Byte

Store Word Short

Store Halfword Short

Store Word and Modify

Store Word Absolute Short

Store Bytes Short

### Unbedingte Verzweigungsbefehle

Branch and Link

Gateway

Branch and Link Register

Branch Vectored

Branch External

Branch and Link External

### Bedingte Verzweigungsbefehle

Move and Branch

Move Immediate and Branch

Compare and Branch if True

Compare and Branch if False

Compare Immediate

and Branch if True

Compare Immediate

and Branch if False

Add and Branch if True

Add and Branch if False

Add Immediate and Branch if True

Add Immediate and Branch if False

Branch on Variable Bit

Branch on Bit

### Arithmetische/ Logische Befehle

Add

Add Immediate

Add Immediate Left

Load Immediate Left

Add Logical

Add and Trap on Overflow

Shift One and Add

Shift Two and Add

Shift Three and Add

Shift One and Add Logical

Shift Three and Add Logical

Shift One, Add, and Trap on Overflow

Shift Two, Add, and Trap on Overflow

Shift Three, Add,

and Trap on Overflow

Add with Carry

Add with Carry and Trap on Overflow

Subtract

Subtract from Immediate

Subtract and Trap on Overflow

Subtract Immediate

and Trap on Overflow

Subtract with Borrow

Subtract with Borrow

and Trap on Overflow

Subtract and Trap on Condition

Subtract and Trap

on Condition or Overflow

Divide Step

Compare and Clear

Inclusive OR

Exclusive OR

AND

AND Complement

Unit XOR

Unit Add Complement

Unit Add Complement and Trap

on Condition

Decimal Correct

Intermediate Decimal Correct

Add Immediate and

Trap on Overflow

Add Immediate, Trap on

Condition or Overflow

Compare Immediate and Clear

Variable Shift Double

Shift Double

Variable Extract Signed

Variable Extract Unsigned

Extract Signed

Extract Unsigned

Variable Deposit

Variable Deposit Immediate

Deposit

Deposit Immediate

Zero and Variable Deposit

Zero and Variable Deposit Immediate

Zero and Deposit

Zero and Deposit Immediate

Move from Control Register

Move to System Mask

Synchronize Caches

Probe Read Access

Probe Read Access Immediate

Probe Write Access

Probe Write Access Immediate

Load Physical Address

Load Hash Address

Purge Instruction TLB

Purge Instruction TLB Entry

Purge Data TLB

Purge Data TLB Entry

Insert Data TLB Address

Insert Data TLB Protection

Insert Instruction TLB Address

Insert Instruction TLB Protection

Purge Data Cache

Flush Data Cache

Flush Instruction Cache

Flush Data Cache Entry

Flush Instruction Cache Entry

Diagnose

### Operationen der Sonderfunktionseinheit

Special Operation Zero

Special Operation One

Special Operation Two

Special Operation Three

### Lade- und Speicherbefehle für den Coprozessor

Coprocessor Load Word Short

Coprocessor Load Word Indexed

Coprocessor Load Doubleword Short

Coprocessor Load

Doubleword Indexed

Coprocessor Store Word

Coprocessor Store Indexed

Coprocessor Store Doubleword

Coprocessor Store

Doubleword Indexed

Coprocessor Operation\*

\* Einschließlich Gleitkommaoperationen

### Befehle zur Systemsteuerung

Break

Return From Interrupt

Set System Mask

Reset System Mask

Load Space ID

Move to Space Register

Move to Control Register

Move from Space Register

## Hewlett-Packard Deutschland

### Hauptverwaltung

Herrenberger Straße 130

7030 Böblingen

Tel. (0 70 31) 14-0

### Vertriebszentrale

Hewlett-Packard-Straße

6380 Bad Homburg v.d.H.

Tel. (0 61 72) 4 00-0

### Verbindungsstelle Bonn

Friedrich-Ebert-Allee 26

5300 Bonn 1

Tel. (0 22 8) 23 40 01

### Werk I Böblingen

● Medizinelektronik

Herrenberger Straße 110

7030 Böblingen, Tel. (0 70 31) 14-0

### Werk II, III, IV Böblingen

● Elektronische Meßtechnik

● Techn.-wissenschaftl. Computersysteme

● Kommerzielle Informationssysteme

Herrenberger Straße 130

7030 Böblingen, Tel. (0 70 31) 14-0

### Werk Waldbronn

● Analytische Meßtechnik

Hewlett-Packard-Straße

7517 Waldbronn 2, Tel. (0 72 43) 6 02-0

### Support-Zentrum Ratingen

Berliner Straße 111

4030 Ratingen, Tel. (0 21 02) 494-500

### Reparatur-Zentrum Frankfurt

Berner Straße 117

6000 Frankfurt/Main, Tel. (0 69) 50 00 01-22

### Reparatur-Zentrum Böblingen

Schickardstraße 2

7030 Böblingen, Tel. (0 70 31) 6 45-0

### Zentrale für Ersatzteile, Verbrauchs- material und Zubehör

Dornierstraße 7

7030 Böblingen, Tel. (0 70 31) 14-0

### Vertriebszentrum Nord

Kapstadtring 5

2000 Hamburg 60

Tel. (0 40) 6 38 04-0

### Geschäftsstelle Hannover

Heidering 37-39

3000 Hannover 61

Tel. (0 51 1) 5 70 06-0

### Geschäftsstelle Berlin

Keithstraße 2-4

1000 Berlin 30

Tel. (0 30) 2 19 90 4-0

### Vertriebszentrum Ratingen

Berliner Straße 111

4030 Ratingen

Tel. (0 21 02) 494-0

### Geschäftsstelle Dortmund

Schleefstraße 28

4600 Dortmund 41

Tel. (0 23 1) 4 50 01-0

### Vertriebszentrum Bad Homburg

Hewlett-Packard-Straße

6380 Bad Homburg v.d.H.

Tel. (0 61 72) 4 00-0

### Geschäftsstelle Mannheim

Rossauer Weg 2-4

6800 Mannheim 31

Tel. (0 62 1) 70 05-0

### Vertriebszentrum Böblingen

Schickardstraße 2

7030 Böblingen

Tel. (0 70 31) 6 45-0

### Geschäftsstelle Karlsruhe

Ermilis-Allee

7517 Waldbronn 2

Tel. (0 72 43) 6 02-0

### Geschäftsstelle Neu-Ulm

Messerschmittstraße 7

7910 Neu-Ulm

Tel. (0 73 1) 70 73-0

### Vertriebszentrum München

Eschenstraße 5

8028 Taufkirchen

Tel. (0 89) 6 12 07-0

### Geschäftsstelle Nürnberg

Emmericher Straße 13

8500 Nürnberg 10

Tel. (0 91 1) 5 20 5-0

## Hewlett-Packard Schweiz

Hewlett-Packard (Schweiz) AG

Abteilung Information

Allmend 2

CH-8967 Widen

Tel. (057) 31 21 11

Hewlett-Packard (Schweiz) AG

Département Informatique et Systèmes

7, rue du Bois-du-Lan

CH-1217 Meyrin 1/Schweiz

Tel. (022) 83 11 11

Schwamendingenstraße 10

CH-8050 Zürich

Tel. (01) 3 15 81 81

## Hewlett-Packard Österreich

Hewlett-Packard Ges.m.b.H

Lieblgasse 1, A-1222 Wien

Tel. (02 22) 25 00-0

Verkaufsbüro Graz

Grottenhofstraße 94, A-8052 Graz

Tel. (03 16) 28 30 66

## Sozialistische Staaten

Hewlett-Packard Ges.m.b.H

Lieblgasse 1, A-1222 Wien

Tel. (02 22) 25 00-0

## Europa-Zentrale

Hewlett-Packard S.A.

150, route du Nant-d'Avril

1217 Meyrin 2-Genf/Schweiz

Tel. (022) 83 81 11

## For more information

(for HP Switzerland, Austria and other countries)

please contact your nearest HP Sales Office

or write to:

Hewlett-Packard

Central Mailing Department

P.O. Box 529

1180 AM Amstelveen

Netherlands

Tel. (31) 20-547 6142