## Maintenance Library

PANEL

DEV-I

ACC

R/W

VOL. R05

HDA

RPI

PWR

LOC

INST

VOL. R06

INDEX

MLX

LGND

START

FSI

MSG

SENSE

OPER

VOL. R07

MICRO

VOL. R08

MICFL

VOL. R09

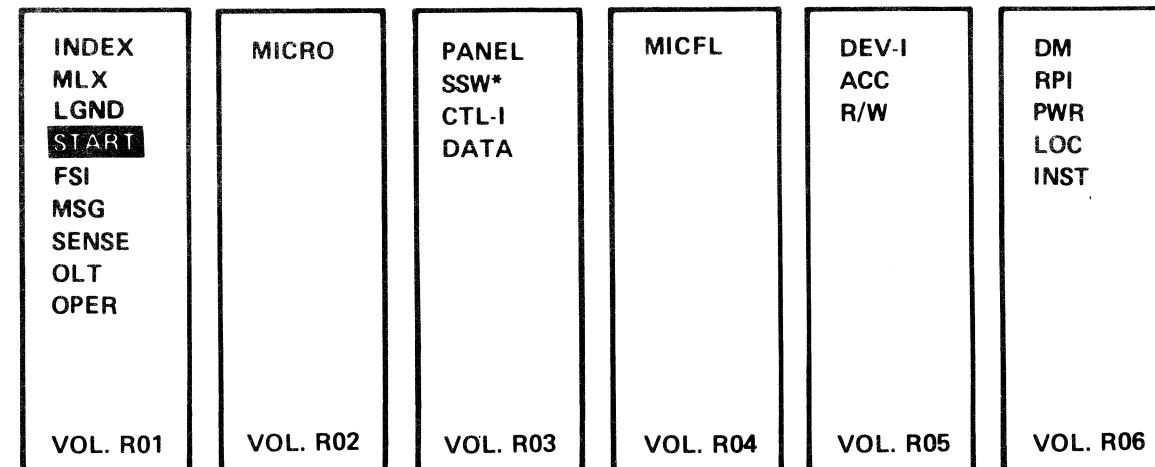

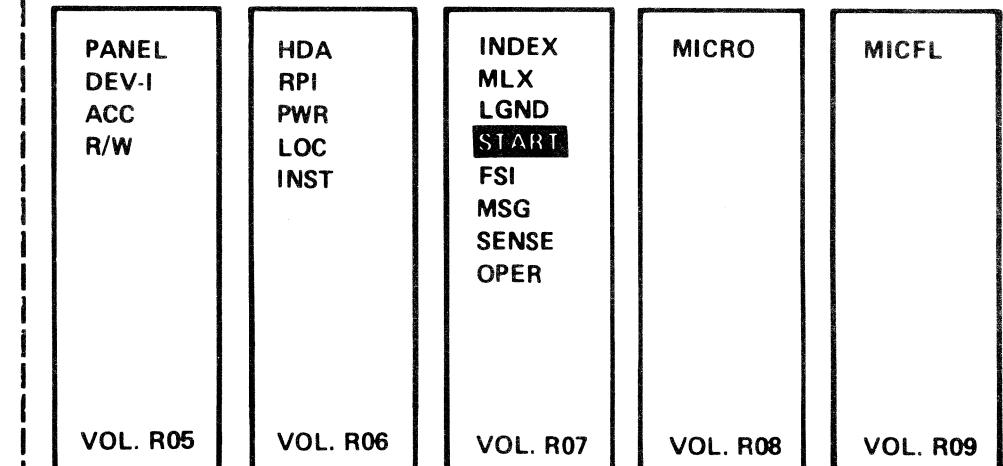

*Every Satellite Module on the 3340 subsystem (including the 3344) has its own Volumes R05 and R06.*

*The 3344 MLM also includes Volumes R07, R08, and R09. See the START section in Volume R07 for details.*

**3344**

### Disk Storage Maintenance Information

## MAINTENANCE LIBRARY MANUAL ORDERING PROCEDURE (IBM Internal)

Individual pages of the 3344 Maintenance Library Manual can be ordered from the San Jose plant by using the Wiring Diagram/Logic Page Request (Order No. 120-1679). In the columns headed "Logic Page" enter the page identifier information: sequence number, sheet number, part number, and EC number. Groups of pages can be ordered by including a description (section, volume, etc.) and the machine serial number.

This manual was prepared by the IBM General Products Division, Technical Publishing, Department G26, San Jose, California 95193.

© Copyright International Business Machines Corporation 1976

## SAFETY

### CE SAFETY PRACTICES

All Customer Engineers are expected to take every safety precaution possible and observe the following safety practices while maintaining IBM equipment:

1. You should not work alone under hazardous conditions or around equipment with dangerous voltage. Always advise your manager if you MUST work alone.

2. Remove all power, ac and dc, when removing or assembling major components, working in immediate areas of power supplies, performing mechanical inspection of power supplies, or installing changes in machine circuitry.

3. After turning off wall box power switch, lock it in the Off position or tag it with a "Do Not Operate" tag, Form 229-1266. Pull power supply cord whenever possible.

4. When it is absolutely necessary to work on equipment having exposed operating mechanical parts or exposed live electrical circuitry anywhere in the machine, observe the following precautions:

- a. Another person familiar with power off controls must be in immediate vicinity.

- b. Do not wear rings, wrist watches, chains, bracelets, or metal cuff links.

- c. Use only insulated pliers and screwdrivers.

- d. Keep one hand in pocket.

- e. When using test instruments, be certain that controls are set correctly and that insulated probes of proper capacity are used.

- f. Avoid contacting ground potential (metal floor strips, machine frames, etc.). Use suitable rubber mats, purchased locally if necessary.

5. Wear safety glasses when:

- a. Using a hammer to drive pins, riveting, staking, etc.

- b. Power or hand drilling, reaming, grinding, etc.

- c. Using spring hooks, attaching springs.

- d. Soldering, wire cutting, removing steel bands.

- e. Cleaning parts with solvents, sprays, cleaners, chemicals, etc.

- f. Performing any other work that may be hazardous to your eyes. REMEMBER – THEY ARE YOUR EYES.

6. Follow special safety instructions when performing specialized tasks, such as handling cathode ray tubes and extremely high voltages. These instructions are outlined in CEMs and the safety portion of the maintenance manuals.

7. Do not use solvents, chemicals, greases, or oils that have not been approved by IBM.

8. Avoid using tools or test equipment that have not been approved by IBM.

9. Replace worn or broken tools and test equipment.

10. Lift by standing or pushing up with stronger leg muscles – this takes strain off back muscles. Do not lift any equipment or parts weighing over 60 pounds.

11. After maintenance, restore all safety devices, such as guards, shields, signs, and grounding wires.

12. Each Customer Engineer is responsible to be certain that no action on his part renders products unsafe or exposes customer personnel to hazards.

13. Place removed machine covers in a safe out-of-the-way place where no one can trip over them.

14. Ensure that all machine covers are in place before returning machine to customer.

15. Always place CE tool kit away from walk areas where no one can trip over it; for example, under desk or table.

16. Avoid touching moving mechanical parts when lubricating, checking for play, etc.

17. When using stroboscope, do not touch ANYTHING – it may be moving.

18. Avoid wearing loose clothing that may be caught in machinery. Shirt sleeves must be left buttoned or rolled above the elbow.

19. Ties must be tucked in shirt or have a tie clasp (preferably nonconductive) approximately 3 inches from end. Tie chains are not recommended.

20. Before starting equipment, make certain fellow CEs and customer personnel are not in a hazardous position.

21. Maintain good housekeeping in area of machine while performing and after completing maintenance.

**Knowing safety rules is not enough.

An unsafe act will inevitably lead to an accident.

Use good judgment - eliminate unsafe acts.**

### ARTIFICIAL RESPIRATION

#### General Considerations

1. Start Immediately – Seconds Count

Do not move victim unless absolutely necessary to remove from danger. Do not wait or look for help or stop to loosen clothing, warm the victim, or apply stimulants.

2. Check Mouth for Obstructions

Remove foreign objects.

3. After victim is breathing by himself or when help is available:

- a. Loosen clothing.

- b. Place victim on his side.

- c. Keep victim warm.

4. Remain in Position

After victim revives, be ready to resume respiration if necessary.

5. Call a Doctor

Have someone summon medical aid.

6. Don't Give Up

Continue without interruption until victim is breathing without help or is certainly dead.

#### Rescue Breathing for Adults

1. Place victim on back; lift neck and tilt head way back. (Quickly remove any noticeable food or objects from mouth.)

2. Pinch nose closed; make airtight seal around victim's mouth with your mouth; and forcefully breathe into victim until chest rises (expands).

3. Continue breathing for the victim 12 times per minute WITHOUT STOPPING.

4. If chest does not rise (expand), roll victim onto side and pound firmly between shoulder blades to remove blocking material. Also, try lifting jaw higher with your fingers. Resume rescue breathing.

# INDEX

# INDEX 1

## A

Abbreviations LGND 16

AC Ripple Check PWR 290

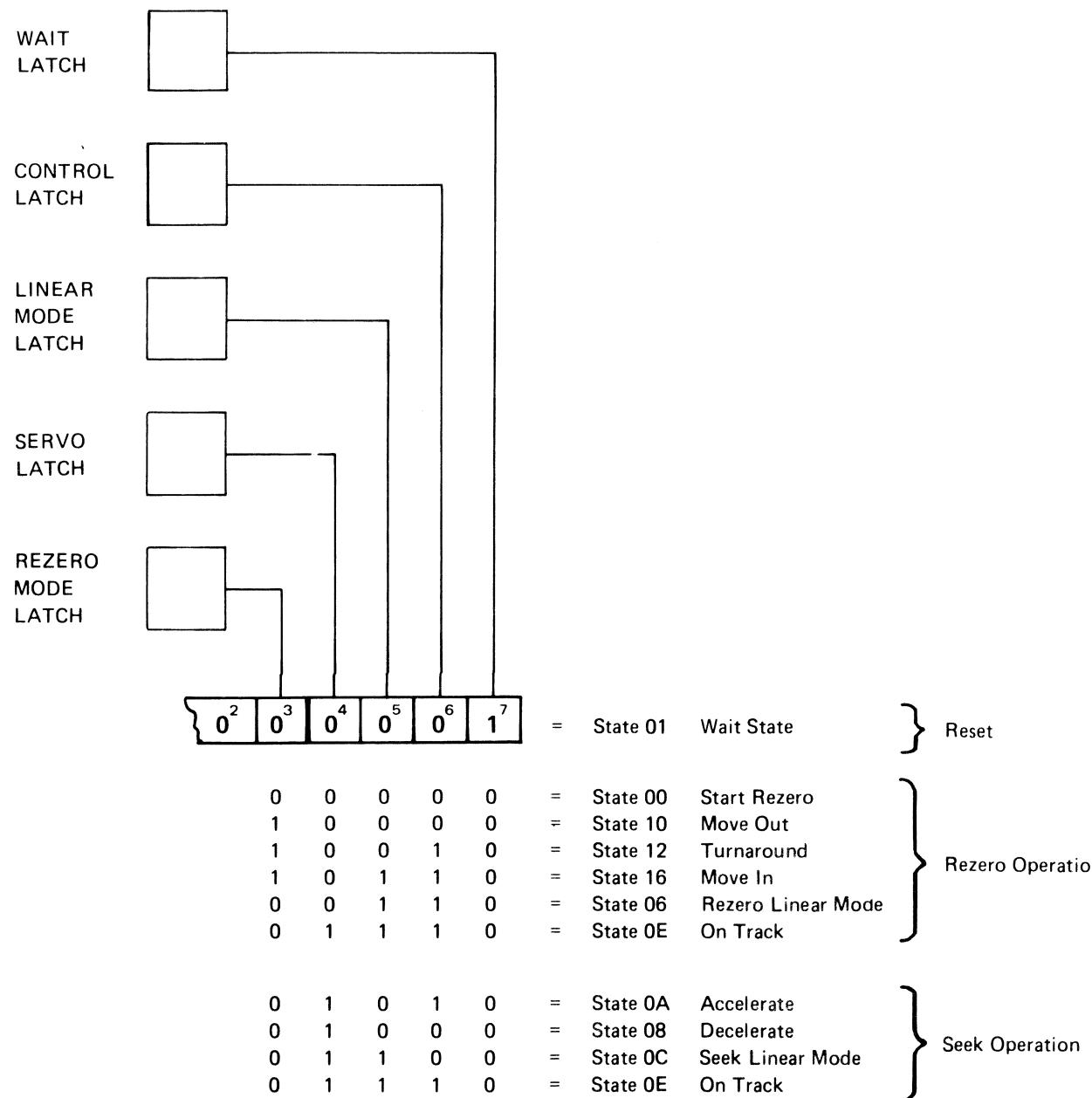

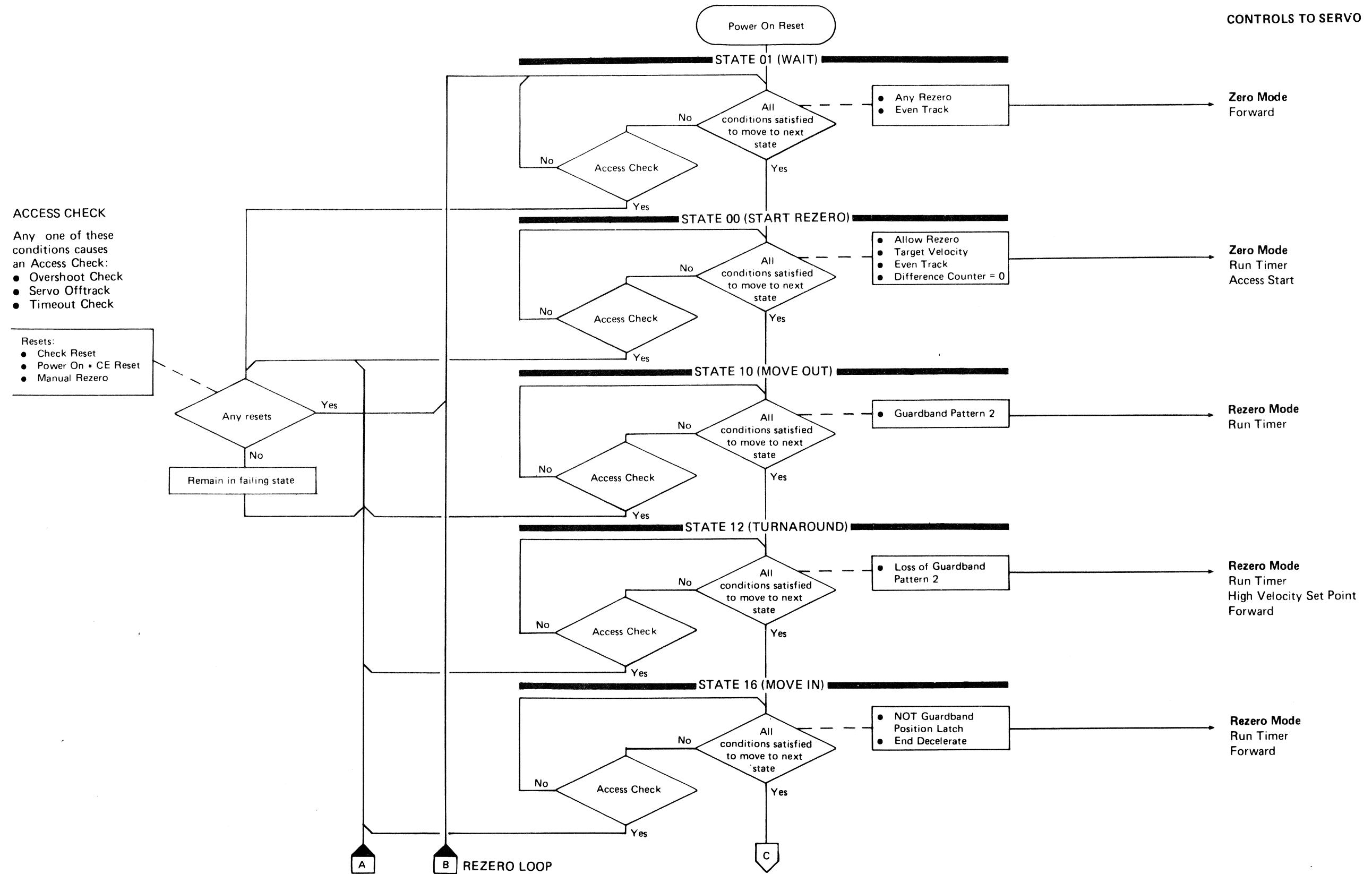

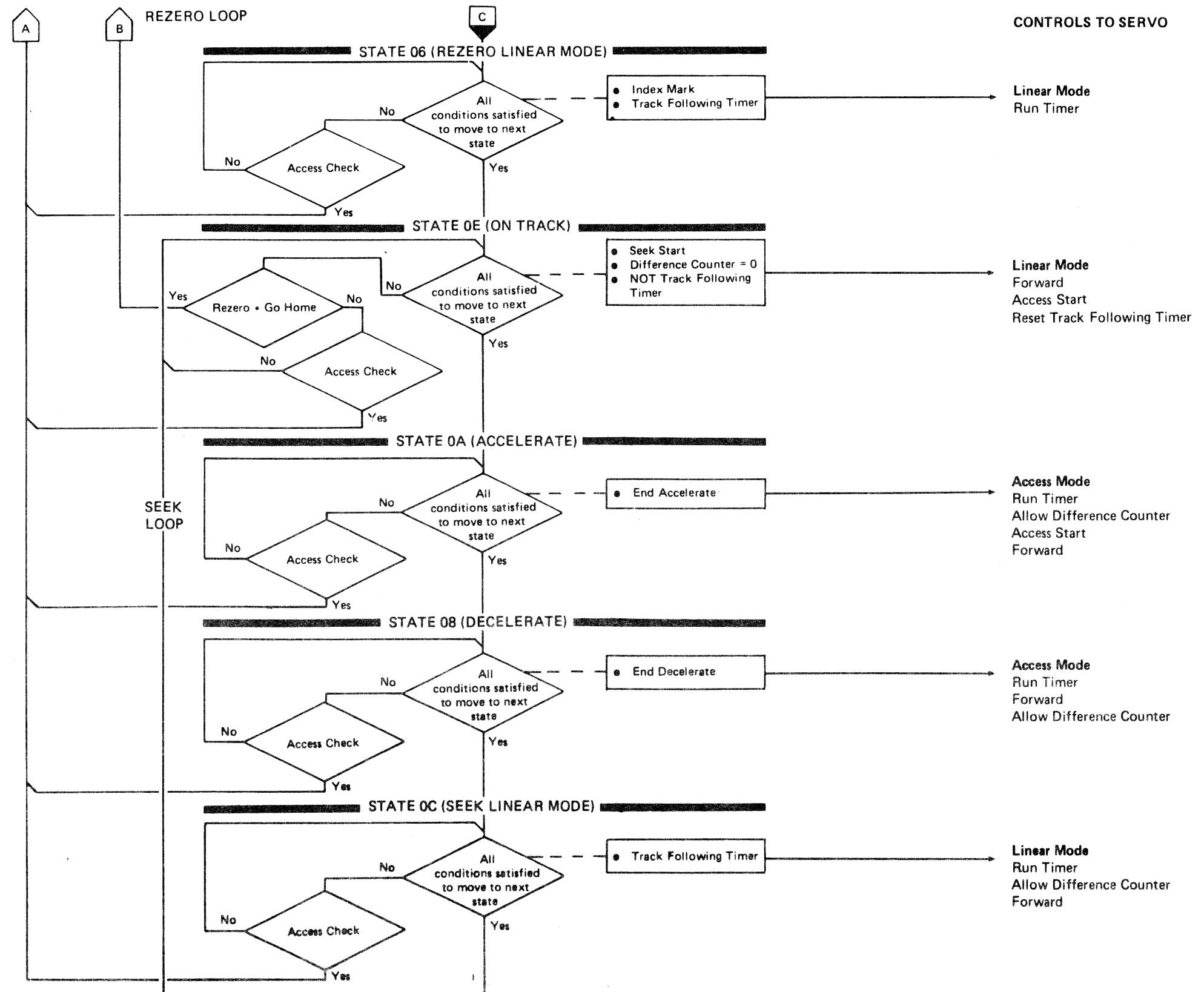

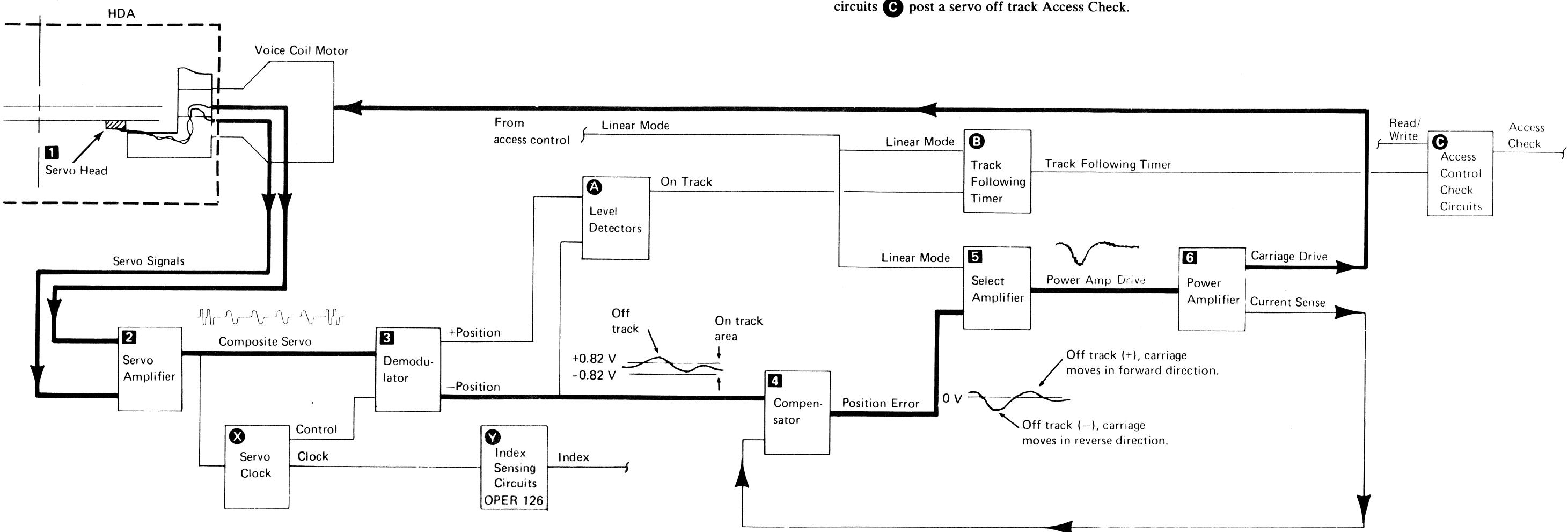

Access Check OPER 119, OPER 123

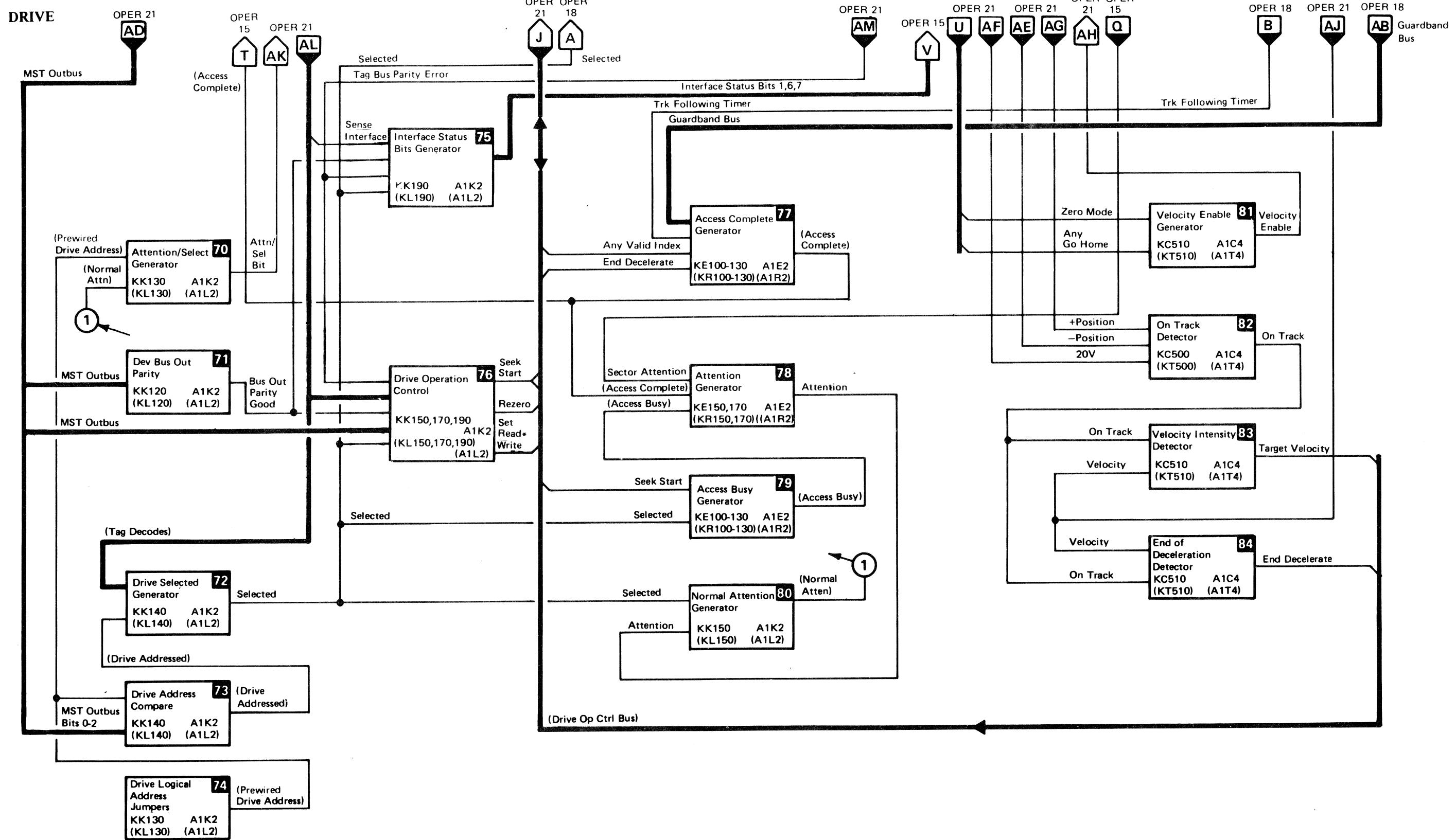

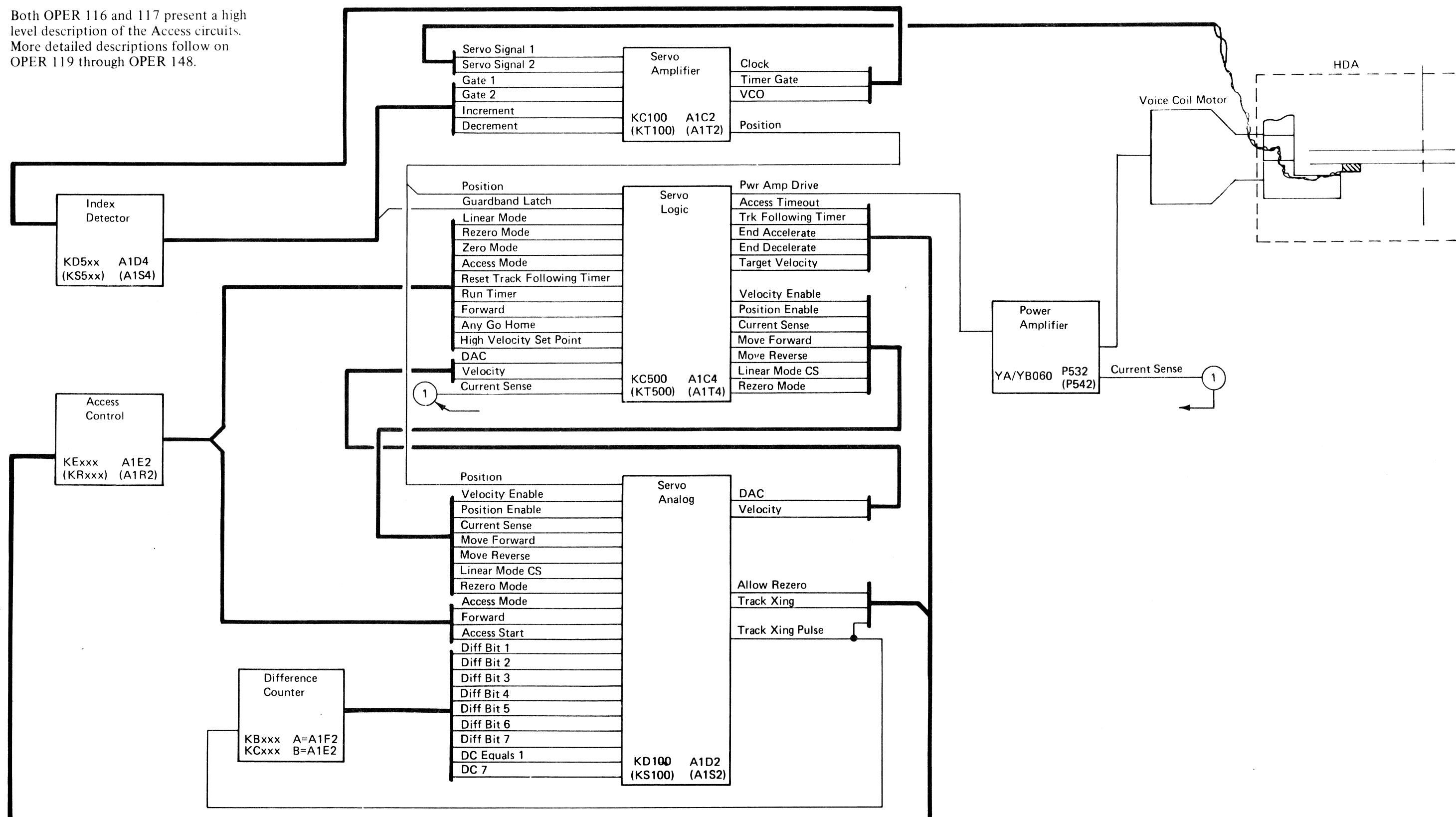

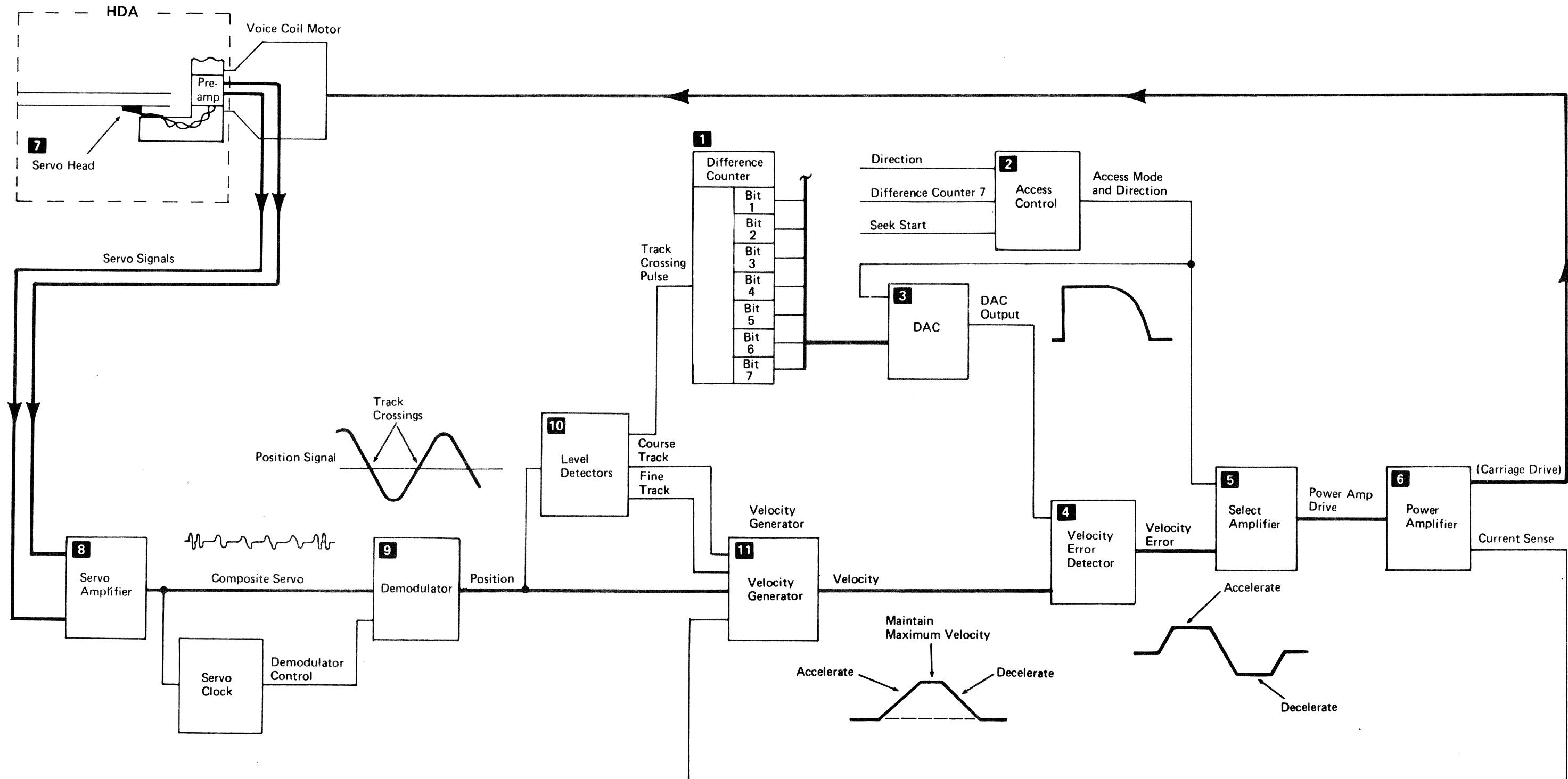

Access Control OPER 117

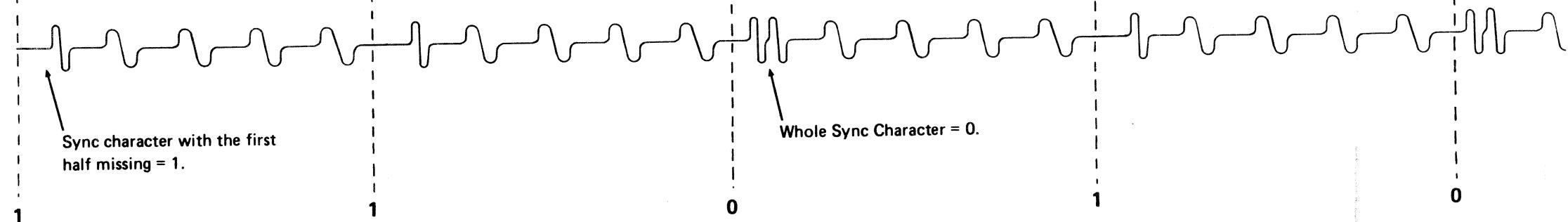

Access Operation

Block Diagram and Description OPER 116

Control Sequence (States) OPER 119

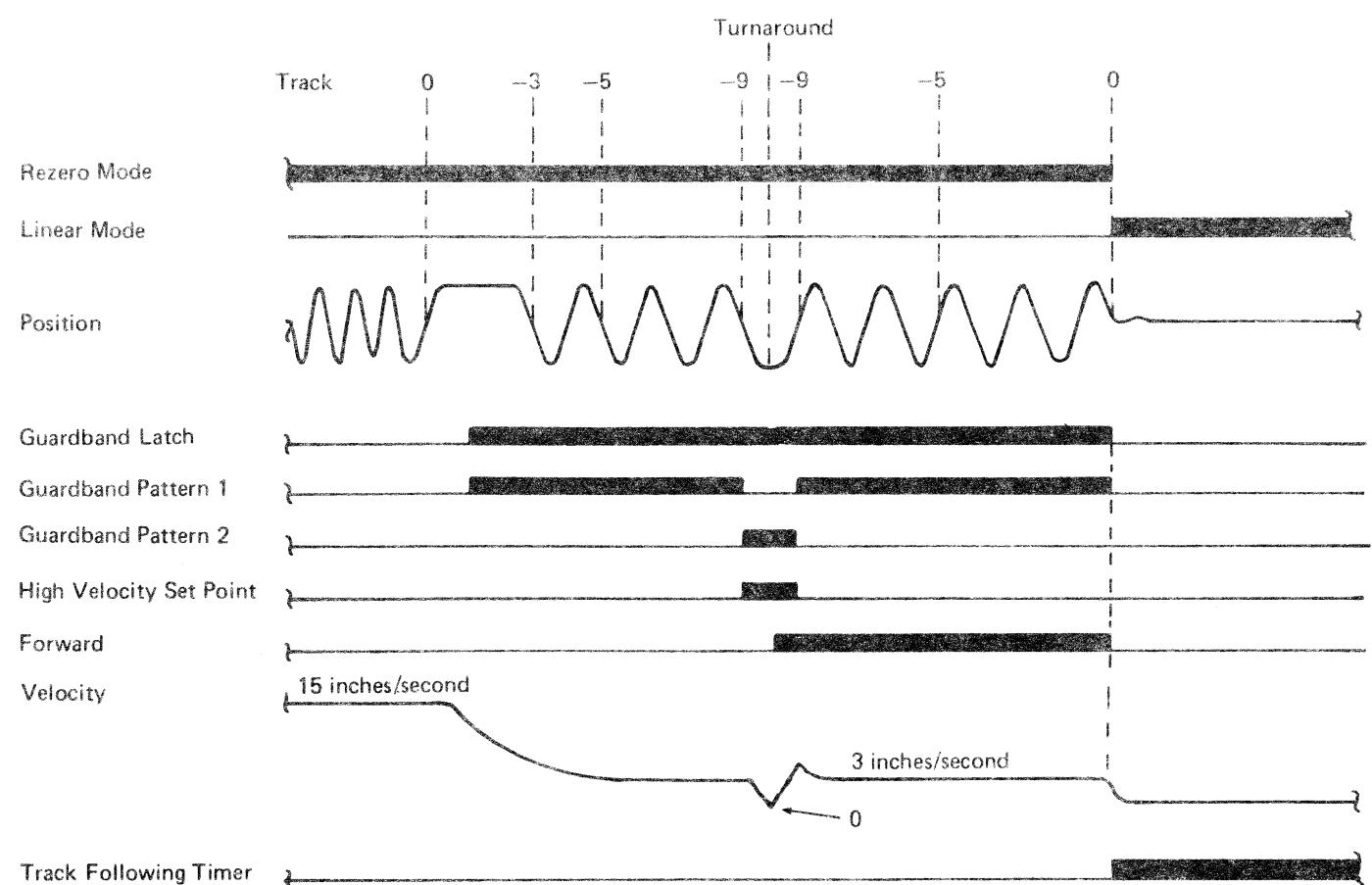

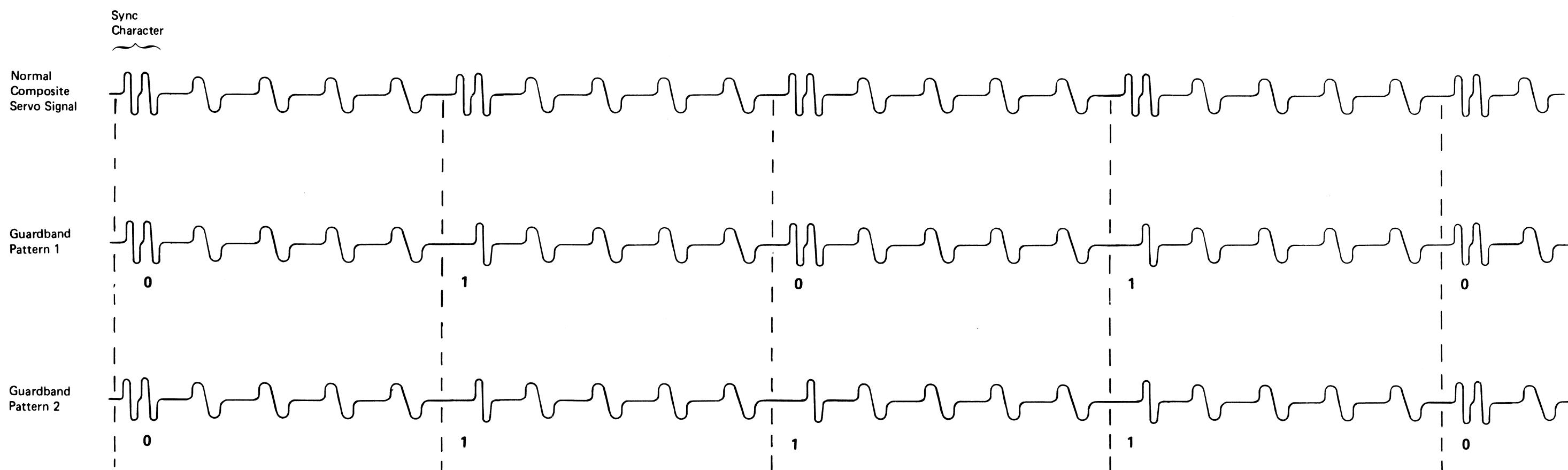

Guardband Pattern Detection OPER 131

Index Detection OPER 126

Rezero OPER 129

Seek OPER 139

State Sequence OPER 119

Track Following OPER 123

Address Conversion R/W 400

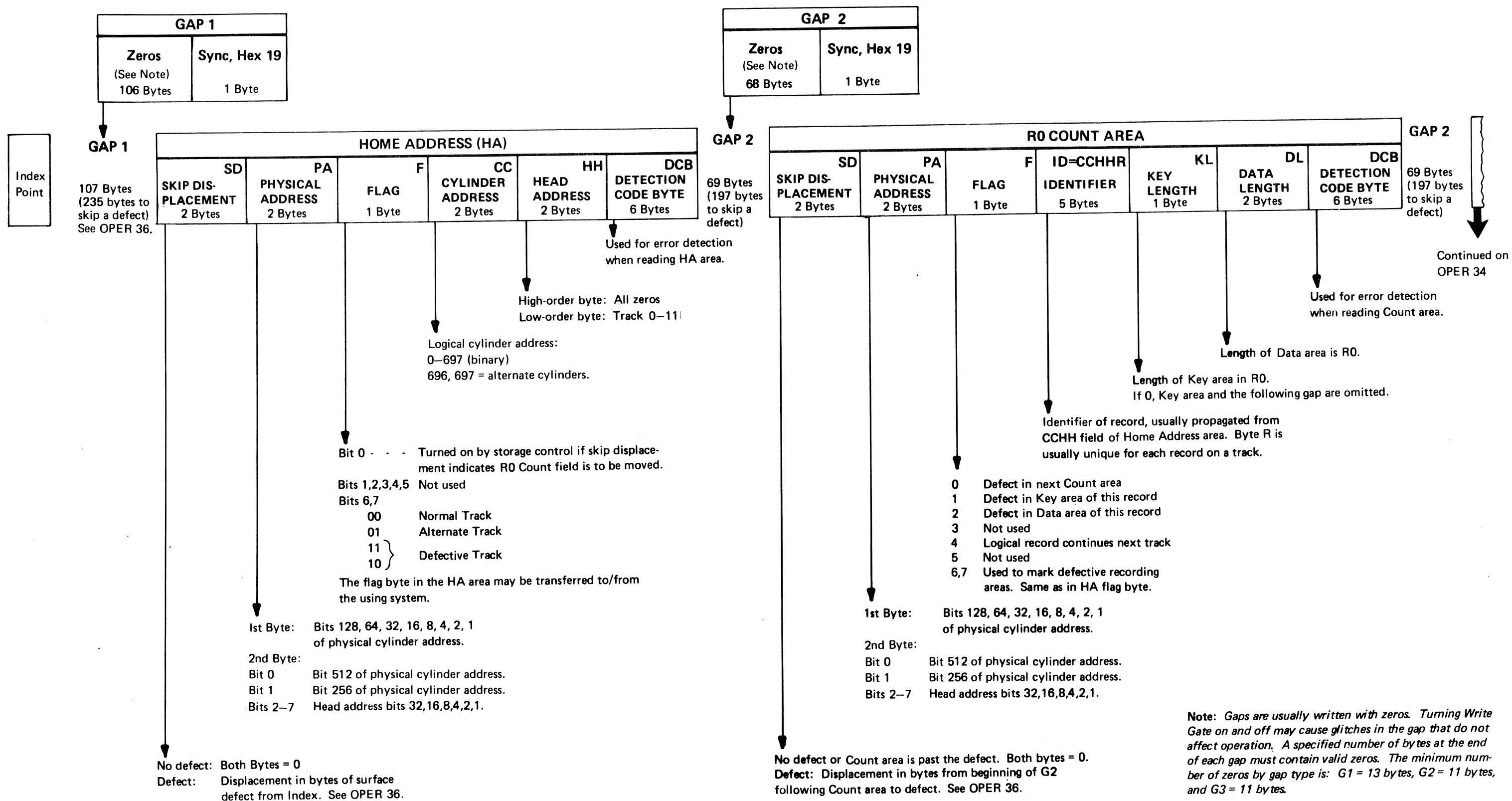

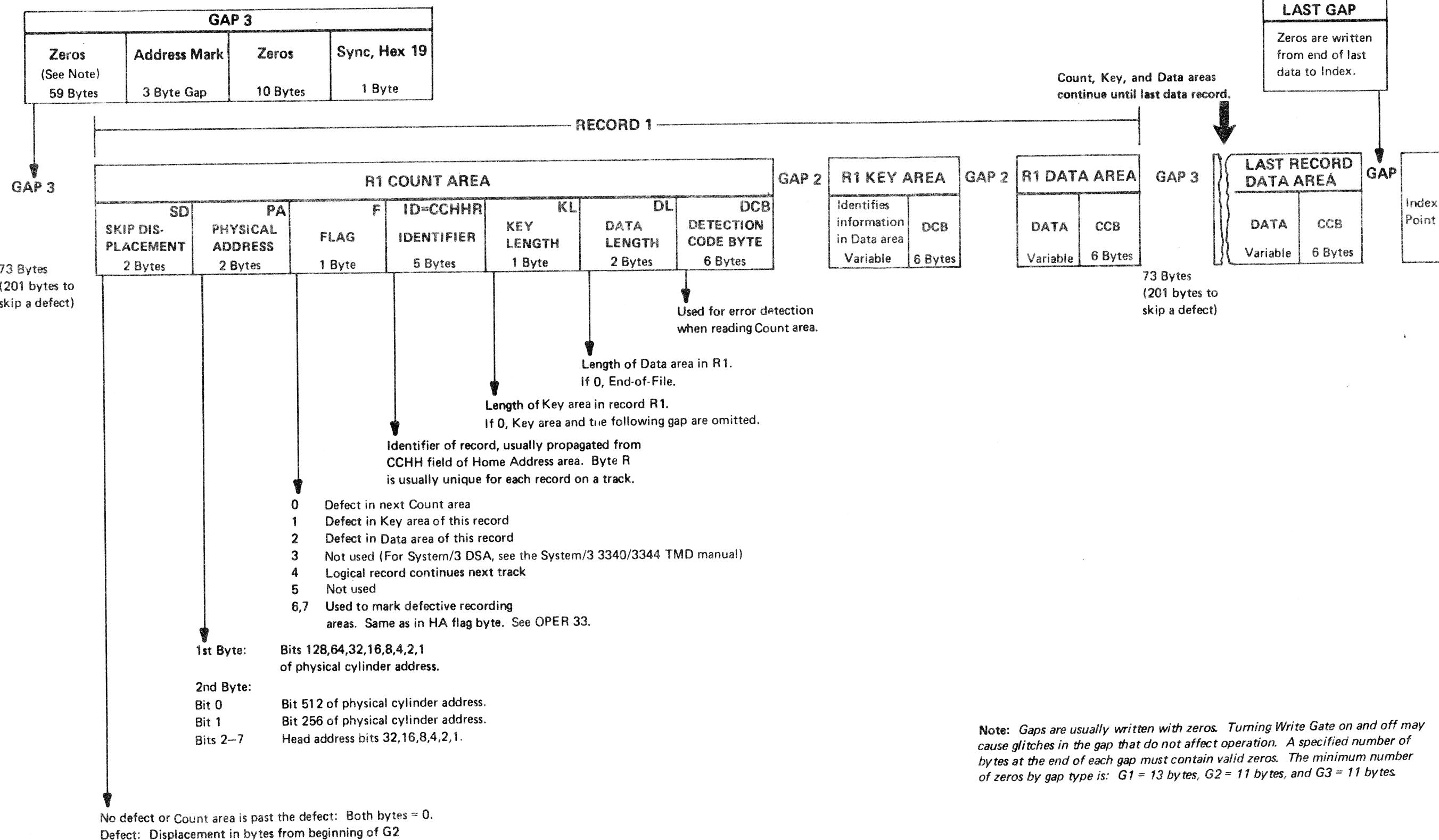

Address Mark OPER 34

Air Indicator LOC 1

Air Switch LOC 1

ALD (See Automated Logic Diagrams)

Alert Lines OPER 90

AP-1 MSG 50

Areas

Count OPER 33

Data OPER 34

Home Address OPER 33

Key OPER 34

Attention Pushbutton Checkout ACC 638

Attention Select Bus DEV-I 164

Attention/Select Response Bus OPER 92

Automated Logic Diagrams LGND 12

A1 Board LOC 1

## B

Base Plate Ground Check R/W 378, INST 4

Belt Removal and Replacement HDA 760

Bit Ring OPER 226

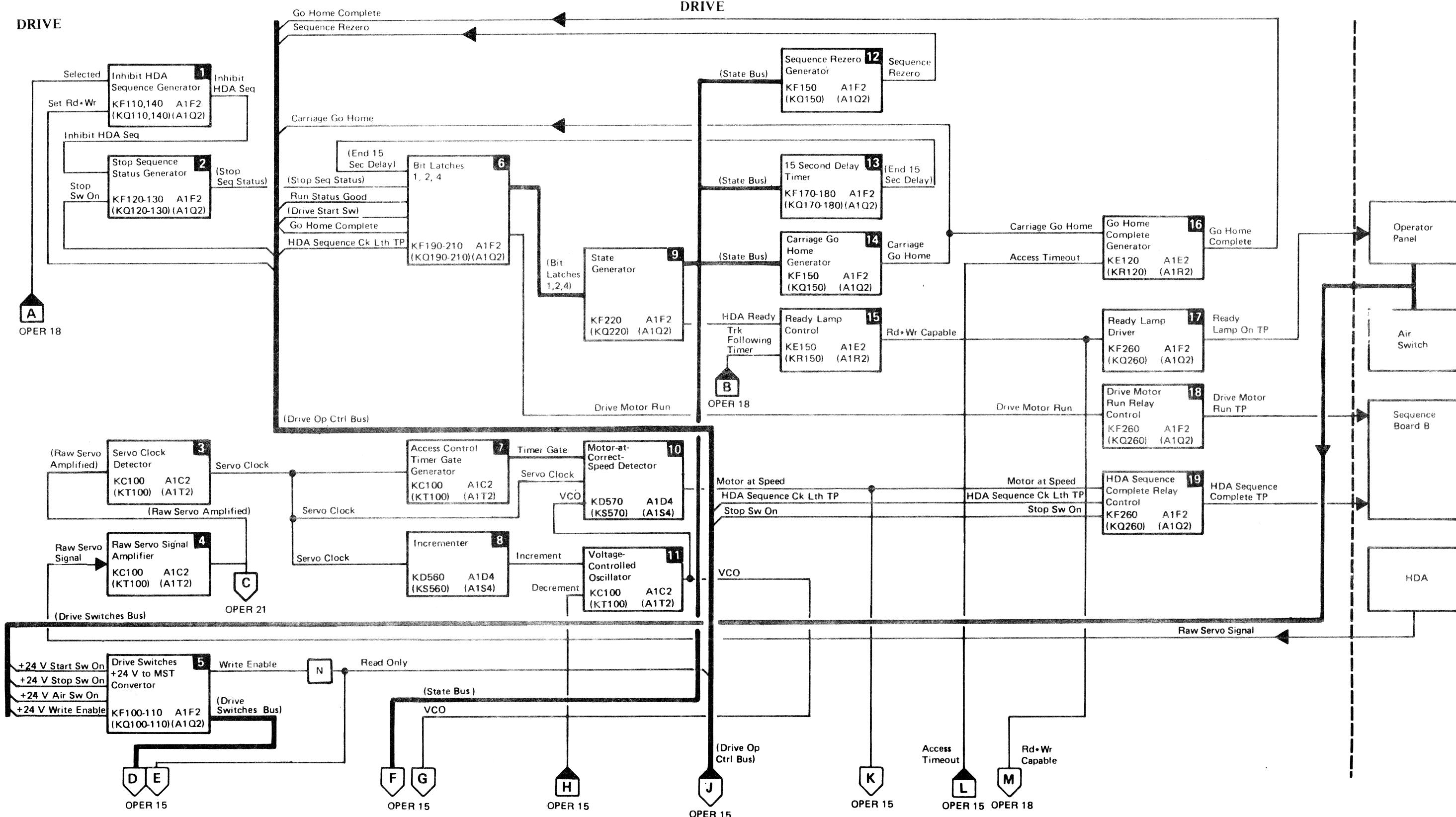

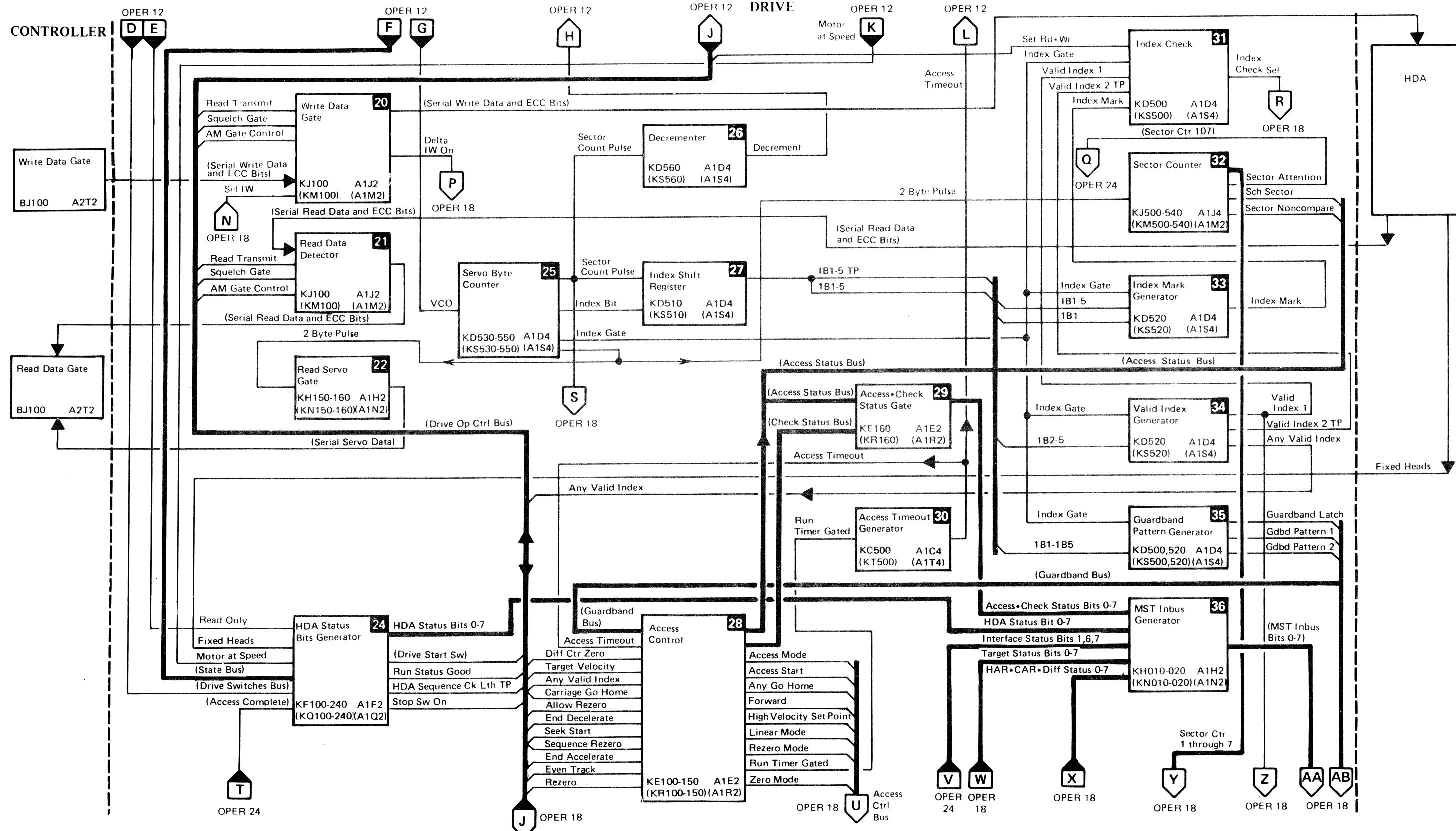

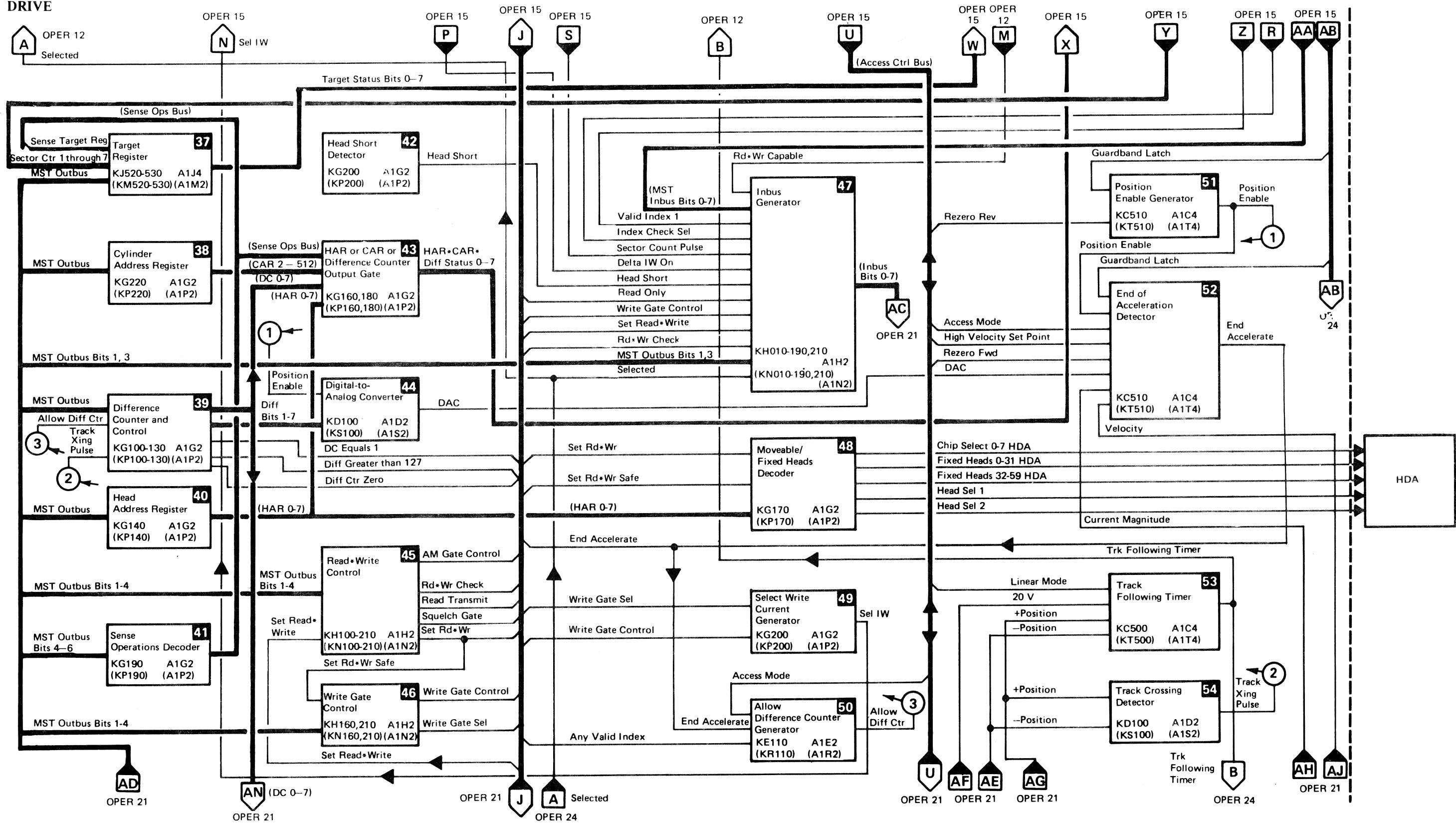

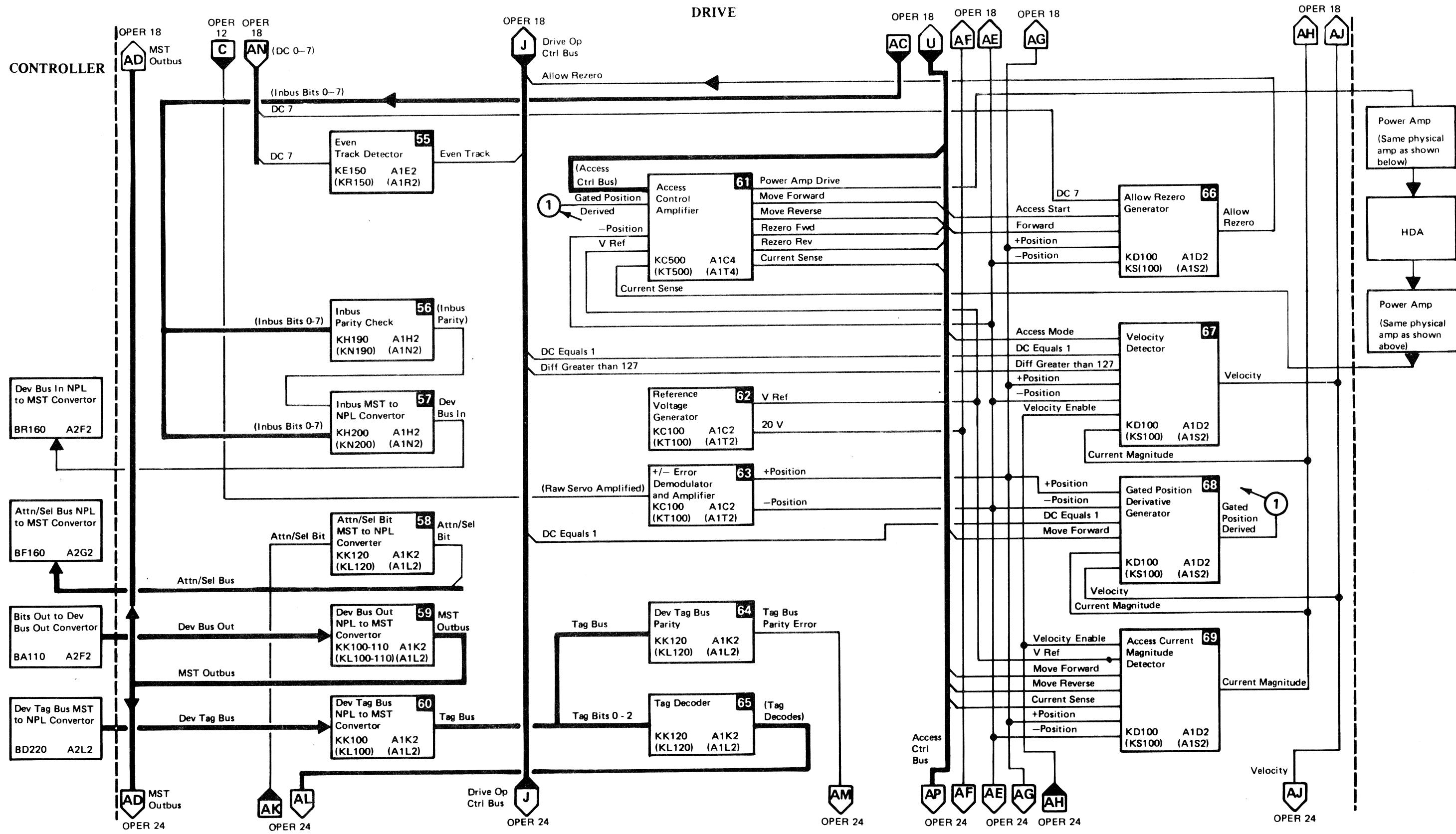

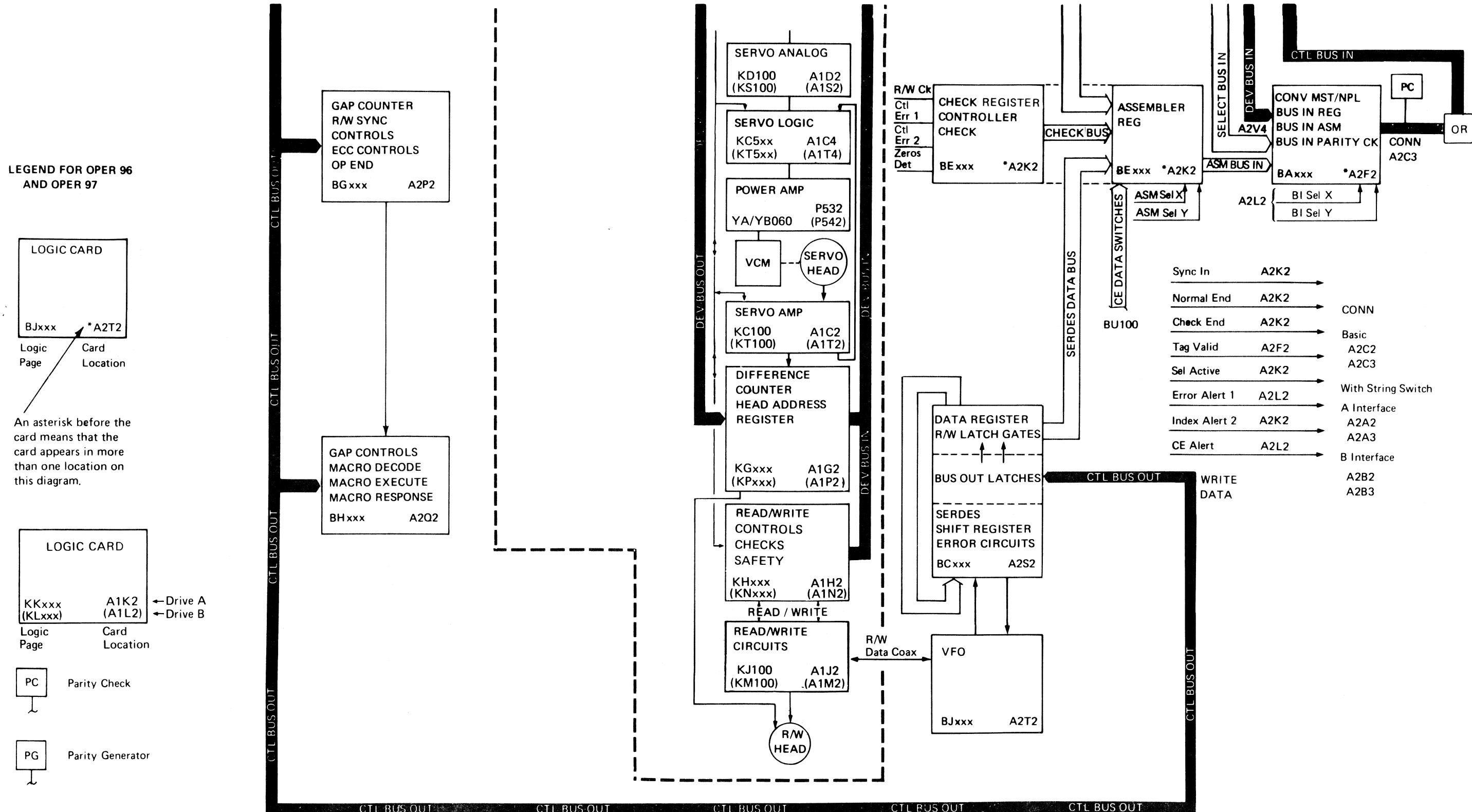

Block Diagrams LGND 10

## C

Cable Groups FSI 940

Cables LOC 1

Capacitors LOC 1

CAR (See Cylinder Address Register)

CB (See Circuit Breakers)

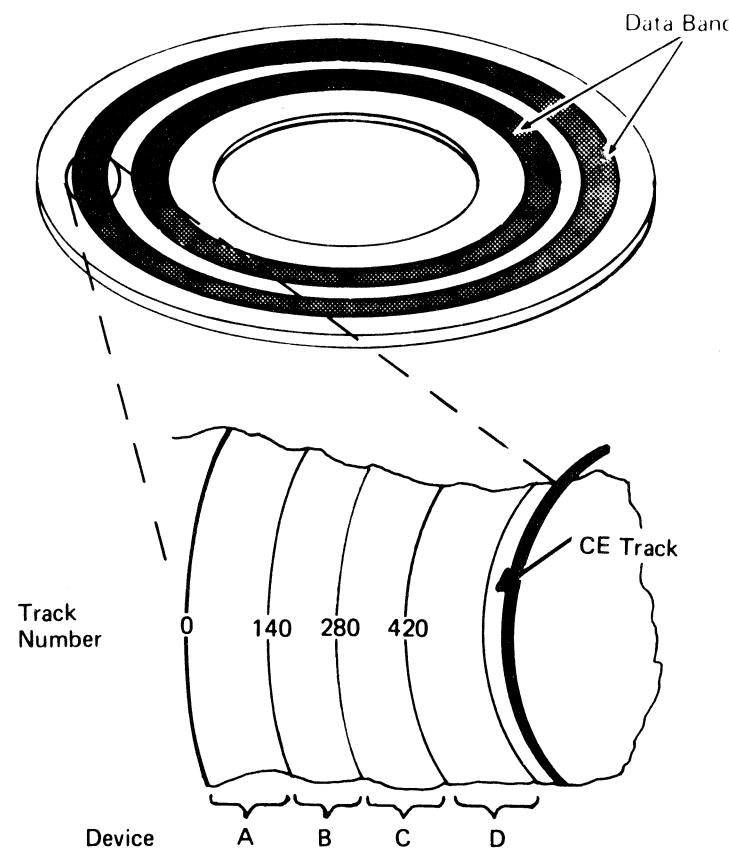

CE Cylinder OPER 32

CE Mode Switch LOC 1, PANEL 10

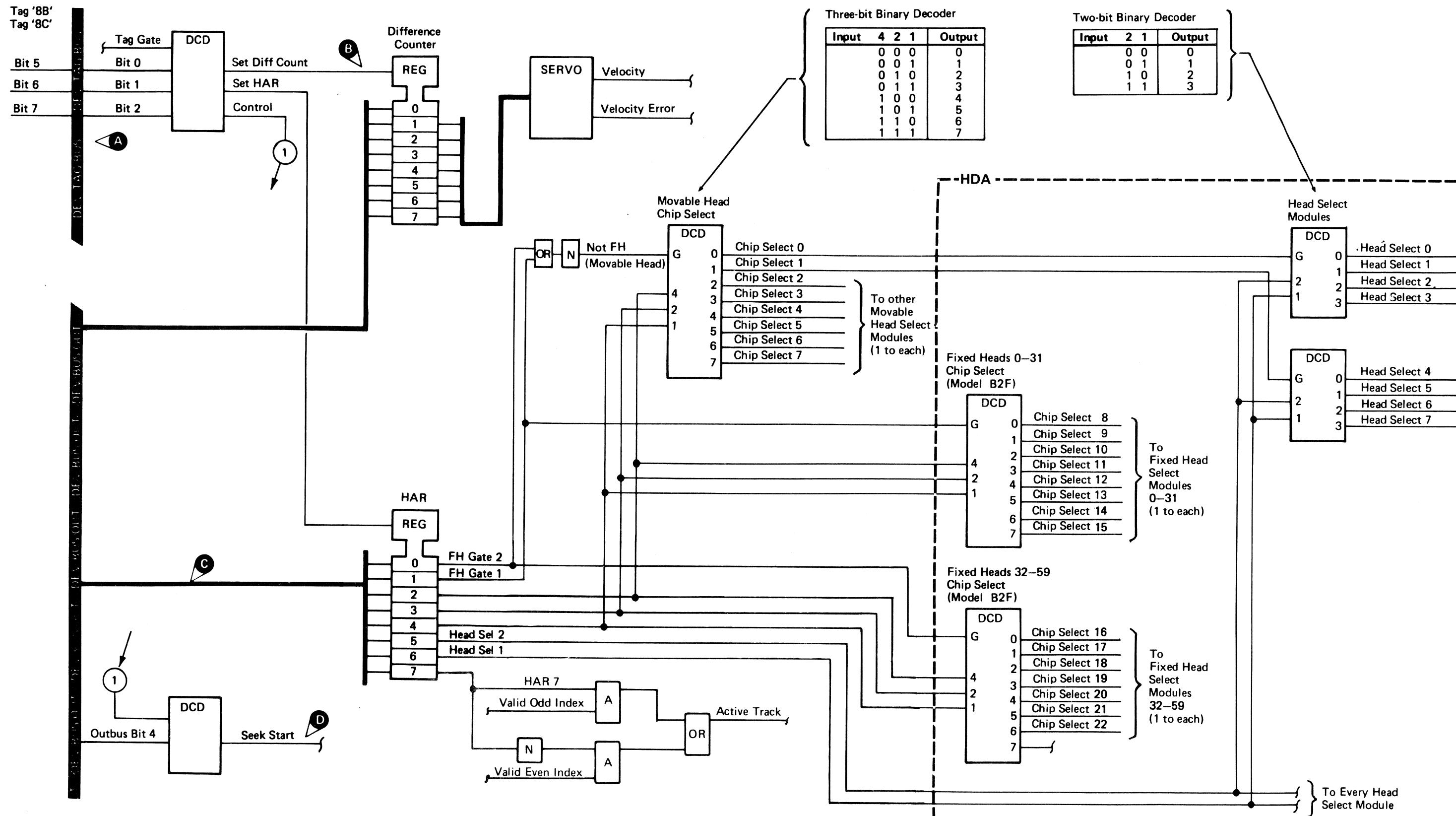

Chip Select OPER 140

Circuit Breakers LOC 1

Circuit Protectors LOC 1

Command Reject SENSE 105

Component Locations Index LOC 1

Connectors LOC 1

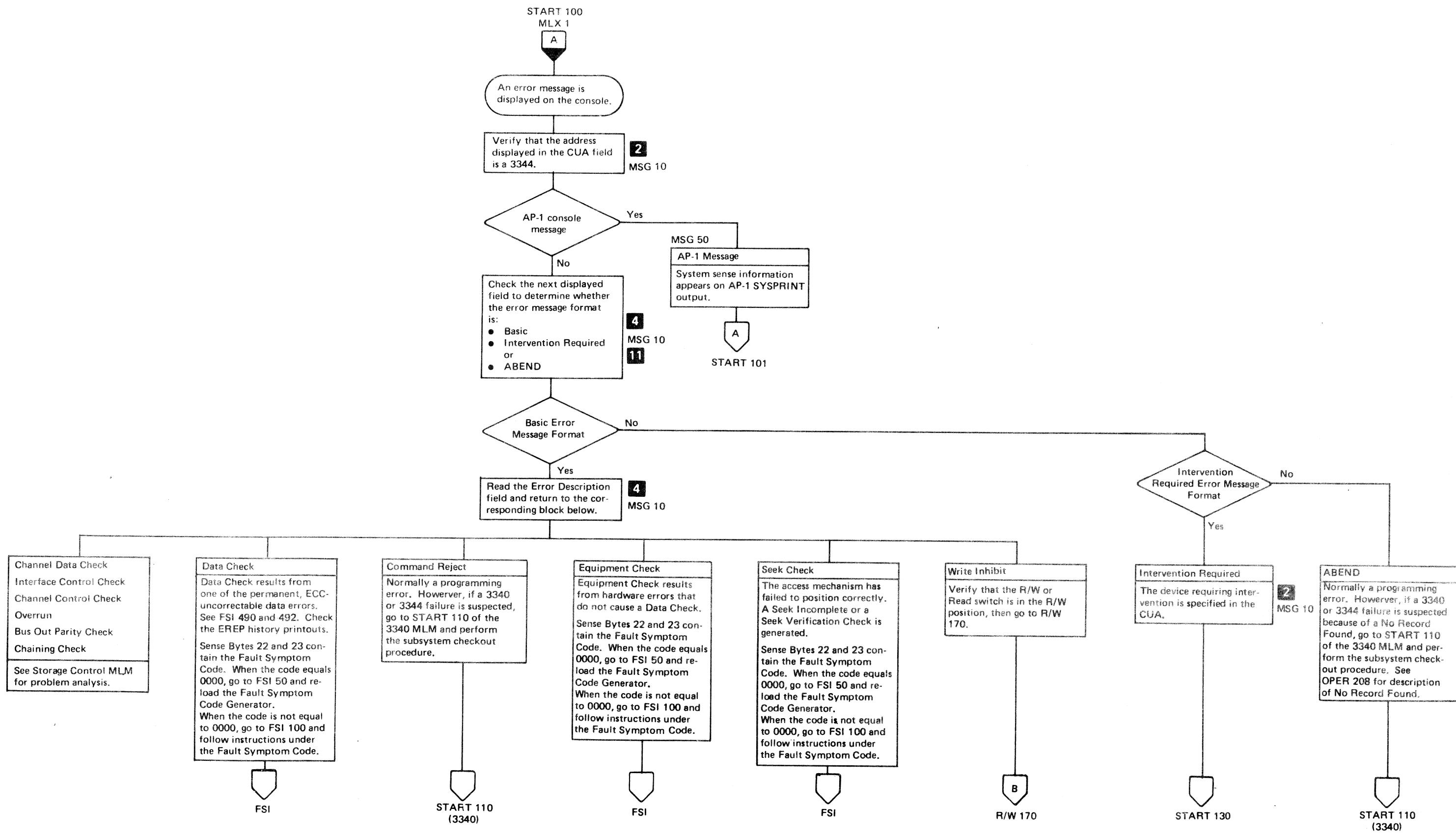

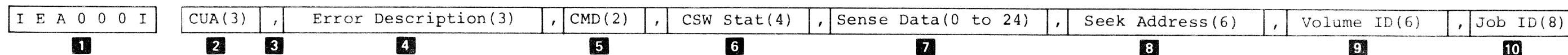

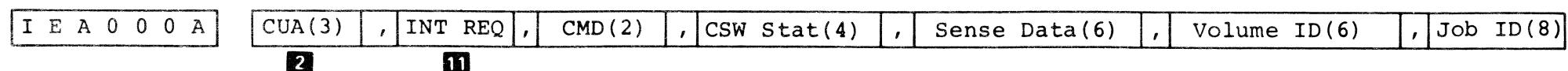

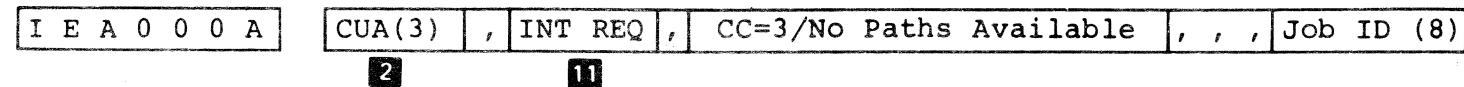

Console Message MSG 1

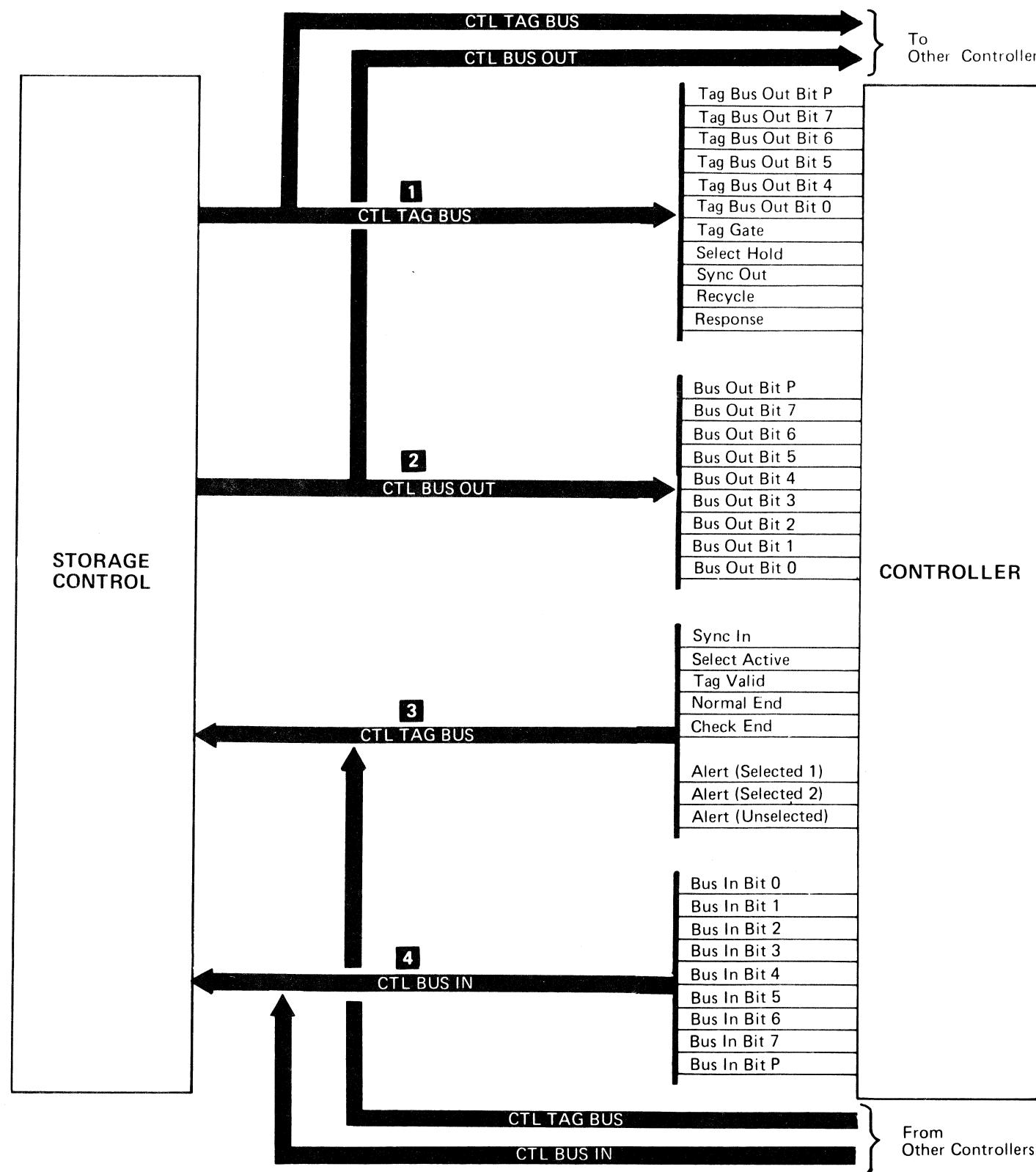

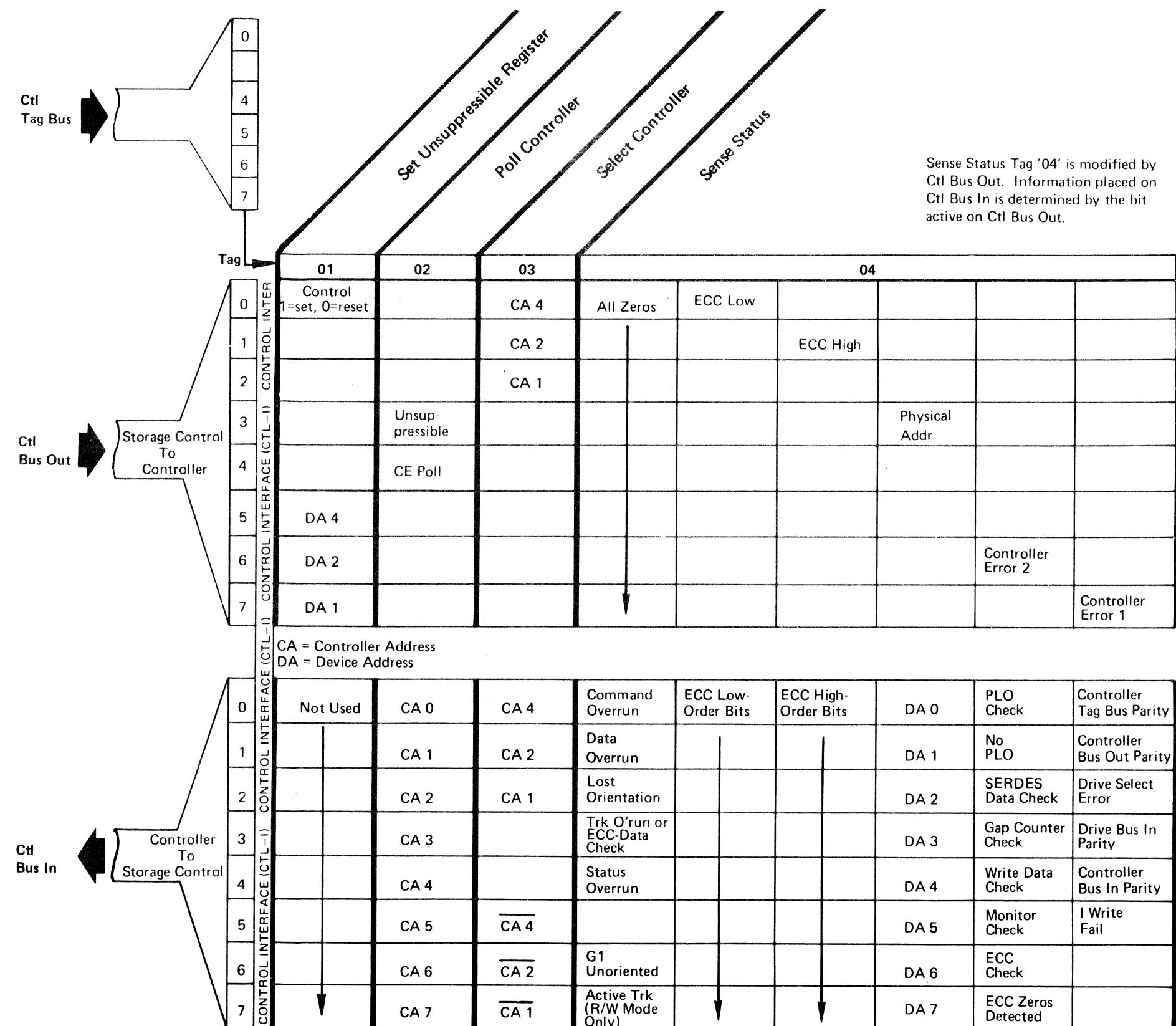

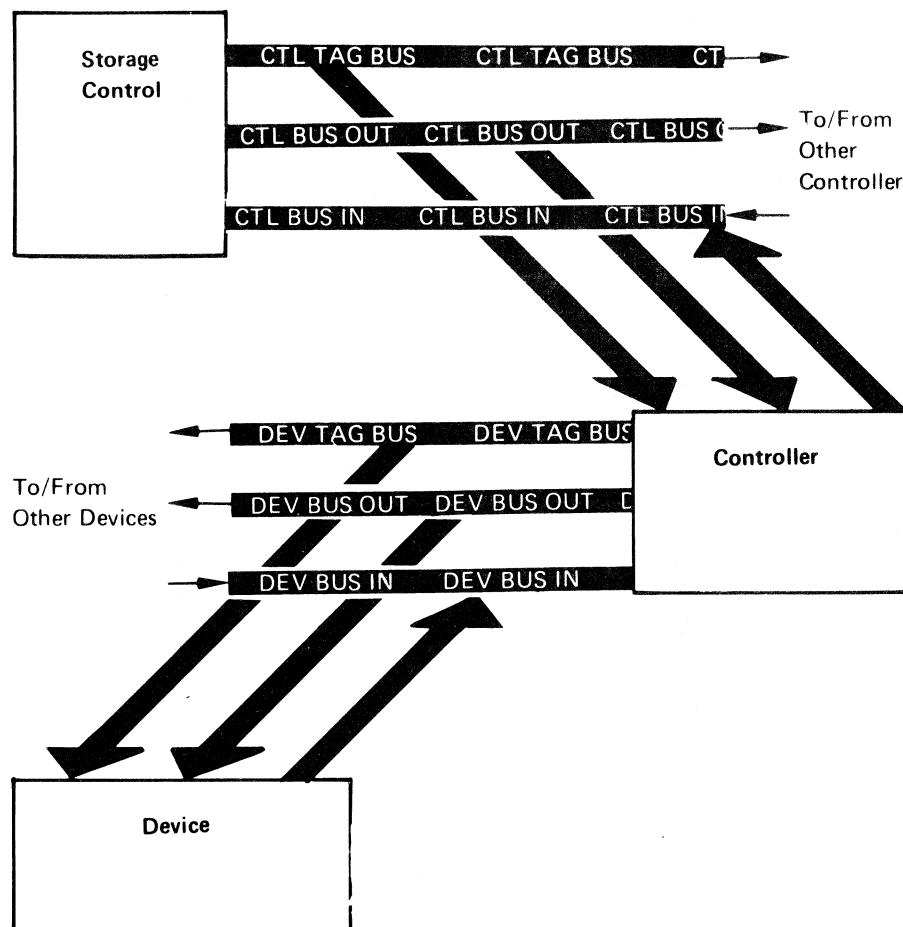

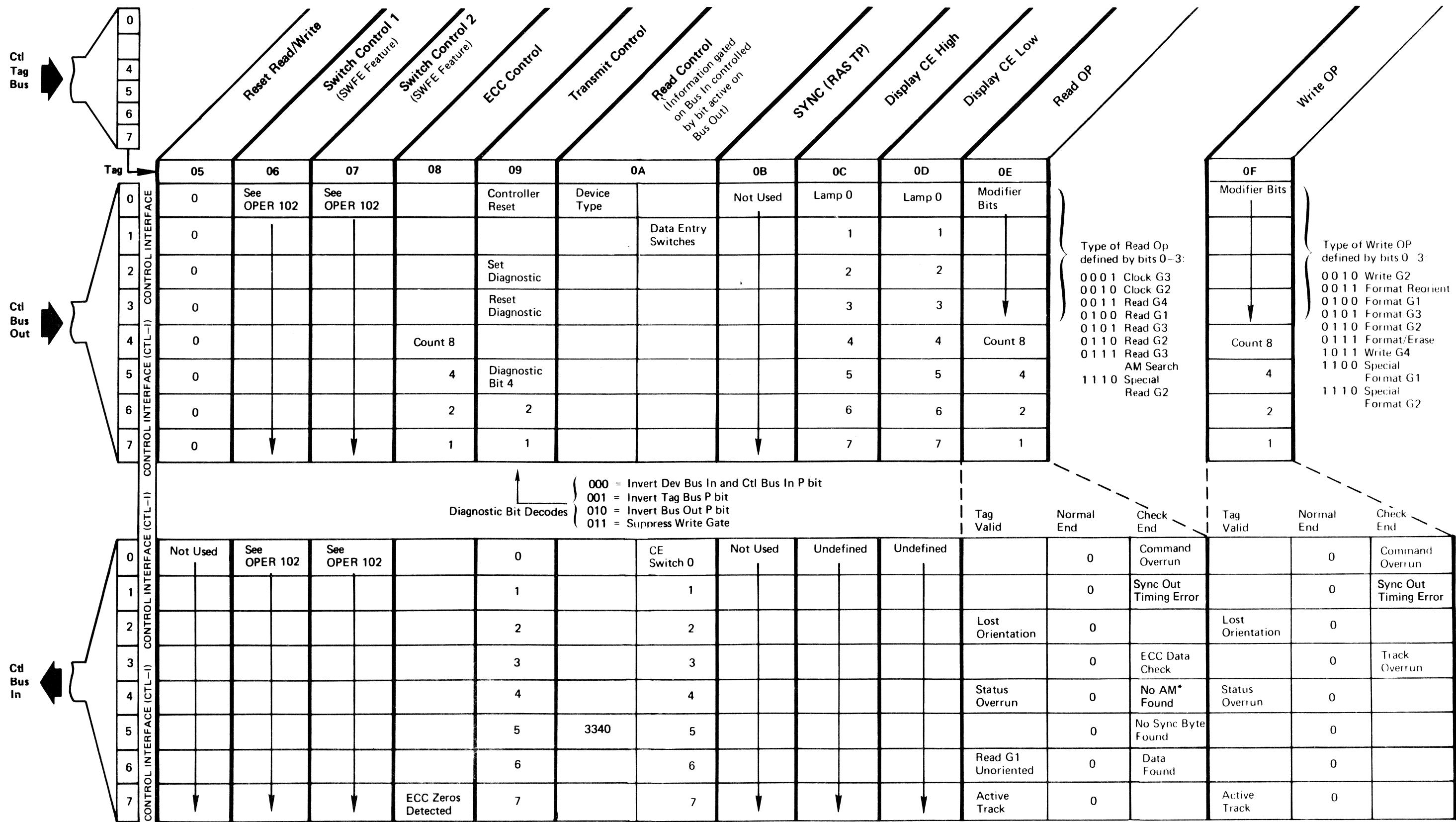

Control Interface

Description OPER 90

Tag Summary OPER 98

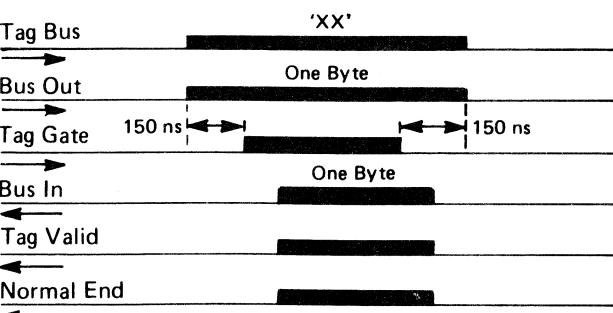

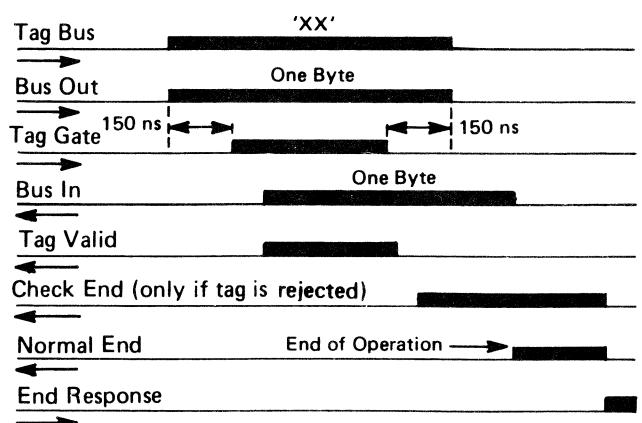

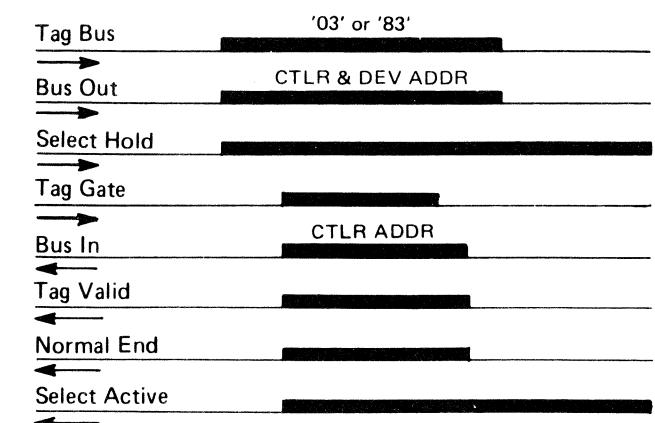

Timing OPER 95

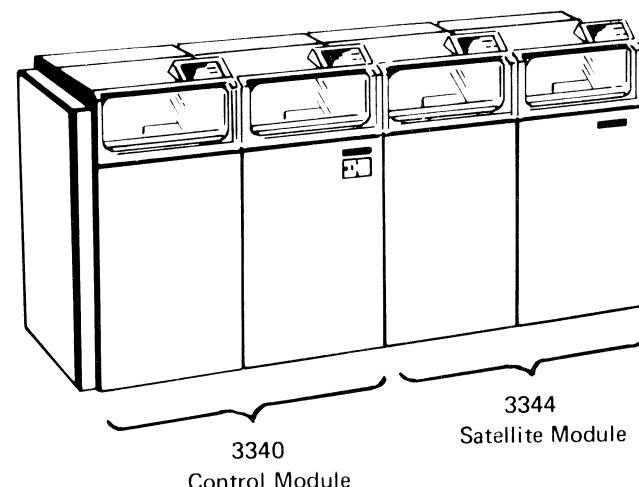

Control Module

Description OPER 3

Installation INST 2

Controller

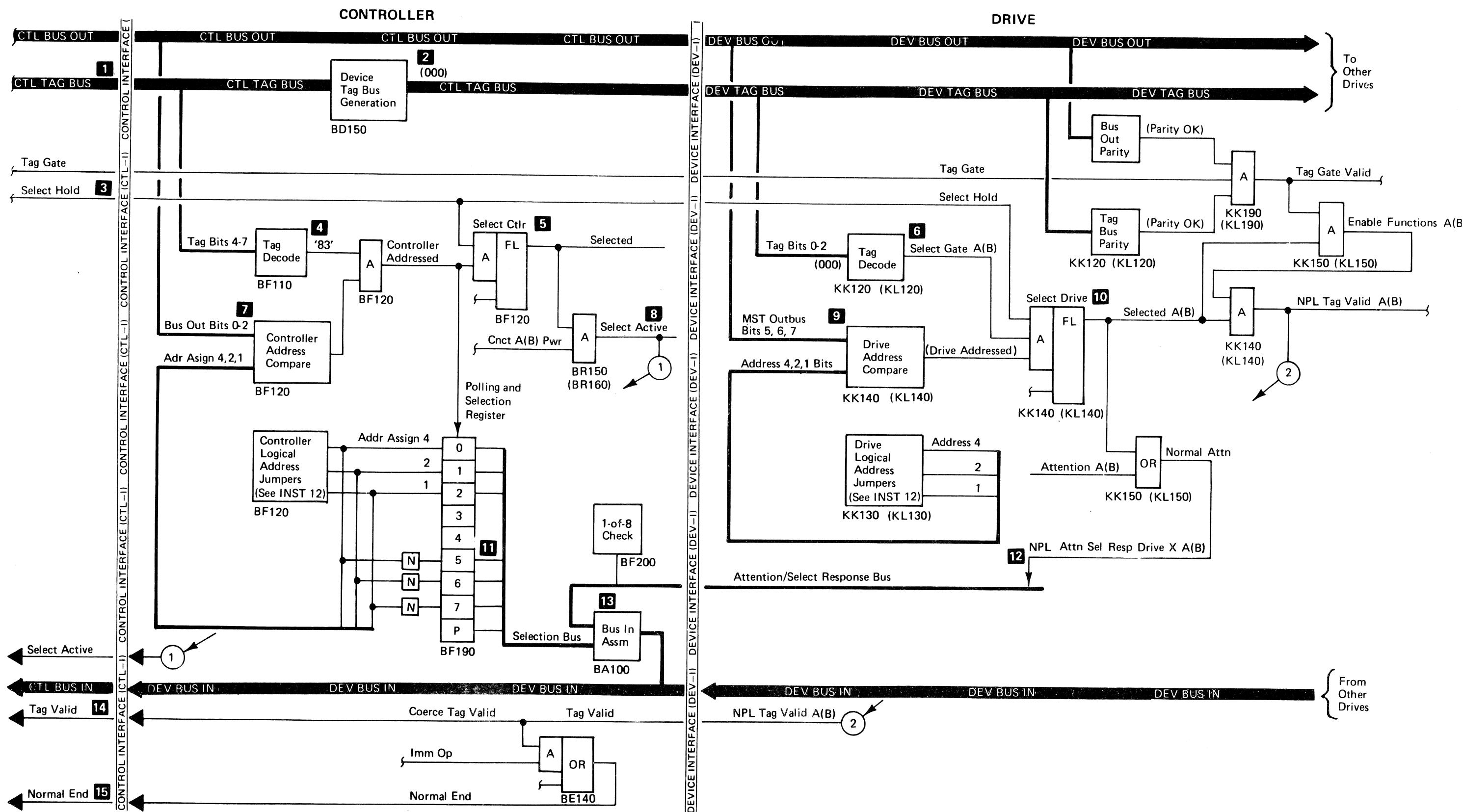

Addressing INST 12, OPER 110

Count Area OPER 33

Cover Latch HDA 770

Covers HDA 705

CP (See Circuit Protectors)

Cylinder Address Register OPER 105

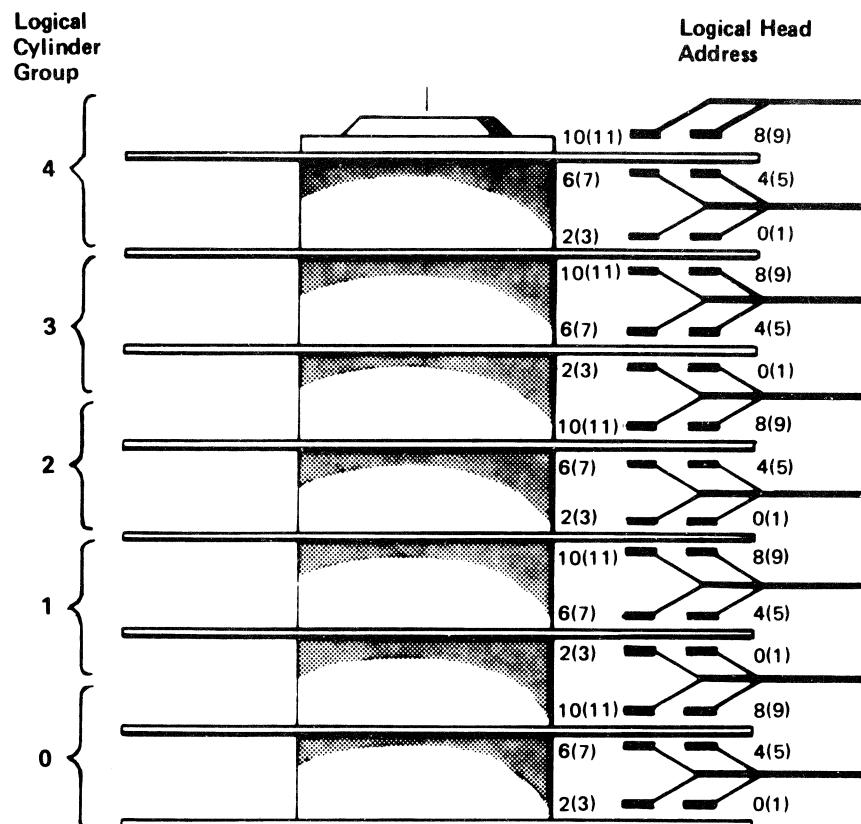

Cylinder, Logical OPER 31

## D

Data Area OPER 34

Data Checks R/W 300, SENSE 105

Data Surface OPER 30

DC Voltage Check PWR 290

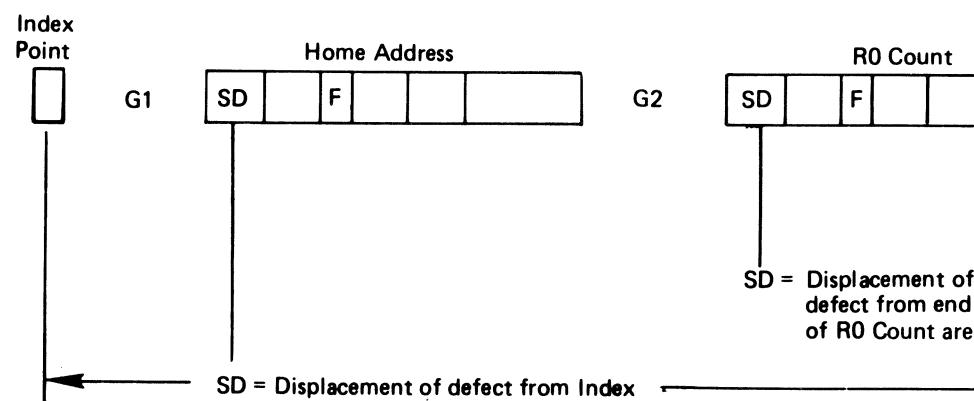

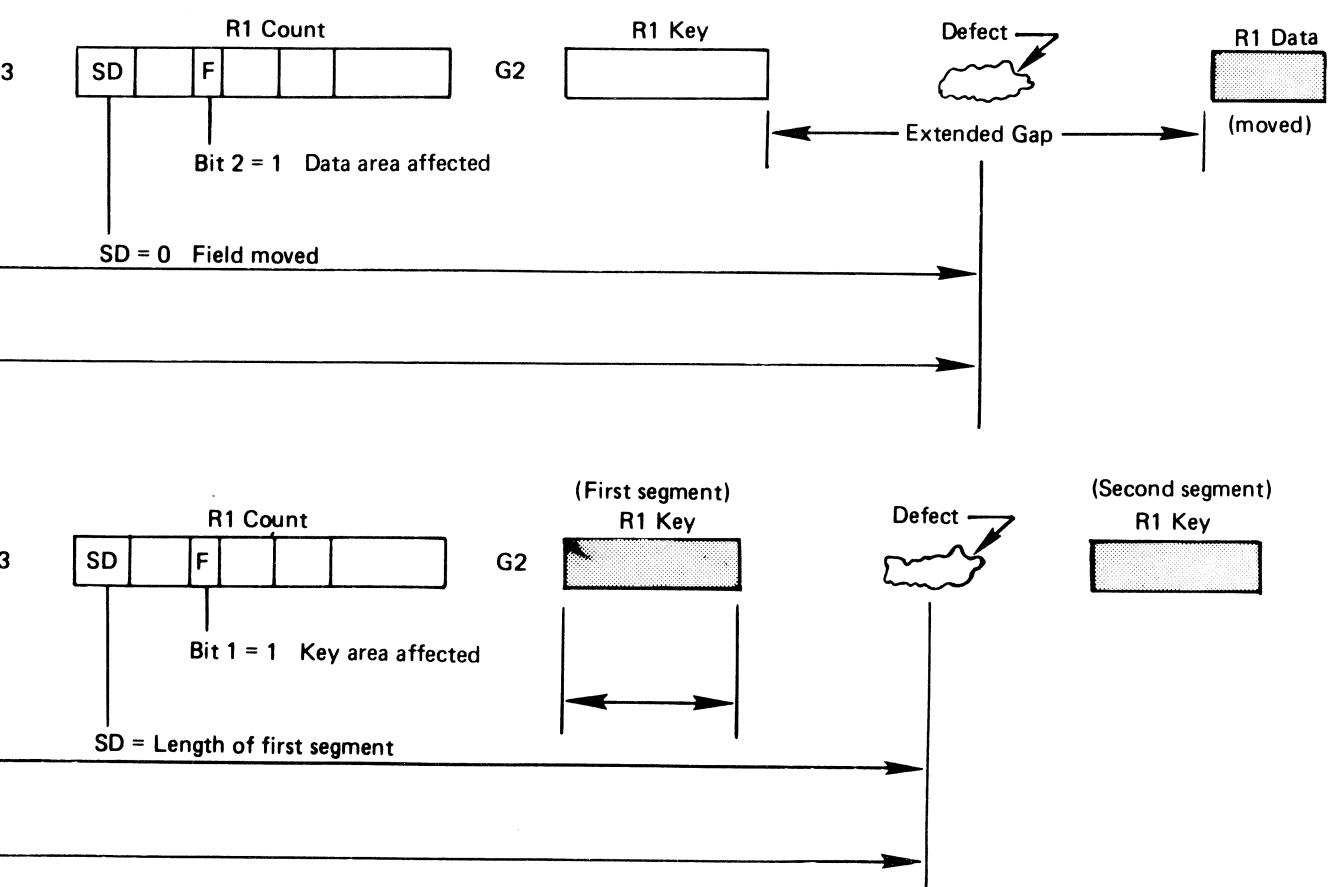

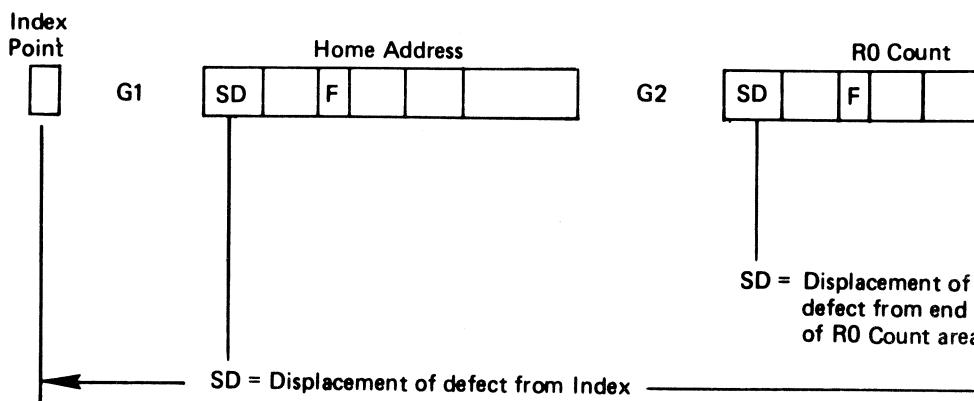

Defect Skipping OPER 36

Definitions LGND 16

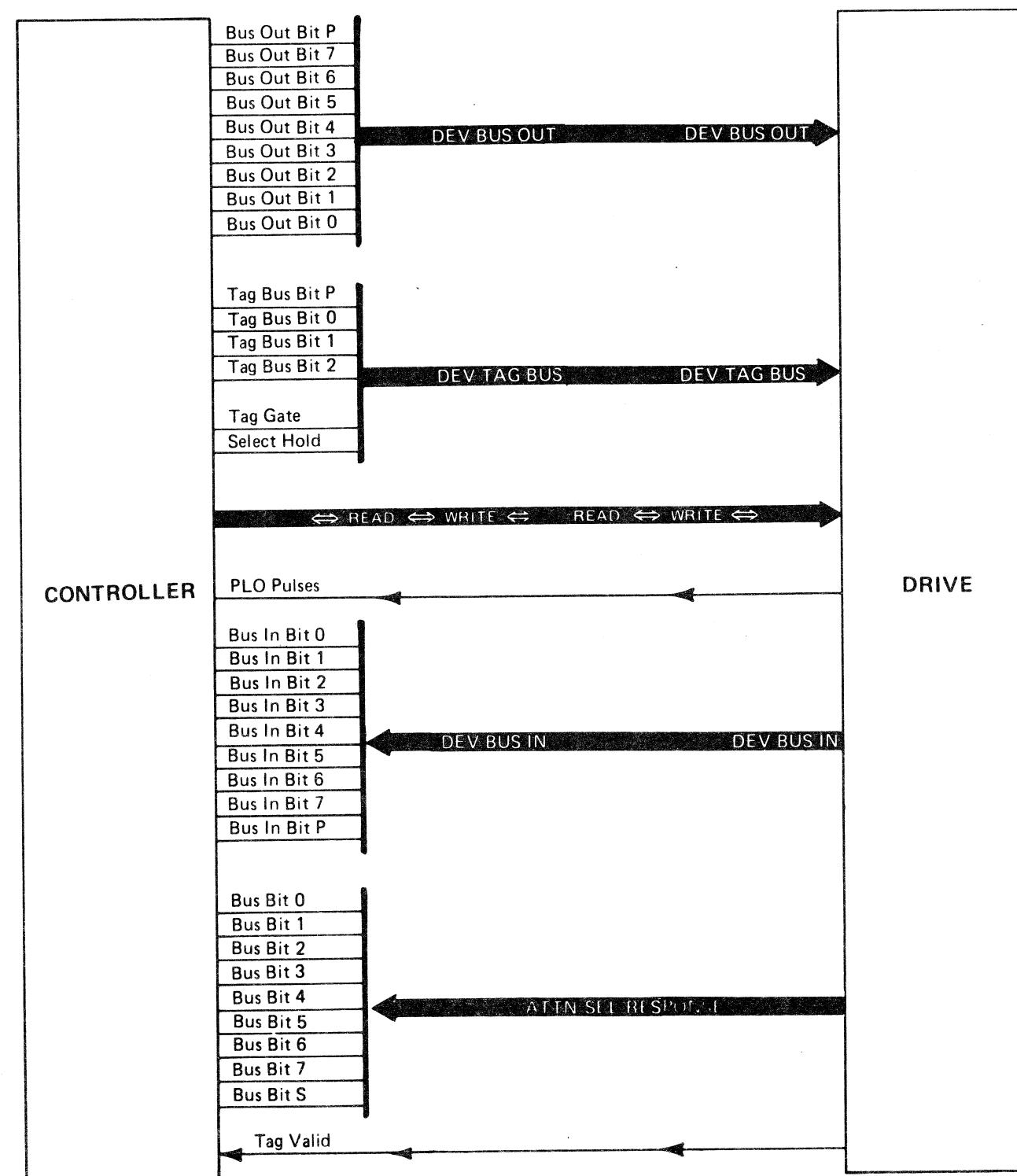

Device Interface

Cables DEV-I 100

Description OPER 92

Tag Summary OPER 98

Timing OPER 95

Device Status DEV-I 184

Device Type Gate OPER 103

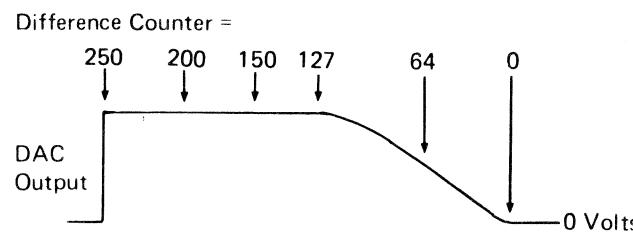

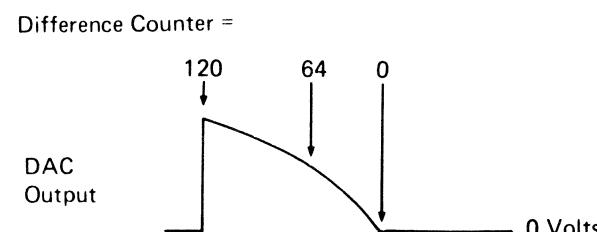

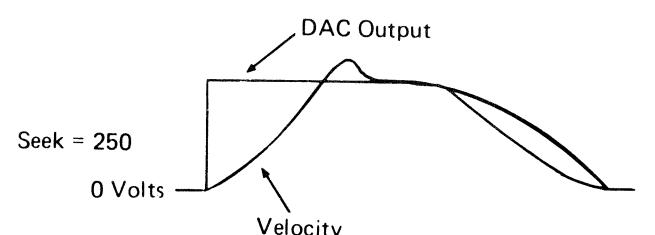

Difference Counter OPER 139

Drive

Addressing INST 12

A1 Board LOC 1

Functional Units OPER 10

Selection OPER 110

Dynamic Servo Checkout ACC 630

## E

ECC (See 3340 MLM)

End Conditions

Check End OPER 103

Error Alert OPER 103

Normal End OPER 90, OPER 103

End of Cylinder SENSE 105

Environmental Data Present SENSE 105

Equipment Check SENSE 105

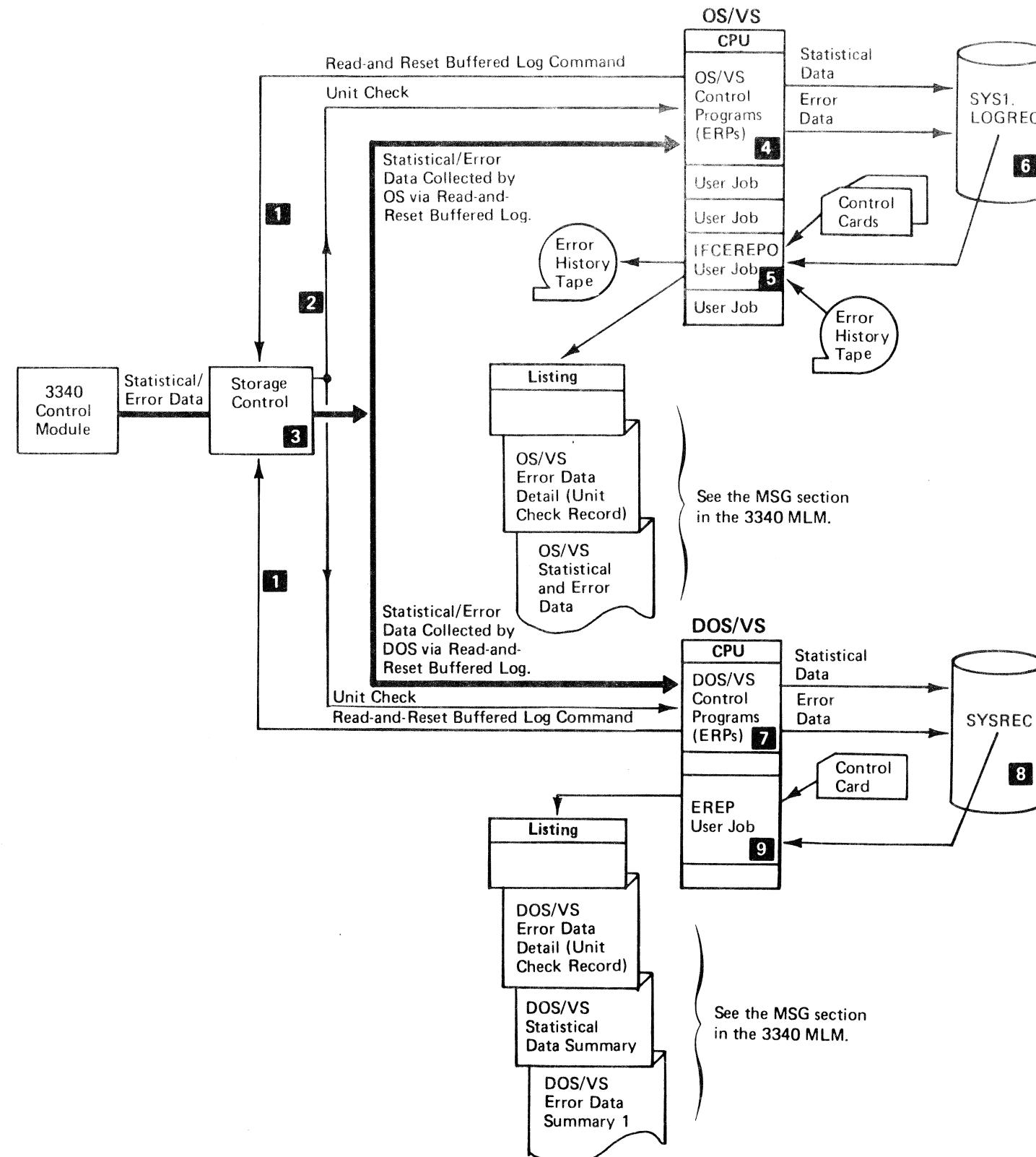

EREP MSG 20

Error Code Dictionary MICRO 1

Error Condition Table MSG 14

Error Data MSG 20

Error Message Analysis MSG 9, MSG 12

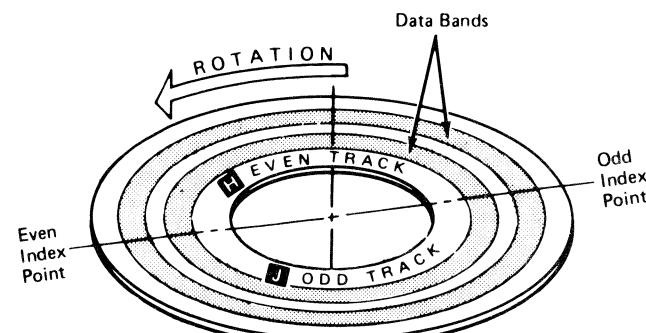

Even Index OPER 31

Extended Operation OPER 95

## F

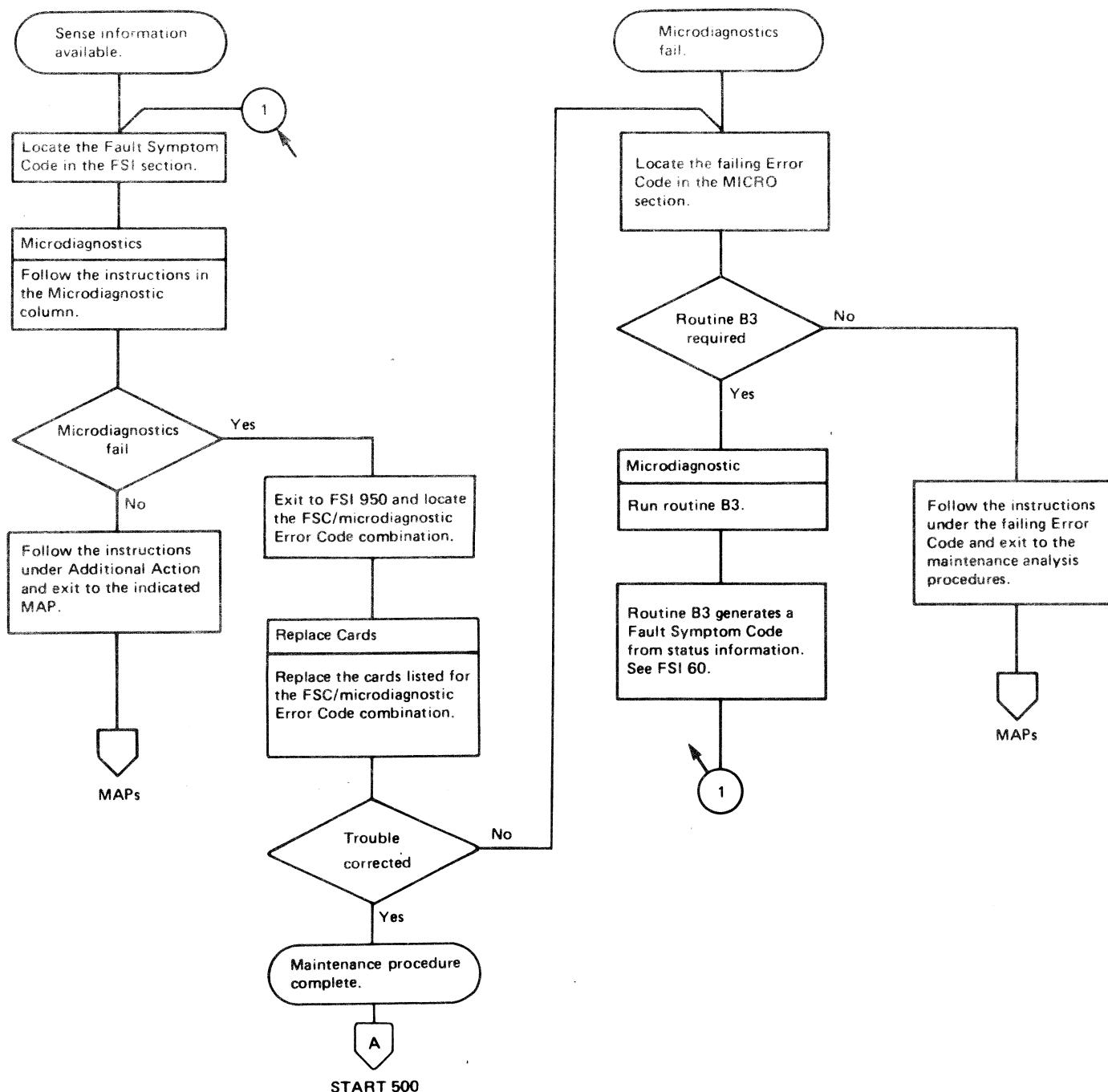

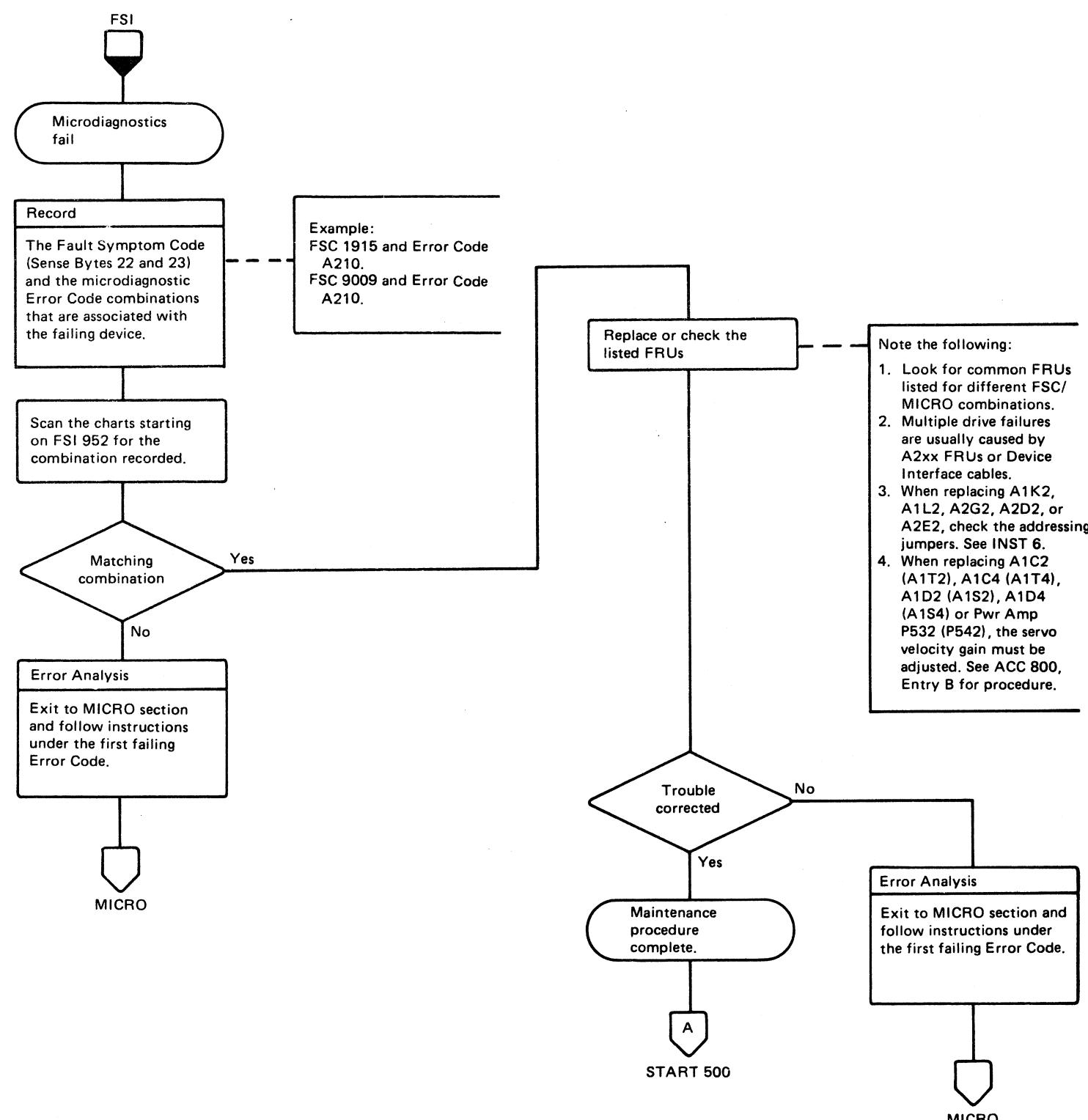

Fault Symptom Code FSI 1

Features and Models

B2F OPER 250

Fixed Head Model OPER 250

Fields (See Areas)

File Protected SENSE 105

Filter LOC 1

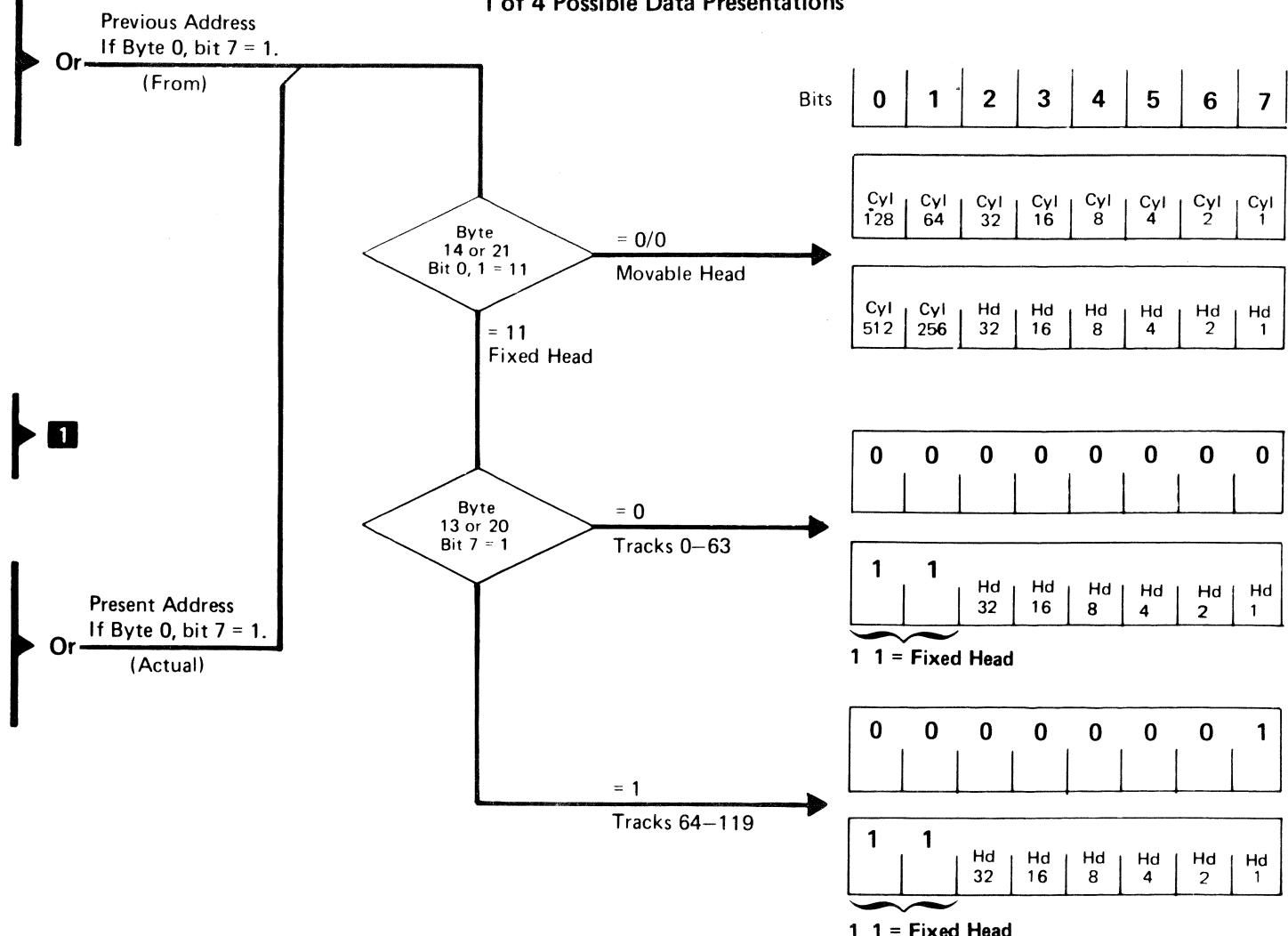

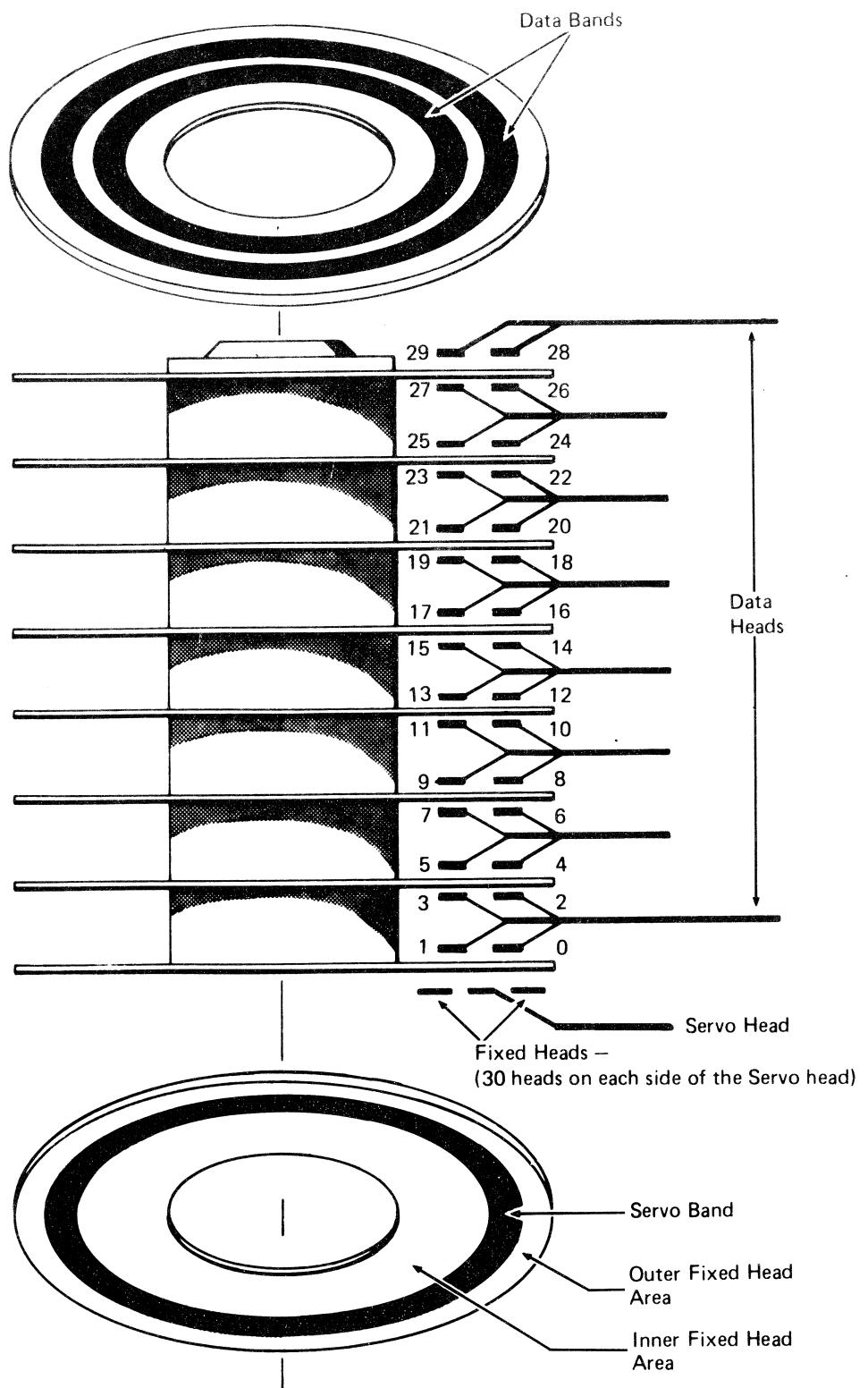

Fixed Heads

Description OPER 250

Location OPER 30

Formats SENSE 1

FSC/Micro Matrix FSI 950

Functional Units OPER 10

## G

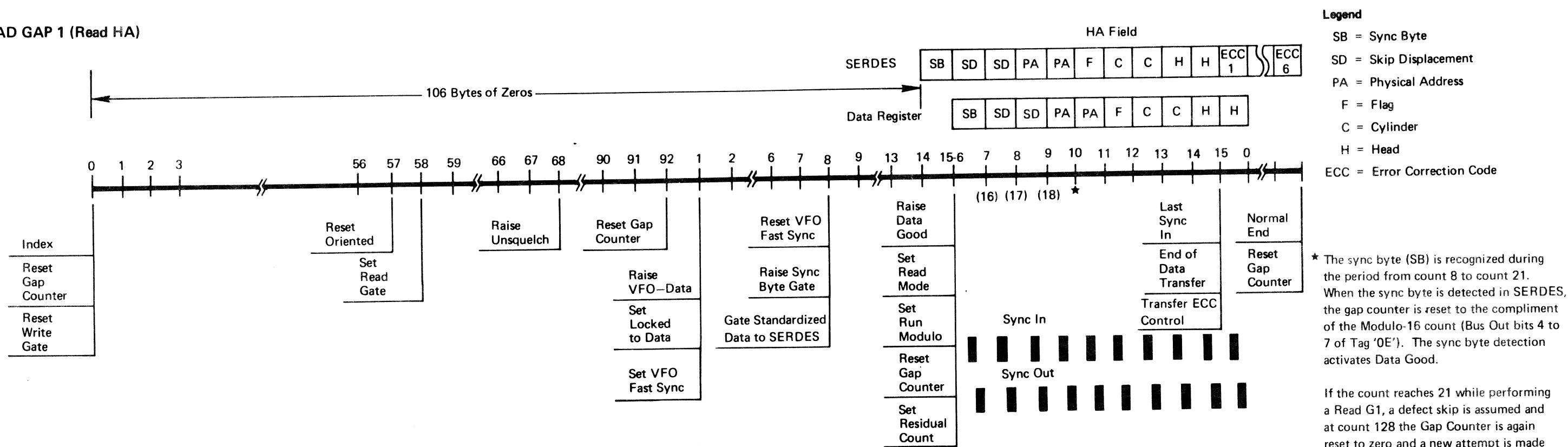

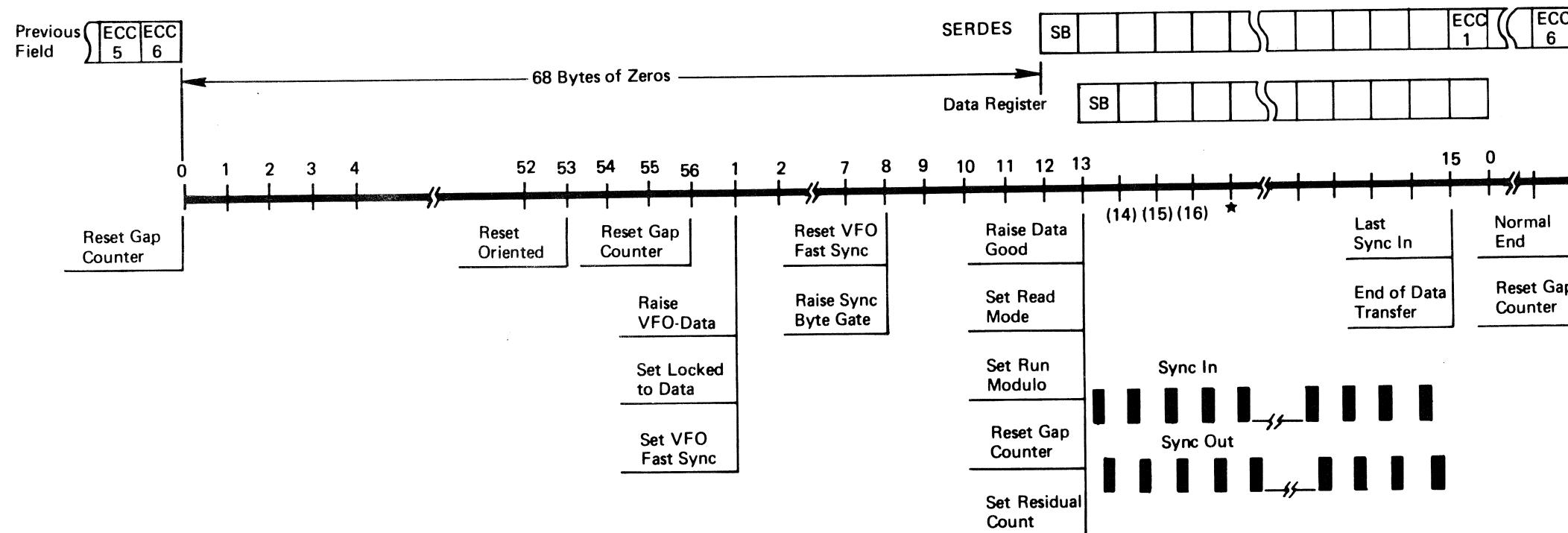

Gap Counter OPER 232

Gaps OPER 33

Glossary LGND 16

Go Home Pulser (P535) LOC 14

Guardband Pattern Detection OPER 131

## H

HAR (See Head Address Register)

HDA (See Head/Disk Assembly)

HDA Ready Sequence Theory HDA 500-502

HDA Stop Sequence HDA 504

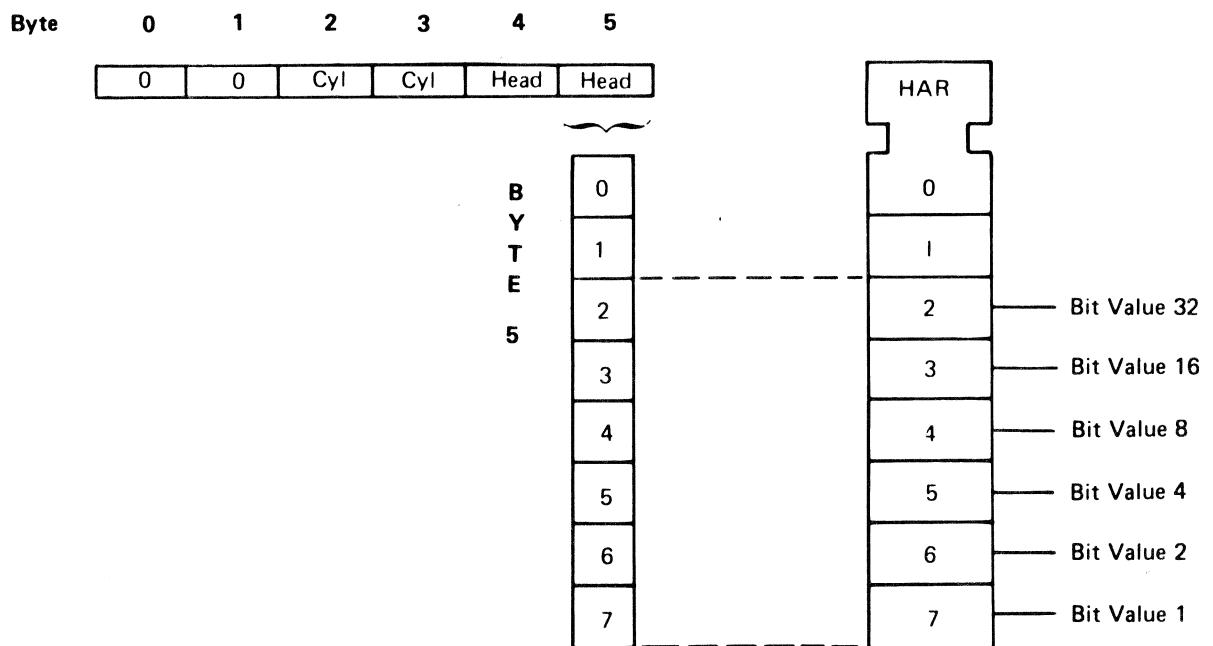

Head Address Register OPER 139

Head/Disk Assembly

Adjustments HDA 700

Cable Checkout Procedure R/W 372

Cable Swap Procedure HDA 713

Checkout, Basic HDA 711

Checkout, Servo ACC 660

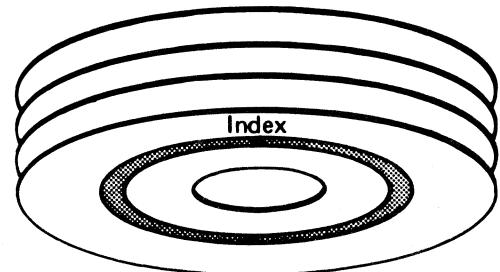

Description OPER 30

Ready Sequence HDA 500

Relay Sequence HDA 510

Removal and Replacement HDA 710

States HDA 500

Stop Sequence HDA 504

Theory HDA 500

Voltage Check R/W 376

Head Locations OPER 31

Head Positioning OPER 30

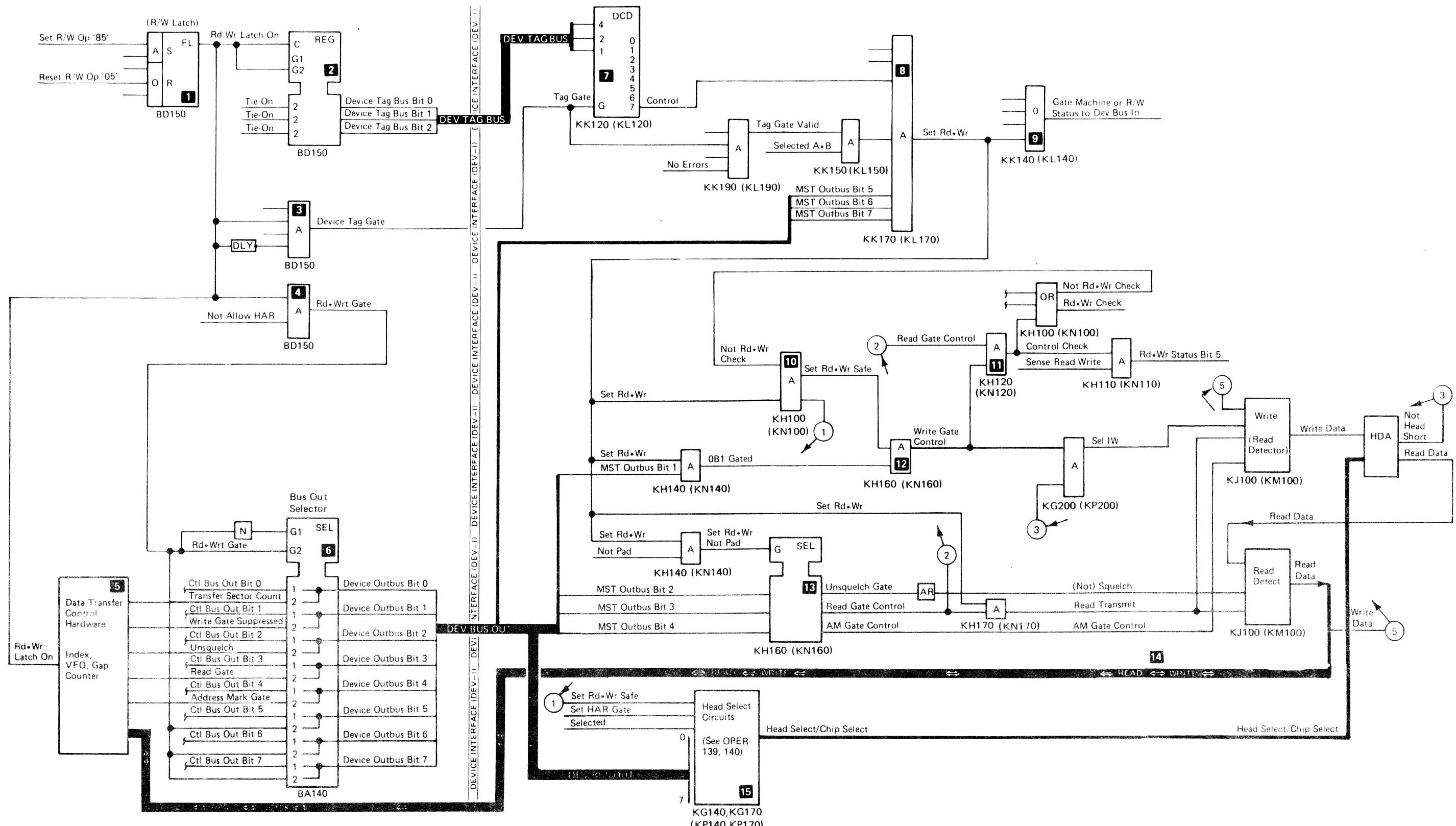

Head Selection OPER 140

Heads

Data OPER 30

Fixed OPER 30

Servo OPER 30

Home Address OPER 33

## I

Immediate Operation OPER 95

Inbus Dot OR DEV-I 184

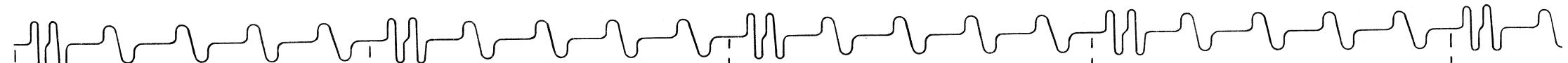

Index Detection OPER 126

Index Point OPER 31

Indicators (Lights)

Air LOC 14

Attention LOC 16

Ready LOC 16, PANEL 10

Start LOC 14

Stop LOC 14

Inductors LOC 1

Installation Procedures INST 1

Interface

Control OPER 90

Data and Control Flow OPER 96

Device OPER 92

Tag Description OPER 102

Tag Summary OPER 98

Timing OPER 95

Interframe Cables DEV-I 100

Intervention Required MSG 10, SENSE 105, START 130

Invalid Track Format SENSE 105

## J

Job ID MSG 10

Jumpers

Addressing INST 12

Sequence INST 6

## K

Key Area OPER 34

## L

Lamps (See Indicators)

Logical Addressing OPER 31

Logical to Physical Address Conversion R/W 400

Logical Volumes OPER 32

Long Connection OPER 102

## M

Maintenance Philosophy START 50

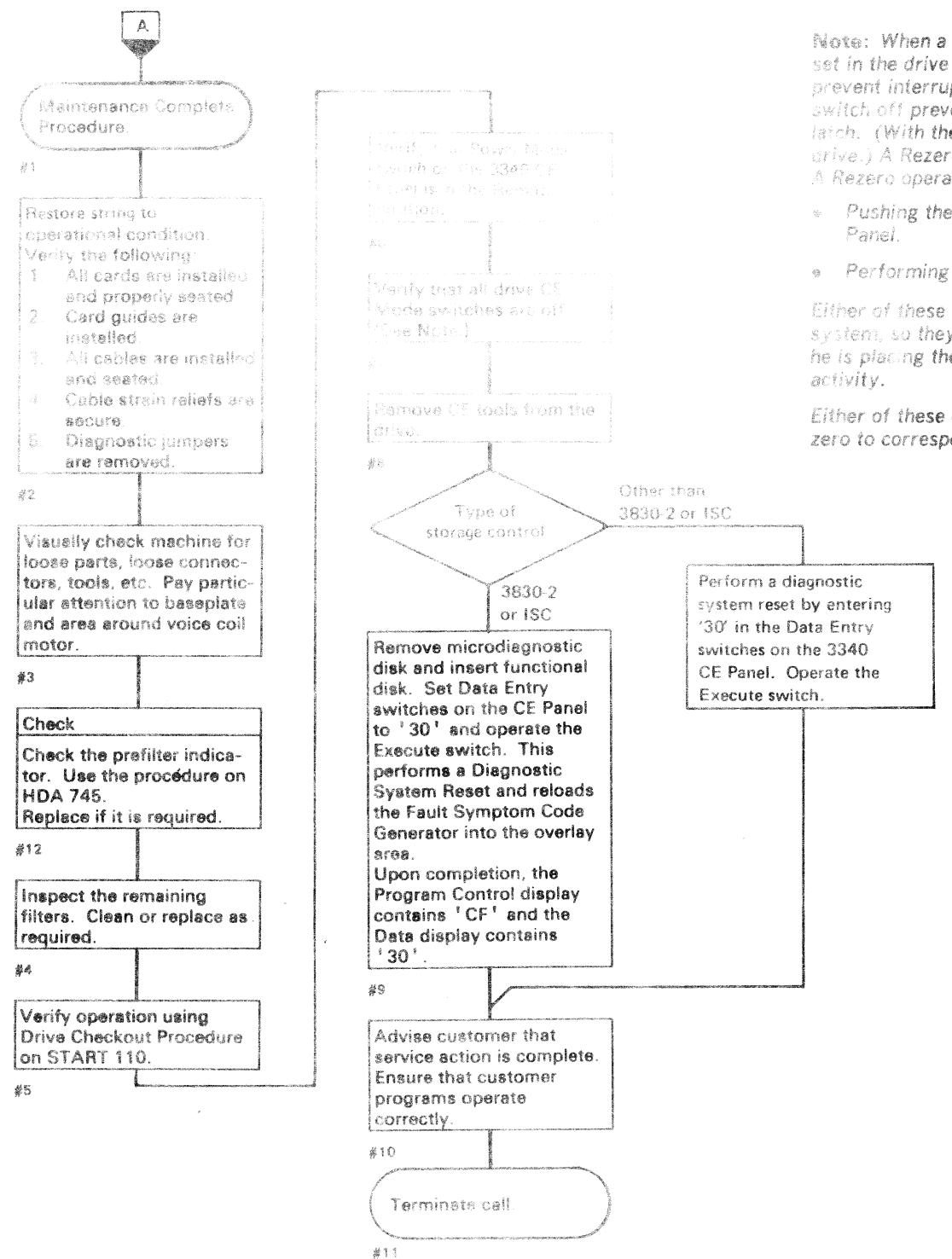

Maintenance Procedure Complete START 500

MAP LGND 4

Mechanical Adjustments

Air Switch HDA 735

Cover Latch HDA 770

Drive Motor Brake HDA 720

Mechanical Removals/Replacements

Air Switch HDA 735

Blower Motor HDA 730

Covers HDA 705

Drive Motor HDA 715

Drive Motor Brake HDA 720

HDA HD .710

HDA Belt HDA 760

Prefilter HDA 745

Spindle Ground HDA 750

VCM HDA 725

Microdiagnostics

Control Options MICRO 11

Disk Loading MICRO 8

Error Code Dictionary MICRO 100

Flowcharts MICFL 1

Linked Series MICRO 1

Loading Procedures MICRO 10

Operating Instructions MICRO 10

Rate Selector MICRO 8

Routine Running Instructions MICRO 1

Monitor Check SENSE 108

Movable Heads OPER 30

## N

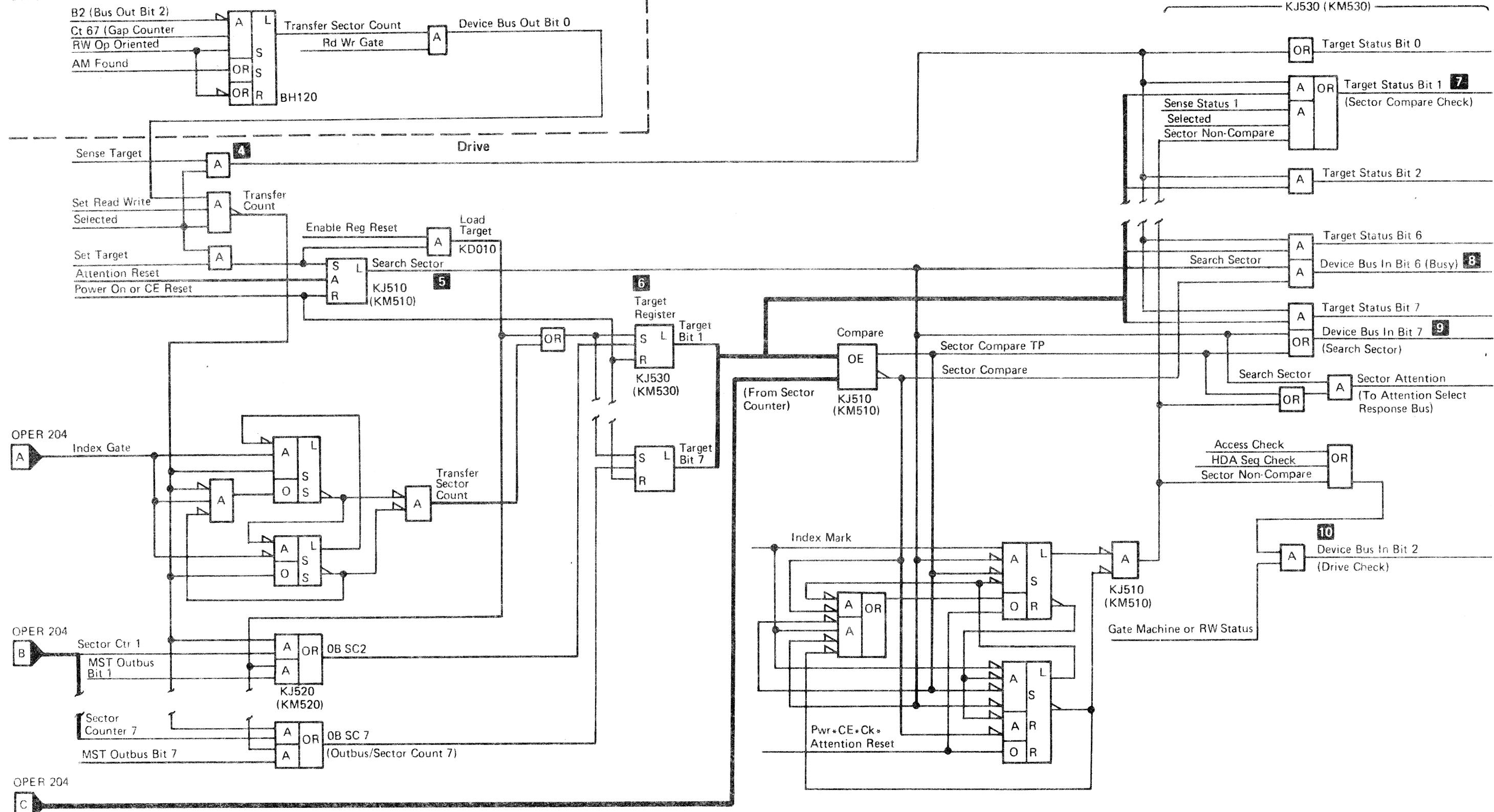

No Record Found OPER 208

|             |          |           |            |          |           |  |

|-------------|----------|-----------|------------|----------|-----------|--|

| KC0001      | 2359293  | 441235    | 441236     | 441238   | 441241    |  |

| Seq. 1 of 2 | Part No. | 28 May 76 | 30 Sept 76 | 3 Oct 77 | 29 Aug 80 |  |

**O**

Odd Index OPER 31

OLT (See 3340 MLM)

Operations, Introduction to OPER 3

Operator Panel LOC 16, PANEL 10

Organization of Information START 5

Orientation OPER 225, OPER 230

Overrun SENSE 105

**P**

Panel

Operator PANEL 10

Sequence LOC 14

Permanent Error SENSE 105

Philosophy of Maintenance START 50

PLO Cable OPER 92

Power

Fix Verification, Drive PWR 290

Sequence PWR 206

Theory PWR 206

Voltage Checks PWR 290

Power Amplifier OPER 116

Prefilter HDA 745

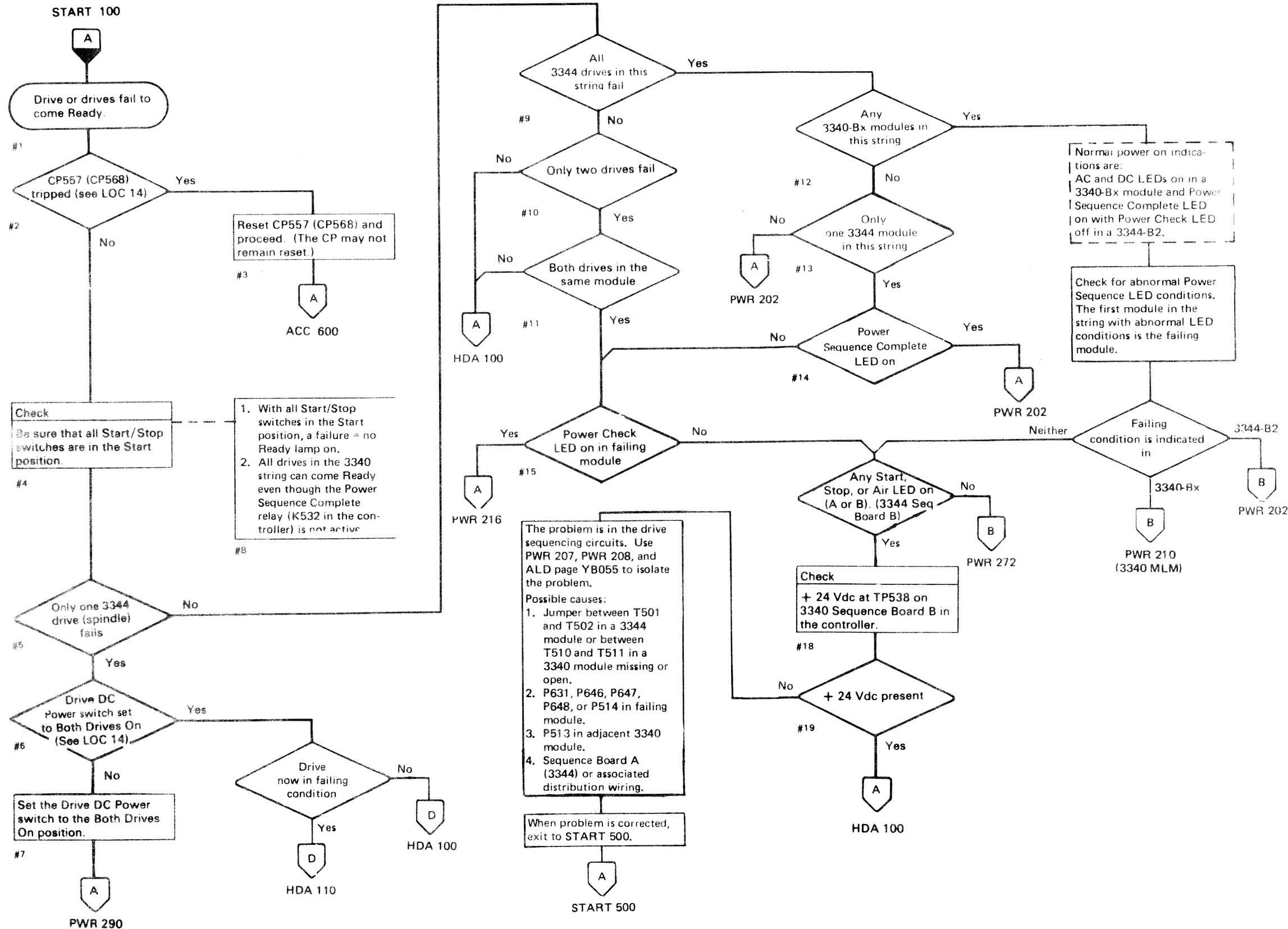

Problem Analysis START 100

**R**

RAS TP, Tag '0B' OPER 103

Read Data Cable Diagram R/W 370

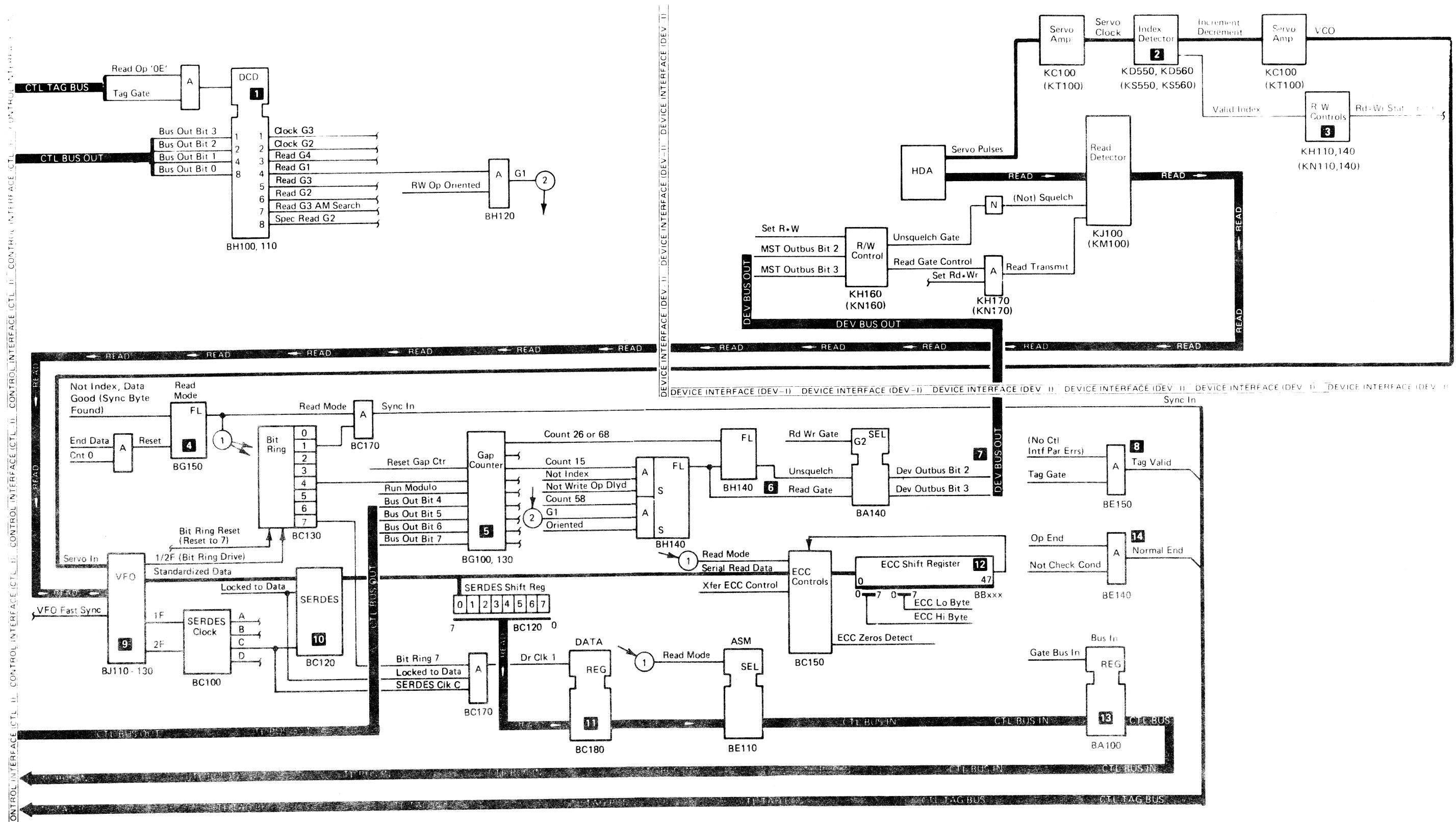

Read Data Path R/W 326

Read Detector OPER 231

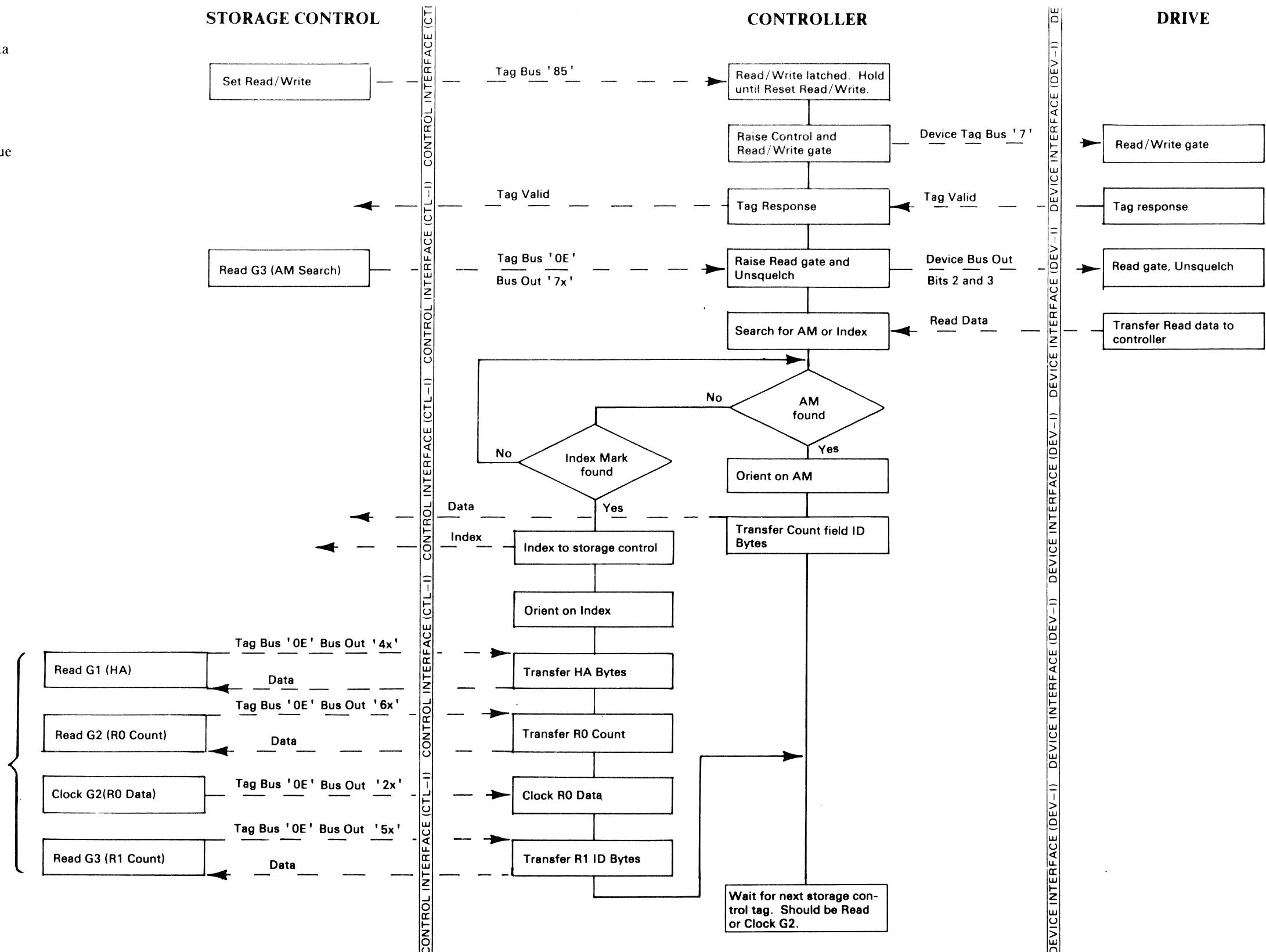

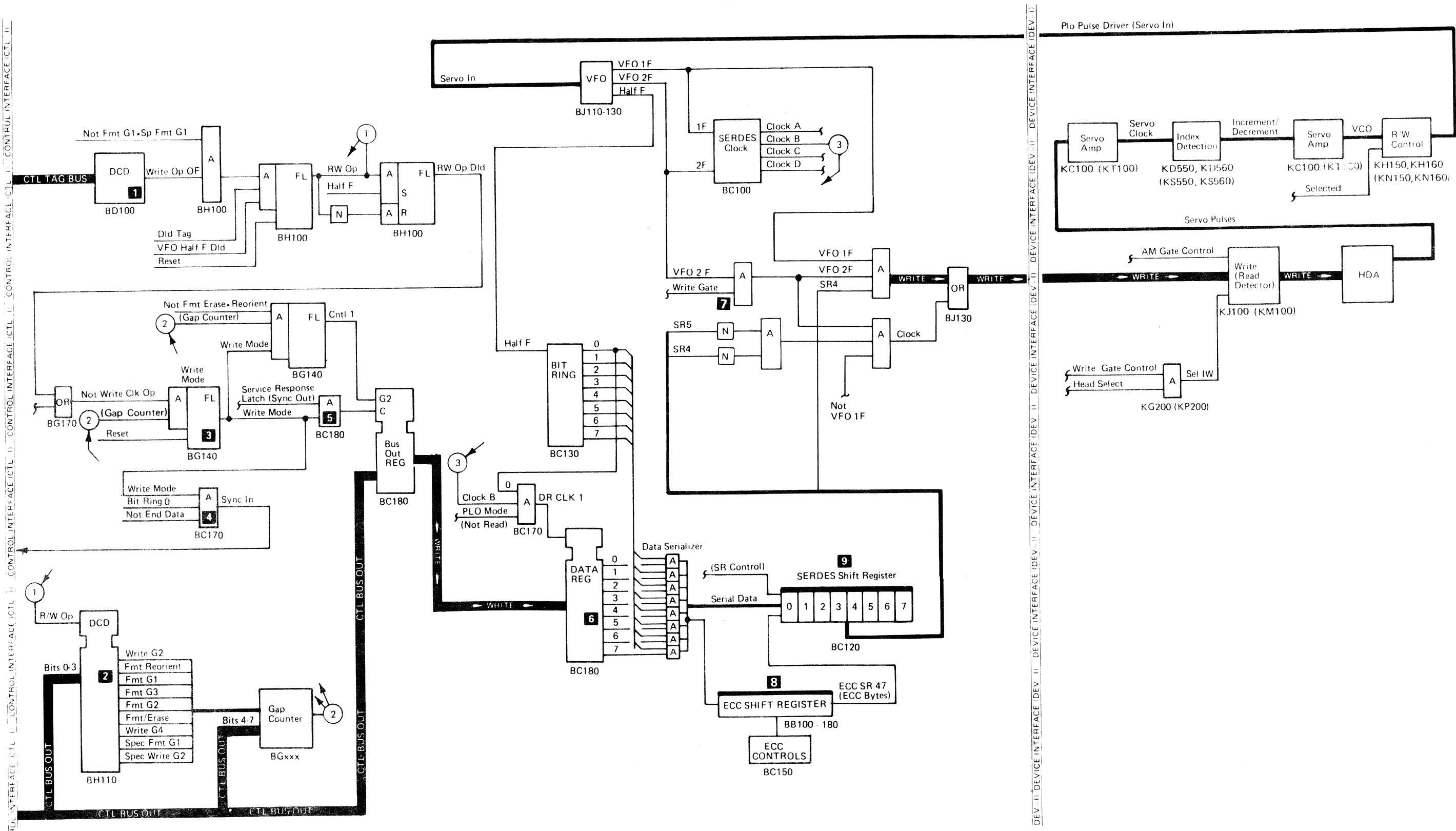

Read Operations OPER 230

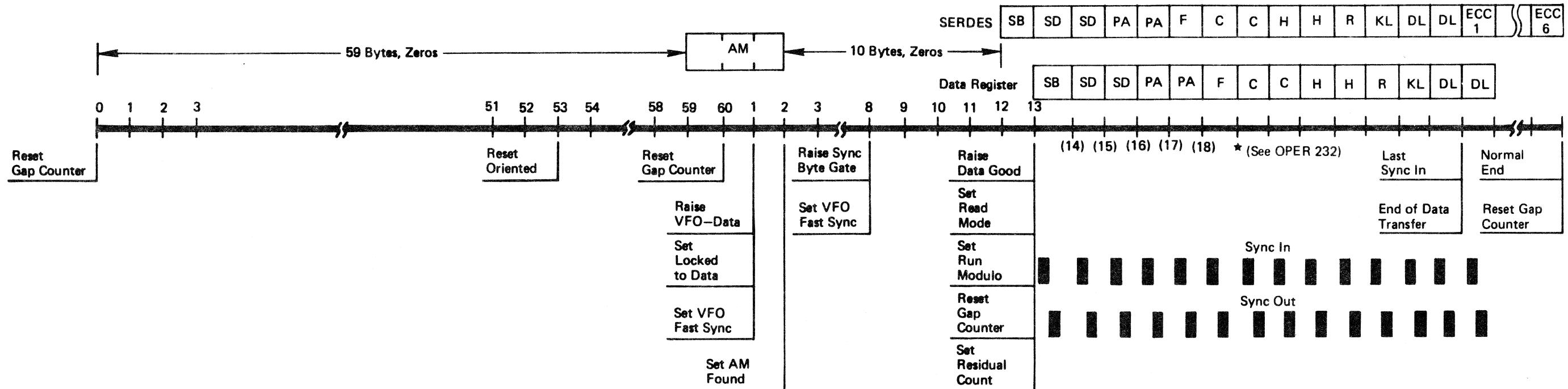

Read Timing OPER 232

Read/Write Control OPER 210

Read/Write Operation

R/W Control (Set-Reset) OPER 210

Read OPER 230

Write OPER 225

Rectifiers LOC 14

Recycle OPER 90

Regulators LOC 14

Relays LOC 1

Resistors LOC 14

Rezero Operation OPER 129, OPER 130

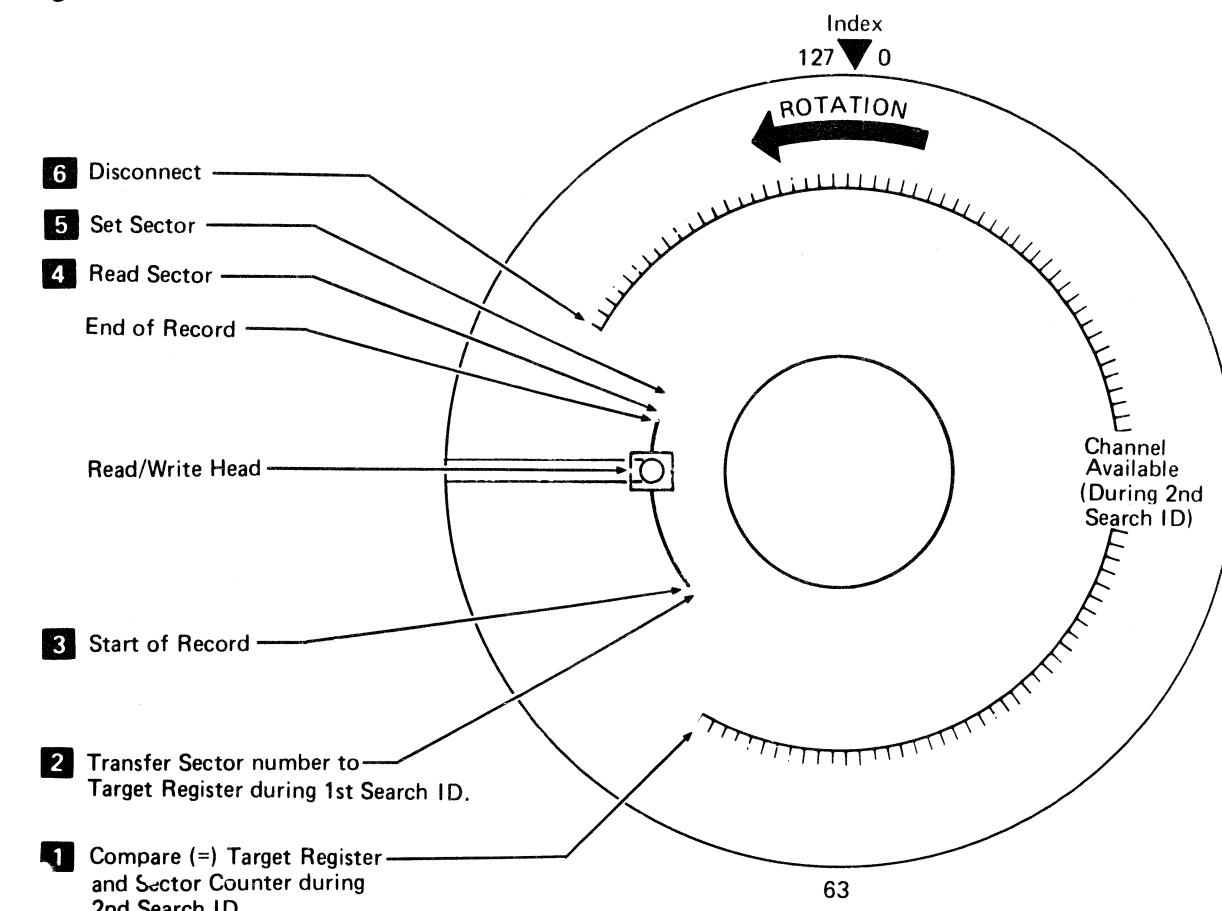

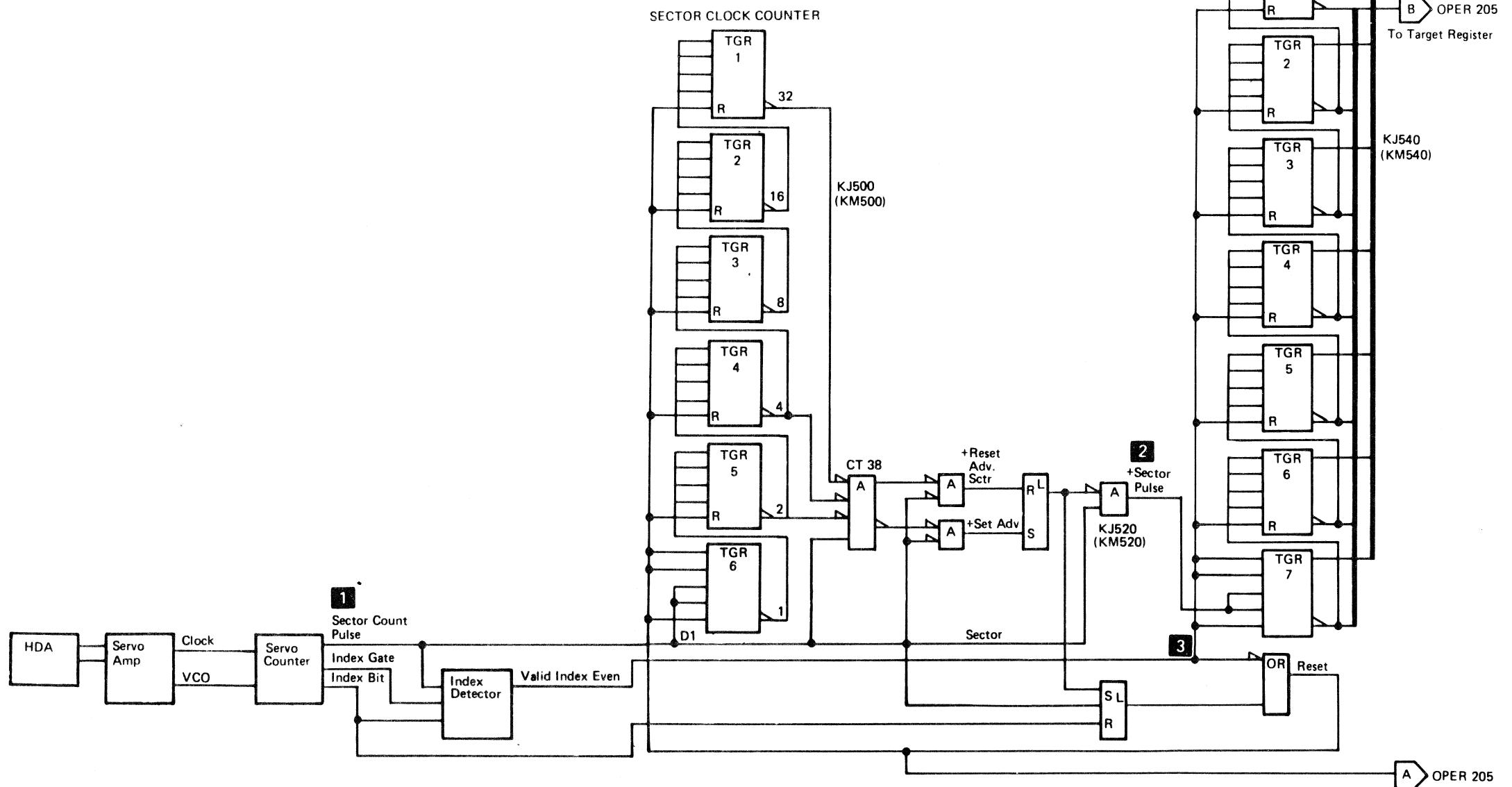

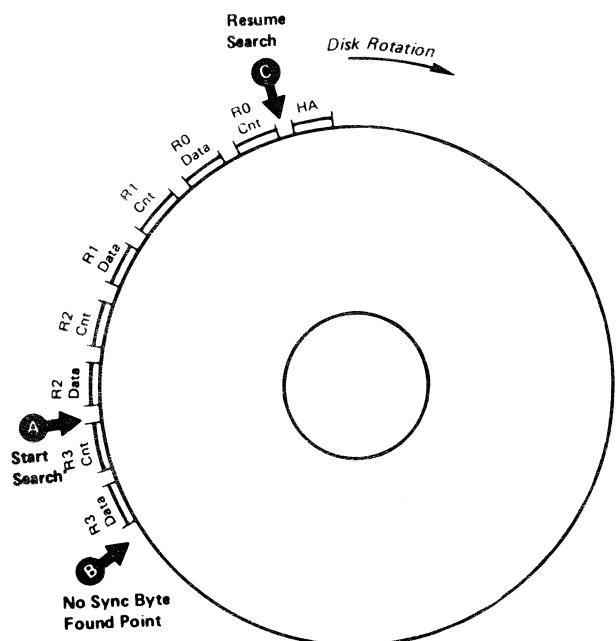

Rotational Position Sensing OPER 203

RPS (See Rotational Position Sensing)

**S**

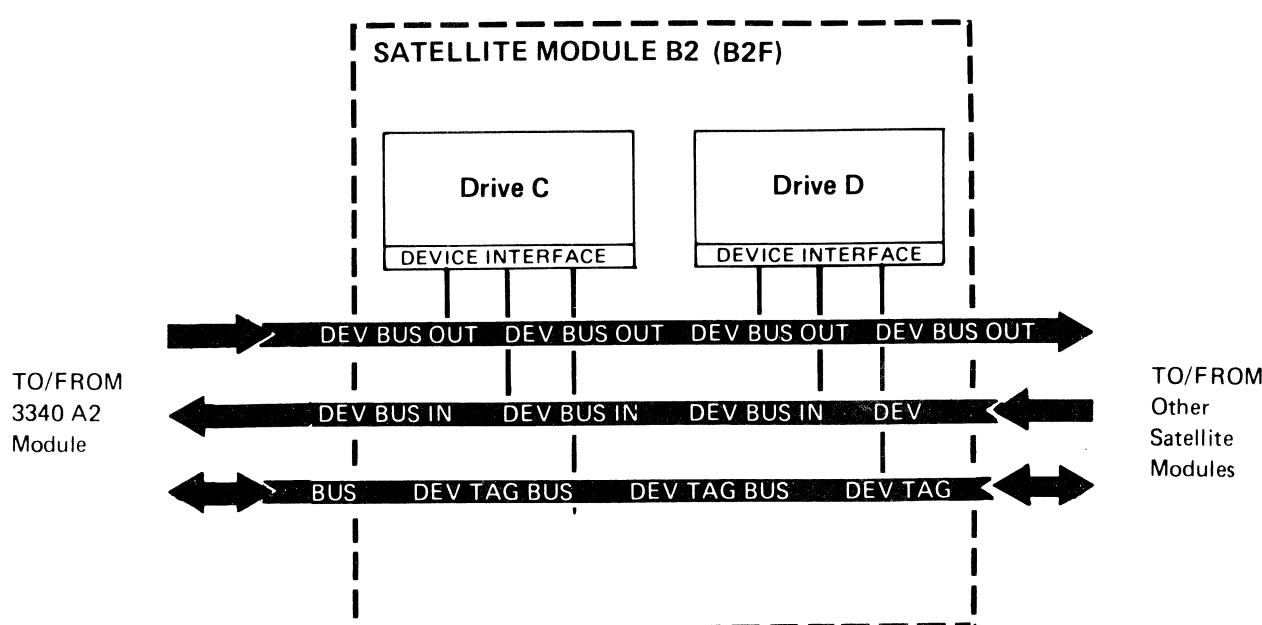

Satellite Module B2(B2F)

Description OPER 3

Installation INST 2

Locations LOC 12

Search Operation OPER 200

Search Sector Operation OPER 204

Sector Clock Counter OPER 204

Sector Counter OPER 203

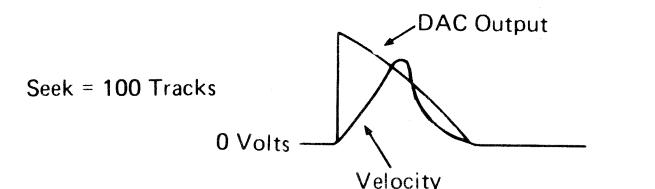

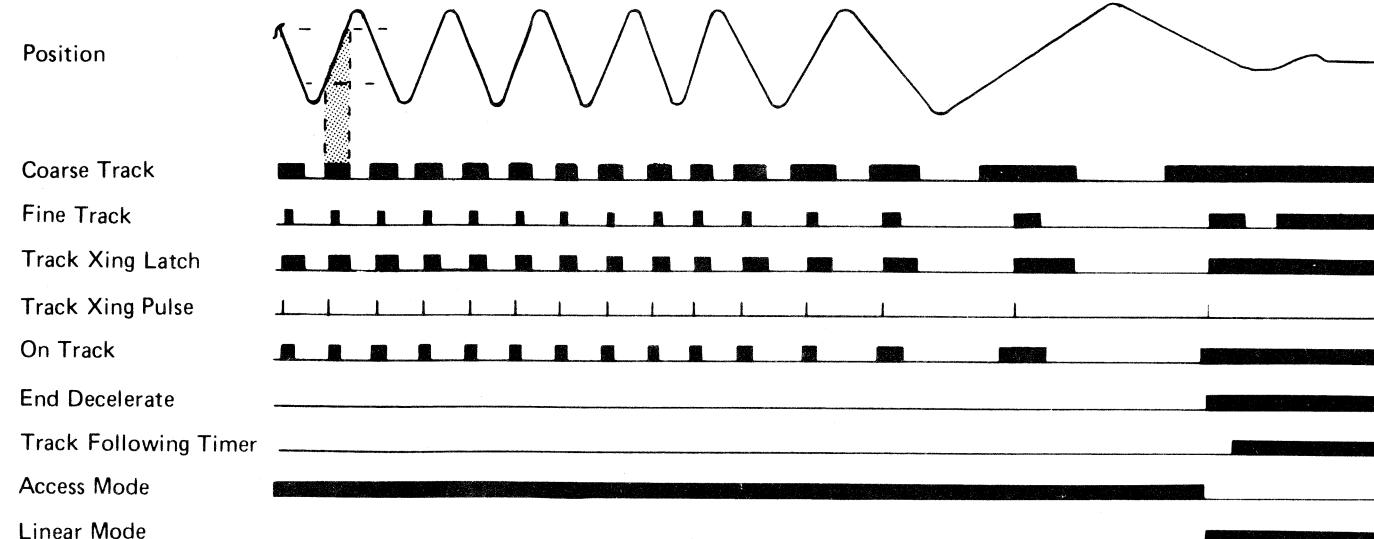

Seek Operation OPER 139, OPER 140, OPER 141, OPER 142

Select Operation

Description OPER 110

Timing OPER 95

**Sense Bytes**

Sense Data Analysis START 101

Sense Data Description SENSE 1

Sense Data Summary SENSE 100

Sequence Charts LGND 10

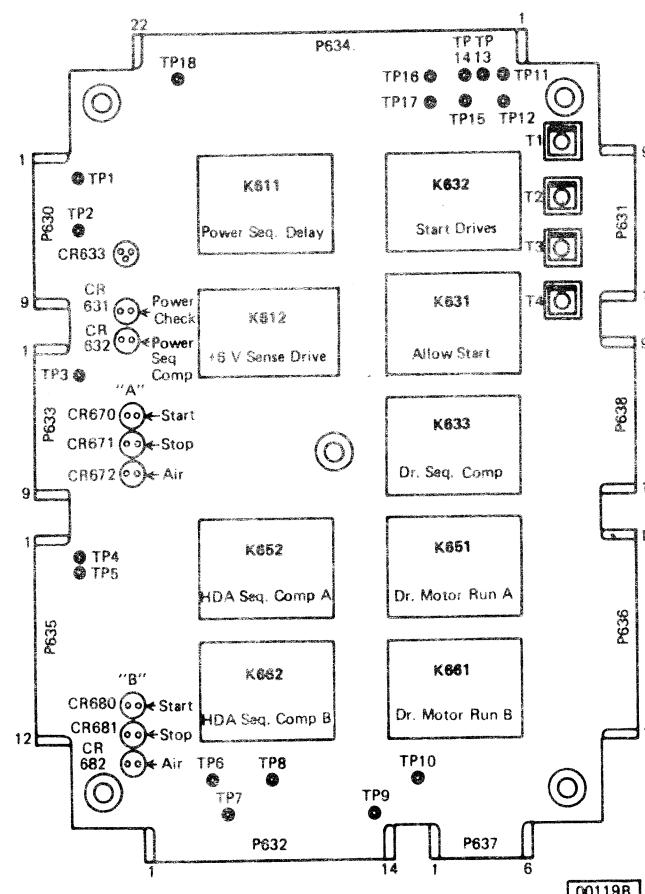

Sequence Panel LOC 14

SERDES OPER 226

Servo (See Access Operation)

Servo Checkout

Dynamic ACC 630

Static ACC 600

Servo Signal ACC 601, OPER 124

Servo Surface OPER 30

Shift Register (See SERDES)

Skip Defect OPER 36

Skip Displacement OPER 36

Spindle Ground HDA 750

Starting Point START 100

States

Access ACC 231, OPER 119

HDA HDA 500, HDA 504

Static Servo Checkout ACC 600

Statistical Data MSG 20

Status Bus DEV-I 184

Surface Defect Skipping OPER 36

Switches

Air LOC 1

Air Switch Removal HDA 735

Attention PANEL 10

CE Mode LOC 16, PANEL 10

DC Power LOC 14

R/W or Read LOC 16, PANEL 10

Service Bypass LOC 1, PANEL 10

Start/Stop LOC 16, PANEL 10

Symbols

Flowchart LGND 4

Sync (RAS TP, Tag '0B' OPER 103

**V**

Valid Index OPER 126

Valid Index 1 (See Even Index)

Valid Index 2 (See Even Index)

VCO (See Voltage Controlled Oscillator)

Velocity Gain Calibration ACC 800

Voice Coil

Removal and Replacement HDA 708

Voice Coil Motor (VCM)

Diagram LGND 8, LGND 10

Removal HDA 725

Terminals ACC 600, LOC 16

Voltage Controlled Oscillator (VCO) OPER 226, OPER 231

Volume ID MSG 10

Volumes, Logical OPER 32

**W**

Write Inhibited SENSE 105

Write Operations OPER 225

**T**

Tag Summary Chart OPER 98

Tag Summary Description OPER 102

Tag Valid OPER 90

Target Register OPER 203

TB (See Terminal Blocks)

Terminal Blocks LOC 1

Tools and Test Equipment INST 2

Track Following OPER 123

Track Format OPER 33

Transformers LOC 1

|             |          |  |           |            |          |           |  |

|-------------|----------|--|-----------|------------|----------|-----------|--|

| KC0001      | 2359293  |  | 441235    | 441236     | 441238   | 441241    |  |

| Seq. 2 of 2 | Part No. |  | 28 May 76 | 30 Sept 76 | 3 Oct 77 | 29 Aug 80 |  |

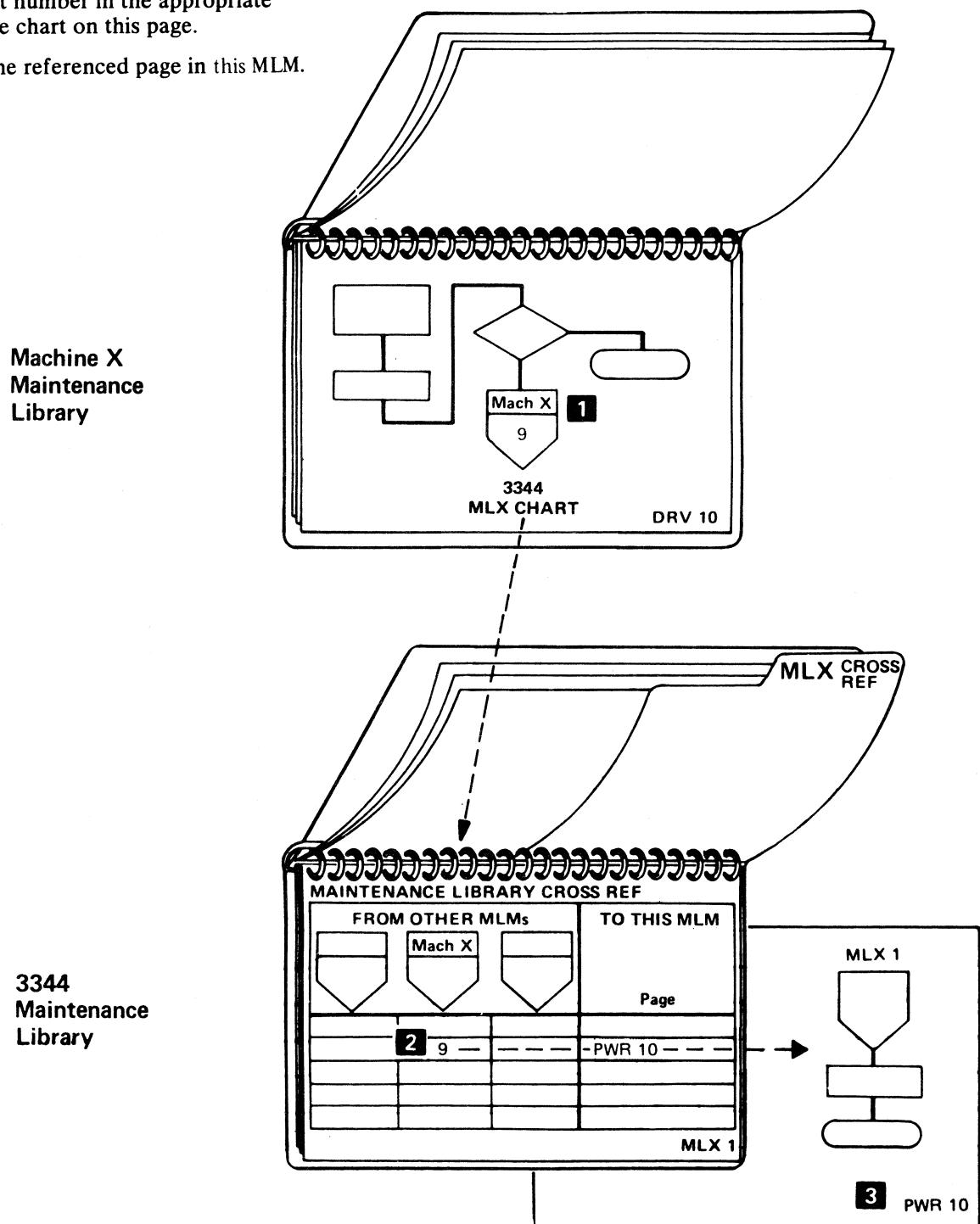

## MAINTENANCE LIBRARY CROSS REFERENCE

## MAINTENANCE LIBRARY CROSS REFERENCE

MLX 1

**USE THIS PAGE WHEN ENTERING THIS MLM

FROM OTHER MAINTENANCE LIBRARY

MANUALS.**

- 1 Note exit number on page of MLM you are leaving.

- 2 Find that exit number in the appropriate column of the chart on this page.

- 3 Proceed to the referenced page in this MLM.

**Note:** Use this page when tracing back from other maintenance library manuals to locate a line that exited from this MLM.

| Exit | Page(s)              |

|------|----------------------|

| 1    | MICFL 860, MICRO 84  |

| 2    | SENSE 100, SENSE 106 |

| 3    |                      |

| 4    |                      |

| 5    | START 101            |

| 6    |                      |

| 7    | SENSE 103, START 101 |

| 8    |                      |

| 9    | SENSE 100            |

| 10   | MICRO 11             |

| 11   | MICRO 8              |

| 12   |                      |

| 13   |                      |

| 14   |                      |

| 15   |                      |

| 16   |                      |

| 17   |                      |

| 18   |                      |

| 19   |                      |

| 20   |                      |

| 21   |                      |

| 22   |                      |

| 23   |                      |

| 24   |                      |

| 25   |                      |

- Exit 1: To Storage Control for instructions on running 3880 wrap test.

- Exit 2: To Storage Control for definition of sense bytes 5 and 6 in Format 6 when attached to a 3880.

- Exit 5: To Storage Control for definition of sense byte Formats other than 1, 4, 5 and 6 (Formats for system or attachment detected problems).

- Exit 7: To Storage Control for definition of sense bytes 18 through 23 of Format 6 (Not device dependent information).

- Exit 9: To Storage Control for definition of sense byte Formats which are not defined by the 3344 (Not Formats 1, 4, 5 or 6).

- Exit 10: To Storage Control for Fxxx microdiagnostic error displays (usually reader errors detected in storage control).

- Exit 11: To Storage Control for instructions on how to load device microdiagnostics.

## LGND CONTENTS

LGND CONTENTS **LGND 1**

### MAINTENANCE ANALYSIS PROCEDURES

Flowchart Symbols . . . . . LGND 4

Flowchart Example . . . . . LGND 6

Diagram Symbols . . . . . LGND 8, 10

### AUTOMATED LOGIC

DIAGRAMS . . . . . LGND 12 - 14

### ABBREVIATIONS AND

DEFINITIONS . . . . . LGND 16, 18

3344

|             |          |

|-------------|----------|

| KG0001      | 2359297  |

| Seq. 1 of 2 | Part No. |

|           |  |  |  |  |

|-----------|--|--|--|--|

| 441235    |  |  |  |  |

| 28 May 76 |  |  |  |  |

© Copyright IBM Corporation 1976

LGND CONTENTS **LGND 1**

## FLOWCHART SYMBOLS

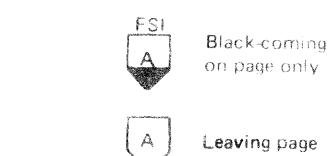

## External Page Connector

Connection between diagrams on separate pages. Letter keys are used to identify corresponding points. Below the symbol is the page number of the connecting point.

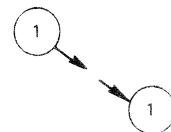

## Internal Page Connector

Connection between several parts of the same diagram. Line-of-sight arrows assist in locating other connector(s).

## Terminal Block

Beginning or end of flow path.

## Decision Block

Branch to alternate paths.

## Annotation Block (Supplementary)

Descriptive comment or explanatory note.

## Annotation Block (In Line)

Descriptive comment or explanatory note.

## General Purpose Action Block

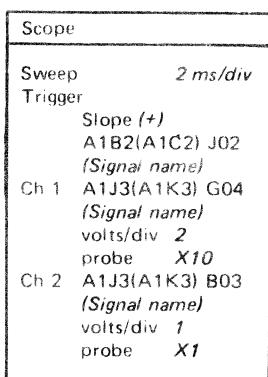

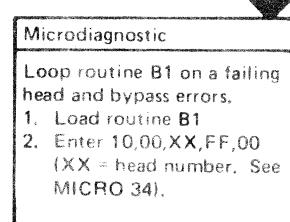

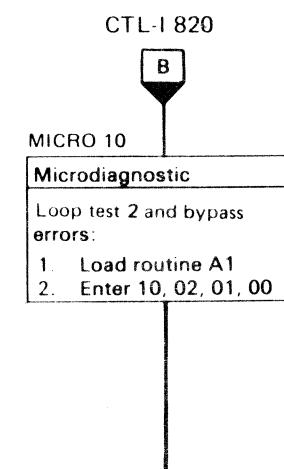

## Scope Setup Block

Shows how to set up to scope. Keys outside the block reference the test points being scoped and the MLM page showing the diagram of those test points.

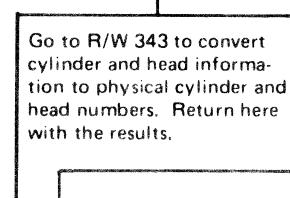

R/W 343 and Return

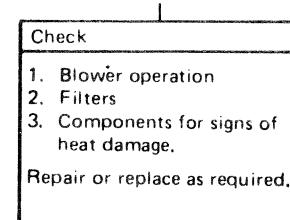

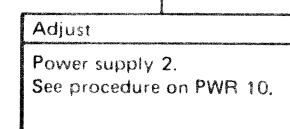

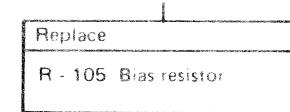

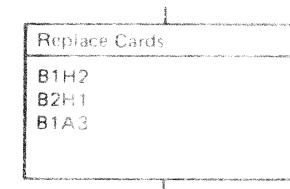

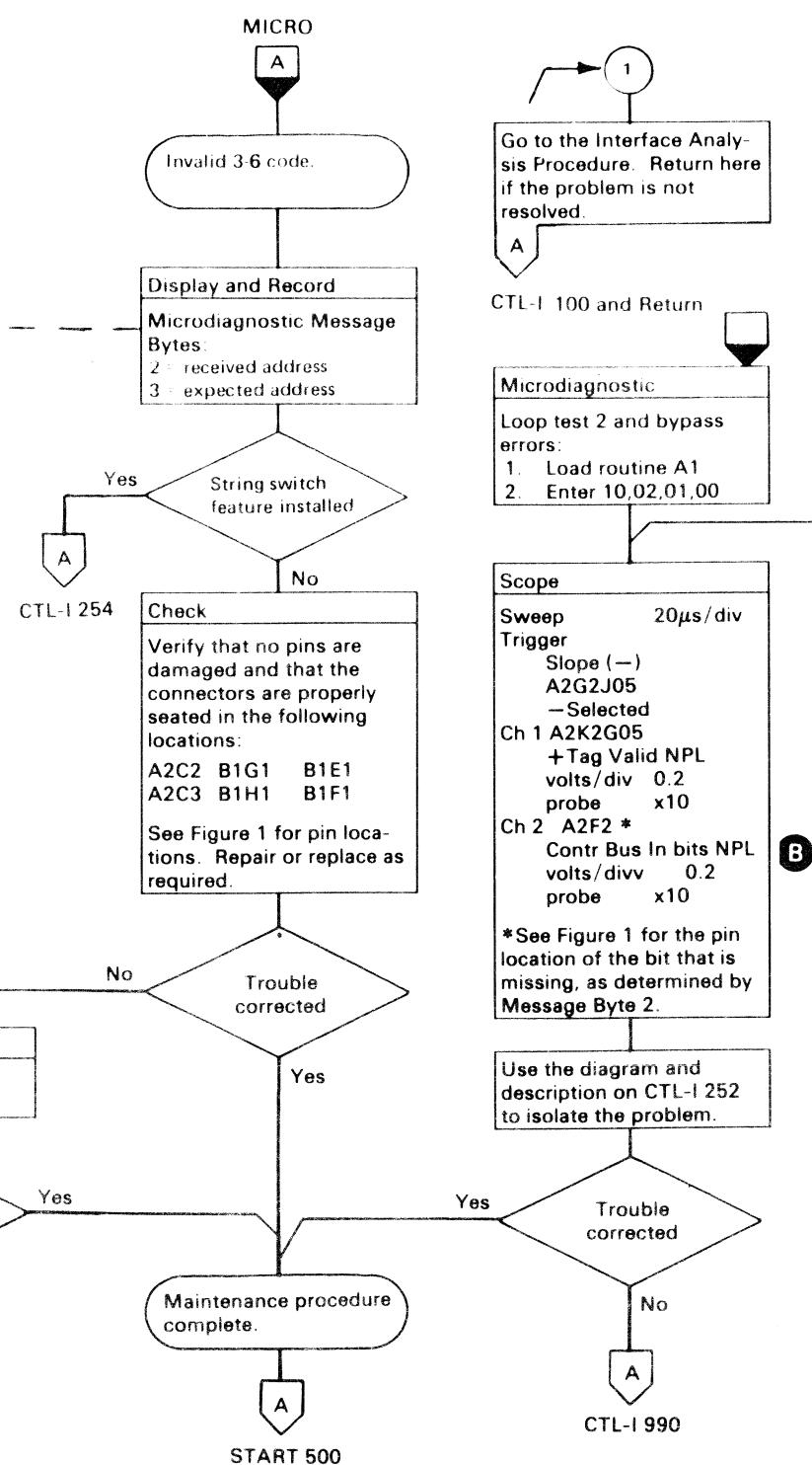

## Specific Action Blocks

Denotes special CE actions: Replacing Cards, Checking, Running Microdiagnostics, Adjusting, or Installing.

## Return Block

This special block is used as a reminder that, after branching to another page, returning to this flowchart is necessary to complete the analysis.

## MAINTENANCE ANALYSIS PROCEDURE (MAP) LEGEND

MAINTENANCE ANALYSIS PROCEDURE (MAP) LEGEND

LGND 6

### FLOWCHART EXAMPLE

| Controller Address | Message bits | Byte 3 | 0 1 2 3 | 4 5 6 7 | Hex Value |

|--------------------|--------------|--------|---------|---------|-----------|

| 0                  | 0 0 0        | -      | 1 1 1   | -       | 07        |

| 1                  | 0 0 1        | -      | 1 1 0   | -       | 26        |

| 2                  | 0 1 0        | -      | 1 0 1   | -       | 45        |

| 3                  | 0 1 1        | -      | 1 0 0   | -       | 64        |

The controller address is determined by jumpers on the A2G2 card. See INST 6 for jumper locations.

Figure 1. Pin Locations

| Line Name           | Card A2G2 Pins <b>A</b> | Card A2F2 Pins <b>B</b> | Conn A2C3 Pins <b>C</b> | Conn B1H1 Pins <b>D</b> | Conn B1F1 Pins <b>E</b> |

|---------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| +Contr Bus In Bit 0 | S02                     | D06                     | D05                     | J04                     | J04                     |

| +Contr Bus In Bit 1 | U05                     | B03                     | B05                     | G05                     | G05                     |

| +Contr Bus In Bit 2 | U02                     | D10                     | D06                     | J06                     | J06                     |

| +Contr Bus In Bit 3 | M12                     | D09                     | B09                     | G08                     | G08                     |

| +Contr Bus In Bit 4 | M13                     | J02                     | D10                     | J09                     | J09                     |

| +Contr Bus In Bit 5 | P13                     | J07                     | B10                     | G10                     | G10                     |

| +Contr Bus In Bit 6 | S09                     | J11                     | D11                     | J11                     | J11                     |

| +Contr Bus In Bit 7 | U13                     | J03                     | B12                     | G12                     | G12                     |

| +Contr Bus In Bit P | G08                     | J12                     | B02                     | G03                     | G03                     |

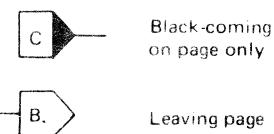

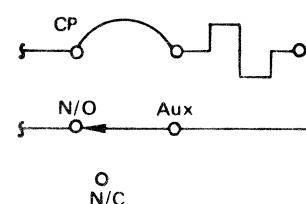

## DIAGRAM SYMBOLS

CHANNEL INTERFACE (CHL-I)CONTROL INTERFACE (CTL-I)DEVICE INTERFACE (DEV-I)DEV BUS IN   DEV BUS INCTL BUS OUT   CTL BUS OUTREAD  $\leftrightarrow$  WRITE  $\leftrightarrow$  READ**External Page Connectors**

Connection between diagrams on separate pages. Letter keys are used to identify corresponding points.

**Solenoid**

Identified by name, for example, Brake Solenoid.

**Relay or Contactor**

Type indicated by letter code.

P = Pick

PL = Pick Lower

PU = Pick Upper

H = Hold

LP = Latch Pick

LU = Latch Upper

**Relay Contacts**

Shown in the de-energized position.

N/C = Normally Closed (break).

N/O = Normally Open (make).

**Connector (multiple line)****Internal Page Connectors**

Connection between several parts of the same diagram. Line-of-sight arrows assist in locating other connector(s).

**Test Points**

Used on diagrams to indicate key test points or key circuit parts.

**LED (Light Emitting Diode)****Indicator (lamp)****Interface Between Two Functional Units**

(For examples of their use, see OPER 3.)

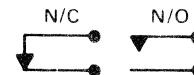

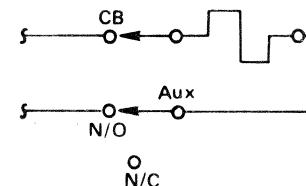

**Channel Buses and Read/Write Bus****Circuit Breaker (CB) with Aux Points**

Electrically or manually tripped, handle generally higher current, and may have auxiliary points (aux). N/O points make contact when associate CB is positioned to conduct current.

**Circuit Protector (CP) with Aux Points**

Normally tripped electrically, handle lower current, and may have auxiliary points (aux). N/O points make contact when associate CP is positioned to conduct current.

# MAINTENANCE ANALYSIS PROCEDURE (MAP) LEGEND

MAINTENANCE ANALYSIS PROCEDURE (MAP) LEGEND

LGND 10

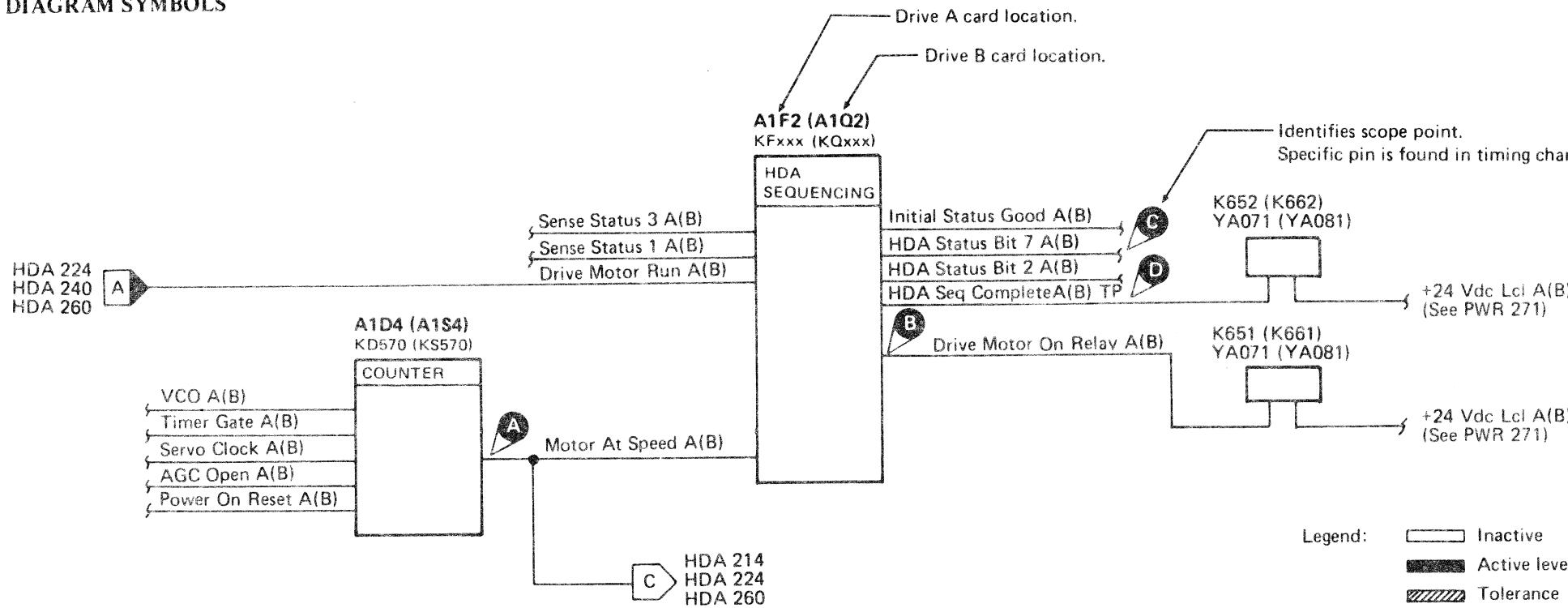

## DIAGRAM SYMBOLS

| Chart Line No. | Line Name                  | ALD           | Test Point      |             |

|----------------|----------------------------|---------------|-----------------|-------------|

| 1              | +VCO A(B)                  | KD570 (KS570) | A1D4 (A1S4) D13 |             |

| 2              | +AGC Open A(B)             | KD570 (KS570) | A1D4 (A1S4) B11 |             |

| 3              | +Timer Gate A(B)           | KD570 (KS570) | A1D4 (A1S4) J13 |             |

| 4              | +Servo Clock A(B)          | KD570 (KS570) | A1D4 (A1S4) G10 | Sync Pulses |

| 5              | -Drive Motor On Relay A(B) | KF260 (KQ260) | A1F2 (A1Q2) U13 | B           |

| 6              | +Motor At Speed A(B)       | KD570 (KS570) | A1D4 (A1S4) D07 | A           |

| 7              | +HDA Status Bit 7 A(B)     | KF240 (KQ240) | A1F2 (A1Q2) J11 | C           |

| 8              | -Sense Status 3 A(B)       | KF130 (KQ130) | A1F2 (A1Q2) B04 |             |

| 9              | +HDA Status Bit 2 A(B)     | KF230 (KQ230) | A1F2 (A1Q2) B02 |             |

| 10             | -Sense Status 1 A(B)       | KF130 (KQ130) | A1F2 (A1Q2) D04 |             |

| 11             | -HDA Seq Complete A(B) TP  | KF260 (KQ260) | A1F2 (A1Q2) S02 | D           |

6

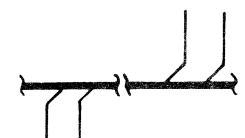

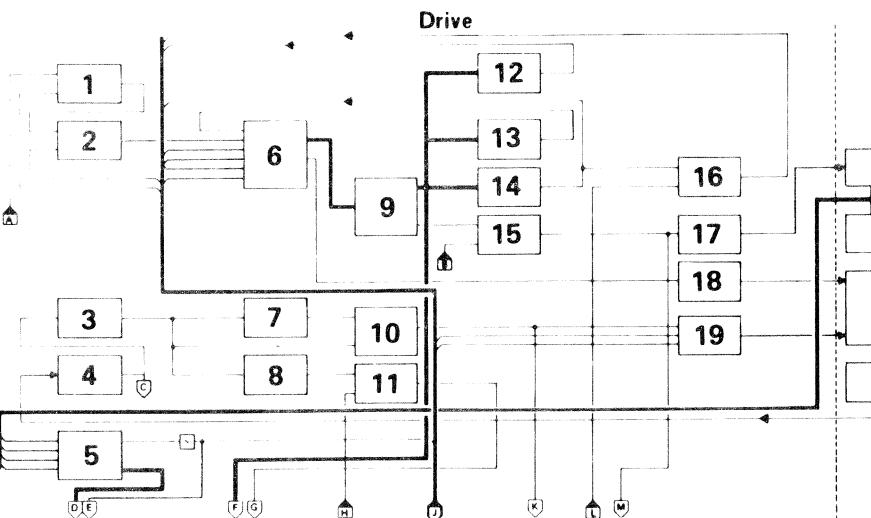

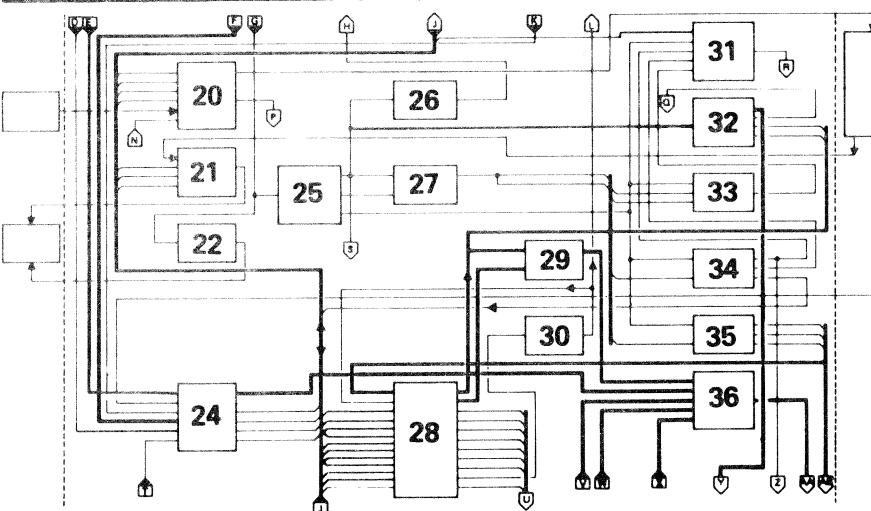

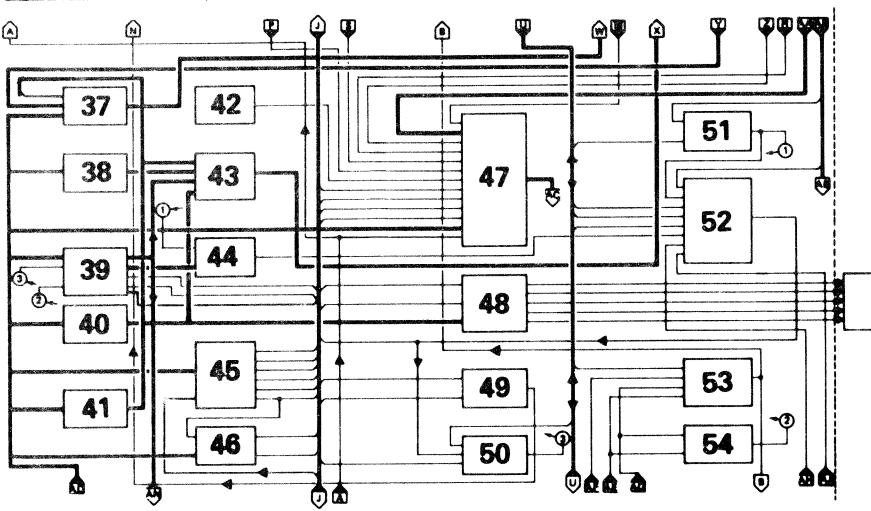

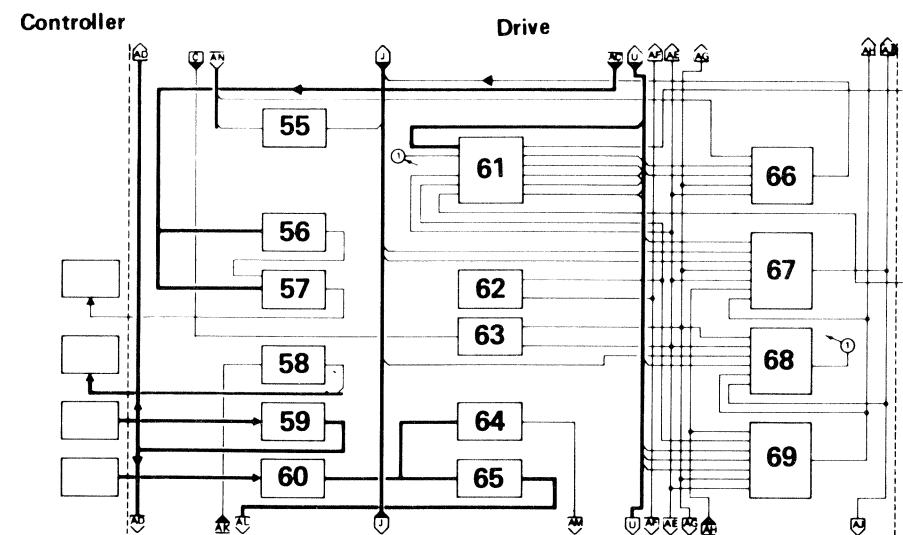

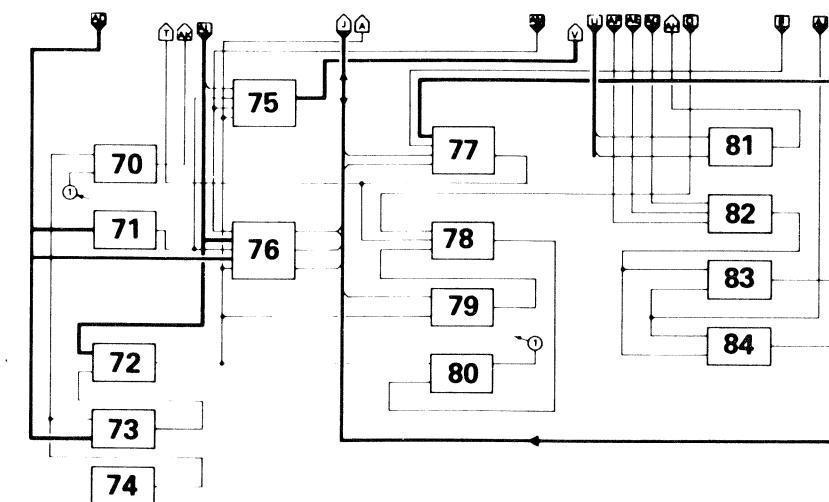

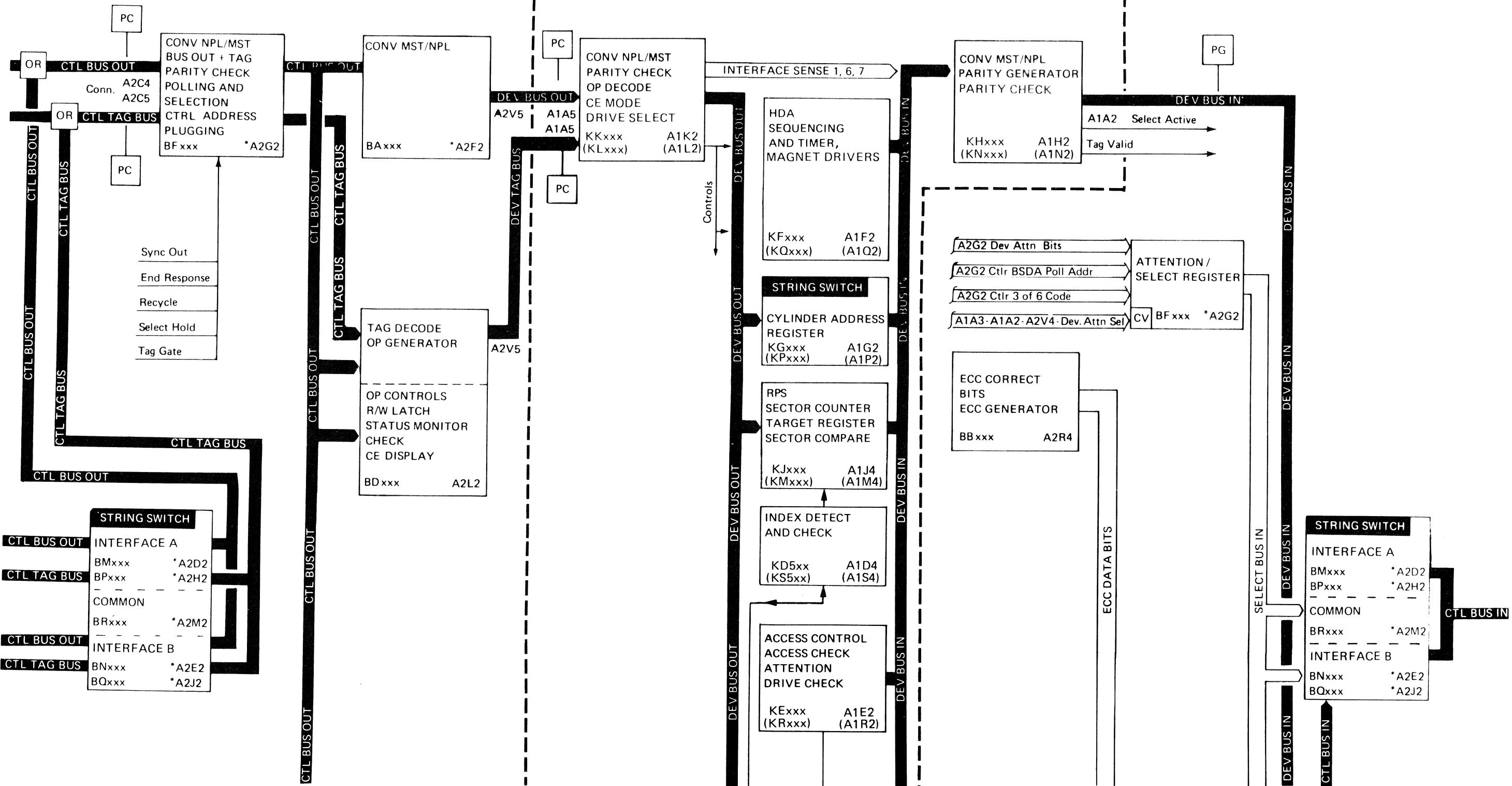

## Block Diagrams

Show the cards that relate to a specific failure in Drive A. The information in the parentheses applies to Drive B. This diagram also shows the ALD references, line names, and test points for each card.

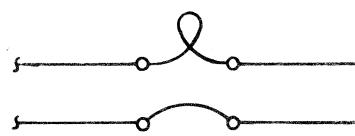

## Sequence Charts

The heavy black lines show the active state for the test point shown.

For example: HDA Seq Complete A(B) TP (chart line no. 11) goes minus when Motor At Speed A(B) is active (chart line no. 6).

LGND 10

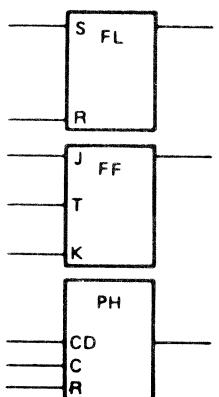

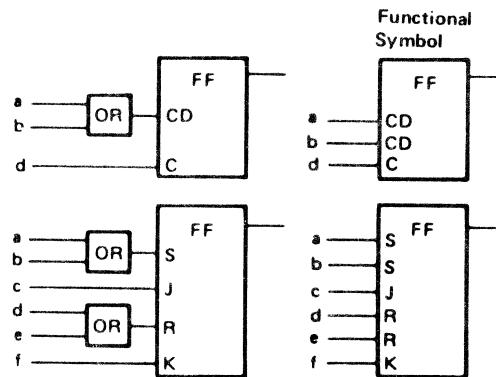

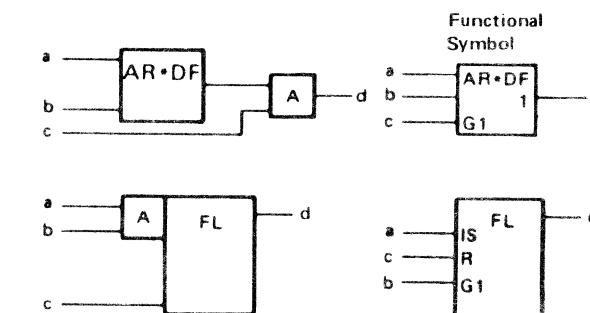

## STORAGE ELEMENT LINE DEFINITIONS

Inputs to blocks are identified by letters inside the block, adjacent to each input. Examples of line designations are shown above.

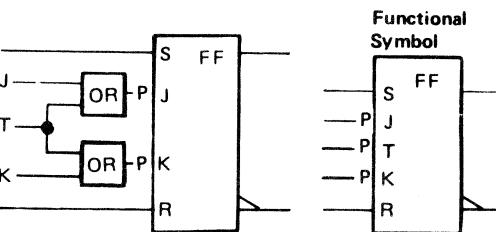

**AC Coupled FF:** The J, T, and K input sources provide an ac triggered flip flop. At least one of the inputs must have a positive transition to cause the FF output to change. However, input sources T and J must both be down simultaneously prior to the positive transition in order to set the FF. Input sources T and K must both be down simultaneously prior to the positive transition in order to Reset the FF. If J and K are both down, then the FF changes states with each positive shift of input source T; input source T may be a clock timing pulse. If J and K are both up, then no transition occurs with positive shift of input source T. If J is down and K is up, a positive shift of T or J sets the FF if it is not already set. Conversely, if J is up and K is down, then a positive shift of T or K resets the FF if it is not already reset.

**S Set:** When set is active, all outputs are at the polarity shown.

**R Reset:** When reset is active, all outputs are at a polarity opposite to that shown.

**C Control:** When active, the control input permits the output to change with changes to the data in input line. When inactive, the control line holds the output at whatever polarity it possessed at the moment the control line became active.

**CD Controlled Data:** When the associated control input is the polarity shown, a CD input at the polarity shown sets the storage element. Likewise, a CD input at its opposite polarity resets the storage element, when a control input is active. If multiple CD inputs to the storage element, any one active CD input can set the storage element.

**G Gate:** Represents the AND function without the use of the AND logic symbol. When multiple gating lines are required, gates are identified by the same numerals used to identify its related gated dependent line. A G1 gate controls an input or output line marked with a 1.

**G Gate (input):** When at the polarity shown, G Gate allows a dependent input of the polarity indicated to affect the storage element. In all other cases, it can be considered inactive.

**G Gate (output):** The dependent output is at the polarity shown when the associated gating line is at its indicated polarity. In all other conditions the output stands opposite to the polarity shown.

## STORAGE ELEMENTS

## Basic Storage Symbols

## Inherent-OR In The FF

## Single Function Application

## AC Coupled FF

## Dependent Notation

*Note: If the outputs can be determined for simultaneous set/reset, an S or R below an output indicates the FF condition, either set or reset. Multiple set (or reset) inputs are considered to be ORed.*

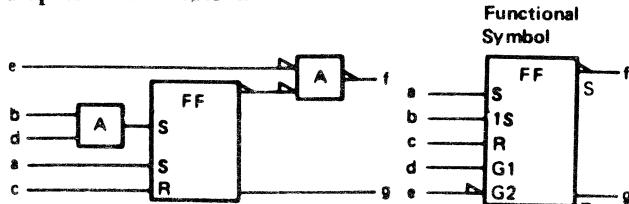

## Special Notations

An equal sign (=) followed by a number specifies the number of input lines of the polarity shown required to produce the indicated output.

A plus (+) or minus (-) under an output line indicates the extreme potential that may be forced by an external source.

A loading character (L or U) under the output line indicates that the external load cannot be isolated from the driving circuit without affecting the output of the driver.

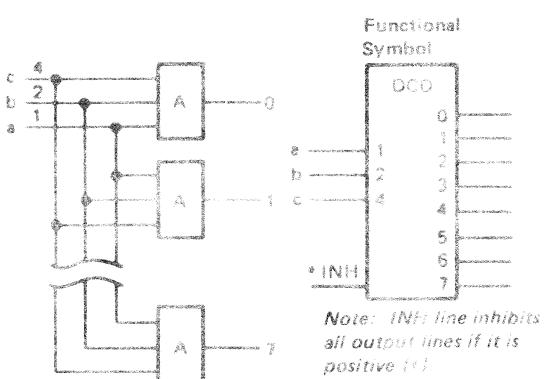

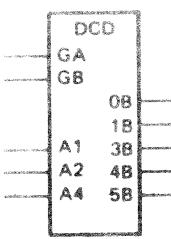

## DECODE

The decimal sum of the line values of those inputs that are at their active level equals the value of the active output line. If no input lines are active, the 0 output line is active. If all input lines are active, the 7 output line is active.

**Note:** The decimal sum value existing at the decoder inputs agrees with the decimal number shown at the output line labels. Only one output can be active at any given time.

| Output Value | Input Line Condition      |

|--------------|---------------------------|

| 0            | $\bar{a} \bar{b} \bar{c}$ |

| 1            | $\bar{a} \bar{b} c$       |

| 2            | $\bar{a} b \bar{c}$       |

| 3            | $\bar{a} b c$             |

| 4            | $a \bar{b} \bar{c}$       |

| 5            | $a \bar{b} c$             |

| 6            | $a b \bar{c}$             |

| 7            | $a b c$                   |

CFEALD

Multiple output lines can be associated with a given output (sum).

CFEALD

A decoder shown with gating lines.

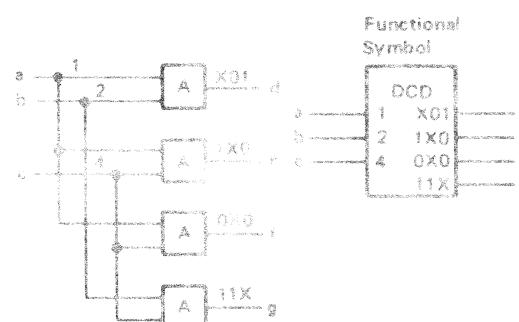

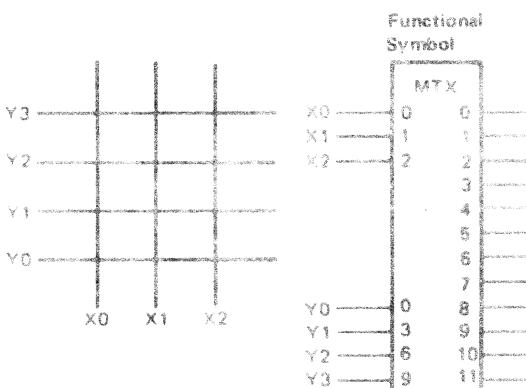

## MATRIX

| Active Input Lines |    |    |    |    |    | Active Output |

|--------------------|----|----|----|----|----|---------------|

| X0                 | X1 | X2 | Y0 | Y1 | Y2 | Y3            |

| X                  |    |    | X  |    |    | 0             |

|                    | X  |    | X  |    |    | 1             |

|                    |    | X  | X  |    |    | 2             |

| X                  |    |    |    | X  |    | 3             |

|                    | X  |    |    | X  |    | 4             |

|                    |    | X  |    | X  |    | 5             |

| X                  |    |    |    |    | X  | 6             |

|                    | X  |    |    |    | X  | 7             |

|                    |    | X  |    |    | X  | 8             |

| X                  |    |    |    |    | X  | 9             |

|                    | X  |    |    |    | X  | 10            |

|                    |    | X  |    |    | X  | 11            |

**Note:** The matrix (MTX) is a functional logic block with two or more groups of inputs. The decimal numbered output is active when it equals the decimal sum of one active line from each input group (shown in Chart). If any input group does not have an active input, then there is no active output from the matrix block.

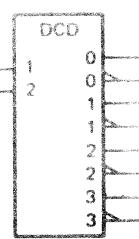

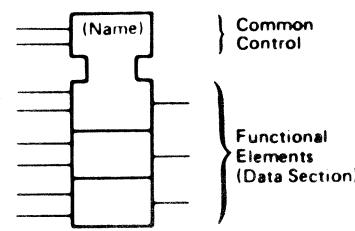

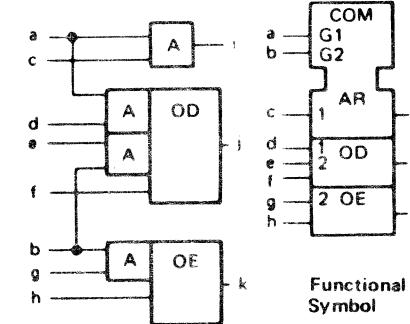

## ELEMENTS WITH COMMON INPUTS/OUTPUTS

## Element Description

**COMMON CONTROL SECTION:** Used only for dependency (gating) and/or common lines for the register. There are no outputs from the common control section.

**NAME:** May be any of the following: selector (SEL), register (REG), decoder (DCD), matrix (MTX), multiregister (MREG), and delay (DLY).

**DATA SECTION:** A group of vertically stacked function elements. The number of stacked elements varies with the number of inputs.

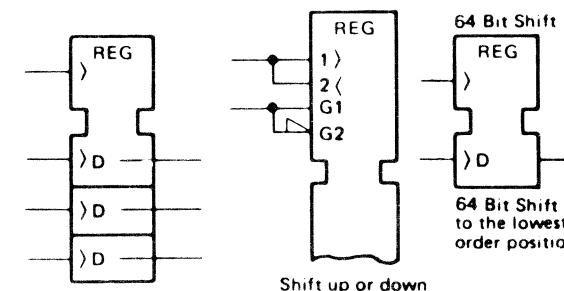

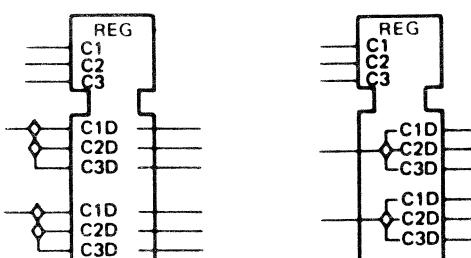

## Shift Register (REG)

**DEFINITION:** The control input causes the data in each bit position to shift one position, as indicated by one of the following designations:

Greater than (>): When this line becomes active, the data content shifts from the top (upper-most) bit position. Similarly, the contents of each bit position shifts down the symbol.

Less than (<): When the line becomes active, the data content shifts from the bottom to the next bit position above and similarly for each bit position in the shift register symbol.

*Note: A time difference in shifting is indicated by a trailing edge symbol (¬).*

## Common Function (COM)

**DEFINITION:** Common Function block may be associated with any group of basic logic elements functionally related by their dependent gating. Each functional element contains the proper letter(s) that makes it an approved logic symbol. The common section may contain the letters COM at the very top line.

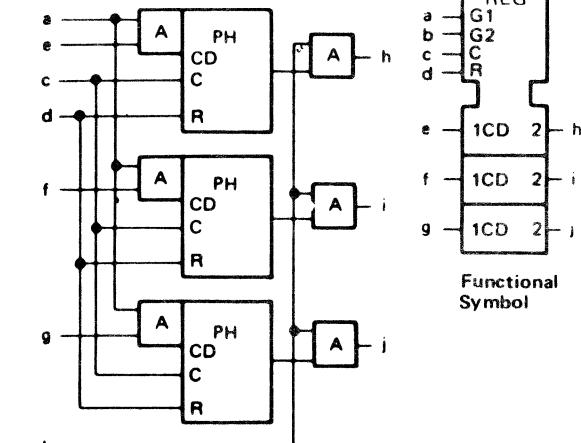

## Multicontrol Register (REG)

The multiple control inputs are designated by sequential numbers shown entering the common section; for example, C1, C2.

The control data enters the data section of the symbol and is normally diagrammed as multiple outputs.

The "C" designator must be a suffix to differentiate it from a gate.

**Example:**

C1D = Storage Data controlled by C1.

*Note: The "◊" symbol represents the OR function connection in the data section.*

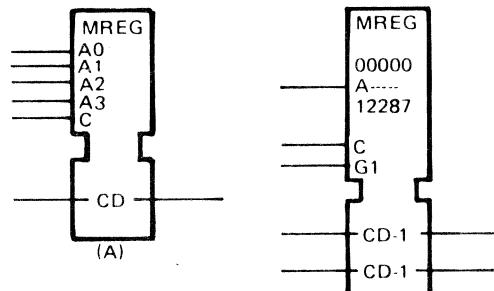

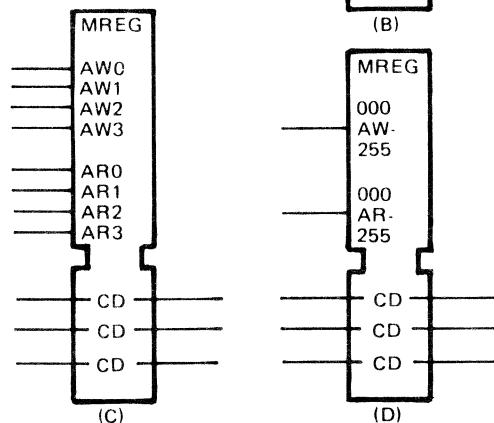

## Multiregister (MREG)

**DEFINITION:** The MREG functional logic block represents groups of associated storage elements in addressable word configuration. The MREG requires address inputs. All functional lines used for storage elements including the dependency notation are applicable.

Addresses are previously decoded and the resultant address line(s) is handled by a single flowline representing all addresses.

## Selector Function (SEL)

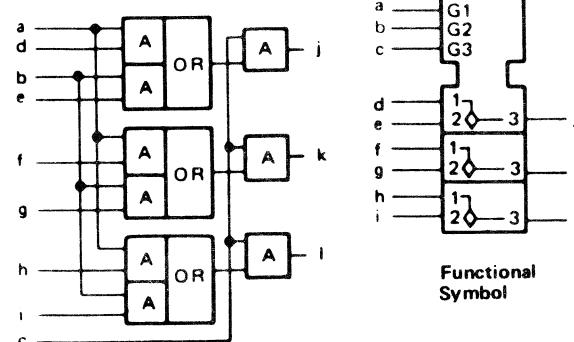

**DEFINITION:** A selector is a functional logic block that consists of two or more OR blocks having input and/or output signals dependent upon common gates.

**Example:**

Output line "j" is active when line "c" is active and lines "d" and "a" or lines "e" and "b" are active.

*Note: The "◊" symbol represents the OR function connection in the data section.*

## Register Function (REG)

**DEFINITION:** A register logic block consisting of a group of associated storage elements with common input and/or output gating or other common input lines such as reset.

*Note: Descriptive nomenclature such as bit 1, may be placed in each logic element.*

**Example:**

Output "h" is active when input lines "e" and "a" are active and the output gate line "b" is active.

Address notation A, AR, or AW must prefix the data. This indicates the data is dependent on an address.

A = Read Only Storage (ROS) or when the read/write address is identical.

AW = Write address. AW must be shown as data input dependent (for example, AWCD).

AR = Read address. AR must be shown as data output dependent.

The numeric address span is specified in the common section.

The G replaces the C to control the data information in the MREG. The C is reserved for the condition that would place a zero in all storage cells not addressed.

| Example | Input Lines Needed    | Output Lines Needed                  |

|---------|-----------------------|--------------------------------------|

| (A)     | A(0,1,2,3)<br>C<br>CD | CD (data)                            |

| (B)     | A(0-12287)<br>C<br>CD | A(0-12287)<br>G1 (gate)<br>CD (data) |

| (C)     | AW(0,1,2,3)<br>CD     | AR(0,1,2,3)<br>CD (data)             |

| (D)     | AW(0-255)<br>CD       | AR(0-255)<br>CD (data)               |

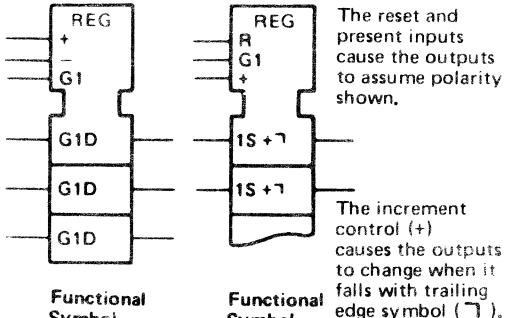

## Counter (REG)

**DEFINITION:** A register to be incremented or decremented under control of input lines drawn to the common section of the symbol with the following notations.

+n: When this line goes to its indicated polarity, the decimal quantity n is added to the binary count contained in the register. The n need not appear when it is a one.

-n: When this line goes to its indicated polarity, the decimal quantity n is subtracted from the binary count contained in the register. The n need not appear when it is a one.

|          |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>A</b> | A<br>A2<br>A2F<br><br>A * OR<br>AC, ac<br>ACC<br>addr<br>ALD<br>AM<br>amps<br>AP-1<br>AR<br>asm<br>assm<br>attn                            | AND function (logic block)<br>control module<br>Control module with fixed heads<br>installed<br>AND * OR function (logic block)<br>alternating current<br>access<br>address<br>Automated Logic Diagram<br>Address Mark<br>amperes<br>Analysis Program<br>Amplifier (logic block)<br>assembly<br>assembler<br>attention                                                                                                              | cm<br>corr<br>CP<br>CPU<br>CR<br>CSW<br>CTL-I<br>ctr<br>CU<br>CUA<br>CV<br>cw<br>cylinder | centimeters<br>correction<br>circuit protector<br>Central Processing Unit<br>diode; rectifier (semiconductor)<br>Channel Status Word<br>control interface<br>controller<br>control unit<br>Channel Unit Address<br>converter<br>clockwise<br>a set of tracks on a storage device<br>that can be accessed without re-positioning the access mechanism                                                                                                |

| <b>B</b> | B2<br>B2F<br><br>BCD<br>BI<br>BO<br>BSCA<br>BSDA<br>BS<br>BSM<br>BTU<br>Bus In<br>Bus Out<br>byte                                          | satellite module<br>satellite module with fixed heads<br>installed<br>binary coded decimal<br>Bus In<br>Bus Out<br>bit significant controller address<br>bit significant device address<br>Bootstrap<br>basic storage module<br>British Thermal Unit<br>bus entering a functional unit<br>bus leaving a functional unit<br>eight bits plus a parity bit                                                                             | DA<br>DAC<br>DC, dc<br>DCB<br>DCD<br>decrement<br>Delta. $\Delta$                         | device address<br>digital-to-analog converter<br>direct current<br>Detection Code Byte<br>decoder (logic block)<br>decrease by regular consecutive steps<br>A three-terminal circuit configuration (usually refers to the primary winding arrangement of a transformer). Also used to indicate a change in some dimension, such as: $\Delta t$ = change in time; $\Delta d$ = change in distance                                                    |

| <b>C</b> | C<br>CA<br>CAR<br>CB<br>CC=3<br>CCB<br>CCHH<br>ccw<br>CCW<br>CDS<br>CE<br>CFEALD<br><br>chan<br>chaining<br>CHK-1<br>CHK-2<br>CHL-1<br>clk | capacitor<br>controller address<br>Cylinder Address Register<br>circuit breaker<br>condition code 3<br>Correction Code Byte<br>cylinder (2 bytes), head (2 bytes)<br>counterclockwise<br>Channel Command Word<br>Configuration Data Set<br>Customer Engineer<br>Condensed Field Engineering<br>Automated Logic Diagram<br>channel<br>sequential linking of instructions or data<br>Check 1<br>Check 2<br>channel interface<br>clock | DEV-I<br>Diff<br>DIO<br>dld<br>DL<br>DOS<br>drive<br><br>Drive A<br>Drive B<br>drop       | edge connector, engineering change<br>Event Control Block (OS/VS only)<br>Error Correction Code<br>Error Log<br>end of file<br>emergency power off<br>error recovery program<br>Environmental Record Editing and Printing<br>Error Code<br>Error Symptom Code generated by a microdiagnostic failure<br>execute input/output<br>external                                                                                                            |

| <b>D</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>E</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>F</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>G</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           | grams<br>gap between Index point and R0<br>gap between Count area and Key area<br>gap between Data area and the Address Mark of the following record<br>gap after Data area of the last record<br>on a track<br>spurious signal<br>ground                                                                                                                                                                                                           |

| <b>H</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           | henries<br>Home Address<br>Head Address Register<br>hard error<br><br>HDA<br>head<br><br>hex                                                                                                                                                                                                                                                                                                                                                        |

| <b>I</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           | identifier<br>integrated file adapter<br>initial microprogram load<br>increase by regular consecutive steps<br>internal<br>IPO<br>IO<br>IPL<br>ISC<br>IW                                                                                                                                                                                                                                                                                            |

| <b>J</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           | Flag Byte<br>Field Engineering Automated Logic Diagram<br>Flip-Flop (logic block)<br>Flip-Latch (logic block)<br>file protect mode<br>Fast Running Interpreter Enabling<br>Natural Diagnosis<br>field replaceable unit<br>Fault Symptom Code<br>Fault Symptom Index                                                                                                                                                                                 |

| <b>K</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           | relay (contactor)<br>key length                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>L</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           | inductor<br>laminar bus<br>light emitting diode<br>limiter (logic block)<br>location<br>microdiagnostic test loop<br>line receiver (logic block)<br>line terminator (logic block)                                                                                                                                                                                                                                                                   |

| <b>M</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           | meter<br>maintenance analysis procedure<br>megabyte<br>microdiagnostic flowchart<br>microdiagnostic Error Code Dictionary<br>maintenance library manual<br>maintenance library cross reference<br>index<br>serial numbered frame containing two drives<br>number system to a base other than ten<br>micropogram load<br>millisecond<br>message<br>monolithic system technology<br>voltage level (see divider tabs)<br>multiple track<br>microsecond |

| <b>N</b> |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           | inverter (logic block)<br>normally closed point<br>normally open point<br>inverter-OR (logic block)<br>no operation<br>voltage level (see divider tabs)<br>nanosecond                                                                                                                                                                                                                                                                               |

## ABBREVIATIONS AND DEFINITIONS

ABBREVIATIONS AND DEFINITIONS

LGND 18

|          |                                             |                                                                                                     |

|----------|---------------------------------------------|-----------------------------------------------------------------------------------------------------|

| <b>O</b> | OBR<br>OE<br>offline                        | outboard recorder<br>exclusive OR function<br>isolated control of a unit from<br>a primary function |

| OLT      | online test                                 |                                                                                                     |

| OLTEP    | online test executive program               |                                                                                                     |

| OLTSEP   | online test standalone executive<br>program |                                                                                                     |

| online   | unit is available to a primary<br>function  |                                                                                                     |

| op       | operation                                   |                                                                                                     |

| OR       | OR function (logic block)                   |                                                                                                     |

| OR * FL  | OR flip latch function (logic block)        |                                                                                                     |

| OS       | operating system                            |                                                                                                     |

|          |                                                                                                                |                                                                                                                                                                                                                                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>P</b> | P<br>PA<br>par<br>parameter<br>P bit<br>PC<br>PG<br>PH<br>pick<br>PLD<br>PLO<br>P/N<br>P/P<br>PS<br>PSW<br>PWR | plug (connector)<br>physical address<br>parity<br>constant value for a given purpose<br>parity bit<br>parity check<br>parity generator<br>polarity hold (logic block)<br>energize relay<br>power line dip<br>phase locked oscillator<br>part number<br>peak-to-peak<br>power supply<br>Program Status Word<br>power |

| <b>Q</b> | Q                                                                                                              | transistor                                                                                                                                                                                                                                                                                                          |

|          |               |                                                           |

|----------|---------------|-----------------------------------------------------------|

| <b>R</b> | R<br>raw data | resistor<br>data as it is read from the storage<br>medium |

|          | R0            | Record 0                                                  |

|          | RCVR          | receiver (logic block)                                    |

|          | Rd            | Read                                                      |

|          | RDCKD         | Read Count Key Data                                       |

|          | RDHA          | Read Home Address                                         |

|          | reg           | register, regulator                                       |

|          | RESV          | Reserved                                                  |

|          | RPS           | Rotational Position Sensing                               |

|          | R/W           | read/write                                                |

|          |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>S</b> | S<br>SCR<br>SCRID<br>SD<br>SEL<br>SERDES<br>servo<br>SERVOUT<br>SFM<br>SIO<br>SIP<br>SK<br>SL<br>SLT<br>soft error<br>SOSP<br>spindle<br>SS<br>SWFE<br>sync bit<br>SYSPRINT | switch<br>silicon controlled rectifier<br>SCR indicator driver<br>skip displacement<br>selector (logic block)<br>serializer/deserializer<br>servo<br>Service Out<br>Set File Mask<br>start input/output<br>Seek in progress<br>Seek<br>system library<br>solid logic technology<br>internally recoverable malfunction<br>that is transparent to the user<br>standalone/online support program<br>that is transparent to the user<br>contained in the HDA<br>single shot (logic block)<br>string switch feature<br>generated by the storage control<br>during Read and Write operations<br>a printer (program assignment) |

| <b>T</b> | T<br>TB<br>TIC<br>TP<br>track (trk)<br>truncate                                                                                                                             | transformer or terminal<br>terminal board<br>transfer in channel<br>test point<br>a location on a storage medium<br>accessible by one R/W head<br>to end an operation before<br>completing the function                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |                        |                                                                                                                       |

|----------|------------------------|-----------------------------------------------------------------------------------------------------------------------|

| <b>U</b> | UC<br>UCW<br>unsuppr   | Unit Check<br>Unit Command Word<br>unsuppressible                                                                     |

| <b>V</b> | V<br>VCM<br>VCO<br>VFO | voltage amplifier (logic block)<br>voice coil motor<br>voltage controller oscillator<br>variable frequency oscillator |

|          |                                     |                                                                                                                                     |

|----------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| <b>V</b> | V<br>VCM<br>VCO<br>VFO              | voltage amplifier (logic block)<br>voice coil motor<br>voltage controller oscillator<br>variable frequency oscillator               |

| <b>W</b> | WCKD<br>word<br>Write<br>wraparound | Write Count Key Data<br>four bytes<br>Write operation<br>advance according to some<br>sequence with automatic restart<br>provisions |

|          |                                     |                                                                                                                                     |

|----------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| <b>W</b> | WCKD<br>word<br>Write<br>wraparound | Write Count Key Data<br>four bytes<br>Write operation<br>advance according to some<br>sequence with automatic restart<br>provisions |

| <b>X</b> | XEQ<br>XOR                          | a three terminal circuit configuration<br>(usually refers to the primary winding<br>arrangement of a transformer)                   |

| <b>X</b> | XEQ<br>XOR                          | execute<br>exclusive OR function (logic block)                                                                                      |

|          |   |                   |

|----------|---|-------------------|

| <b>Z</b> | Z | impedance network |

| <b>Z</b> | Z | impedance network |

---

START CONTENTS

START 1

## START CONTENTS

### INTRODUCTION

Organization of Information . . . . . START 5

How to Perform a Task . . . . . START 10

Documentation Description . . . . . START 20, 21

### 3344 MAINTENANCE PHILOSOPHY

Resources . . . . . START 50

Techniques . . . . . START 50

Procedures . . . . . START 50

Scoping . . . . . START 55

### PROBLEM ANALYSIS

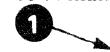

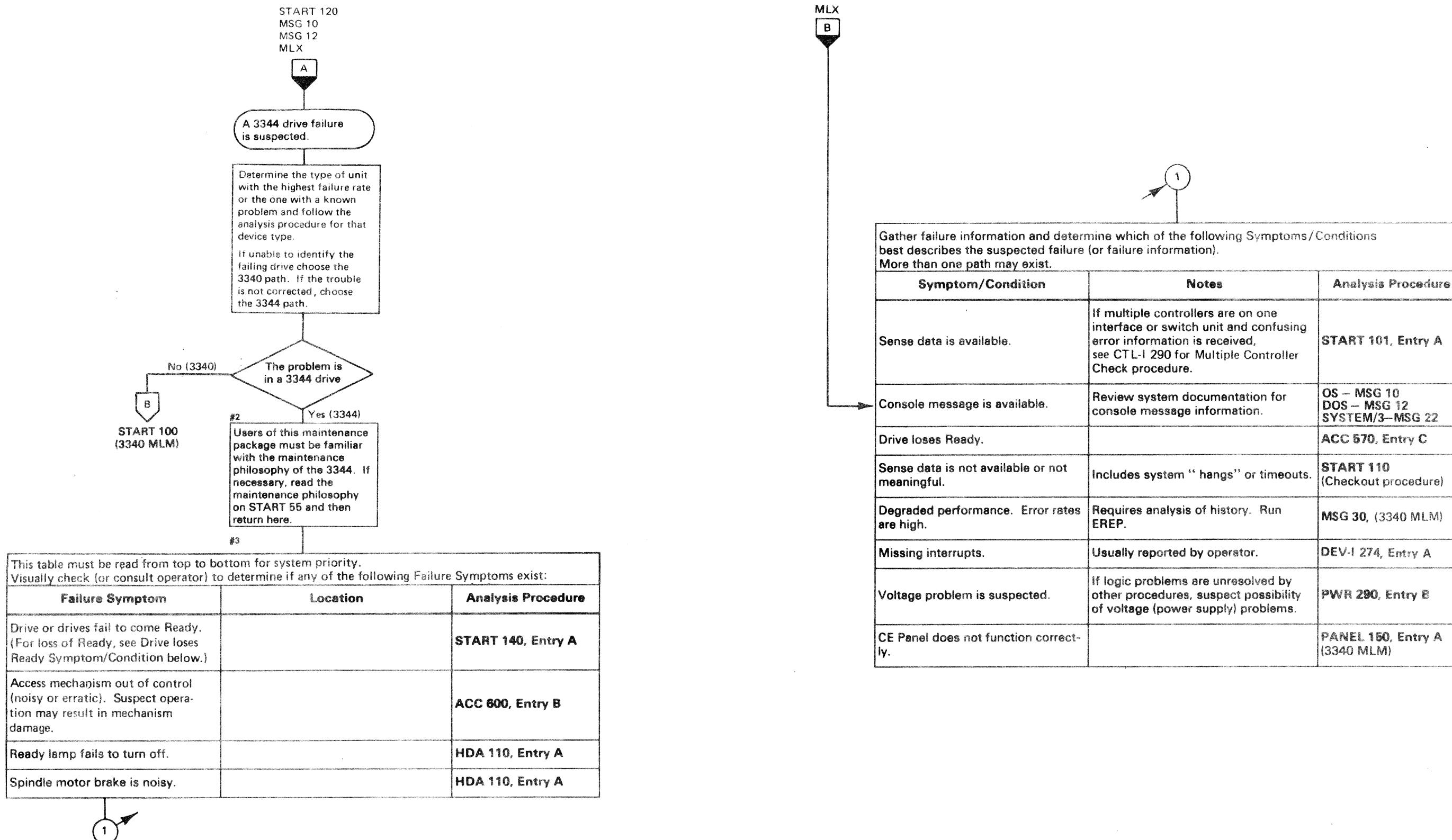

Subsystem Failure . . . . . START 100

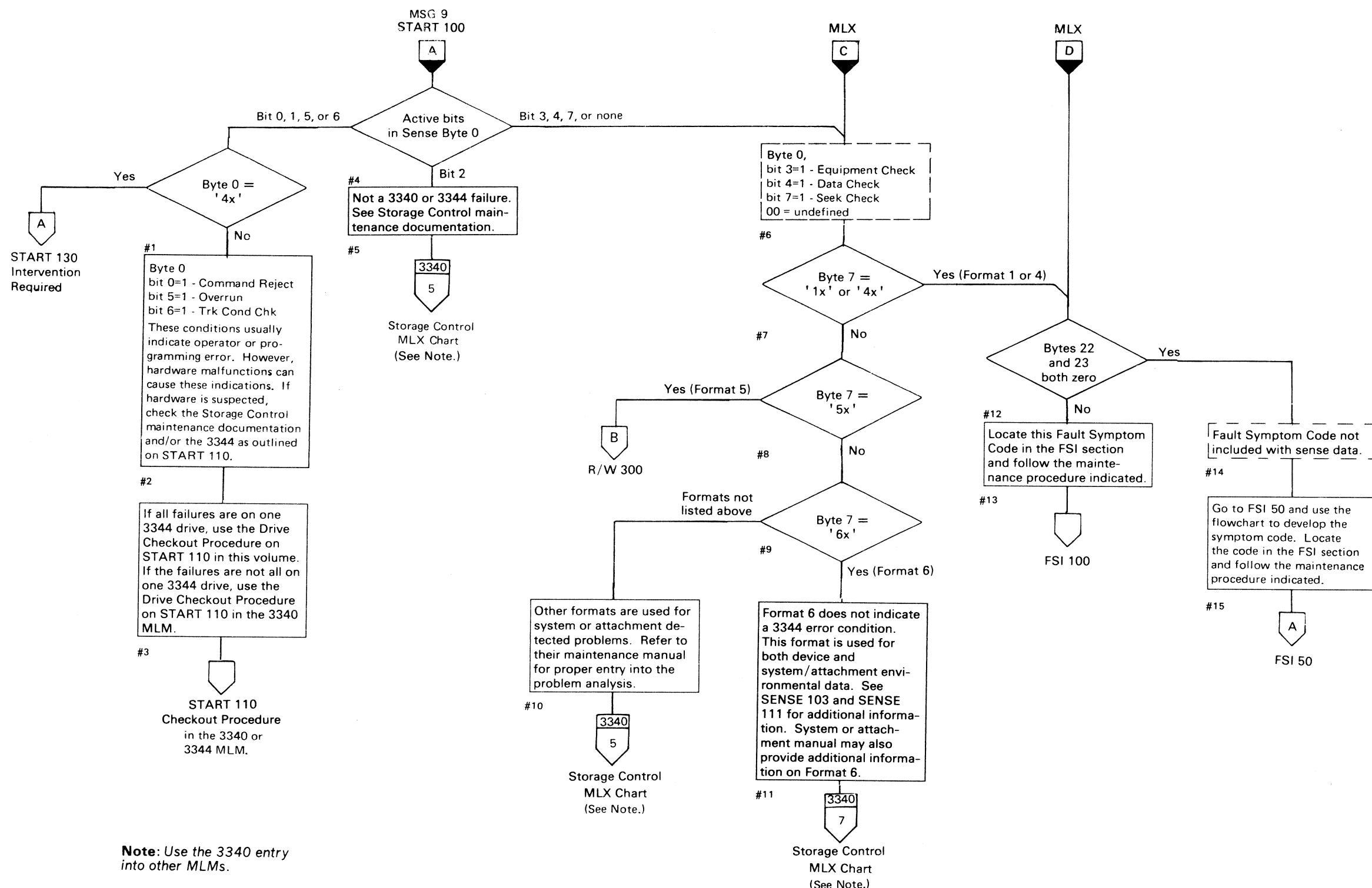

Sense Data . . . . . START 101

Basic Drive Checkout . . . . . START 110

INTERVENTION REQUIRED . . . . . START 130

DRIVE READY FAILURE . . . . . START 140

### MAINTENANCE PROCEDURE

COMPLETE . . . . . START 500

*Note: For 3340 problems (and all problems not related to the 3344), go to the START section in the 3340 MLM.*

3344

KJ0001

Seq. 1 of 2

2359304

Part No.

441235

28 May 76

START CONTENTS

START 1

## ORGANIZATION OF INFORMATION

The START section describes the MLM and the 3344 maintenance philosophy. All problem analysis begins on START 100.

Documentation description on START 20 and 21 defines each section of the manual. Where practical, documentation is arranged in sections corresponding to natural breakdown of machine elements.

Page 1 of each section shows the contents of that section and where related information can be found in other sections of the manual.

Maintenance analysis procedures in each section are entered after the START section and lead the reader through a detailed analysis of each problem. These procedures consist of flowcharts, block diagrams and timing charts.

The OPER section describes the functional operation of the 3344. The information is presented logically; each subject is presented in the order in which it occurs in overall machine operation.

The LGND section defines each symbol used throughout the manual and shows examples of the diagrams used. This section also includes a glossary of special words and abbreviations.

|             |          |

|-------------|----------|

| KJ0001      | 2359304  |

| Seq. 2 of 2 | Part No. |

|           |  |

|-----------|--|

| 441235    |  |

| 28 May 76 |  |

© Copyright IBM Corporation 1976

3344

## HOW TO FIND INFORMATION

Title page in the front of each volume shows the location of each section by volume.

Page 1 of each section shows the contents of that section and where related information can be found in other sections of the manual.

Divider tabs make it easy to locate sections. The tabs also contain useful information about scoping and voltage levels.

Page numbers and titles in "thumbing" position allow rapid scanning.

The alphabetic subject index gives references to specific subjects in the manual.

MLM Feedback forms are located in the front of Volume R01. This is a simple and quick means of sending comments and suggestions directly to the author.

**HOW TO PERFORM A TASK****To install the machine:**

Go to INST 1.

**To learn how the machine operates:**

Go to OPER 1.

**To troubleshoot or repair the machine:**

Go to START 100.

**To remove and replace mechanical parts:**

Go to HDA 700.

**To analyze a console message:**

Go to MSG 9 for OS/VS.

Go to MSG 13 for DOS/VS.

**To operate the CE Panel:**

Go to PANEL 20 in the 3340 MLM.

**To run microdiagnostics:**

Go to MICRO 8.

**To run FRIEND:**

Go to OLT 26 in the 3340 MLM.

**To run online tests:**

Go to OLT 1 in the 3340 MLM.

**To assign alternate tracks:**

Go to OLT 30 in the 3340 MLM.

**To analyze a diagnostic error message:**

Go to MICRO 12 for microdiagnostic error messages.

Go to OLT 40 in the 3340 MLM for online test error

**To review the maintenance philosophy:**

Go to START 50.

**To analyze an EREP printout:**

Go to MSG 22.

**To analyze sense bytes:**

Go to SENSE 100.

**To power off a drive:**

Go to PANEL 10.

The 3344 MLM was designed to be a part of the 3340 MLM.

The 3340 MLM contains six volumes. The entire set of six volumes is shipped with every 3340-A2 Module. Only two volumes, R05 and R06, are shipped with every 3340-Bx Module. Each serial-numbered 3340 module is shipped with its own MLM volumes to ensure that the correct level of documentation for any machine is matched with hardware at any level.

Because the 3344 module is a B2 Module that attaches to a 3340 subsystem, it also has its own volumes R05 and R06. Because of other differences between the 3340 and the 3344, the 3344 MLM also includes volumes R07, R08, and R09.

See START 21 for descriptions of the individual sections.

3340-A2

3340-Bx

3344-B2

3344

|             |          |

|-------------|----------|

| KJ0010      | 2359305  |

| Seq. 2 of 2 | Part No. |

|           |  |  |  |  |

|-----------|--|--|--|--|

| 441235    |  |  |  |  |

| 28 May 76 |  |  |  |  |

© Copyright IBM Corporation 1976

## DOCUMENTATION DESCRIPTION (By section)

## DOCUMENTATION DESCRIPTION (By section) **START 21**

These sections can only be found with each 3340 Control Module (one set per facility). See START 20 in the 3340 MLM.

These sections accompany every 3344 (one set per serial numbered frame).

### START

Primary MLM starting point:

The 3340 START section points to the 3344 START section for all 3344 maintenance information.

### PANEL

Description, operation, and maintenance of the 3340 CE and Operator panels. The 3344 MLM also contains a PANEL section for the 3344 Operator Panels.

### SSW

Maintenance (MAPs) and theory for the string switch feature and associated circuits.

### CTL-I

Maintenance (MAPs) and theory for the control interface and associated circuits. (Tag decodes, addressing, bus assembly circuits, etc.)

### DATA

Maintenance (MAPs) and theory for the controller circuits involved with data transfer. Includes: Read/Write control, Error Detection and correction, SERDES, and PLO/VFO.

### VOLUME R05

#### PANEL

Description of the 3344 Operator Panel.

#### DEV-I

Maintenance (MAPs) and theory for device interface and associated circuits. (Tag decodes, selection, bus assembly circuits, etc.)

#### ACC

Maintenance (MAPs), adjustments, and theory of servo circuits and head positioning mechanics.

#### R/W

Maintenance (MAPs) and theory for drive read/write circuits.

### VOLUME R06

#### HDA

Maintenance (MAPs), theory, adjustments, and removals for the head/disk assembly.

#### RPI

Maintenance (MAPs) and theory for the Index detection and checking, and the rotational position sensing circuits.

#### PWR

Maintenance (MAPs), adjustments, and theory for power supplies, distribution, and sequencing.

#### LOC

Shows structural and component locations.

#### INST

Installation instructions.

### VOLUME R07

#### INDEX

Alphabetical subject index of the MLM.

#### MLX

Pages for cross-referencing other MLMs (3830-2, ISC, IFAs, etc.).

#### LGND

Glossary of technical terms. Abbreviations, Legend of the symbols used in the MLM, including FEALD circuit symbology.

#### START

3344 MLM starting point: Documentation description. How to use the MLM. Maintenance philosophy. Entry point for trouble-shooting and exits to MAPs within functional area MLM sections.

#### OPER

Description of 3344 operations to tie functional units together. Provides high level description of string operation, including some command descriptions allowing the CE to obtain the "big picture" without going to system documentation.

### VOLUME R08

#### MICRO

Microdiagnostic operating instructions and brief routine and test descriptions for the 3344 drives only. See the MICRO section in the 3340 MLM for 3340 microdiagnostic operating instructions.

#### MICRO

Microdiagnostic Error Code Dictionary. Defines Error Codes and ties codes to analysis procedures for the 3344 drives only. See the MICRO section in the 3340 MLM for 3340 Microdiagnostic Error Code Dictionary.

### VOLUME R09

#### MICFL

Microdiagnostic routine descriptions, flowcharts, and scoping procedures for the 3344 drives only. See the MICFL section in the 3340 MLM for the 3340 microdiagnostic flowcharts.

The 3344 is always attached to a 3340-A2 Controller. Because it is attached to a 3340-A2, all maintenance action begins on START 100 of the 3340 MLM. When maintenance is required on a 3344 drive, the START section of the 3340 MLM points to the START section of this 3344 MLM.

The main objective of the 3344 maintenance philosophy, incorporated in the Maintenance Library Manual (MLM), is to help the CE repair hardware failures quickly. To accomplish this objective, emphasis is placed on "how to fix" rather than "how it works". For each failure, the "how to fix" approach utilizes the CE resources, the failure isolation techniques, and the individual analysis procedures.

## RESOURCES

Although the maintenance philosophy is designed for the Product Trained CE, it is recognized that there are significant differences in skill levels, experience, and natural ability among CEs. Additional maintenance procedures and sections of the MLM are provided to allow each individual CE to continue with the maintenance procedure until he has exhausted his resources, or until existing policies dictate that he request assistance.

## TECHNIQUES

The normal card-isolation technique is to replace or swap the specified cards within a particular maintenance procedure until the failing card is located. At the CE's discretion, and/or depending on the customer's requirements, cards may be swapped between drives and/or modules to speed the isolation. In certain areas where it is not practical to rapidly swap or replace components, information is provided to allow isolation of the failing replaceable unit. (These areas include the Power and Head/Disk Assembly.)

Scoping procedures are provided if components are not available for replacement or swapping. Keep in mind that swapping or replacing is the primary card-isolation technique and that scoping is the secondary technique.

## PROCEDURES

Maintenance Analysis Procedures (MAPs) are provided to assist the CE in making decisions (based on sense data, microdiagnostic results, customer data, or visual indications) to isolate the failure to the smallest possible area. MAPs are composed of analysis flowcharts, functional diagrams, and descriptions. Analysis flowcharts and functional diagrams reference other

material in the MLM and ALDs to provide a more complete path to failure isolation. The descriptions are provided to help the CE understand the failing operation. The MAPs are made up of the following interacting parts:

### Start

#### Flowcharts

- Entry

- Microdiagnostics

- Replace Or Order

- Isolation

- Interaction With Other MAP Parts

#### Diagrams

#### Routines

- Microdiagnostics

- Online Tests (OLTs) - (3340 MLM)

- Special Utility Microdiagnostics

- Scoping Procedures

- Support Material And References

- Support Theory

### Start

START 100, in this volume, is always the beginning page for all 3344 maintenance activity. START 100 lists symptoms from visual indications, sense data, console messages, or customer information to point to the correct analysis procedure. (For problems not related to the 3344 drive, go to START 100 in the 3340 MLM.)

### FSI

When instructed to exit to the FSI section, use the FSI section in the appropriate MLM (3340 or 3344).

### Flowcharts

*(For a complete coverage of the blocks used in the flowcharts, refer to the LGND section.)*

### ENTRY

Entry into the flowcharts is made from START, the Microdiagnostic Error Code Dictionary, or another flowchart.

- Replace all the FRUs, return the machine to the customer and defer the isolation procedure until a more opportune time. The CE must use his knowledge of the customer situation, good fiscal management of his territory, and parts availability, to determine the best method for each incident.

### INTERACTION WITH OTHER MAP PARTS

The flowchart is the focal point of the Maintenance Analysis Procedure. Since the other MAP components are all integral parts of the procedure, they are tied to the flowcharts in some way, either directly or by reference.

### Diagrams

The block diagrams and sequence charts support the flowcharts. They give more detail, such as interconnections between cards, and show specific test points for each function. They include physical location and ALD page references if more specific information is needed. (See LGND 10.) Where necessary, detailed descriptions and scoping information are provided.

### Routines

#### MICRODIAGNOSTICS