Funktionsbeschreibung

für Schnellspeicher und Indexregister

**1. Allgemein:**

Schnellspeicher und Indexregister setzen sich zusammen aus der Zusammenschaltung von:

- |                                                   |               |

|---------------------------------------------------|---------------|

| 1 Umlaufkopf für 1 Wort (i.f. Schnellspeicher 1)  |               |

| 1 Umlaufkopf für 2 Worte (i.f. Schnellspeicher 2) |               |

| 2 Lesevorverstärkern                              |               |

| 1 Karte 2fach LSV ✓                               | Z.-Nr. 80 617 |

| 1 Karte S4/Q5-Flip-Flop ✓                         | Z.-Nr. 80 620 |

| 1 Karte S5/Q8-Flip-Flop ✓                         | Z.-Nr. 80 790 |

| 1 Karte Schnellspeicher-Logik 1 ✓                 | Z.-Nr. 80 792 |

| 1 Karte Index-Logik 1                             | Z.-Nr. 80 816 |

| 2 Karten 3fach-Flip-Flop 3 ✓                      | Z.-Nr. 80 791 |

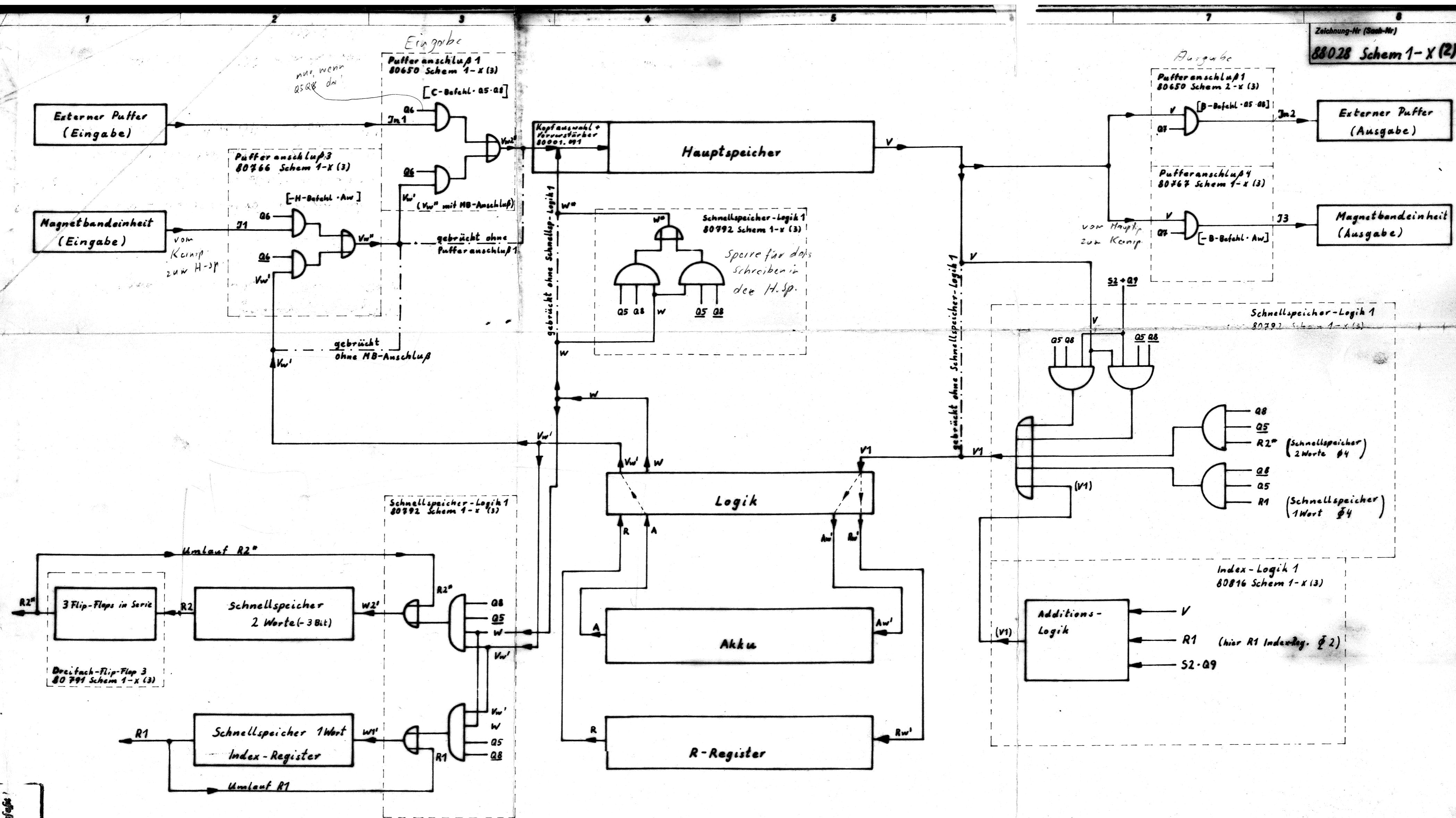

und ihrer Verschaltung mit der LGP-21-Logik.

Die logischen Gleichungen sind den entsprechenden Datenblättern zu entnehmen. Die Gesamtübersicht ergibt sich aus dem Blockschaltbild für EC 84/3 I, Z.-Nr. 88 028 Schem 1-x (2).

Lesen und Schreiben in die Umlaufspeicherköpfe funktionieren wie bei den Registern A, A\*, C und R und werden nicht besonders aufgeführt.

**2. Schnellspeicher:**

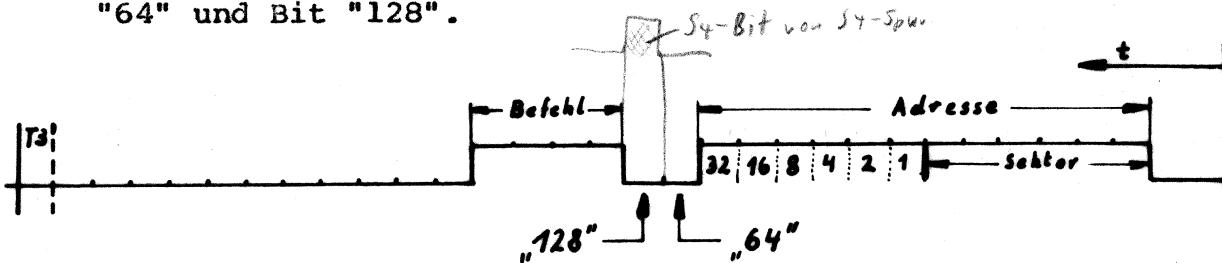

Die Schnellspeicherlogik benutzt zum Ansprechen der Schnellspeicher die beiden Bits zwischen Befehl und Adresse; wenn man die Wertigkeit der Spuradressenbits fortsetzt, also Bit "64" und Bit "128".

Das "128"er Bit wird durch die Karte S4/Q5 Flip-Flop, das "64"er Bit durch die Karte S5/Q8-Flip-Flop entschlüsselt.

S4 entspricht einem Analogsignal auf der Speicherplatte (S4-Spur). Es erscheint genau in der Mitte einer Wortzeit

(nur einmal ist S 4 zur T3-Zeit aufgebracht, um den Scheibenumfang zu markieren) und charakterisiert das "128"er Bit.

S5 gibt S2 um 1 Bit nach links verschoben wieder. Damit charakterisiert S5 S2 das "64"er Bit.

Der Zyklusablauf bei Schnellspeicherbefehlen ist zunächst ganz normal:

- Ø 1: Suche nach dem neuen Befehl

- Ø 2: (1 WZ) Befehl wird aus Hauptspeicher ins R-Register geschrieben

- Ø 3: Auf den Befehl wird entschlüsselt, und der Operand wird gesucht:

Hier wird der Schnellspeicher angesprochen:

Ist zur T3 S4-Zeit in R eine "1", wird Q5 gesetzt

bzw. ist zur S5 S2-Zeit in R eine "1", wird Q8 gesetzt.

$$Q5' = F \underline{G} \underline{H} \underline{T3} R S4 \quad \text{Bit 128 - Bit}$$

$$Q8' = F \underline{G} \underline{H} R S5 \underline{S2} \quad \text{Bit 64 - Bit}$$

Da der Schnellspeicher einen Hauptspeicherplatz ohne Zugriffszeit darstellt, gibt es keine eigentliche Operandenadresse; zweckmäßig wird sie daher immer optimal liegen.

- Ø 4: Befehl wird entsprechend der Lage von Q5 und Q8 ausgeführt.

Man hat also 4 Befehlstypen, die durch die Lage von Q5 und Q8 gekennzeichnet sind:

- a) Q5 Q8 → normale Befehle ✓

- b) Q5 Q8 → Befehle für Schnellspeicher 1 (mit "128"er Bit)

- c) Q5 Q8 → Befehle für Schnellspeicher 2 (2 Wort-Kopf) (mit "64"er Bit)

- d) Q5 Q8 → Befehle für den externen Puffer

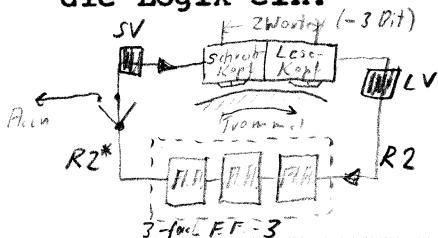

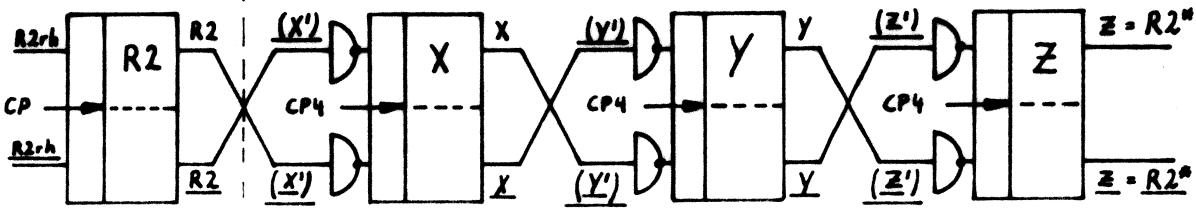

An dieser Stelle sei noch bemerkt, daß beim Schnellspeicher 2 (2-Wort-Umlaufkopf) wegen der doppelten Wortlänge das "vordere" oder "hintere" Wort durch gerade oder ungerade Spuradresse angesprochen wird. Da der 2-Wort-Kopf auf der "Pufferspur" - also weiter außen als die normale Umlaufspur - liegt, und dort die Bitdichte geringer ist, wurden dem gelesenen Signal R2 noch 3 Flip-Flops (Karte 3fach-Flip-Flop 3) nachgeschaltet. Damit wurden Fertigungstoleranzen ausgeschaltet und die doppelte Wortlänge von 64 Bit erreicht. Das eigentlich gelesene Signal R2 geht also erst mit 3 Bit Verzögerung als R2\* in die Logik ein.

X = 00 01 02 03 04 05 06 07 08 09

2 fach LSV

80617 Schem 3-Y(3)

3 fach Flip-Flop 3

80791 Schem 1-X(3)

### Schnellspeicher

Bei Schnellspeicherbefehlen, die vom Akku zum **Hauptspeicher** wirken (H-, C-, R-, Y-Befehle), wird  $Vw'$  in  $\phi 4$  (W) in Schnellspeicher 1 bzw. 2 geschrieben:

$$W1' = \dots + Vw' W Q5 Q8$$

$$W2' = \dots + Vw' W \underline{Q5} Q8$$

Gleichzeitig wird die Schreiberlaubnis  $W^*$  unterbunden und verhindert ein Schreiben von  $Vw'$  in den Hauptspeicher:

$$W^* = W (\underline{Q5} \underline{Q8} + Q5 Q8)$$

Ext. Puffer

Der Umlauf für Schnellspeicher 1 bzw. 2 erfolgt über

$$SSp\ 1: \quad W1' = \dots + R1 (\underline{Q5} + Q8 + \underline{W})$$

$$SSp\ 2: \quad W2' = \dots + R2 (Q5 + \underline{Q8} + \underline{W})$$

Bei Schnellspeicherbefehlen, die vom Schnellspeicher zum Akku wirken (B-, D-, M-, N-, E-, A-, S-Befehle), wird die Information vom Hauptspeicher (V) unterdrückt:

$$V1 = \dots + V (\underline{S2} + \underline{Q9}) (\underline{Q5} \underline{Q8} + Q5 Q8).$$

Statt dessen wird die Information von Schnellspeicher 1 bzw. 2 entsprechend den Befehlen logisch mit dem Akkuinhalt verknüpft:

$$V1 = \dots + R1 Q5 \underline{Q8} + R2^* \underline{Q5} Q8$$

Schn.-Sp. 1                                    Schn.-Sp. 2

### 3. Index-Register:

Schnellspeicher 1 kann zusätzlich auch als Indexregister verwendet werden. Dazu werden noch 3 Flip-Flops benötigt (Karte 3fach-Flip-Flop 3):

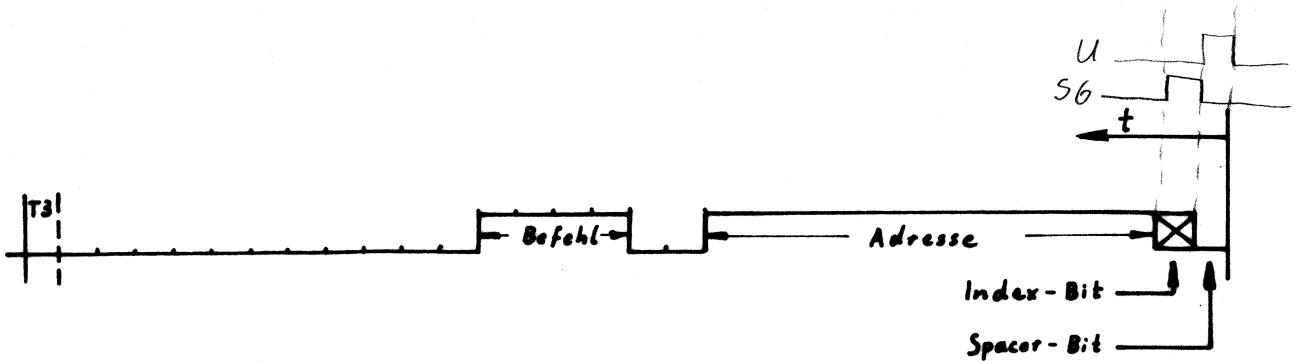

einer, der das Index-Bit markiert ( $S6$ ), ein Übertrags-Flip-Flop für die Additionslogik ( $U$ ) und ein Flip-Flop, der die Zeit der Indizierung angibt ( $Q9$ ). [ $S6, Q9$ ] und [ $U$ ] für Index.

Für die Indizierung kommt nur die Adresszeit - also  $S2$ -Zeit - in Frage. Man kann also das Bit vor der  $S2$ -Zeit als "Index-Bit" ausnutzen.

X = 00 01 02 03 04 05 06 07 08 09

Ein Übertrag durch die Additionslogik kann frühestens ein Bit nach S2 erfolgen. Man kann also den U-Flip-Flop vorher noch anderweitig verwenden. U wird generell mit T3 angesetzt und mit U S2 wieder ausgesetzt, ist damit zur Spacerbitzeit immer angesetzt:

$$U' = \dots + T3$$

$$\underline{U}' = \dots + \underline{S2} \quad U$$

U wird auch noch als Übertragsbit bei der Indexaddition benutzt!

Das wird benutzt, um S6 anzusetzen, S6 wird mit sich selber wieder ausgesetzt:

$$S6' = U \underline{S2} \underline{Q} \underline{9}$$

$$\underline{S6}' = S6$$

S6 markiert also das Index-Bit. - Jämer zur Index-Bit-Zeit da.

In  $\emptyset 2$  wird ganz normal der Inhalt einer Hauptspeicherzelle ins Befehlsregister geschrieben, d.h. es ist  $V1$  (vorher  $V$ ) =  $Rw'$ . Haben wir jedoch einen indizierten Befehl in dieser Hauptspeicherzelle (mit einem Bit zwischen Spacerbit und S2), so wird Q9 gesetzt:

$$Q9' = \underline{E} \underline{G} \underline{S6} \underline{V} \quad \emptyset 2 \quad S6 \underline{V} \quad Q9 \underline{S2} = \text{Indexrechn-Zeit}$$

$$\underline{Q9}' = T3$$

zur  $\emptyset 2$

In diesem Fall ist Q9 zur S2-Zeit an, und Q9 . S2 markiert die Zeit der Indizierung. Der normale Weg von  $V1 \rightarrow Rw'$  wird während der S2.Q9-Zeit unterdrückt:

$V1 = \dots + V (\underline{S2} + \underline{Q9}) (Q5 \underline{Q8} + Q5 Q8)$ , da die Klammer (S2 + Q9) nicht erfüllt ist.

Dafür wird V und Schnellspeicher 1 über die Additionslogik arithmetisch miteinander verknüpft (ohne Übertrag in die S2-Zeit):

$$V1 = \dots + S2 \cdot Q9 (U \underline{V} \underline{R1} + U V R1 + \underline{U} \underline{V} R1 + \underline{U} V \underline{R1})$$

Indexzeit

Setzen und Rücksetzen des Übertrags-Flip-Flops U während der Additionszeit erfolgt über:

$$U' = \dots + S2 \cdot Q9 R1 V \underline{U}$$

$$\underline{U}' = \dots + U S2 \underline{R1} V$$

Am Ende der  $\emptyset 2$  steht also

der Befehl mit der um den Inhalt von R1 erhöhten Adresse im R-Register.

X = 00 01 02 03 04 05 06 07 08 09

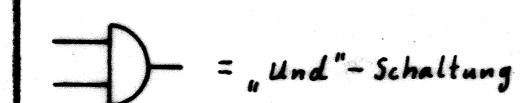

### Schaltzeichen:

z.B.: Schnellspeicher 1 Wort

besteht aus: 1 Umlauspeicherkopf für 1 Wort,

1 Leseverstärker, 1 Lese-Schreib-

verstärker und einer Verstärkung.

### Erläuterung:

Der Übersichtlichkeit wegen ist in diesem Blockschaltbild der direkte logische Weg angegeben. Die Realisierung der logischen Funktionen auf den einzelnen Druckschaltungen weicht oft von dieser Darstellung ab, z.B. Benutzung der inversen Signale statt der normalen u.ä.m. - Die technischen Einzelheiten ergeben sich aus den entsprechenden Schemen.

Zusätzlich ist der „externe Pufferanschluß“ und der „Magnetbandanschluß mit eingezeichnet. Die auslösenden Befehle stehen in [ ] dabei.

Bei Pufferanschluß 1 Z.Nr. 80650-X(3) gibt es noch Ausführungen, die den -B-Befehl (für Ausgabe) und den -C-Befehl (für Eingabe) benutzen.