April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 1

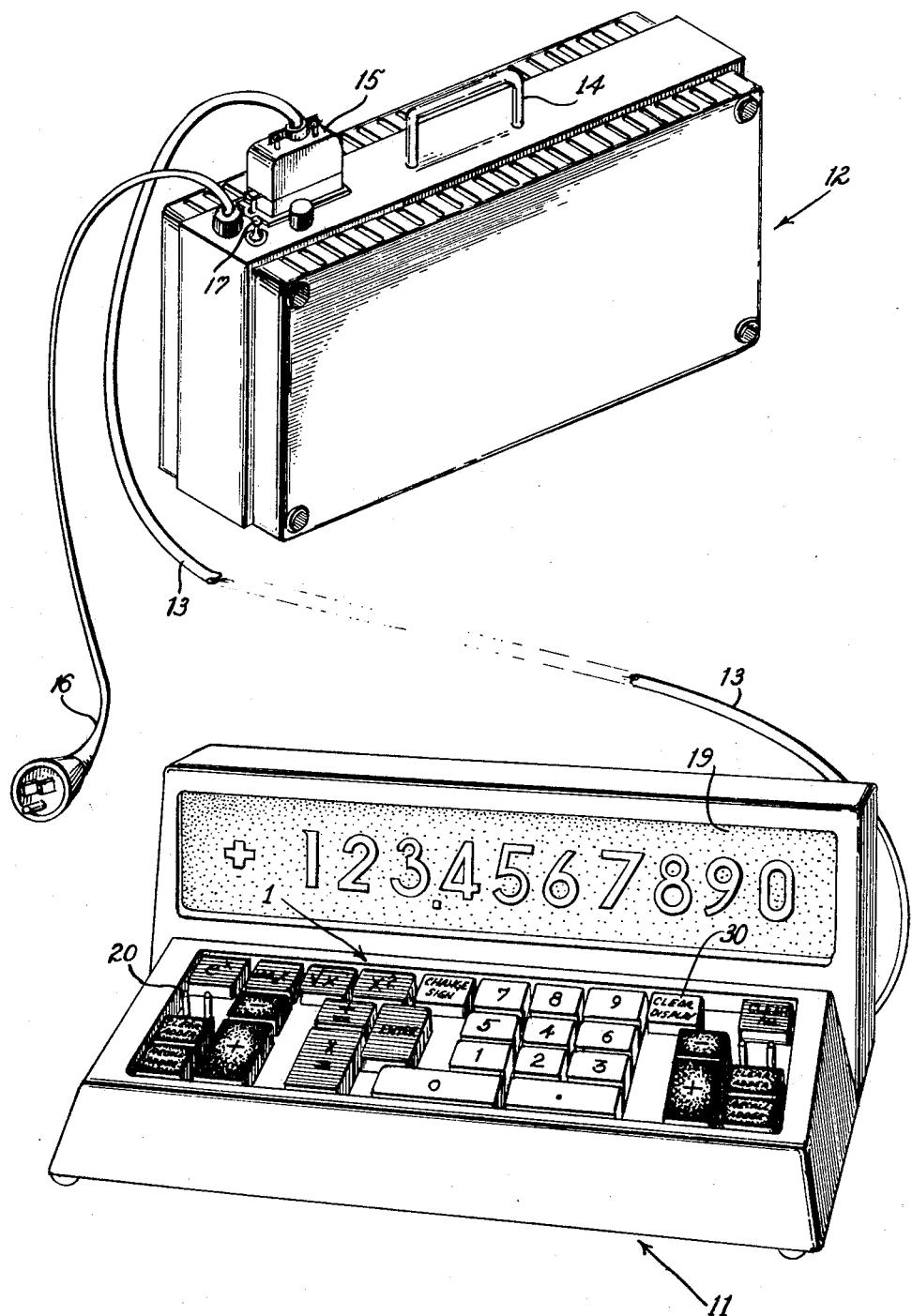

FIG 1

April 28, 1970

AN WANG ET AL

**3,509,329**

## CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 2

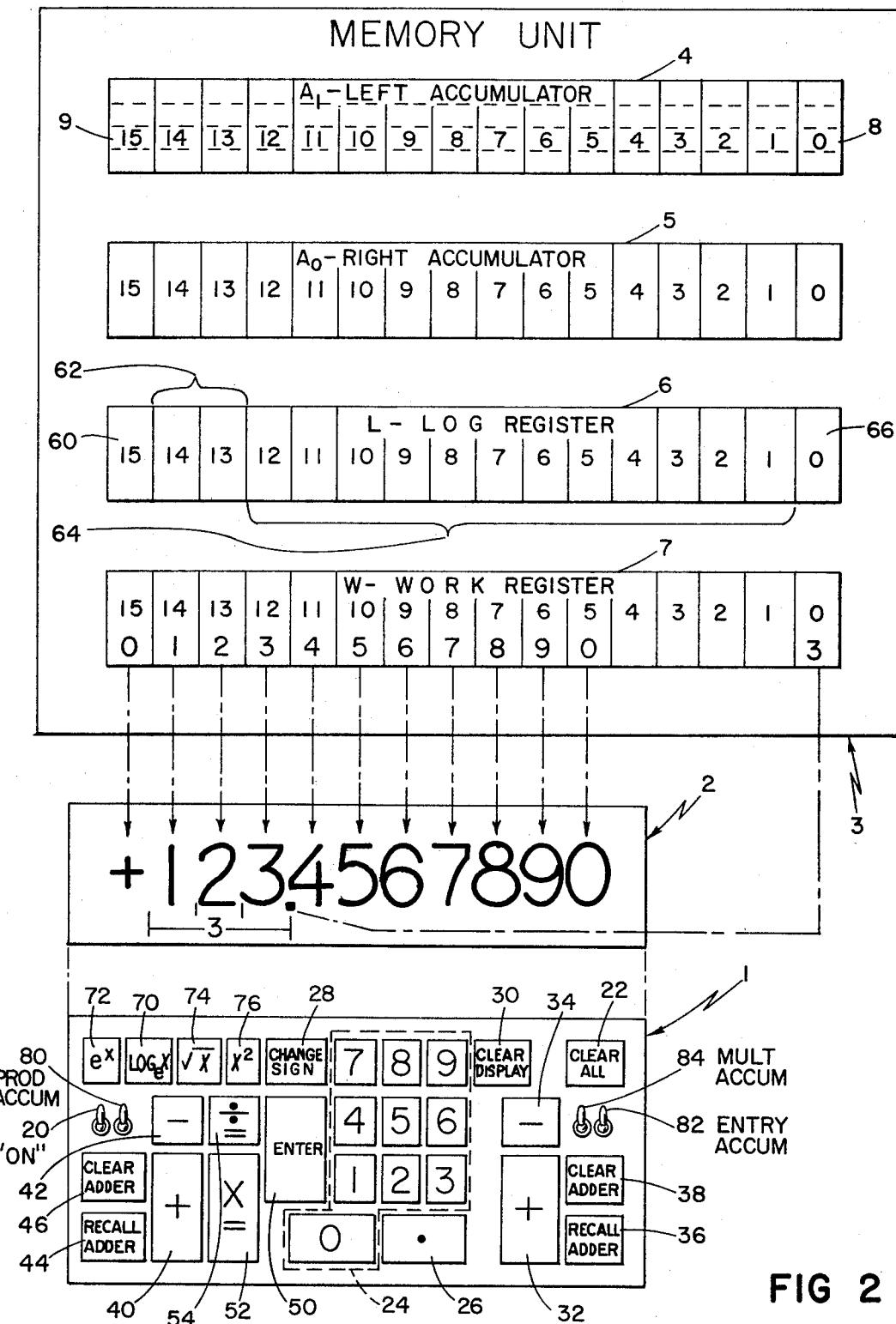

FIG 2

April 28, 1970

AN WANG ET AL

**3,509,329**

## CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 3

3

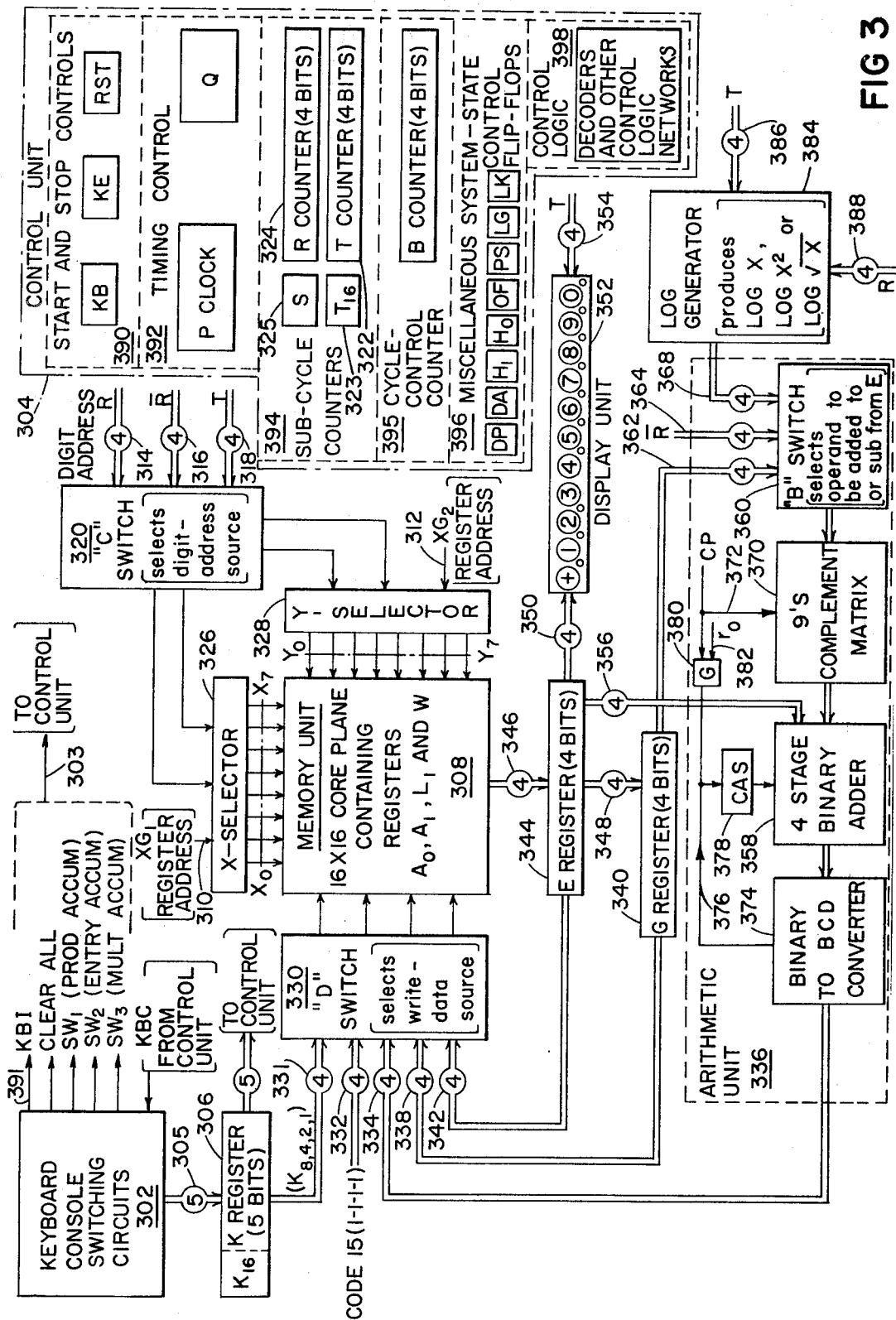

FIG

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 4

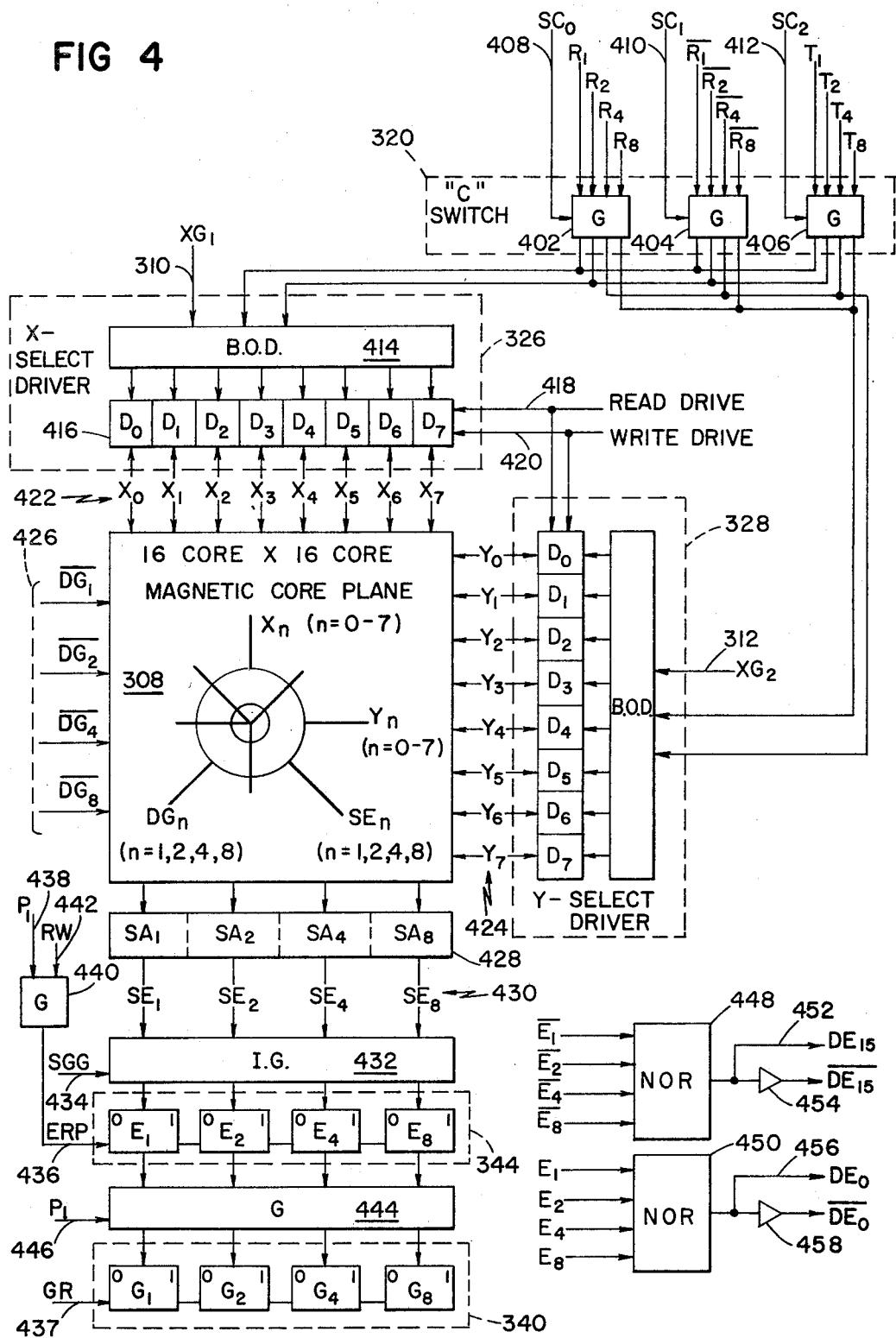

FIG 4

April 28, 1970

AN WANG ET AL

**3,509,329**

## CALCULATOR

filed Oct. 24, 1966

47 Sheets-Sheet 5

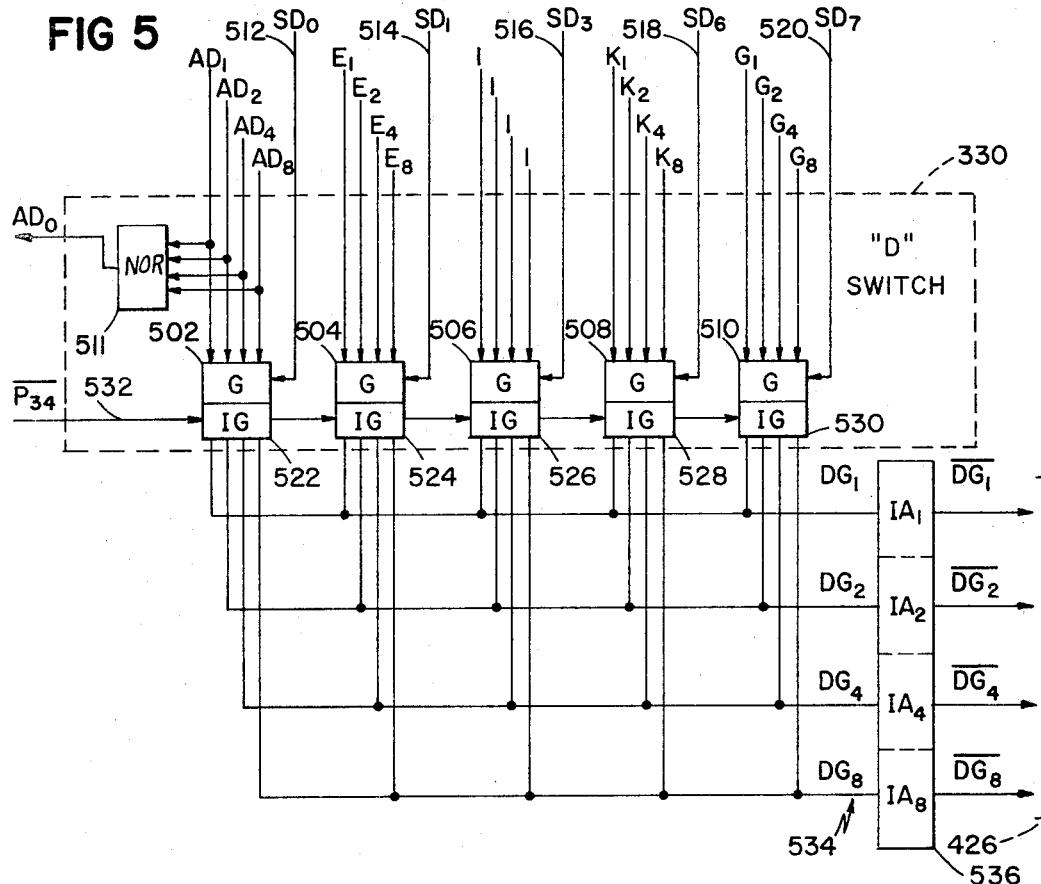

FIG 5

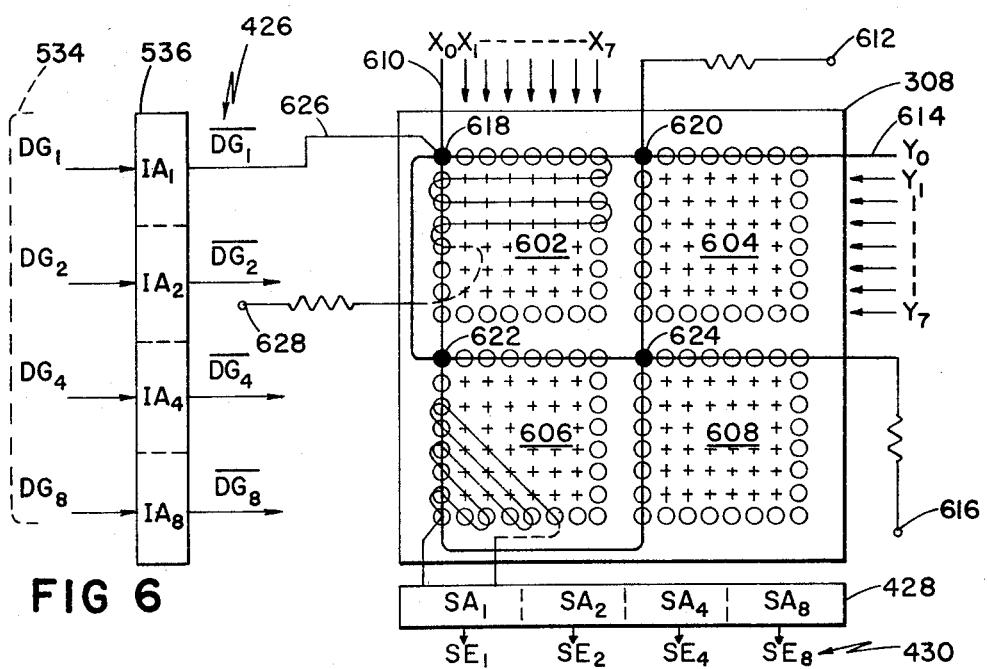

FIG 6

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 6

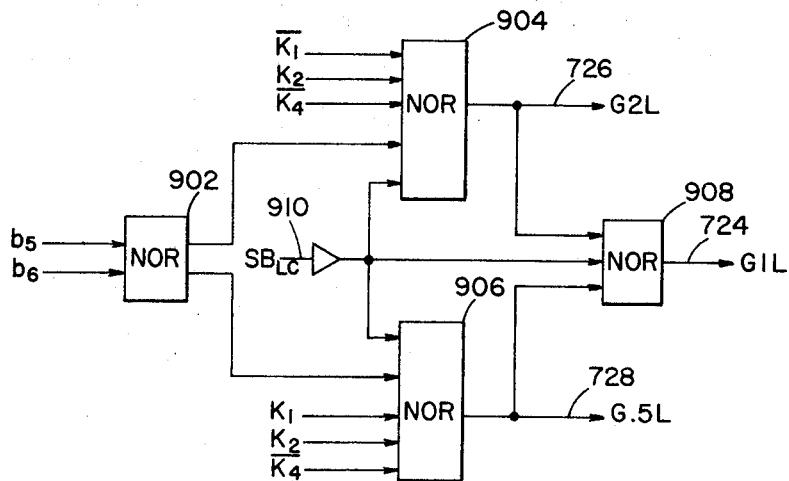

FIG 9

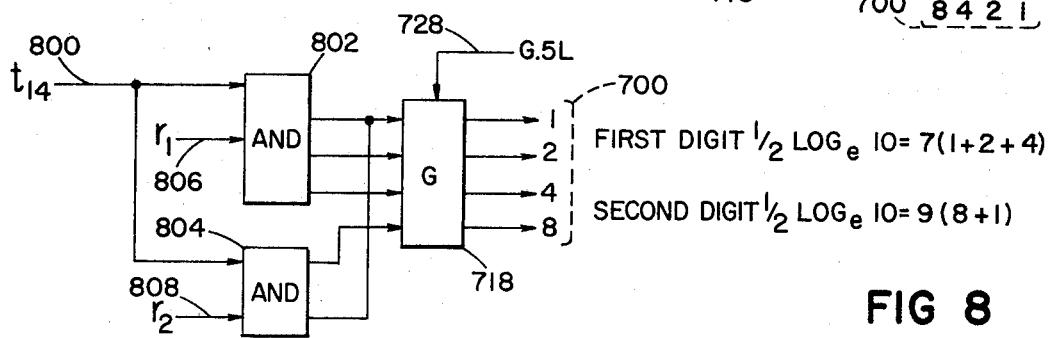

FIG 8

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 7

FIG 10

April 28, 1970

AN WANG ET AL

3,509 329

## CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 8

FIG

April 28, 1970

AN WANG ET AL

**3,509,329**

## CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 9

**FIG 12**

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 10

FIG 13

April 28, 1970

AN WANG ET AL.

**3,509,329**

## CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 11

FIG 14

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 12

FIG 15

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 13

FIG 16

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 14

FIG 17

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 15

FIG 18

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 16

FIG 19

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 17

FIG 20

April 28, 1970

AN WANG ET AL

3,509,329

## CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 18

FIG 21

April 28, 1970

AN WANG ET AL

3,509,329

## CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 19

FIG 22

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 20

## FIG 23

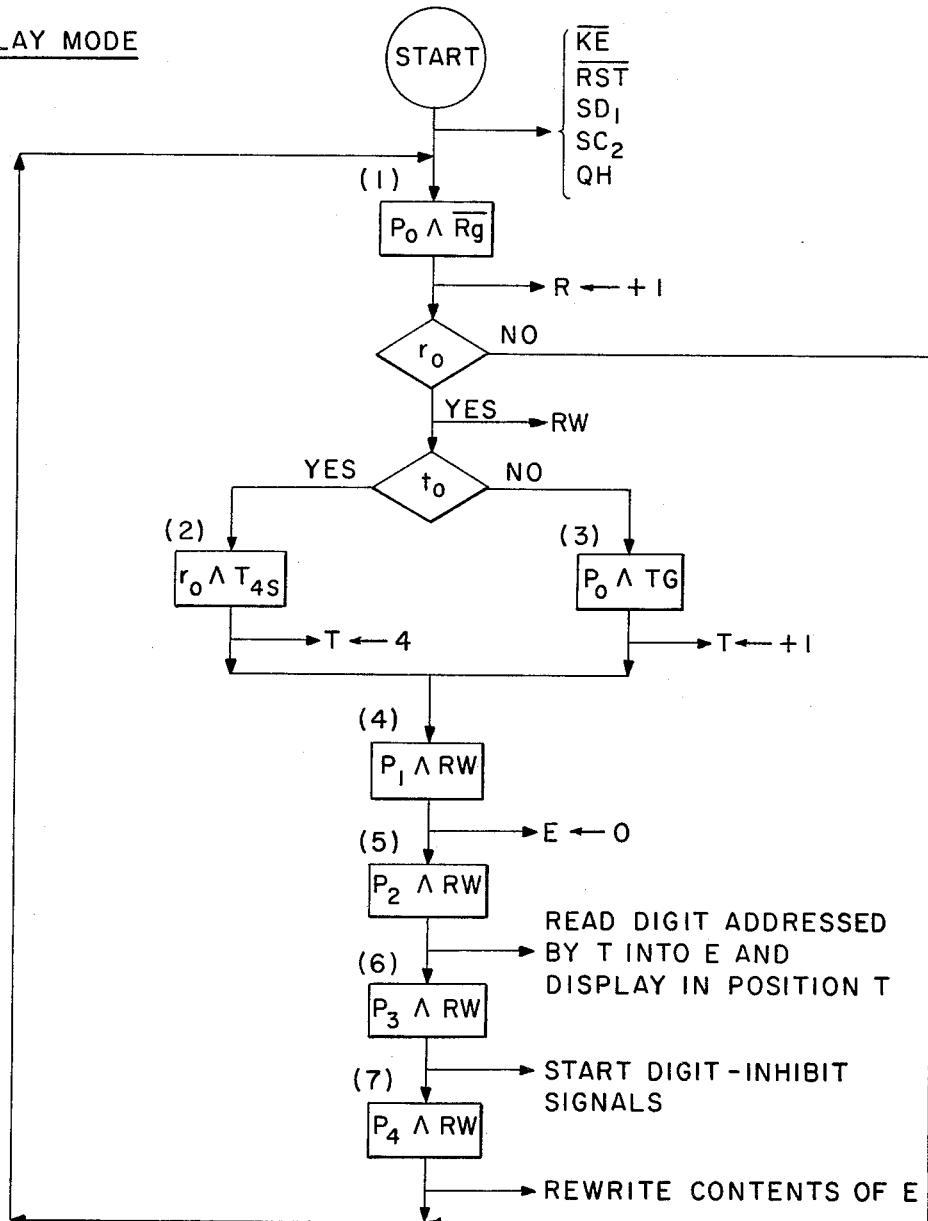

### DISPLAY MODE

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 21

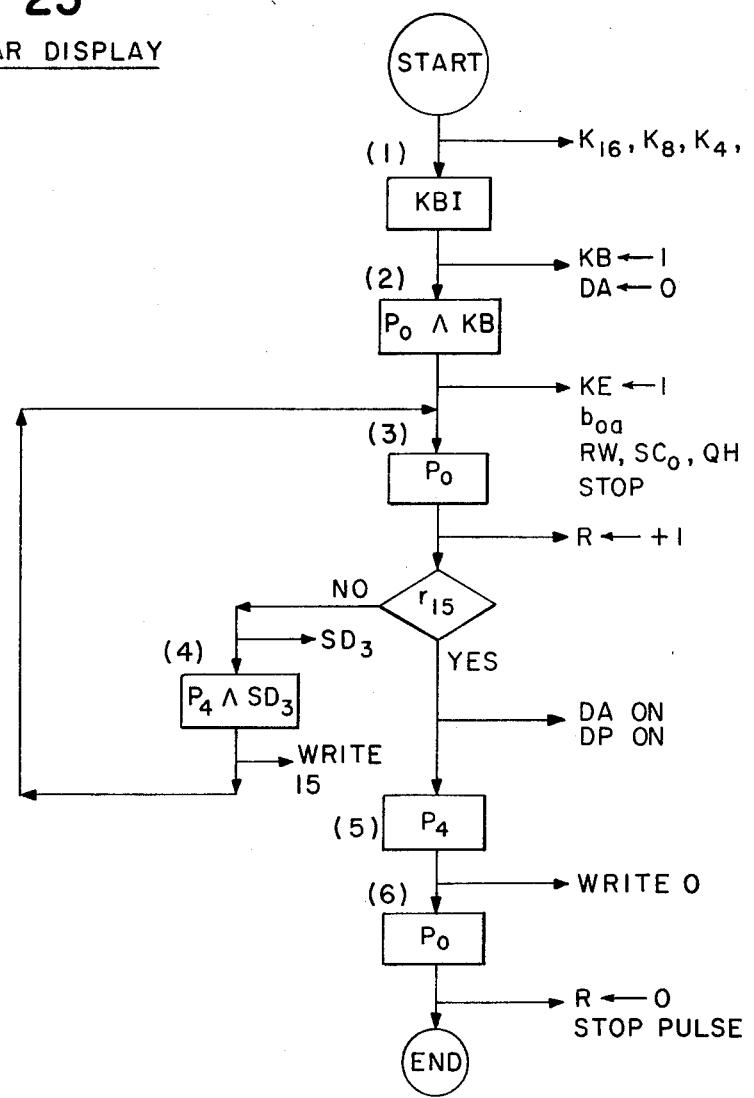

## FIG 24

CLEAR ALL

NOTE:

| Q | S | XG <sub>1</sub> | XG <sub>2</sub> |                |

|---|---|-----------------|-----------------|----------------|

| 0 | 0 | 0               | 0               | W              |

| 1 | 0 | 1               | 0               | L              |

| 0 | 1 | 0               | 1               | A <sub>0</sub> |

| 1 | 1 | 1               | 1               | A <sub>1</sub> |

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 22

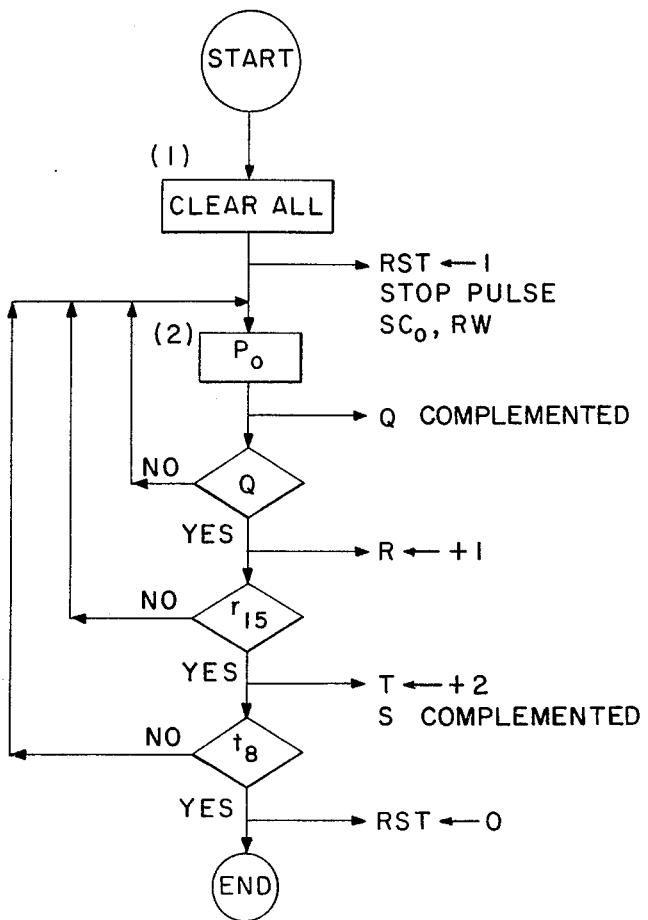

## FIG 25

### CLEAR DISPLAY

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

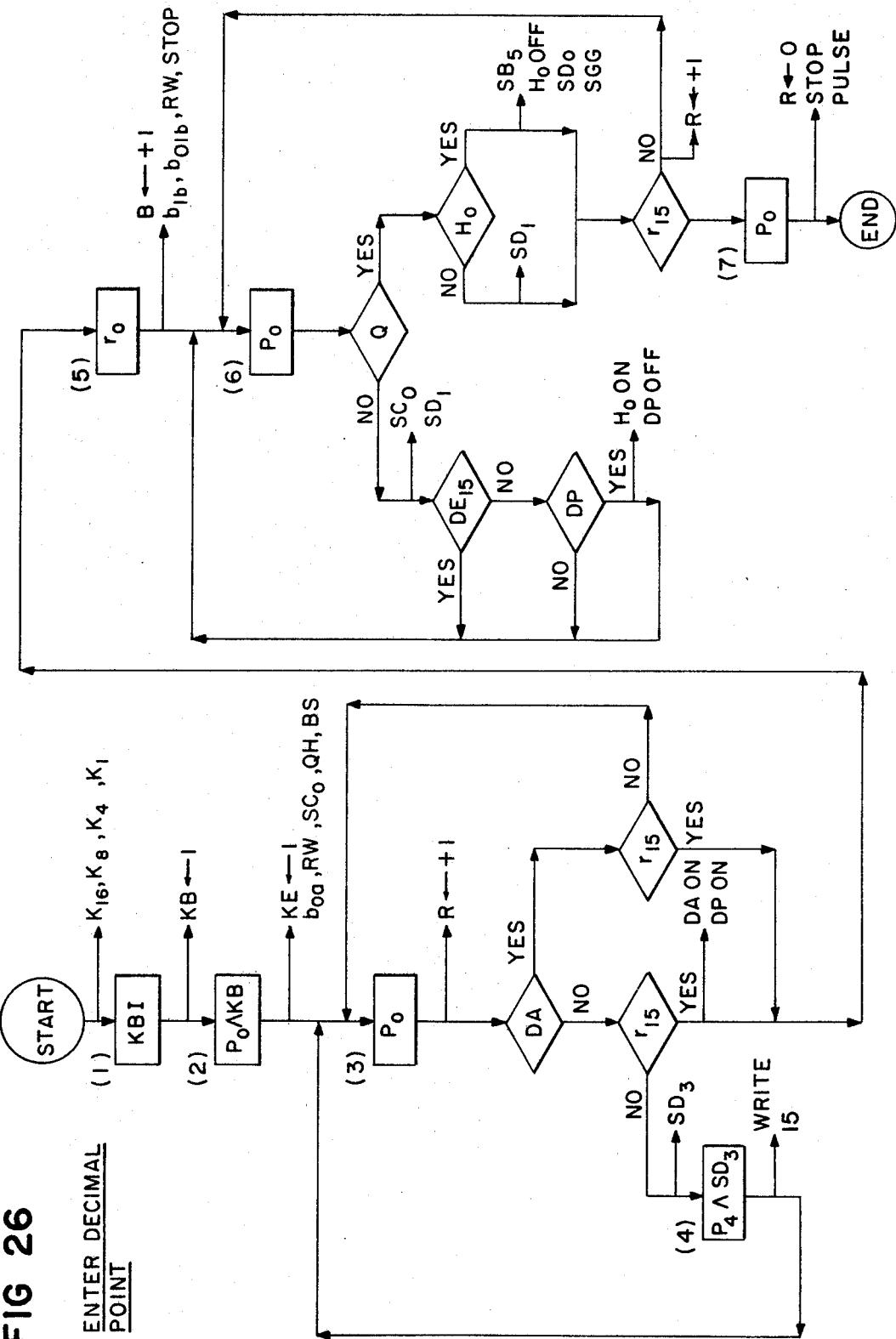

47 Sheets-Sheet 23

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 24

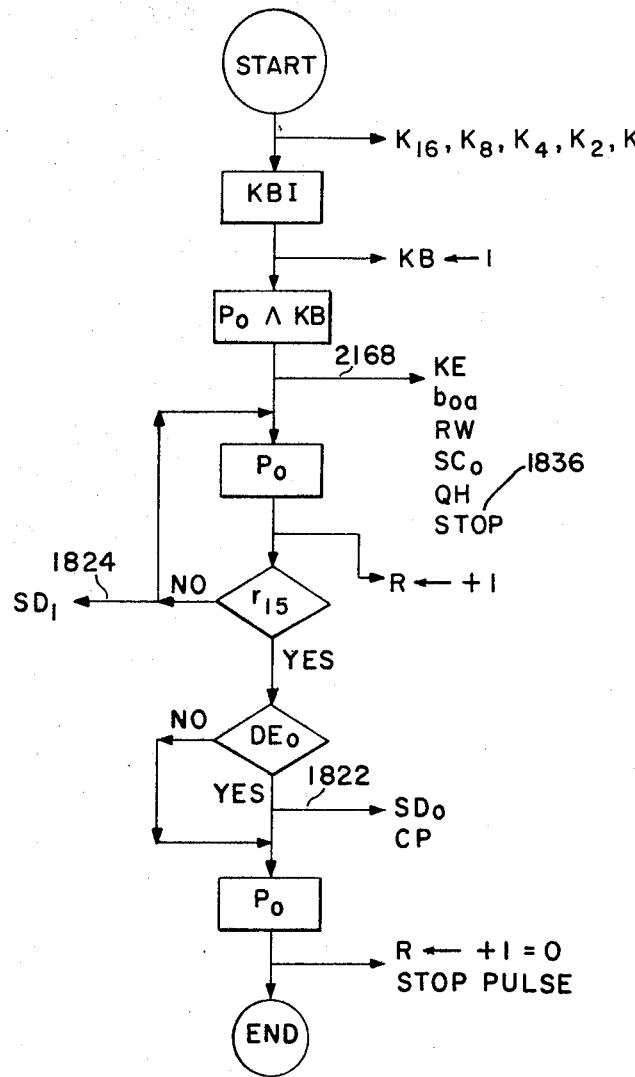

FIG 27

CHANGE SIGN

April 28, 1970

AN WANG ET AL

3,509,329

## CALCULATOR

Filed Oct. 24, 1966

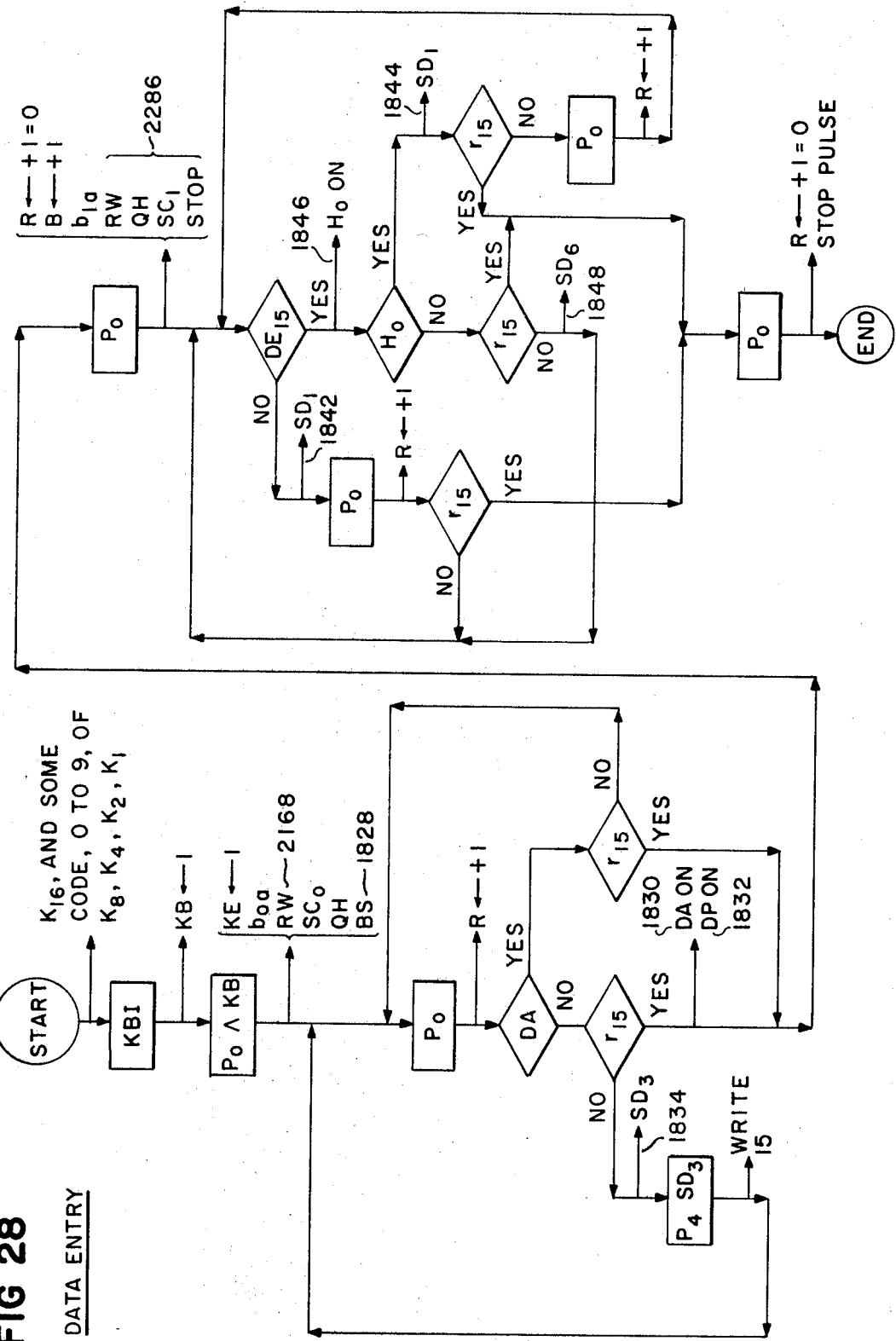

47 Sheets-Sheet 25

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 26

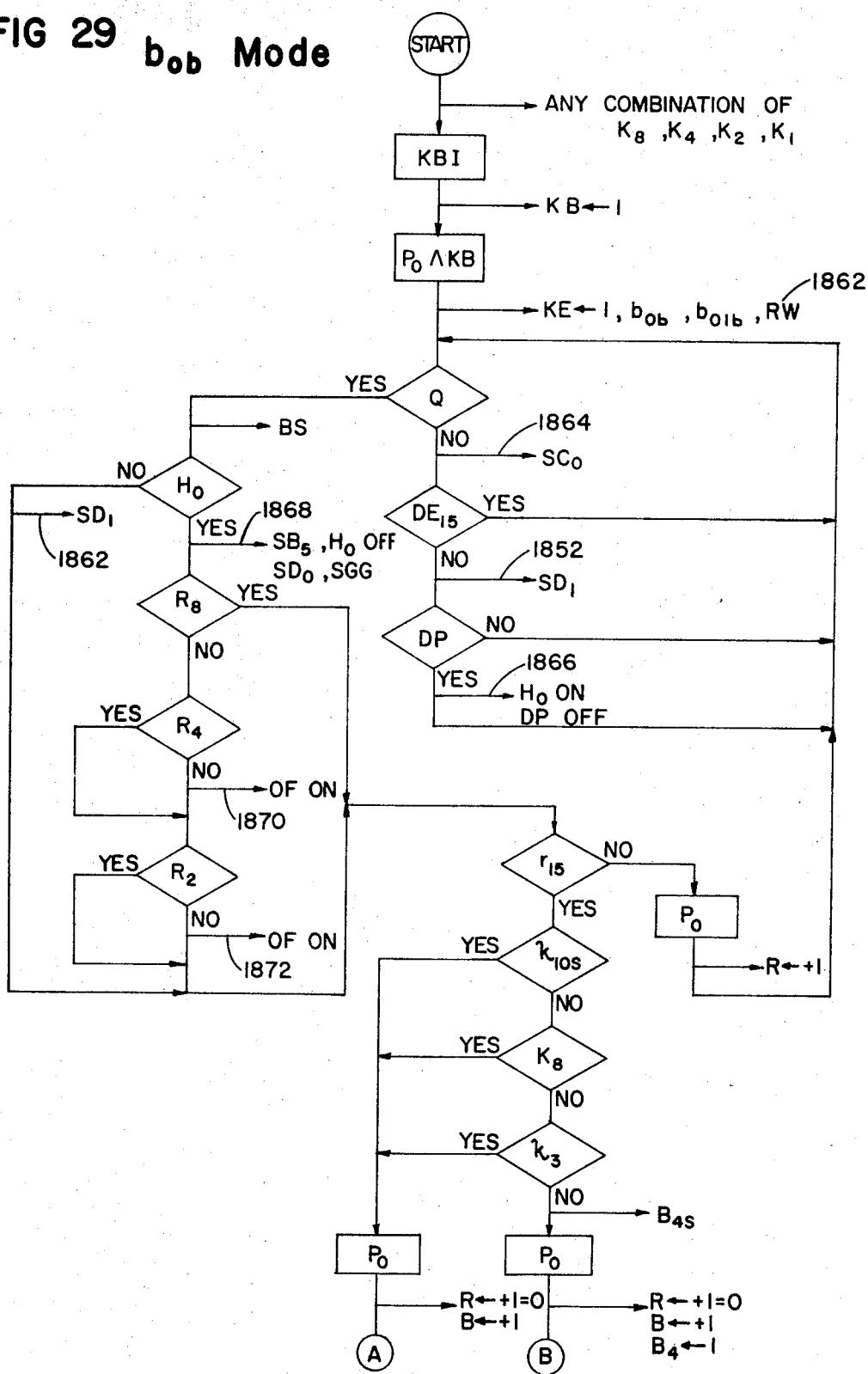

FIG 29  $b_{ob}$  Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 27

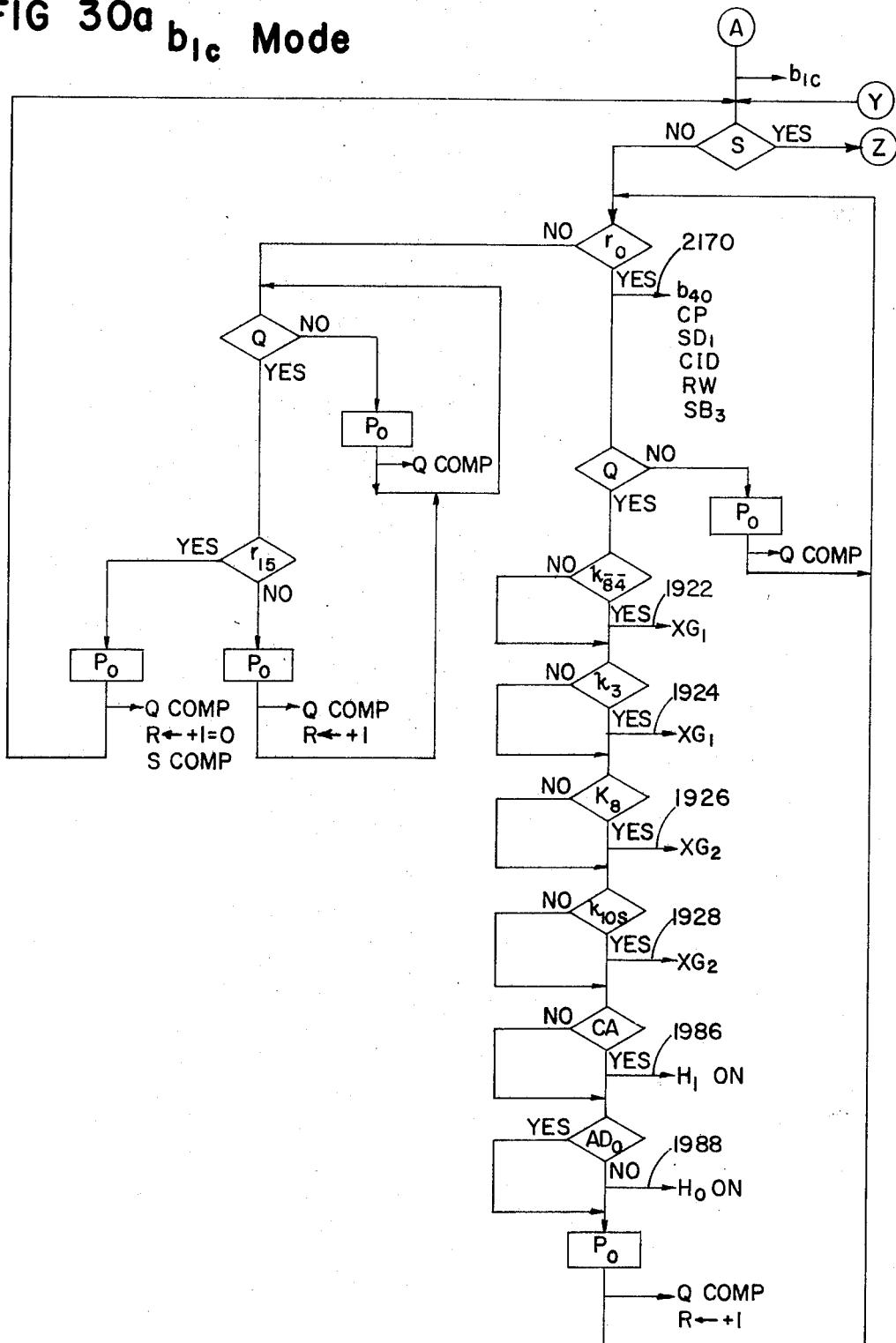

FIG 30a  $b_{1c}$  Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 28

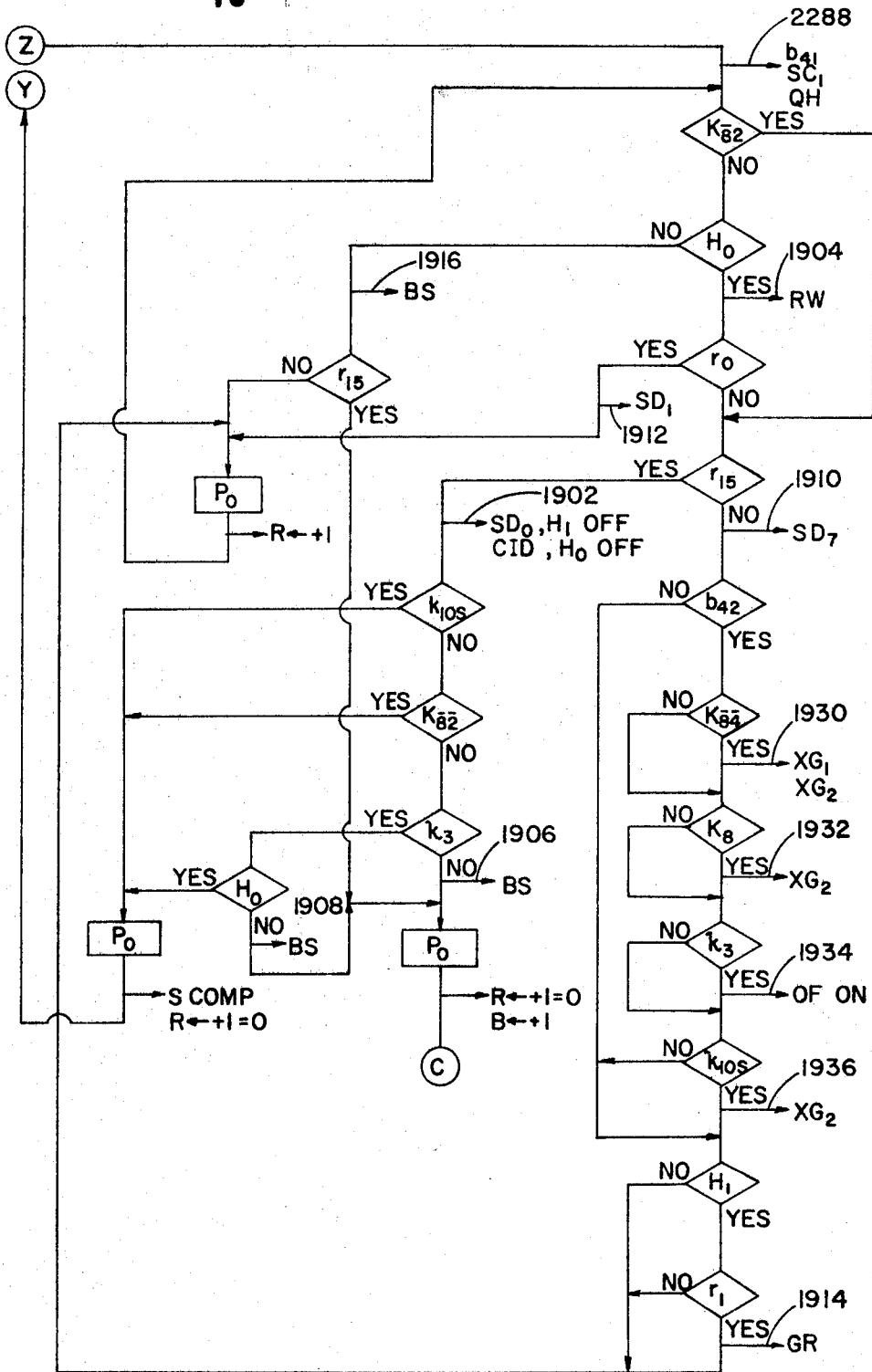

**FIG 30b  $b_{1c}$  Mode**

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 29

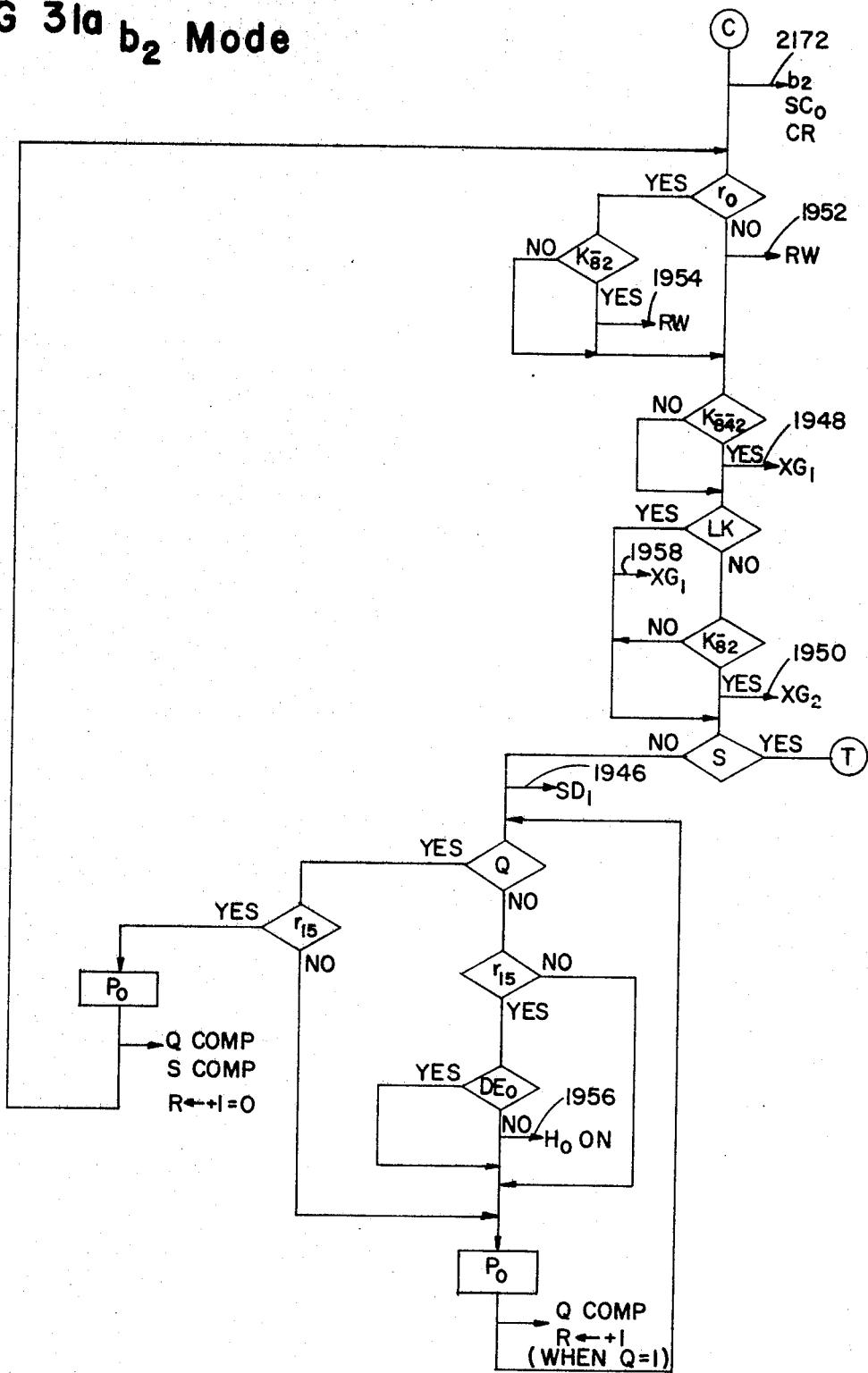

FIG 3a b<sub>2</sub> Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 30

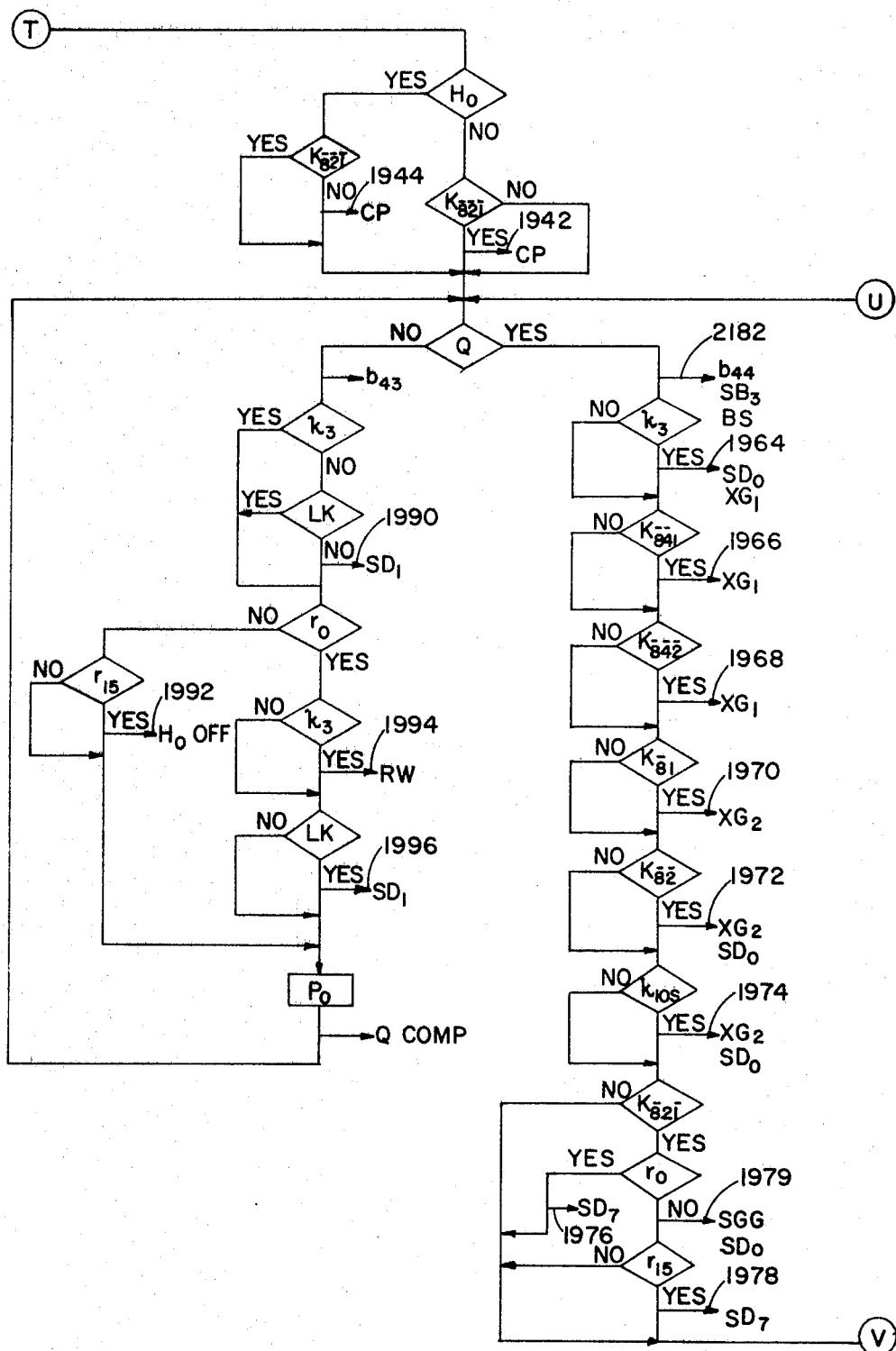

## FIG 3lb b<sub>2</sub> Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 31

### FIG 31c $b_2$ Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 32

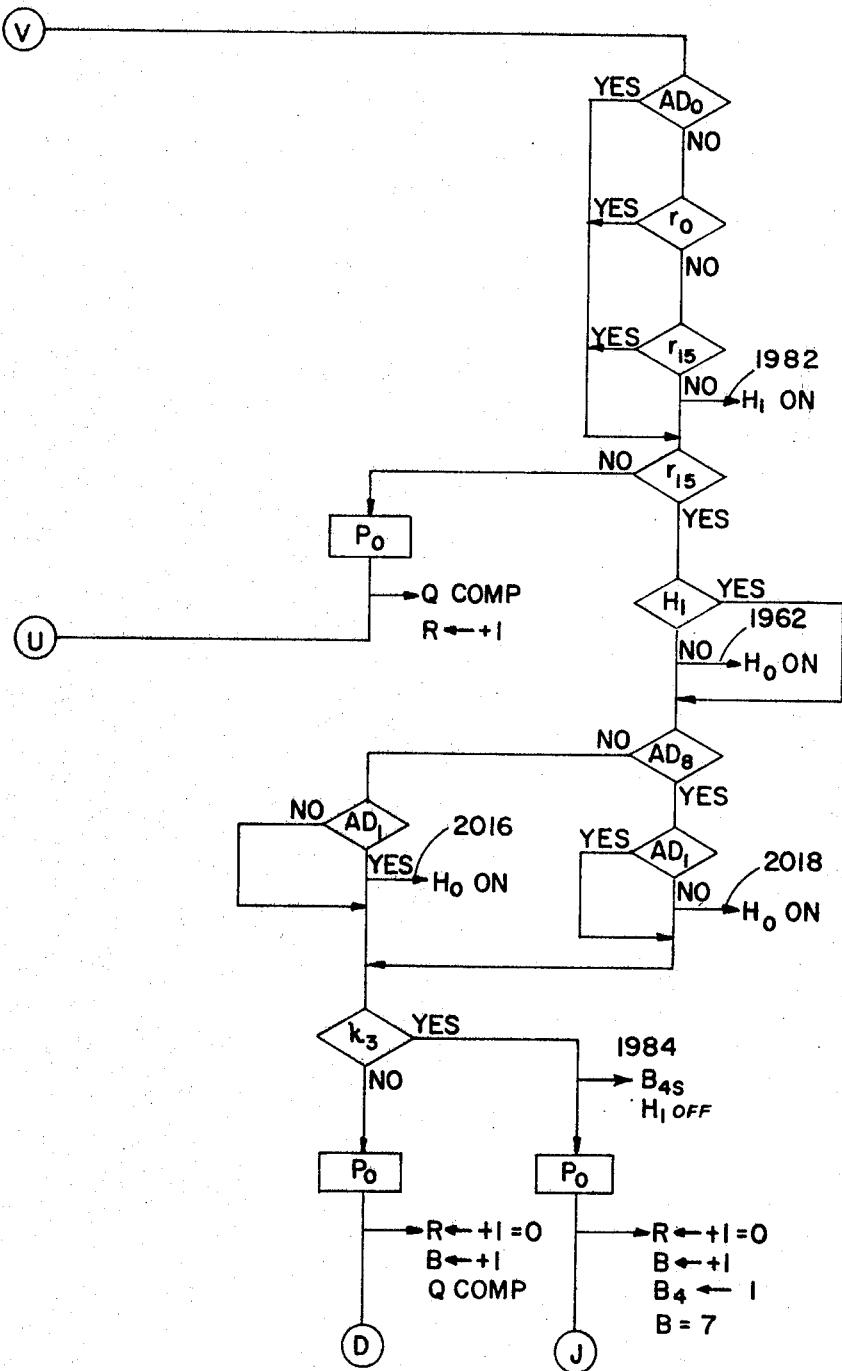

FIG 32 b<sub>3</sub> Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 33

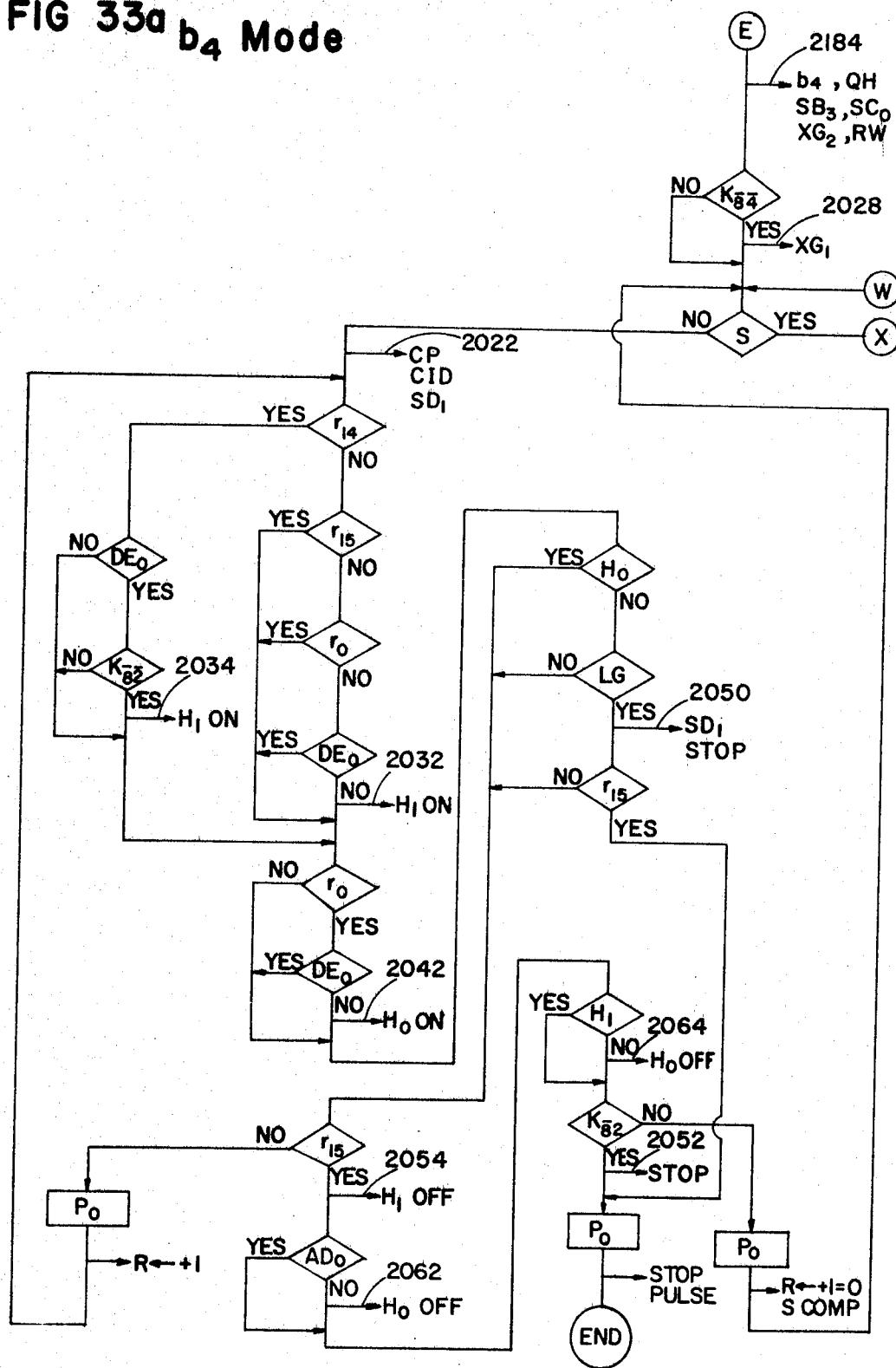

FIG 33a b<sub>4</sub> Mode

April 28, 1970

AN WANG ET AL.

**3,509,329**

## CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 34

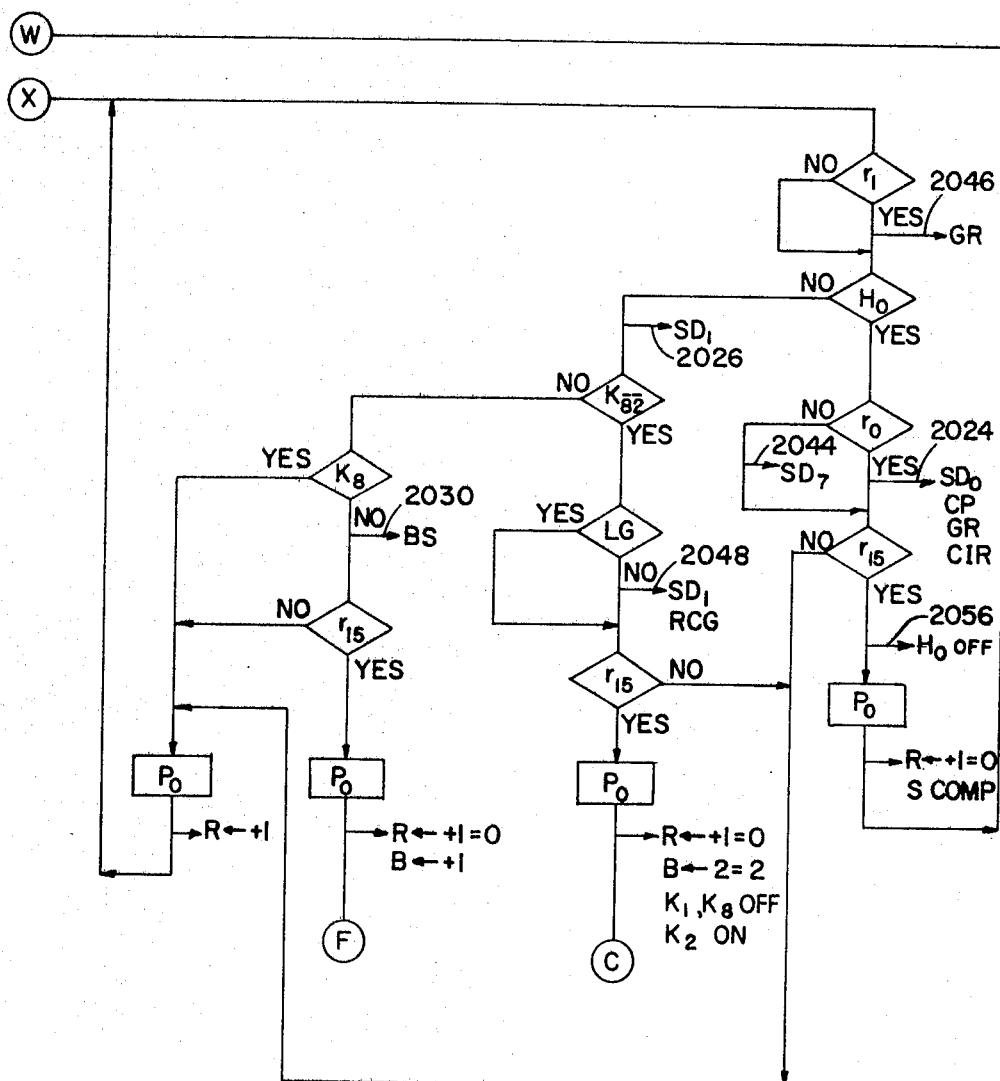

FIG 33b  $b_4$  Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 35

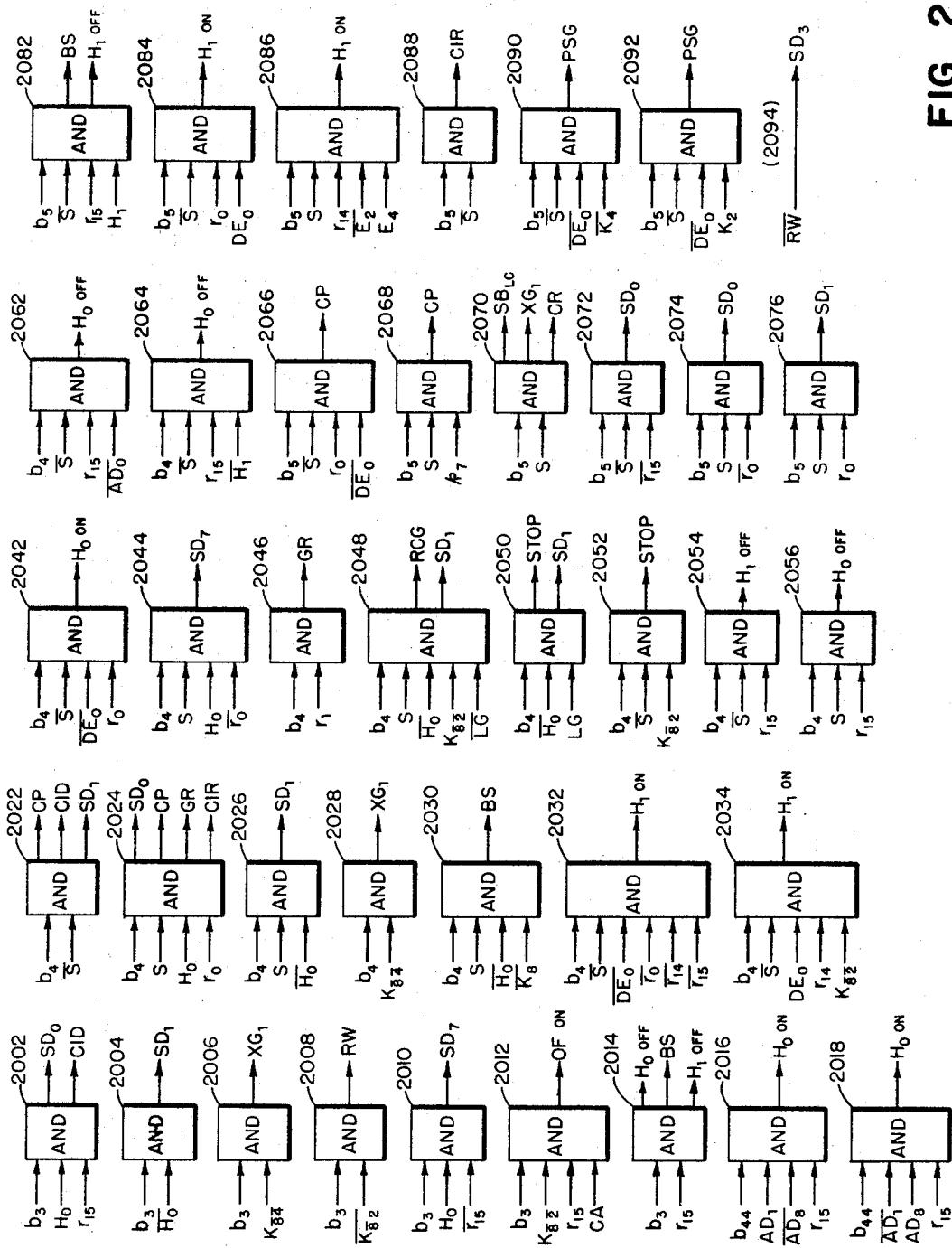

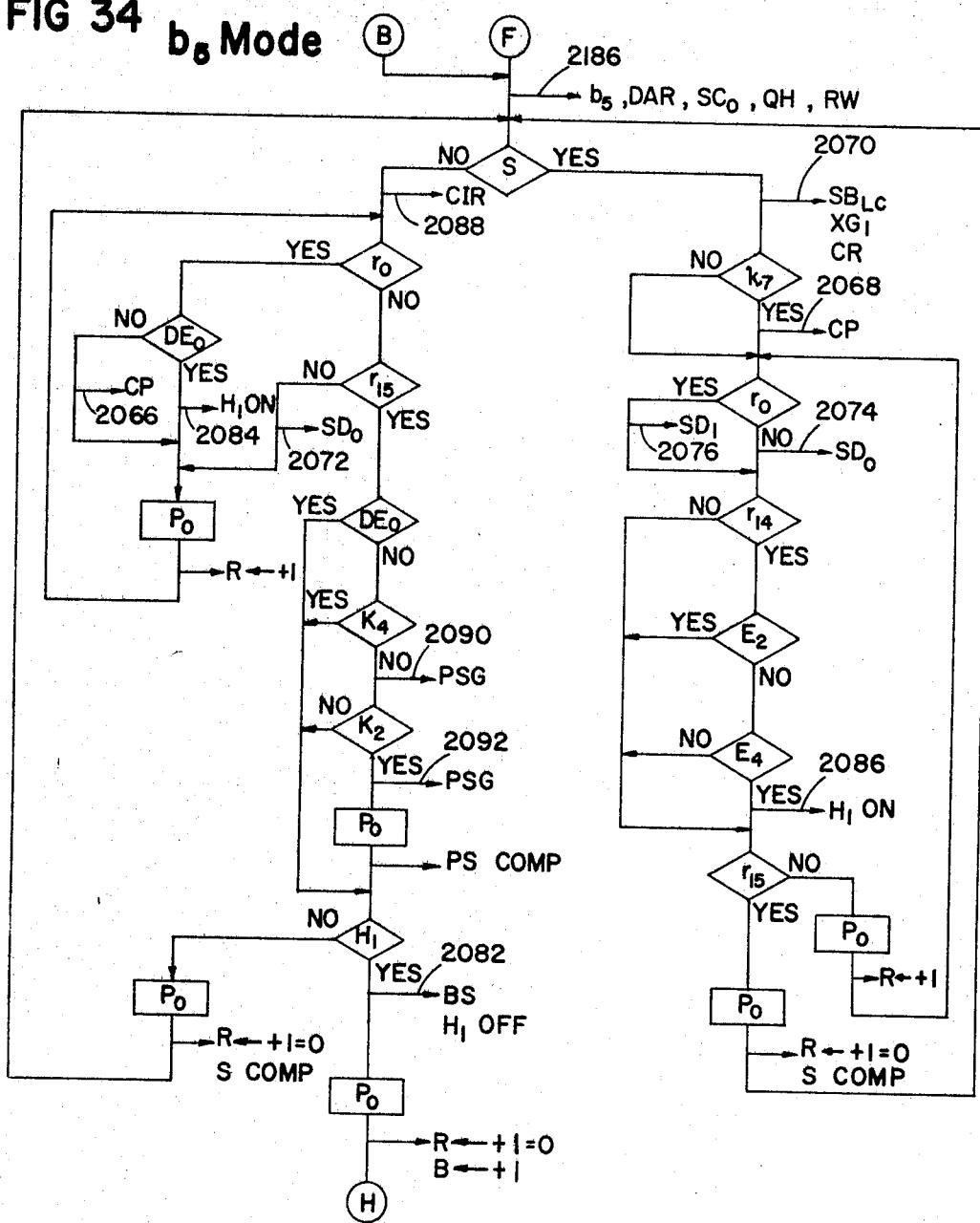

FIG 34  $b_5$  Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 36

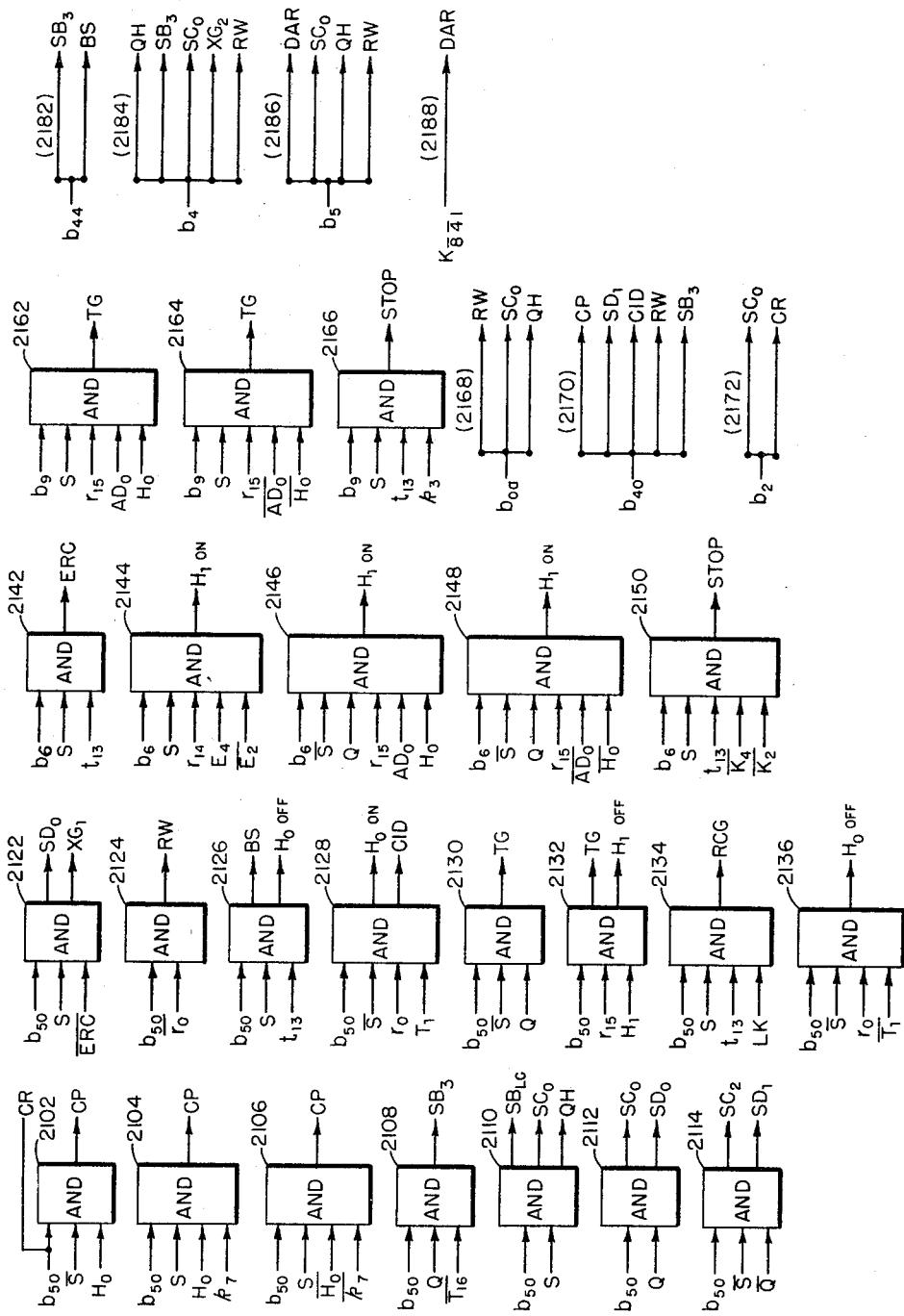

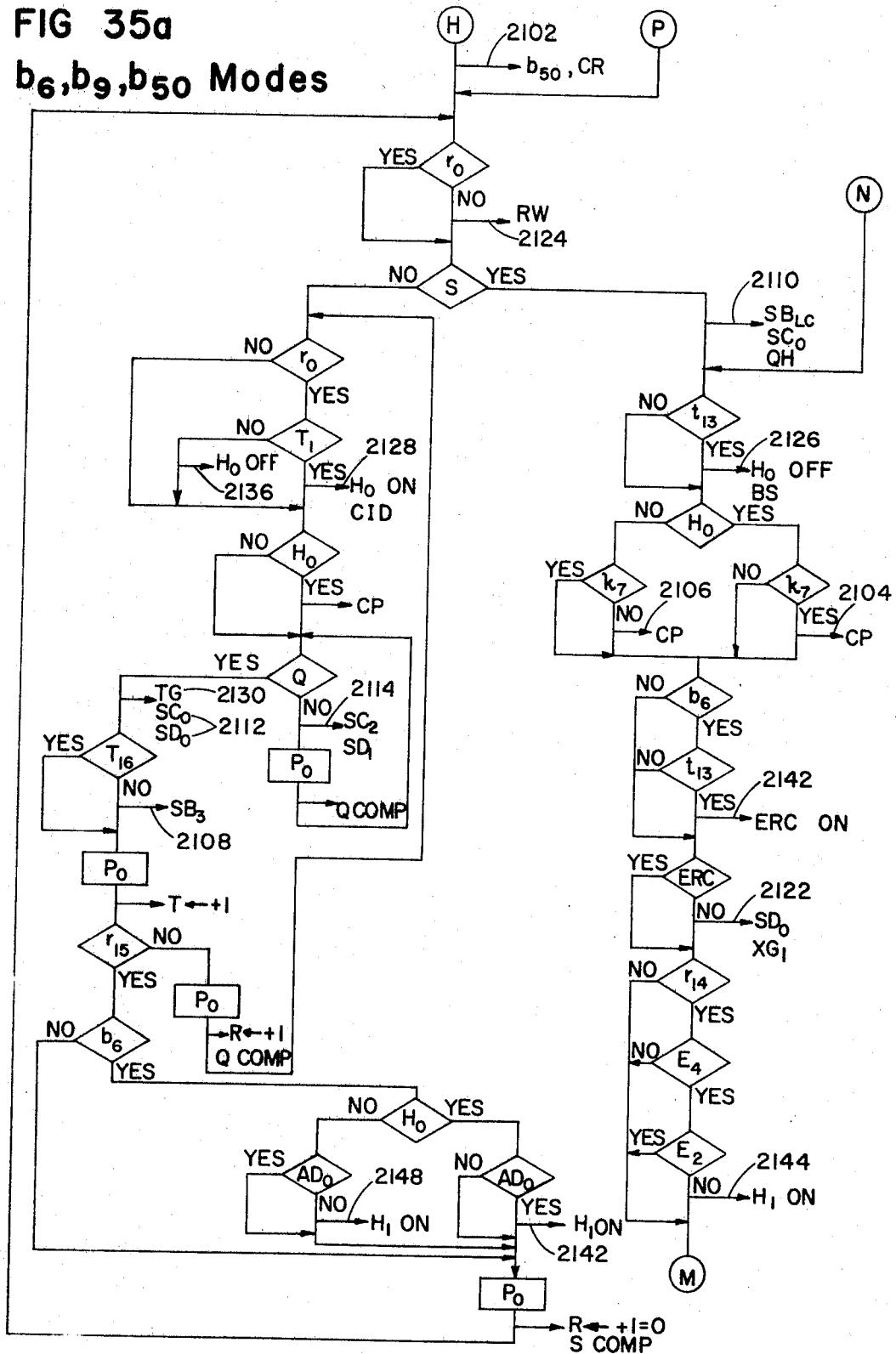

FIG 35a

$b_6, b_9, b_{50}$  Modes

April 28, 1970

AN WANG ET AL.

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 37

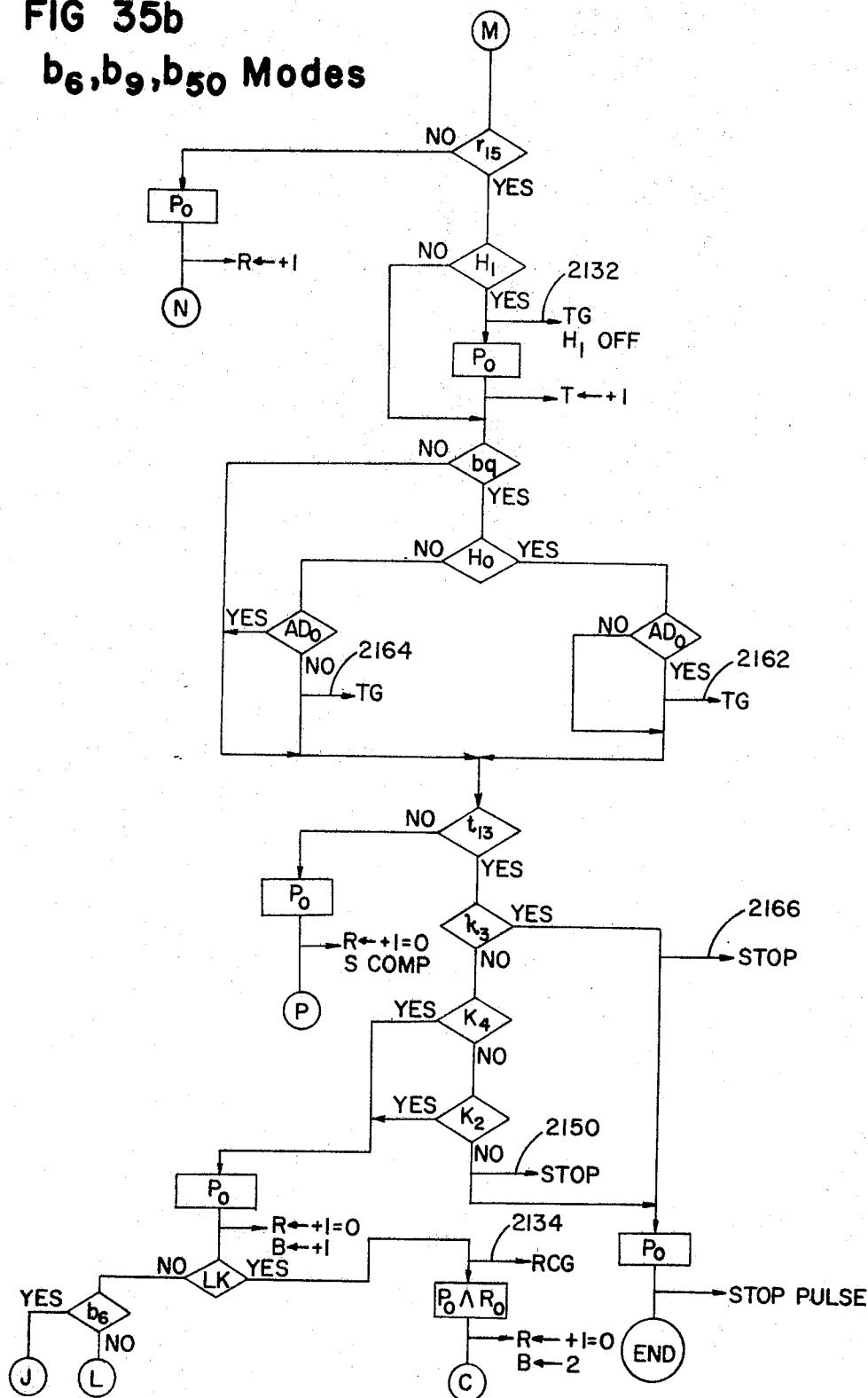

FIG 35b

$b_6, b_9, b_{50}$  Modes

April 28, 1970

AN WANG ET AL

**3,509,329**

## CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 38

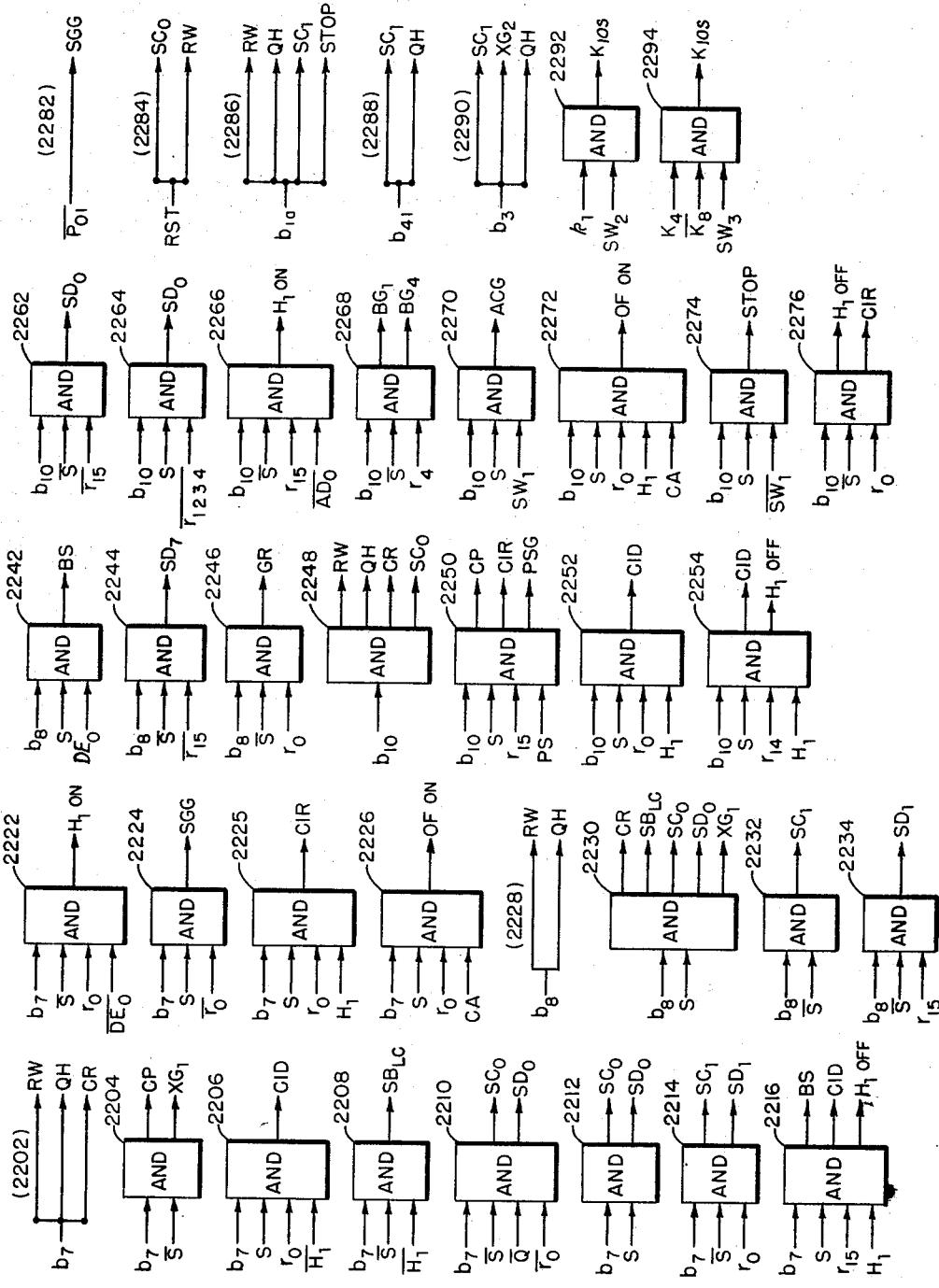

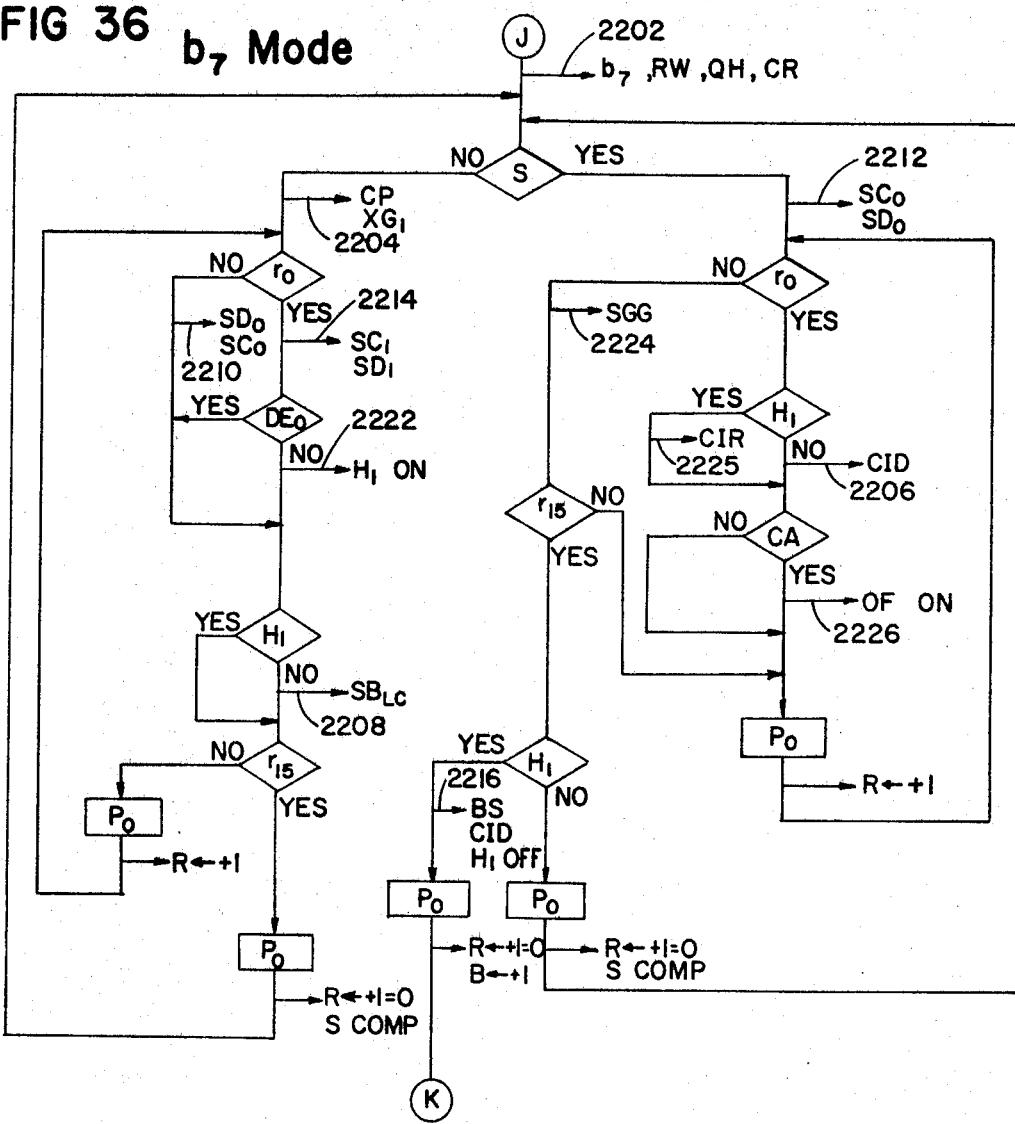

FIG 36 b<sub>7</sub> Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 39

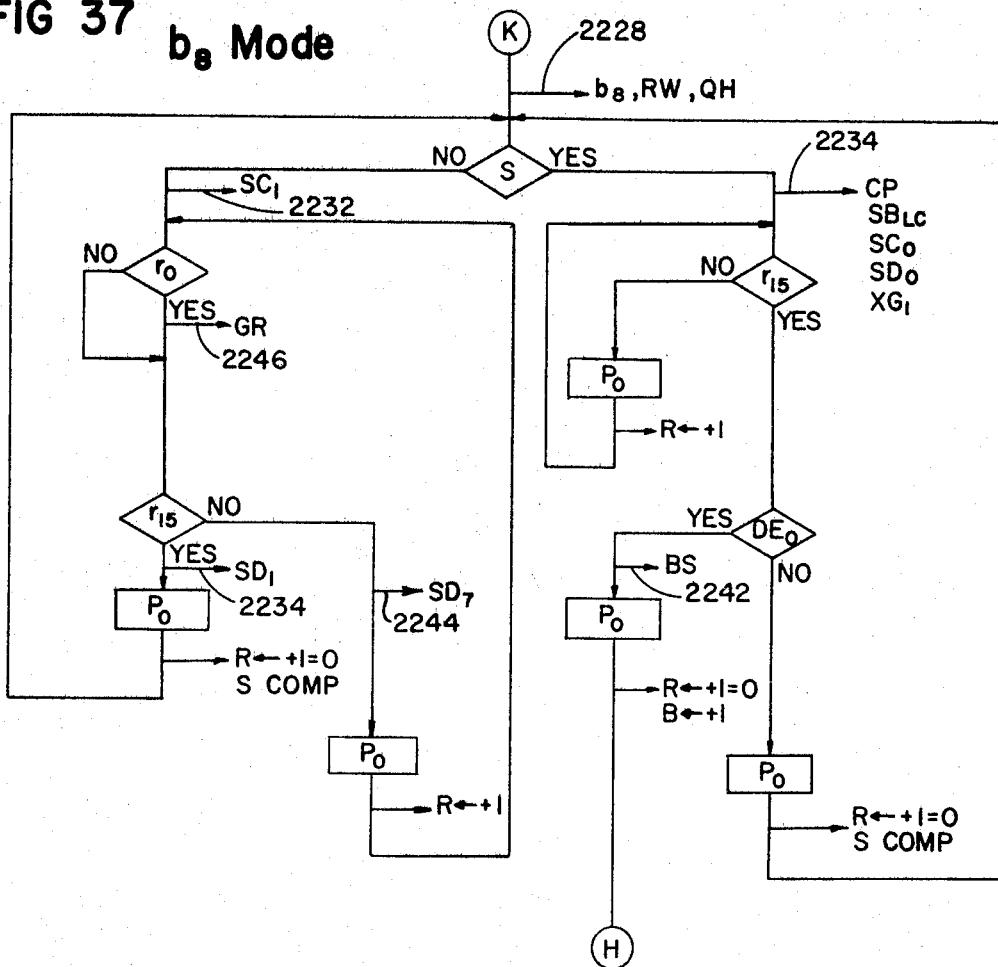

FIG 37  $b_8$  Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 40

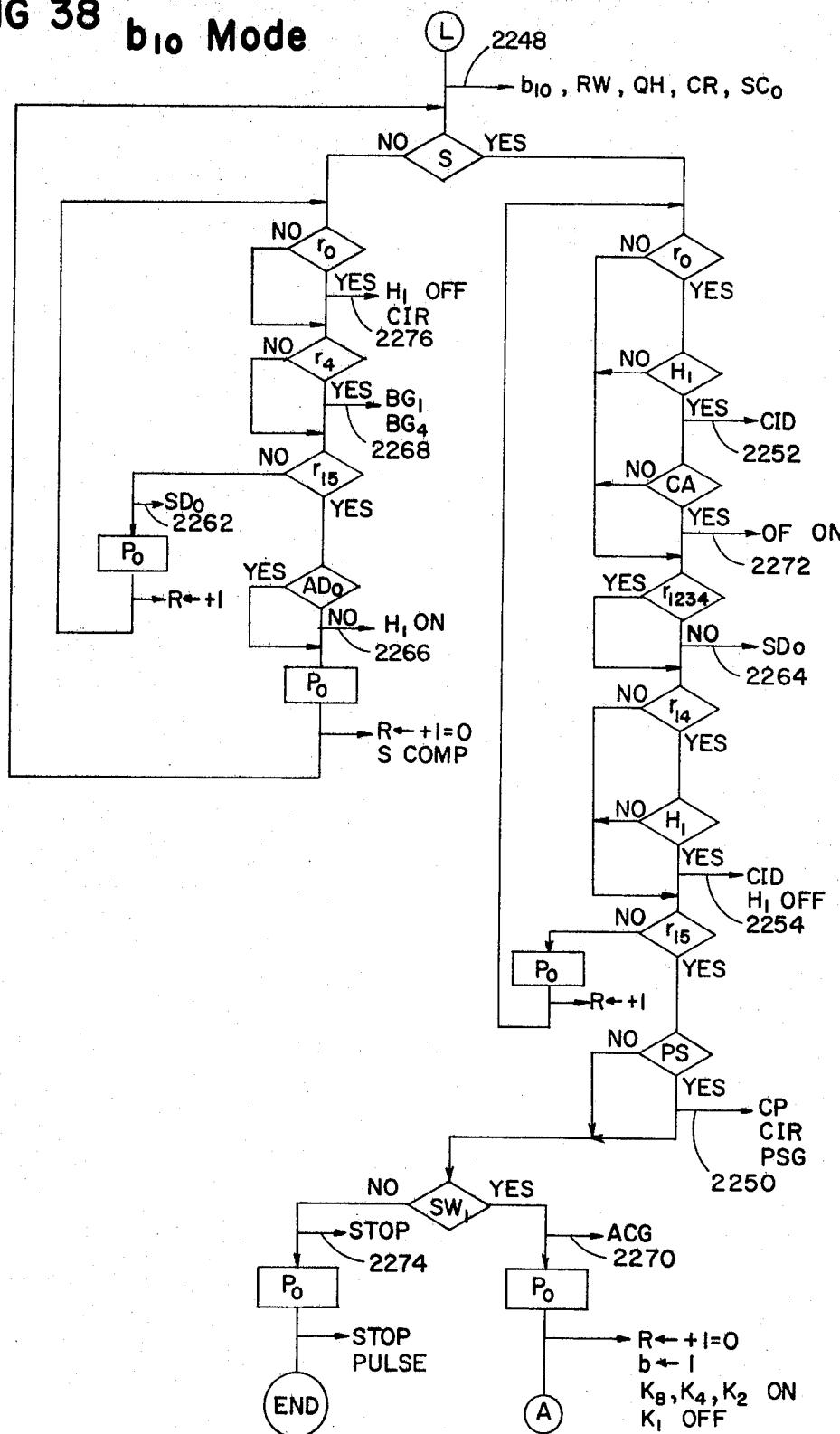

FIG 38 b<sub>10</sub> Mode

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 41

**FIG 39**

**FIG 40**

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 42

**FIG 41**  $e^x$

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 43

**FIG 43**

ENTRY ACCUMULATOR

ENTER-K<sub>1</sub>; ENTRY ACCUMULATOR

SWITCH ON

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 44

**FIG 44**

MULTIPLIER ACCUMULATION

$X = K_2, K_4$

MULT. ACCUMULATOR SWITCH ON

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 45

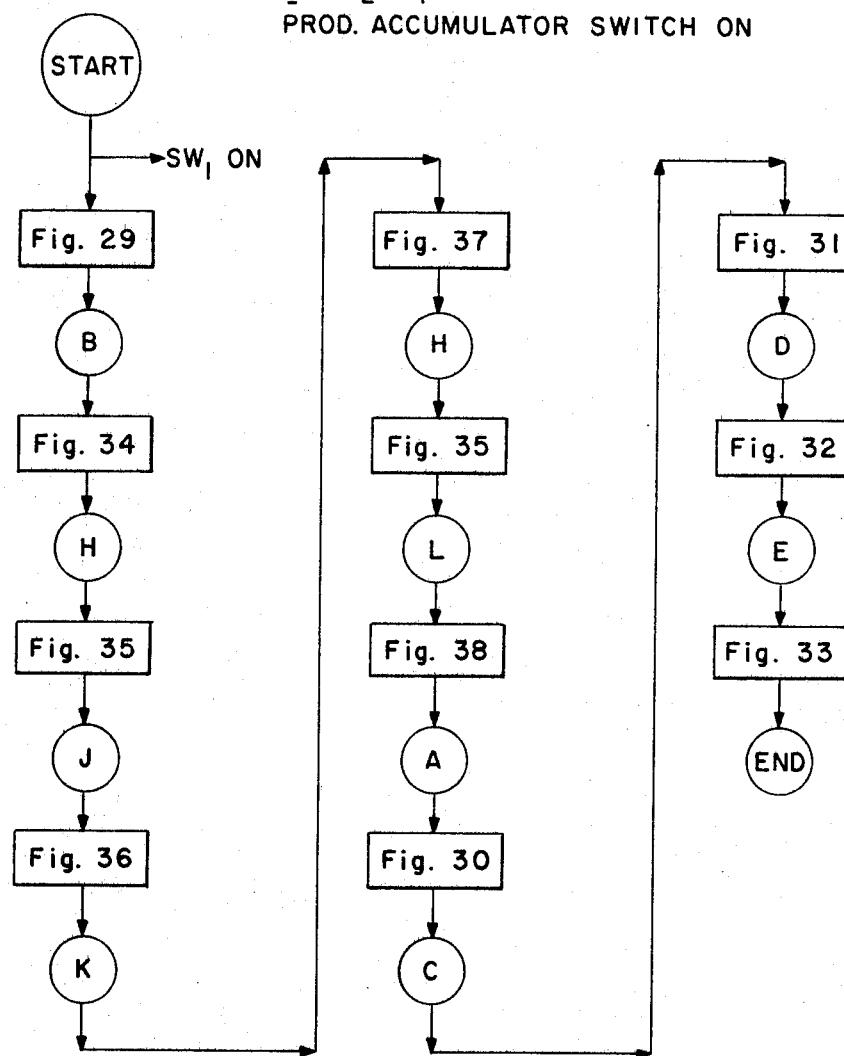

## FIG 45

### PRODUCT ACCUMULATION

$X = K_2, K_4$

PROD. ACCUMULATOR SWITCH ON

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 46

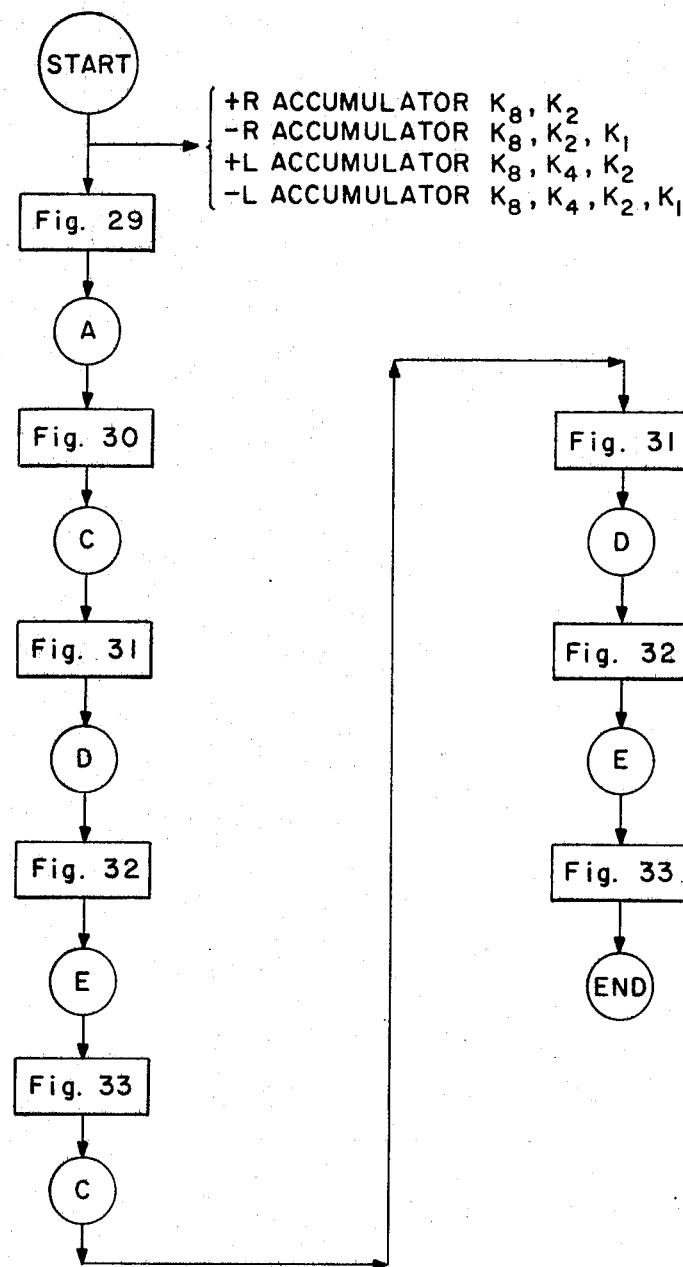

## FIG 46

### ADD AND SUBTRACT

April 28, 1970

AN WANG ET AL

3,509,329

CALCULATOR

Filed Oct. 24, 1966

47 Sheets-Sheet 47

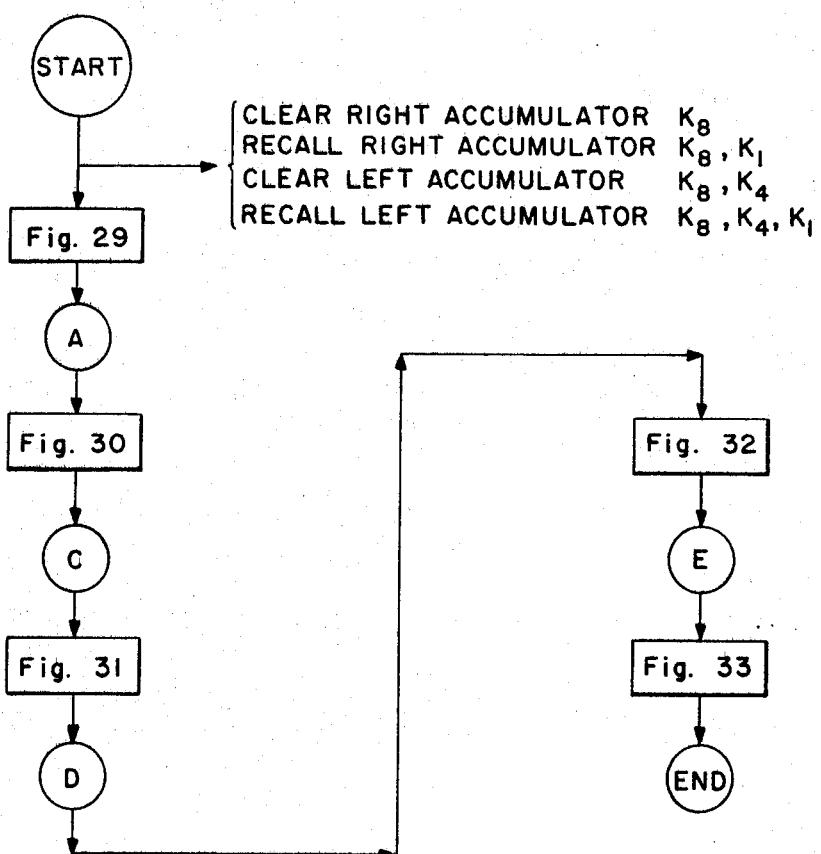

**FIG 47**

CLEAR AND RECALL

**1****3,509,329**

**CALCULATOR**

An Wang, Lincoln, Mass., and Prentice Irving Robinson, Hudson, N.H., assignors to Wang Laboratories, Inc., Tewksbury, Mass., a corporation of Massachusetts

Filed Oct. 24, 1966, Ser. No. 588,863

Int. Cl. G06f 15/02

U.S. Cl. 235—156

37 Claims

**ABSTRACT OF THE DISCLOSURE**

An electronic calculator includes two independently controllable accumulators permitting simultaneous accumulation of products or quotients from successive multiplications or divisions in one accumulator and accumulation of operands in the other accumulator. A store of logarithmic constant values is utilized to permit single-keystroke generation of logarithms and antilogarithms.

This invention relates to calculating apparatus of the type which do not employ large data storage capabilities.

Current commercial and scientific procedures demand that increasingly large masses of data be processed, and such processing frequently involves or is an integral part of mathematical analyses. Such mathematical analyses encompass in addition to addition, subtraction, multiplication, and division even more complex manipulations, e.g. those employing exponential values. While digital computers of conventional logic organization can perform such manipulations the techniques that are employed frequently involve complex, circuitous and time-consuming operations to obtain the desired results or solutions to specific problems.

The calculator provides the basic logic arrangement for performing mathematical manipulations. It is an object of this invention to provide novel and improved arrangements for controlling a calculator. Another object of the invention is to provide novel and improved arrangements enabling logarithmic manipulations to be performed in a calculator logic organization.

Still another object of the invention is to provide novel and improved calculator control arrangements that are compact, relatively inexpensive, and which can be maintained with relative ease.

Another object of the invention is to provide a novel and improved calculator organization capable of accumulating, on a selective basis, the results of a plurality of a series of data manipulations.

Still another object of the invention is to provide novel and improved data entry control arrangements for use in electronic calculators.

A further object of the invention is to provide novel and improved calculator logic organizations which enables the efficient and rapid performance of a wide variety of data manipulations.

Another object of the invention is to provide novel and improved data entry and decimal point control arrangements.

A further object of the invention is to provide simplified control logic arrangements in a calculator which increase the number and power of subordinate logic operations without increasing the amount of hardware necessary to perform those logic operations.

In accordance with the invention there is provided a calculator having an arithmetic unit that includes added circuitry for performing basic data manipulation operations such as addition and subtraction. In the preferred embodiment disclosed herein, the calculator further includes a log register which is coupled through accumulating logic to

**2**

a store of log constants. The preferred embodiment also includes a display or work register, two accumulator registers, and logic which permits duplex accumulation of the results of a series of mathematical manipulations performed by the calculator. Data entry to the work register is provided through a manually operable keyboard.

The control logic provided in this calculator includes a first control register settable to a plurality of states, a first state responsive to data entry signals and controlling the entry of data into the calculator; a second state controlling basic arithmetic manipulations; and further states controlling other data manipulations performed by the calculator. A subsidiary control register, operable in conjunction with data entry signals and signals indicative of the state of the first control register controls, among other things, the entry of data into the calculator from the keyboard. A subsidiary feature of the invention, relating to data entry, is the circuitry controlling the entry of a decimal point in a register. The calculator control, in response to the first data digit stored in the register places unique indications in the subsequent stages of the register and in response to the next entered signal, serially senses the stages of the register and enters the appropriate indication in the first stage that is sensed to store the unique "no data" indication. Other subsidiary control elements are utilized in conjunction with the first control register outputs, to control the alignment of decimal points, the basic arithmetic operations of addition or subtraction, more complex mathematical manipulations involving the generation of logarithms and/or antilogarithms, the selection of one of the two accumulator registers for accumulation of the results of series of mathematical operations; and the display of the results of the many operations of which the calculator is capable. The outputs of the control registers and control signals are applied through comprehensive logic arrangements, which in the preferred embodiment, are diode AND circuit logic arranged on five removable cards which facilitate maintenance of the calculator, to combine and channel control signals necessary for the operation of the calculator.

The calculator constructed in accordance with the invention is a compact, easy to operate and versatile device, featuring coordinated control logic arrangements.

Other objects, features and advantages of the invention will be seen as the following description of a particular embodiment progresses in conjunction with the drawings, in which:

FIG. 1 is a pictorial view of the calculator of the invention;

FIG. 2 is a diagrammatic view of the keyboard console operation controls and display and of the four magnetic core registers comprised by the calculator's memory unit;

FIG. 3 is an overall block diagram of the system logic of the calculator;

FIG. 4 is a block diagram of the calculator's Memory Unit with its associated input and output circuitry;

FIG. 5 is a block diagram of the data-input logic of the calculator which controls the input data that is written into the Memory Unit;

FIG. 6 is a diagrammatic view of the Memory Unit core plane;

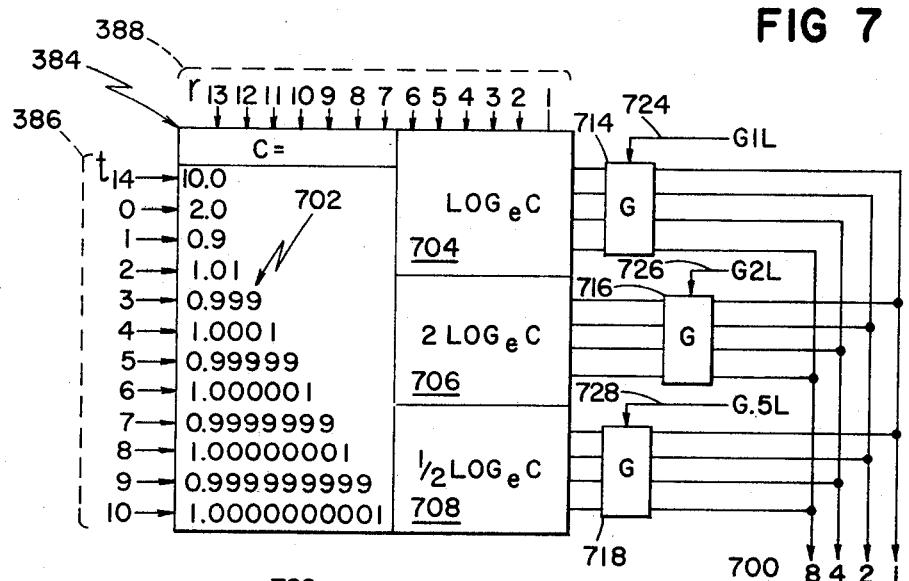

FIG. 7 is a diagrammatic view of the log generator employed in the calculator;

FIG. 8 is a block diagram of two of the component logic networks comprised by the log generator;

FIG. 9 shows the logic network used to generate the log generator control signals;

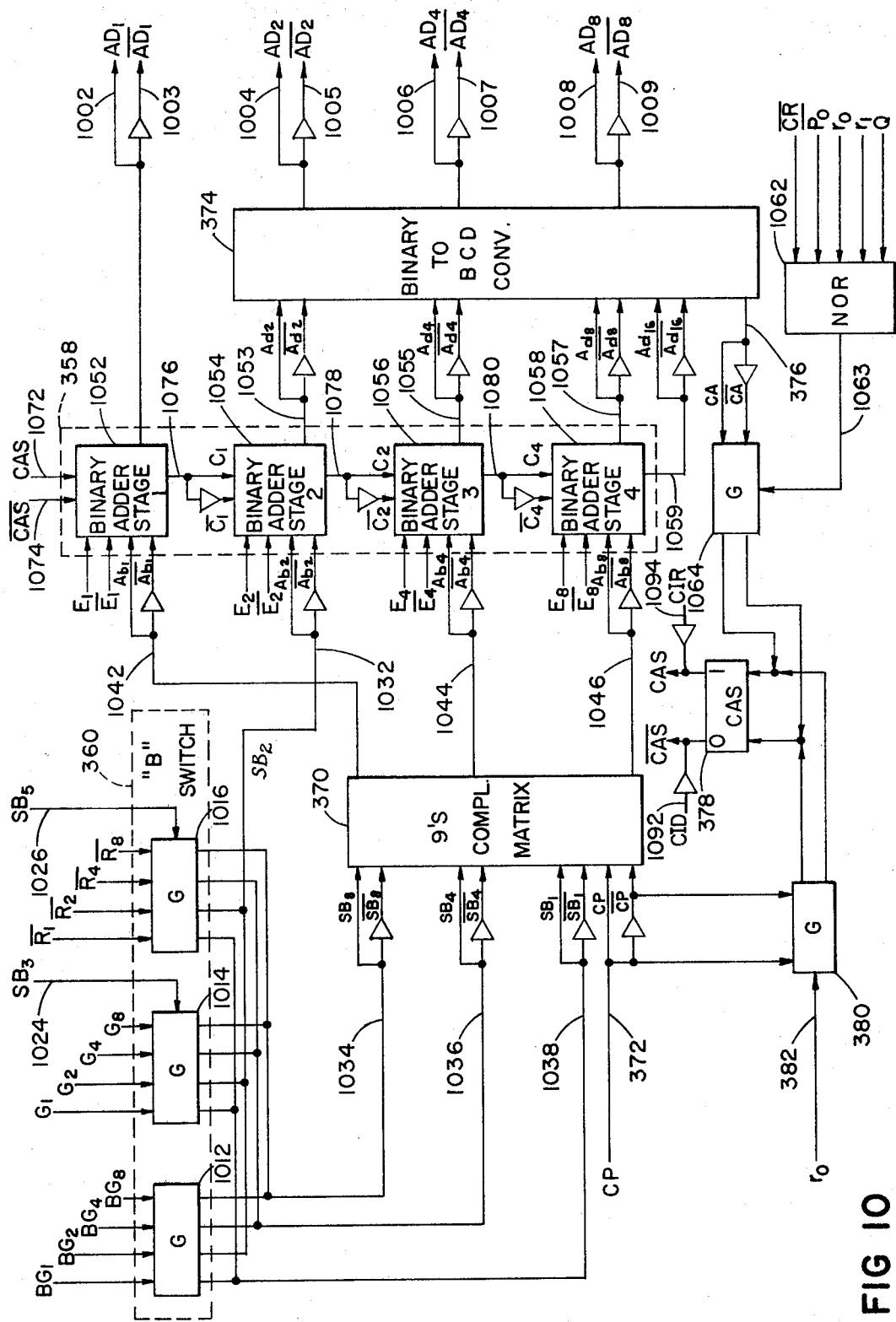

FIG. 10 is a block diagram of the calculator's Arithmetic Unit;

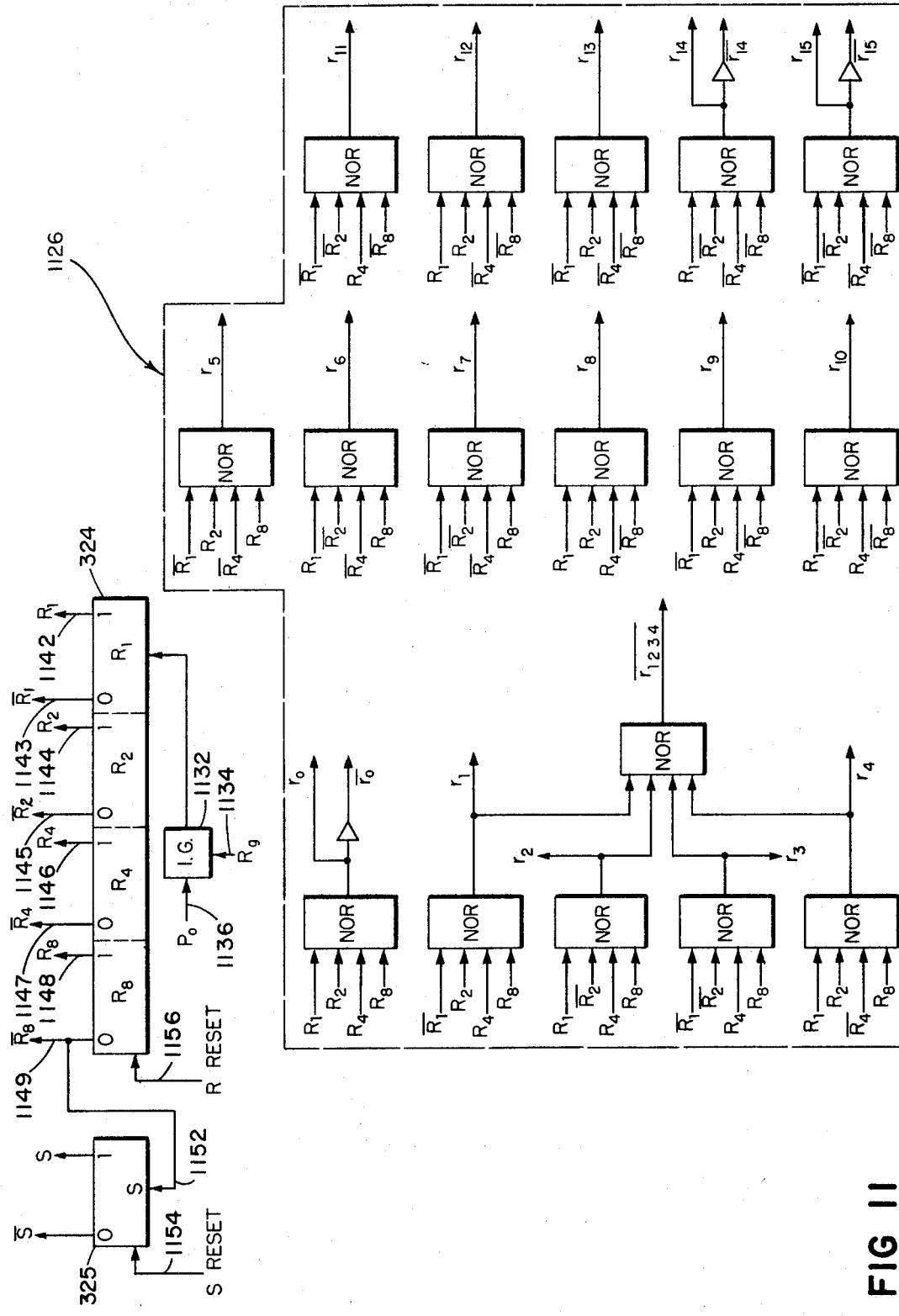

FIG. 11 is a block diagram of the sub-cycle control counter R, the S flip-flop, and the associated decoders employed in the calculator;

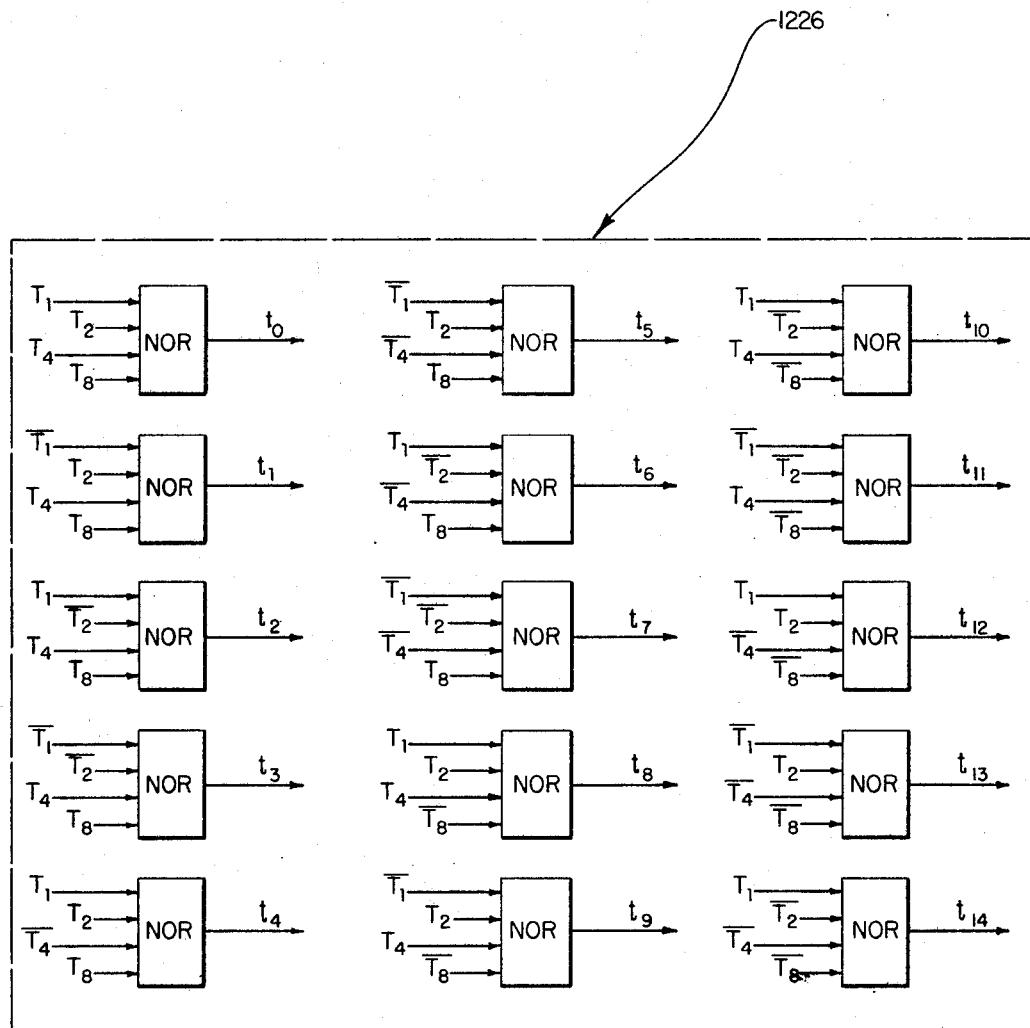

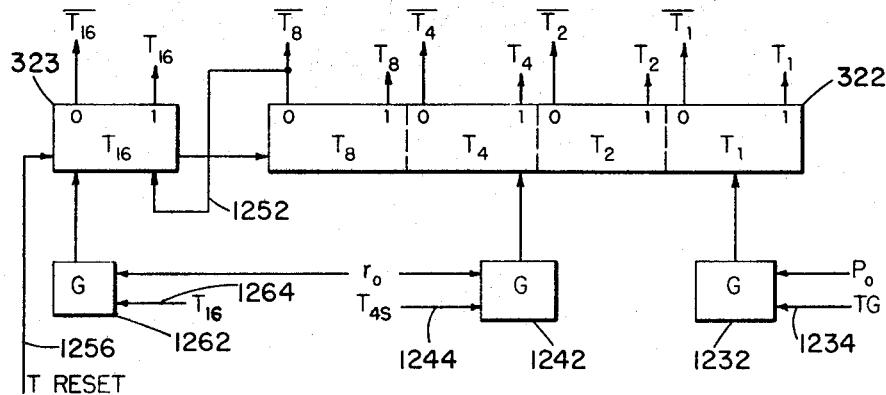

FIG. 12 is a block diagram of the sub-cycle control counter T, the  $T_{16}$  flip-flop, and the associated decoders employed in the calculator;

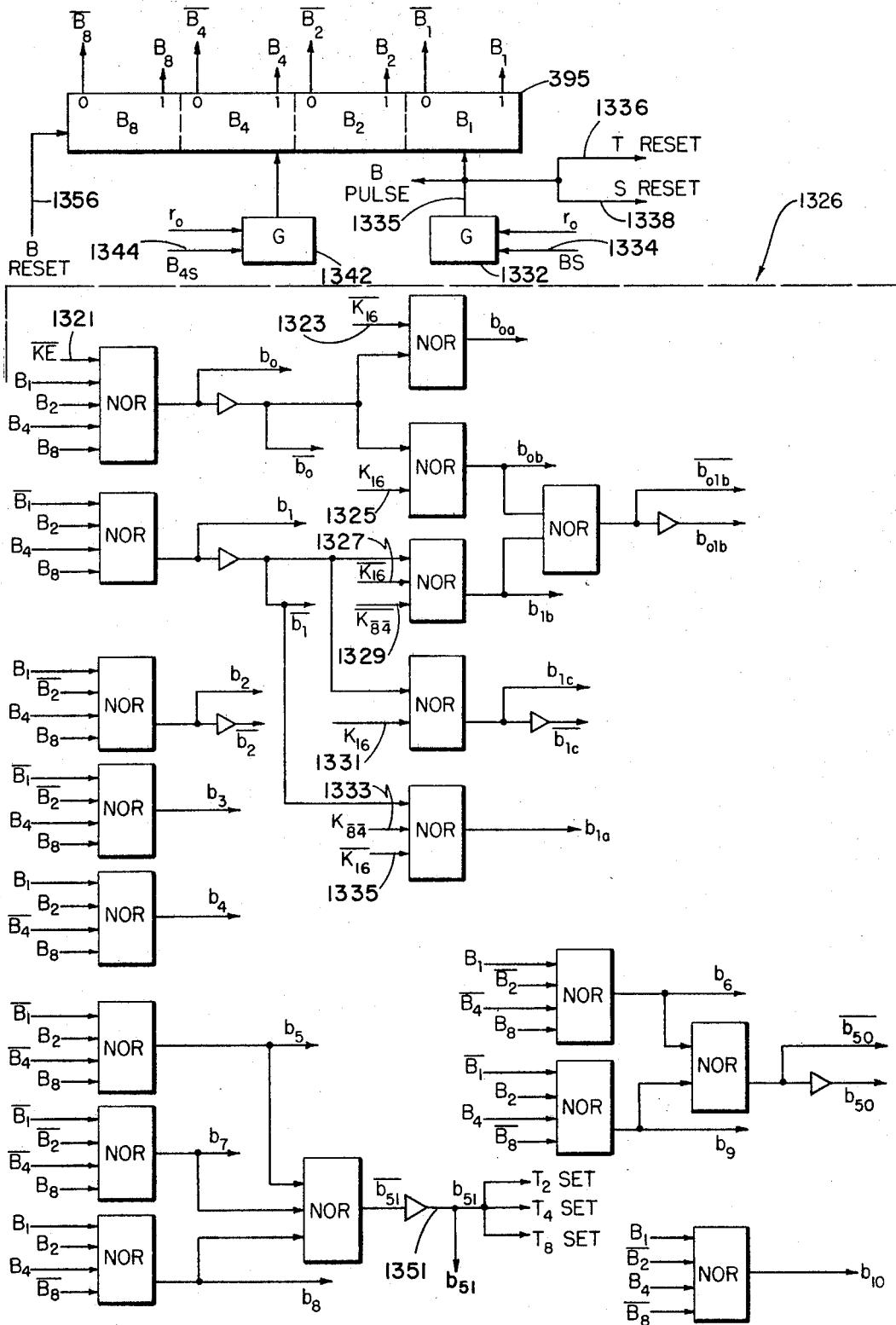

FIG. 13 is a block diagram of the cycle control counter B, and the associated decoders employed in the calculator;

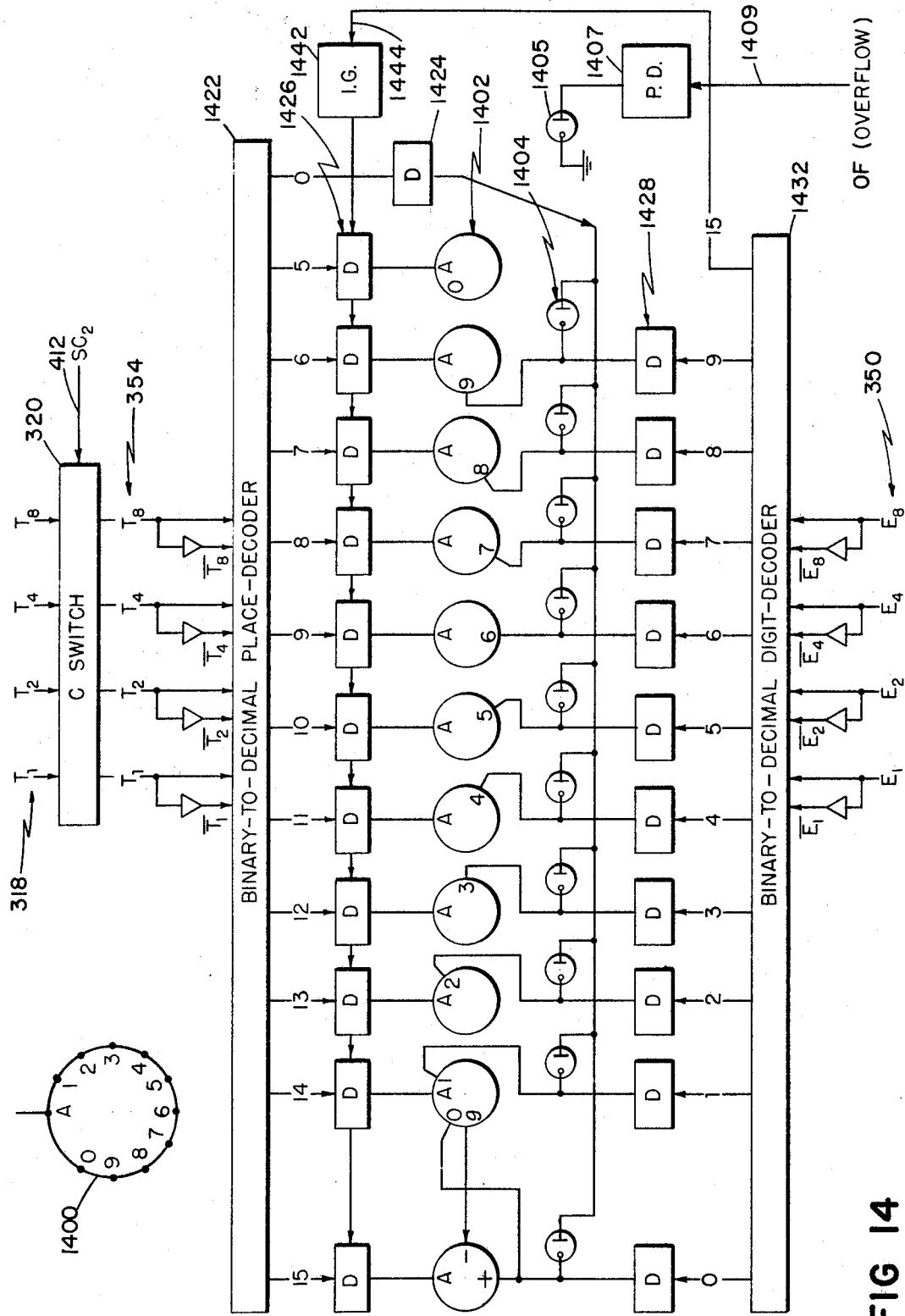

FIG. 14 is a block diagram of the Display Unit.

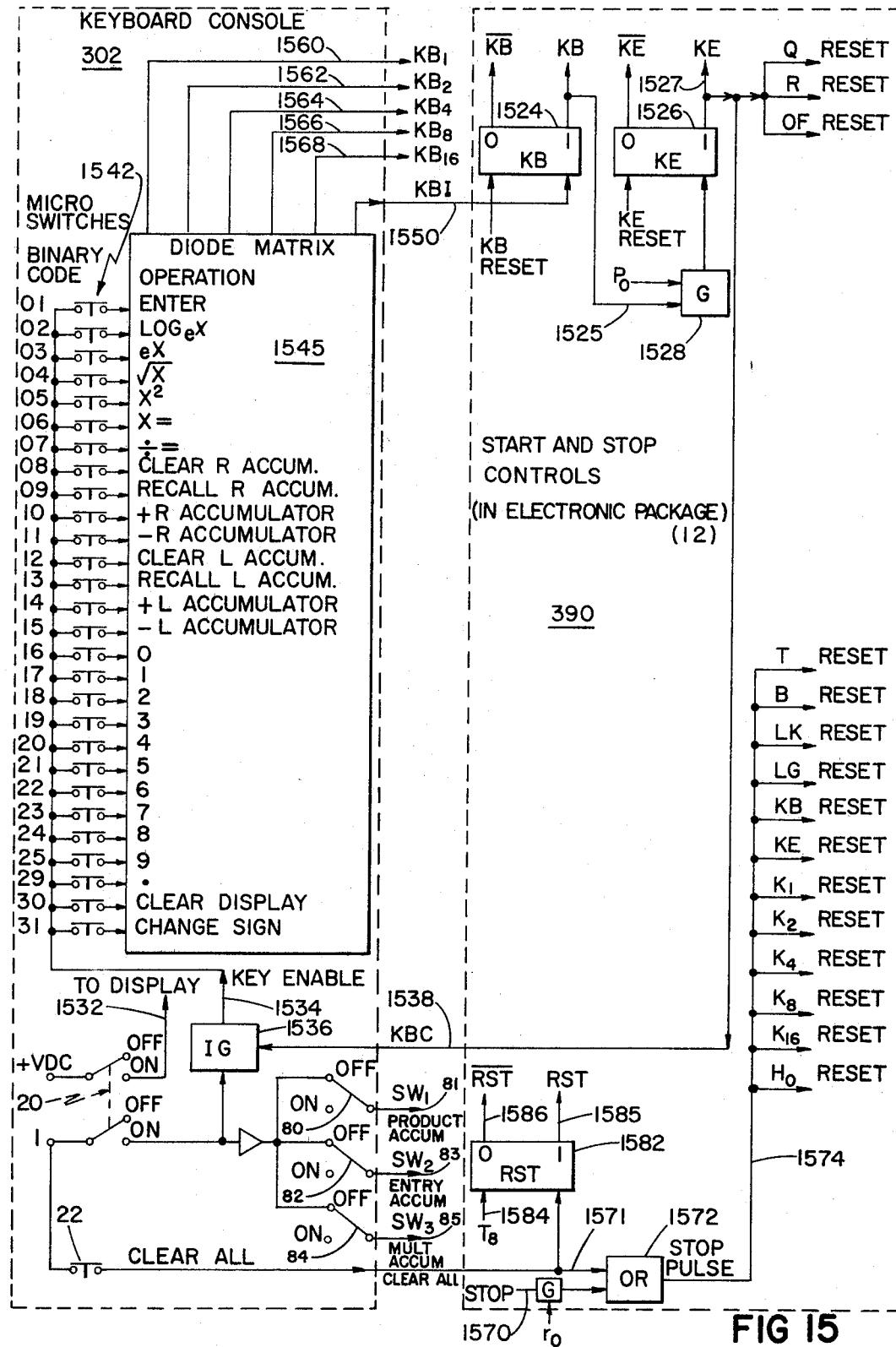

FIG. 15 is a block diagram of the Keyboard Console switching circuits and of the start and stop controls employed in the calculator;

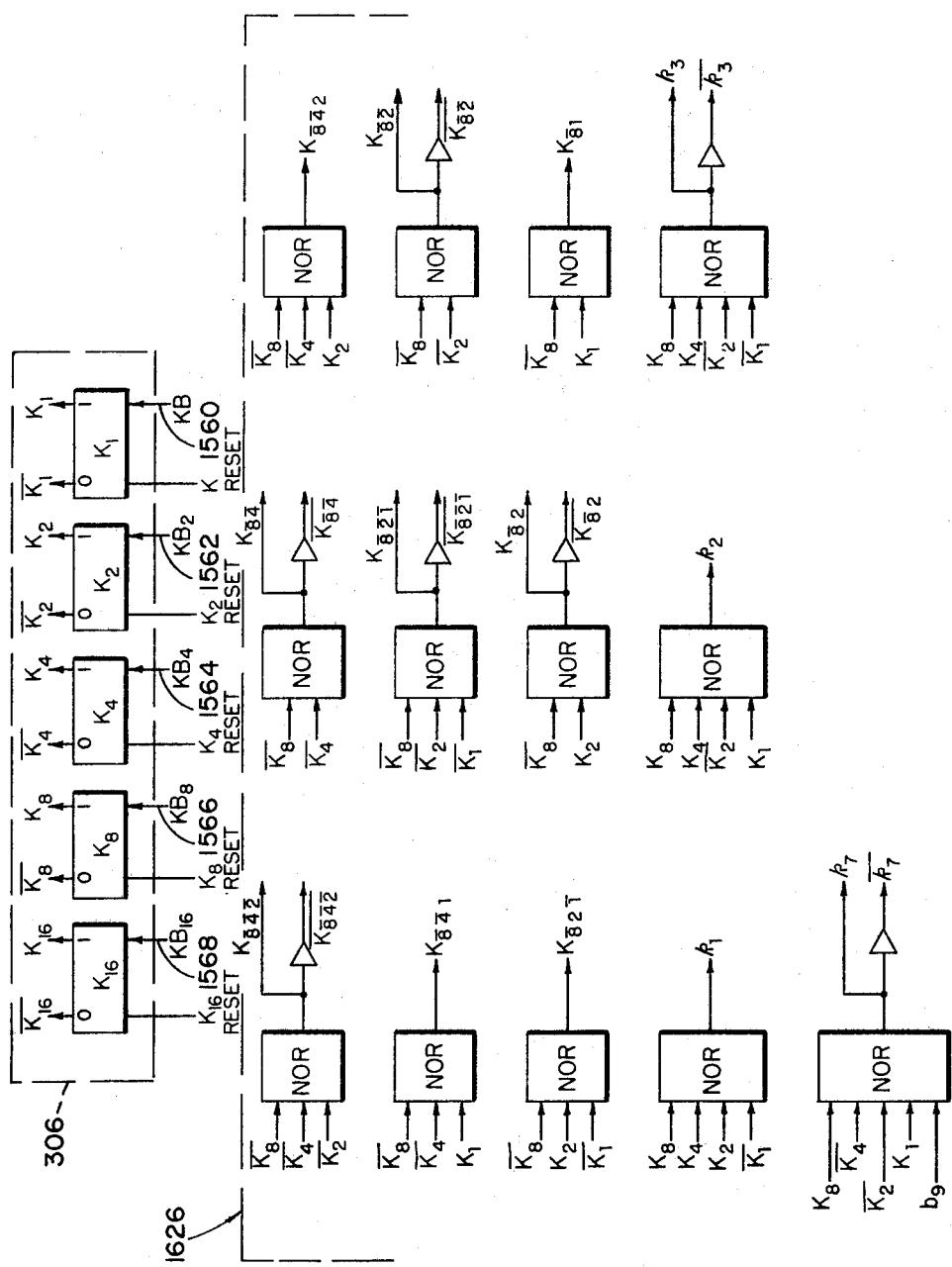

FIG. 16 is a block diagram of the input buffer K register and of the associated decoders employed in the calculator;

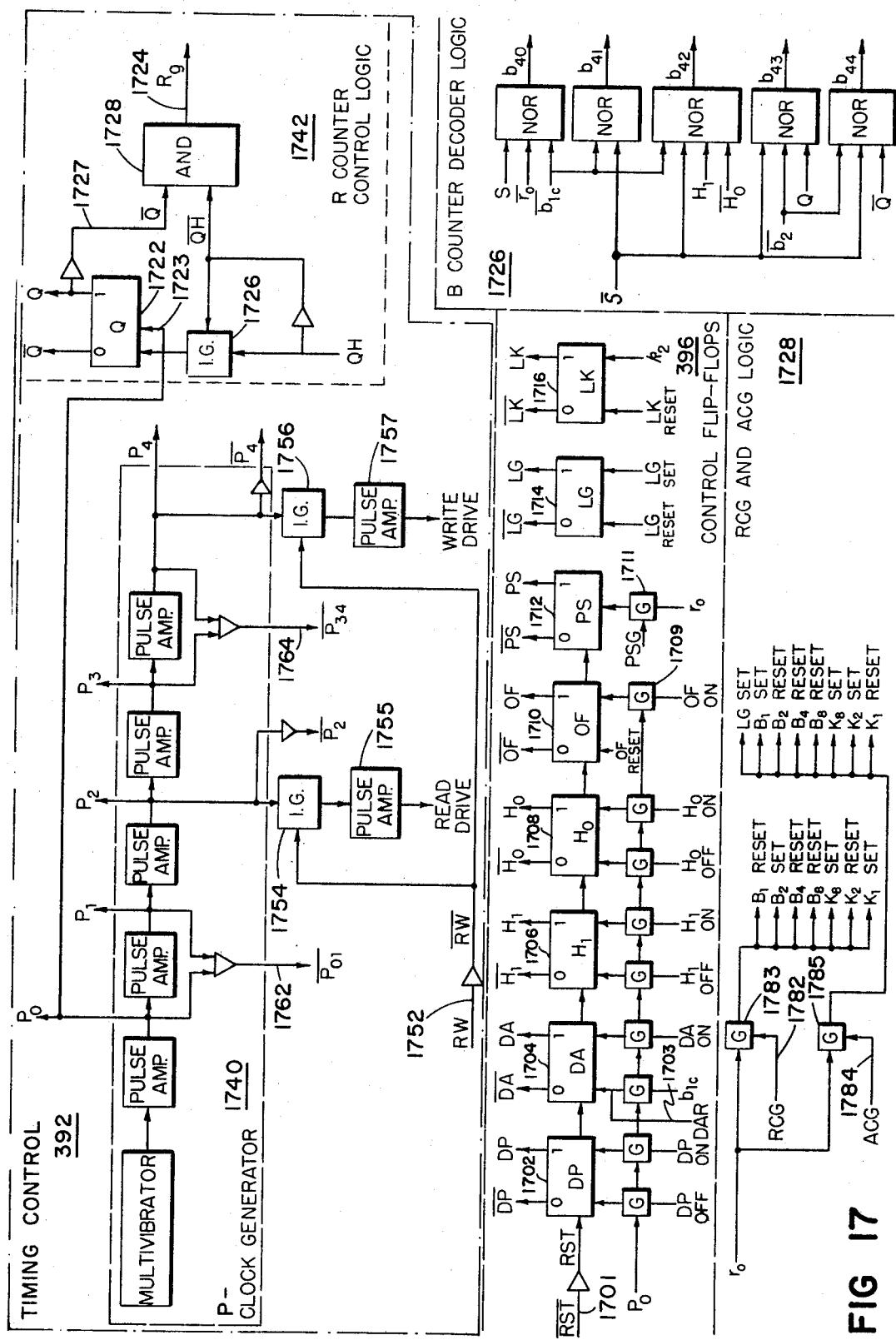

FIG. 17 is a block diagram of several portions of the Control Unit including the timing control, miscellaneous system state control flip-flops, a portion of the B counter decoder logic and the RCG and ACG logic employed in the calculator.

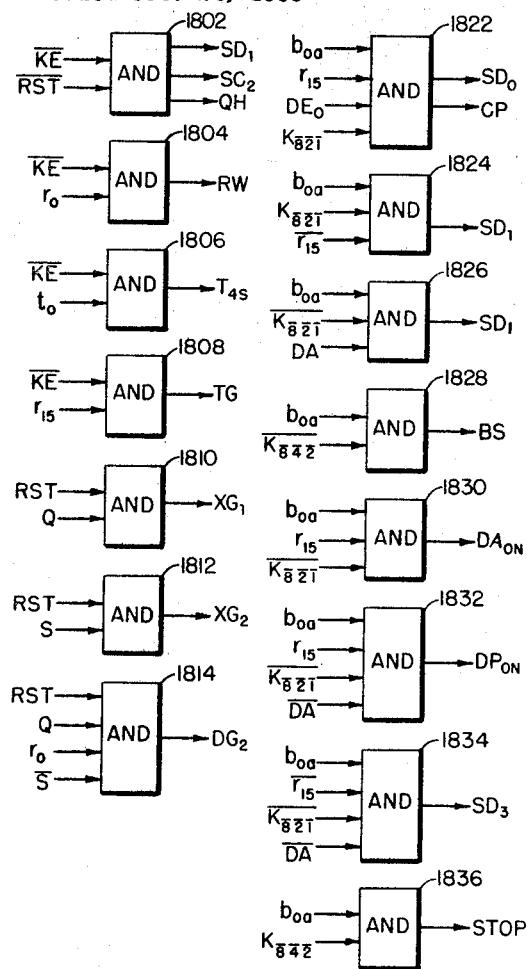

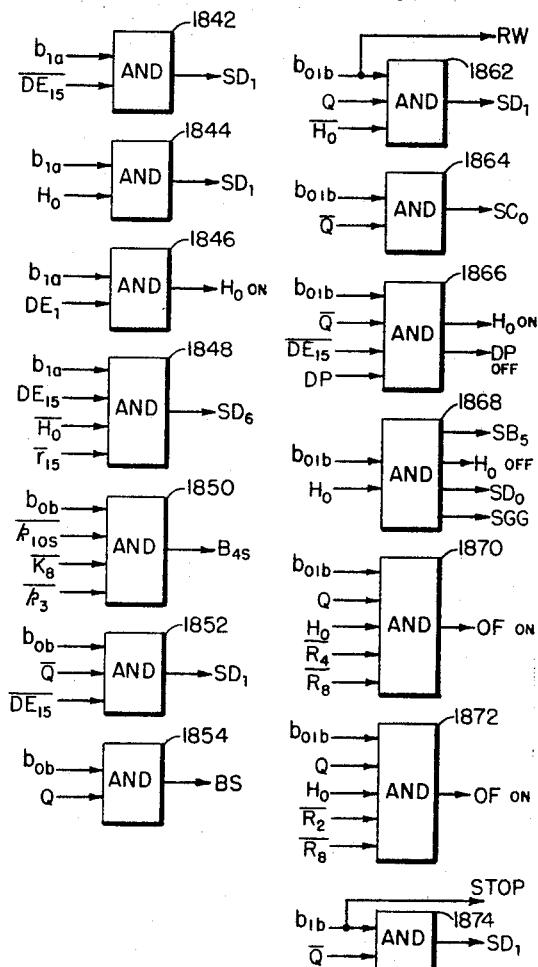

FIGS. 18, 19, 20, 21 and 22 show a plurality of logical ANDs making up the bulk of the calculator control logic which in the preferred embodiment are diode networks;

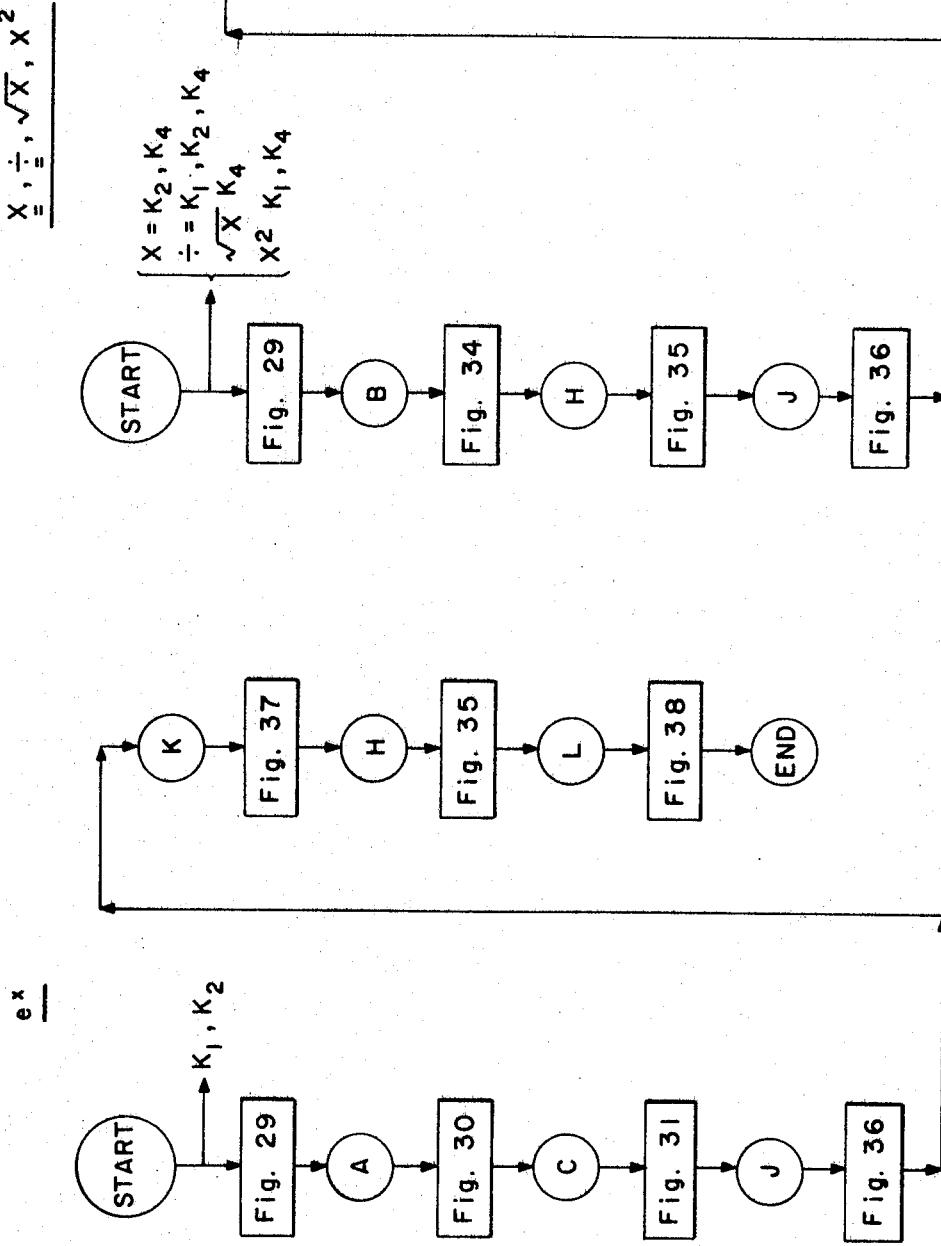

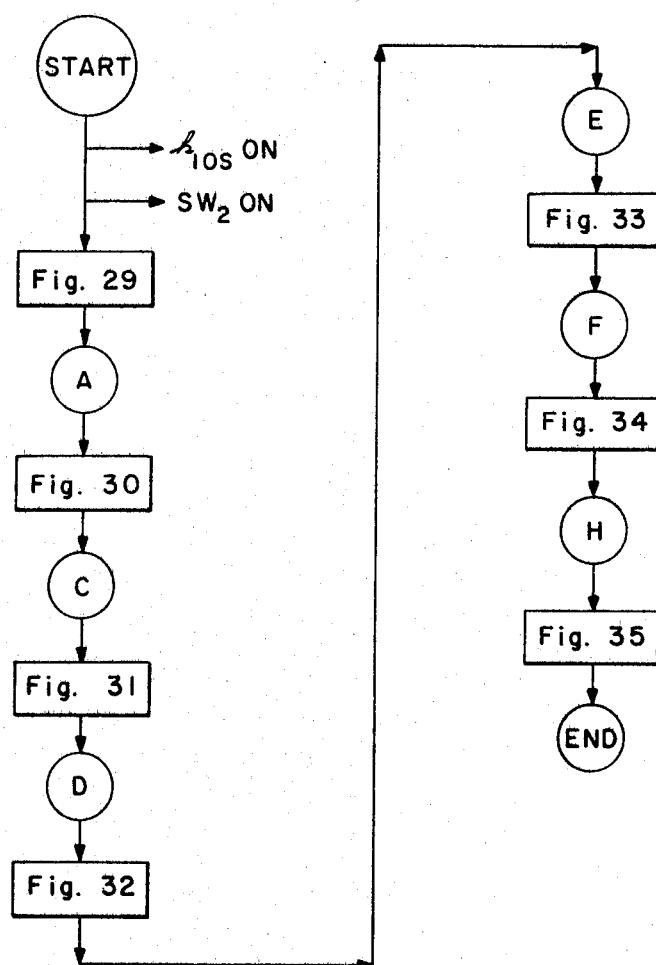

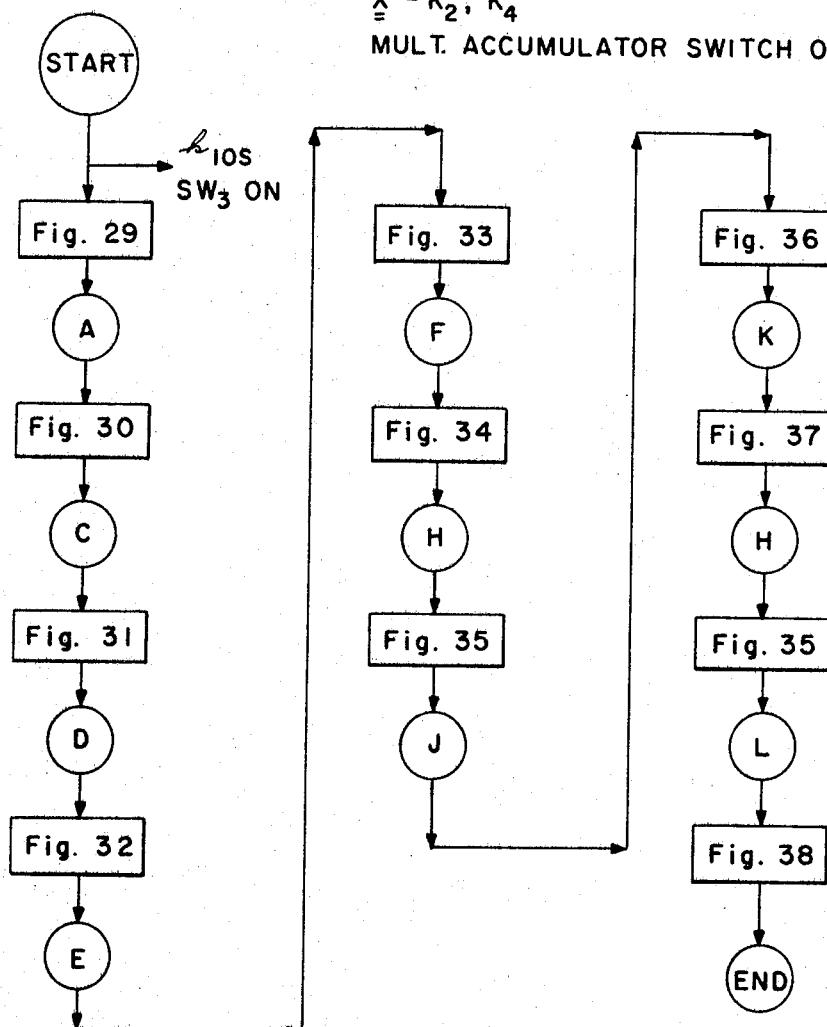

FIGS. 23 through 28 each show flow charts of one of the more simple calculator operations;

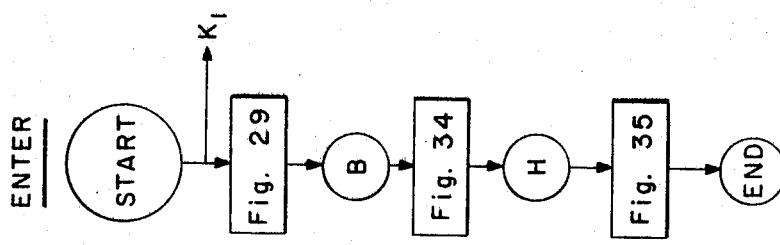

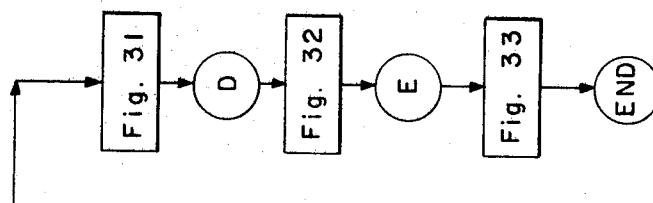

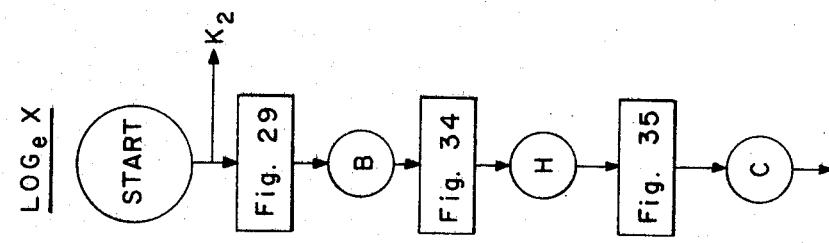

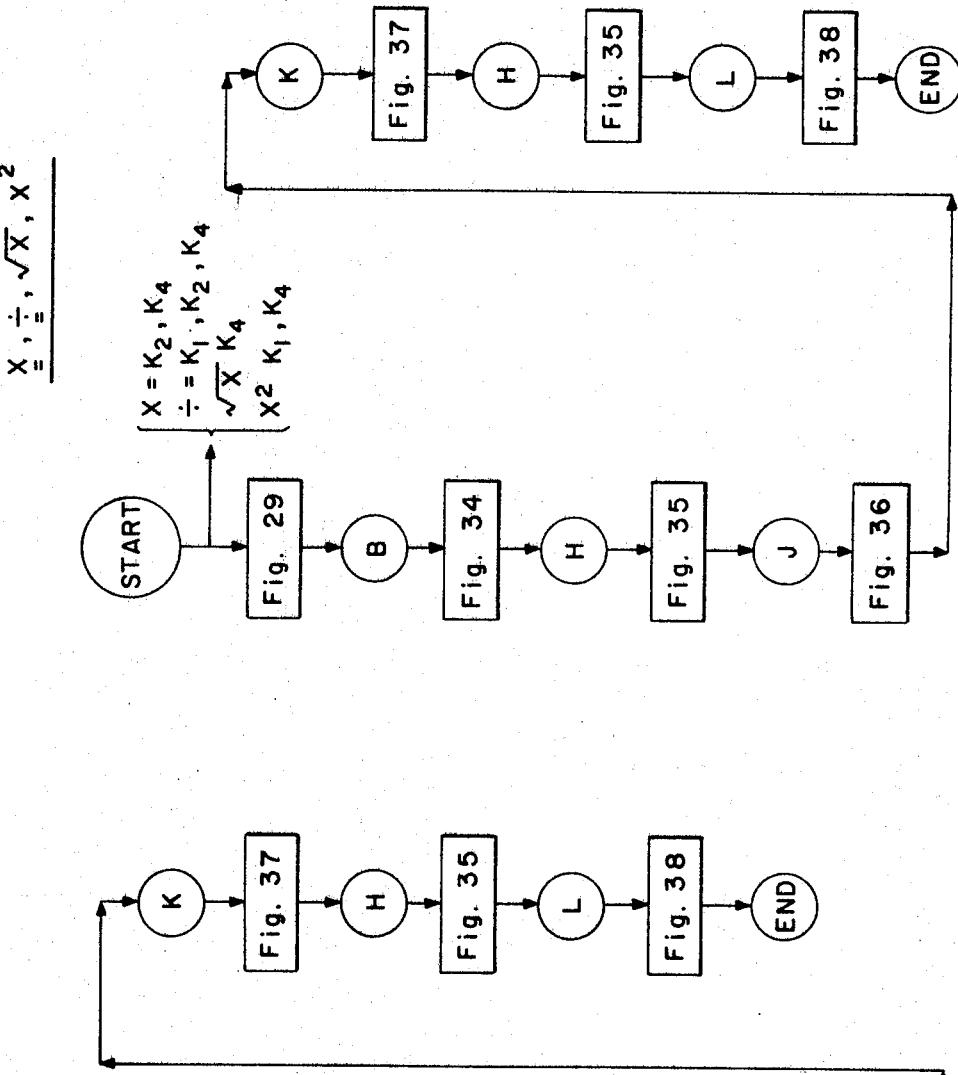

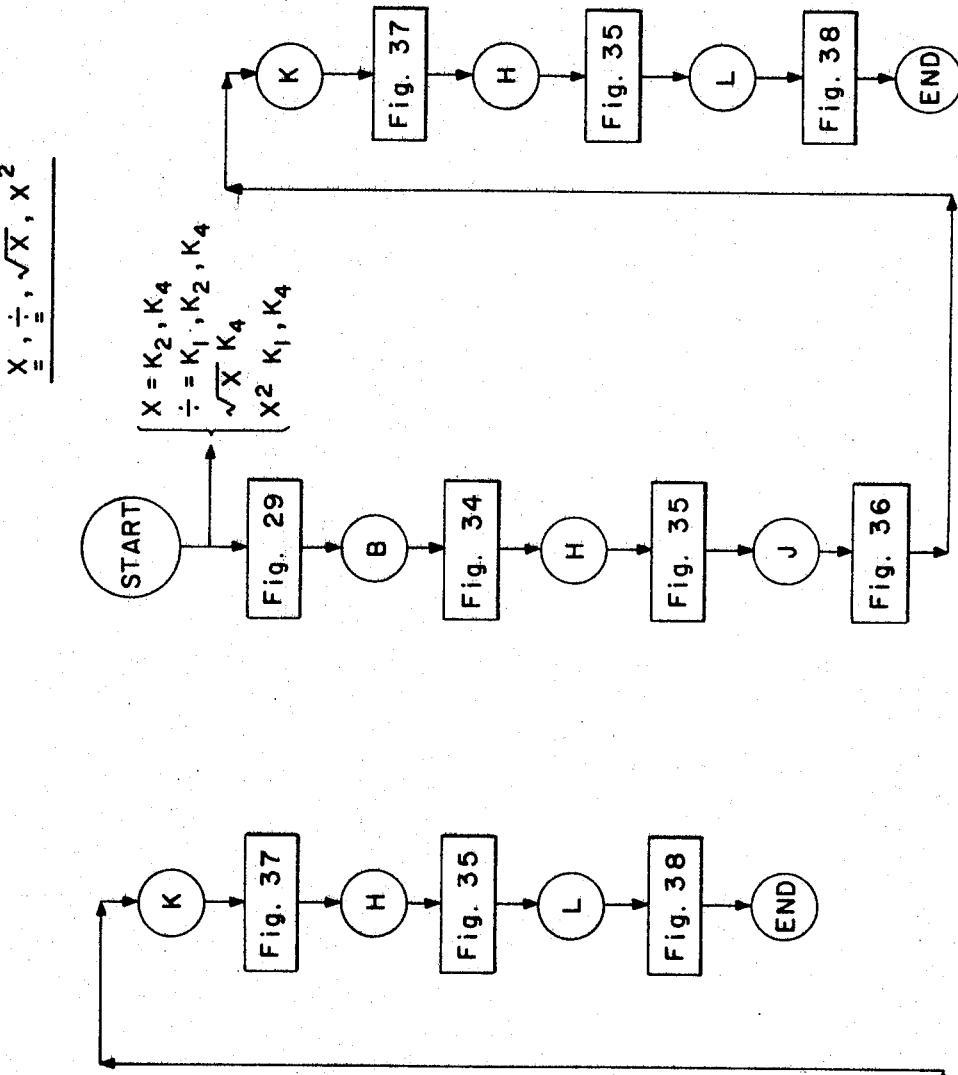

FIGS. 29 through 38 show flow charts of the ten major system cycles of the calculator ("b modes"); and

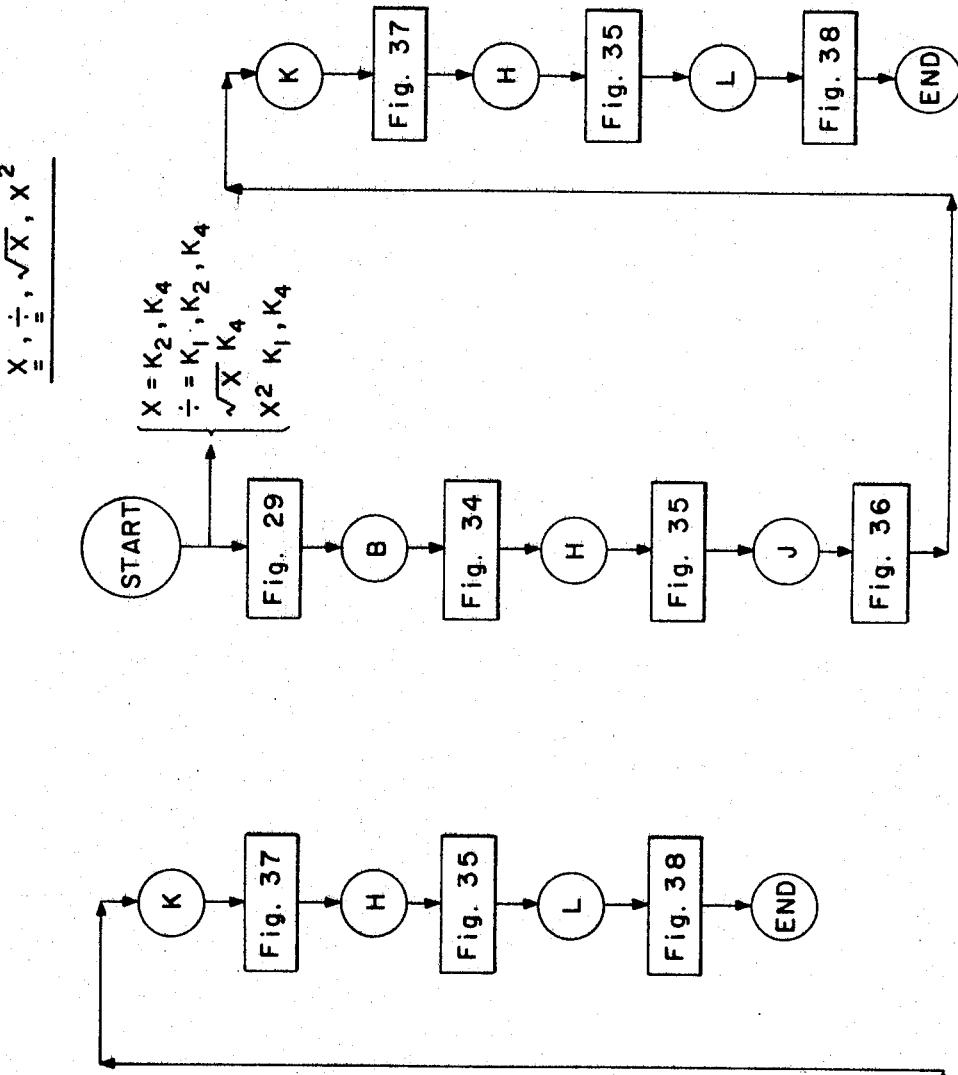

FIGS. 39 through 47 are simple "macro" flow charts showing the manner in which the calculator combines the "b modes" to produce more complex operations of the calculator that are built up from various combinations of these major system cycles.

This invention relates to a compact and relatively inexpensive electronic calculating apparatus capable of performing an unusually wide range of mathematical operations at electronic speeds. As appears in FIG. 1, the calculator consists of two major components, a desk-top keyboard console 11, and an electronics package 12. The electronic package utilizes solid-state circuits on readily replaceable plug-in modules, thus ensuring easy maintenance and quiet operation. The keyboard console is connected to the electronic package by a single compact (1/4" diameter) cable 13. The electronic package may be plugged into a standard, grounded, 115 v. AC wall outlet.

The console weighs less than six pounds and measures approximately 10 1/4" x 8" x 4 1/2". The electronic package weighs less than 14 pounds and measures about 16 1/2" x 8" x 5 1/2". The electronic package has a convenient carrying handle 14, and may be readily disconnected from the console cable at detachable plug 15. Both units may be moved about with ease. When the calculator is set up at a new location no complicated adjustments or calibrations are required. The console cable 13 is plugged into the electronic package at plug 15; power cable 16 is plugged into a wall outlet; the electronic package is turned on at switch 17 and the console is turned on at switch 20. The calculator is then ready to use.

Data and commands are entered into the calculator by actuating appropriate keys on the console keyboard 1. Each key is marked with a self-explanatory numeral or symbol. The size, grouping, and color coding of the keys are engineered for learning and efficient operation. Each key operates a sensitive microswitch. Operator fatigue is thus much less than in the case of electro-mechanical calculators which usually require longer key travel against greater mechanical resistance.

Input data and the results of computations are displayed in illuminated characters in a darkened display aperture 19 immediately above the keyboard. As a number is indexed on the keyboard, the display shows the number instantaneously. A glance at the display will confirm correct indexing. If a wrong number has been

indexed, simple error correction is available. The Clear Display key 30 is pressed to remove the error; the correct number may then be indexed.

The calculator described herein readily performs all the normal arithmetic functions of existing electronic and electro-mechanical calculators; for example, it adds, subtracts, multiplies, and divides operands of up to ten decimal digits on single keystroke commands. However, one major innovation incorporated in said calculator is that besides the basic arithmetic operations described above it is capable of performing far more powerful mathematical functions. On single-keystroke command, the calculator extracts eight-place natural logarithms, generates anti-logarithms thereof, extracts square roots, or generates squares. These capabilities are not obtained by utilizing the basic arithmetic operations in slow and cumbersome algorithms. On the contrary, they are built into the basic system logic; and are used as a means of implementing the more basic arithmetic functions of multiplication (accomplished by addition of logarithms of the operands) and division (subtraction of logarithms).

Other features of the calculator greatly facilitate computations applicable to a wide range of business and scientific problems. Two independent adders have sets of keys operating independently to add, subtract, recall, or clear numbers. By setting of well marked control switches for duplex operations, the calculator affords automatic accumulation of products, multipliers, and other entries for various mathematical requirements. Successively accumulated running sub-totals can be recalled from the calculator's memory unit at any time to continue the calculation. Floating decimal point control is provided; the decimal point is keyed in naturally with the number. The calculator automatically positions the decimal point, and shows it correctly in the display. Reciprocals are generated by a single key stroke (there is no need to enter 1 and then divide it by the number). There is a key which converts the sign of a number from plus to minus, and vice versa. This gives additional flexibility to many calculations.

All of the operations described above are executed almost instantaneously. Even in the case of long multiplication and division operations, successive operations are executed faster than any human operator can actuate the keyboard. Consequently, unlike slower electro-mechanical devices, the calculator ensures that no operator time is wasted while waiting for the machine to complete intermediate computations.

FIG. 2 is a diagrammatic view of the keyboard console operating controls 1 and display 2, and of the four magnetic core registers comprised by the calculator's memory unit 3. These registers are the Left Accumulator 4, the Right Accumulator 5, the Log Register 6, and the Work (or display) Register 7.

Each of these four rapid-access core registers is composed of sixteen binary-coded decimal digits. Each digit is in turn composed of four magnetic cores which store the four binary bits required to code a single decimal digit. Thus each of the four registers is physically composed of a set of sixty-four magnetic cores. The least significant digit 8 of each register (in digit position 0) stores the decimal point position (modulo 10). The most significant digit 9 of each register (in digit position 15) stores the sign of the number stored therein. (A plus sign is coded "0," a minus sign is coded "9.") The intermediate digits in positions 1 through 14 store fourteen numerical digits. Although the calculator displays only the ten most significant digits of the Work Register 7 it operates upon an additional four digits, thus obtaining added accuracy.

The following table correlates the functions of the various keys and switches on keyboard 1 with their characters or designations.

TABLE I.—KEYBOARD CONTROLS

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BASIC CONTROLS<br>ON (switch)            | This switch 20 is turned on to energize the keyboard console. When turned off, the entire keyboard, with the single exception of the CLEAR ALL key 22, is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CLEAR ALL                                | This key 22 clears all register contents in one stroke even if the ON switch is turned off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Numerical Keys<br>Decimal Point Key.     | Numerical Keys 24 and Decimal Point Key 26, when operated, place their information in the Work Register 7. (The contents of the Work Register are always visible at display 2.) For example, to key in 3.45, press the keys 10      3      .      4      5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CHANGE SIGN                              | This key 28 changes the sign of the number in the Work Register 7. For example, to key in -3.45, press the keys: 15      3      .      4      5      Change Sign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CLEAR DISPLAY                            | This key 30 clears the Work Register, but leaves the contents of the other three registers unchanged.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RIGHT ADDER CONTROLS<br>+                | This key 32 adds the contents of the Work Register to the contents of the Right Accumulator 5. The resulting sum is stored in both the Right Accumulator and the Work Register. Because the sum is in the Work Register, it is visible at display 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -                                        | This key 34 subtracts the contents of the Work Register from the contents of the Right Accumulator and stores the difference in both the Right Accumulator and the Work Register. The difference is thus visible at display 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RECALL ADDER                             | This key 36 transfers the contents of the Right Accumulator into the Work Register for display while leaving the Right Accumulator itself unchanged.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CLEAR ADDER                              | This key 38 clears the Right Accumulator and does not preserve its contents.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LEFT ADDER CONTROLS<br>+                 | These four keys 40, 42, 44, and 46 perform the same functions with respect to the Left Accumulator 4 that their counterparts 32, 34, 36, and 38 respectively (described above) perform with respect to the Right Accumulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RECALL ADDER                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLEAR ADDER                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MULTIPLY AND<br>DIVIDE CONTROLS<br>ENTER | This key 50 stores the natural logarithm (logarithm to the base e) of the number in the Work Register 7 in the Log Register 6, and clears the Work Register. The most significant digit 60 of the Log Register then represents the sign of the logarithm, the next two digits 62 represent the characteristic of the logarithm, the next twelve digits 64 represent the actual mantissa of the logarithm, and the least significant digit 66 always contains 2, indicating that the decimal point is to be spaced over two places from the most significant end of the logarithm (to mark the division between the characteristic and the mantissa). If some logarithm is already stored in the Log Register when the ENTER key is operated, the logarithm of the number in the Work Register is added to the logarithm in the Log Register. This feature permits chain multiplication of a series of factors without the necessity of entering intermediate sub-products. For example, to multiply $2 \times 3 \times 4 \times 5$ , press the keys: 40      2      ENTER      3      ENTER<br>45      4      ENTER      5      = |

X

=

The Work Register then displays the correct result, +120.0000000. This key 52 multiplies the number previously entered by the contents of the Work Register, and displays the result in the Work Register. The logarithm of the multiplier in the Work Register is added to the logarithm of the number previously entered (currently in the Log Register). This leaves the sum of the logarithms in the Log Register. The calculator then generates the anti-logarithm of this sum (which represents the product of the two numbers to be multiplied) and stores the result in the Work Register. The Log Register is cleared by the process of generating the anti-logarithm.

This key 54 divides the number previously entered by the contents of the Work Register and displays the result in the Work Register. The logarithm of the divisor in the Work Register is subtracted from the logarithm of the number previously entered (currently in the Log Register). This leaves the difference of the logarithms in the Log Register. The

TABLE I.—Continued

|                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENTER                                      | calculator then generates the anti-logarithm of this difference (which represents the quotient of the two numbers to be divided) and stores the result in the Work Register. The Log Register is cleared by the process of generating the anti-logarithm. If no number was previously entered, this key generates the reciprocal of the number in the Work Register and displays this reciprocal in the Work Register. (This follows from the fact that the Log Register initially contains 0, which is the natural logarithm of 1.) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LOGARITHMIC CONTROLS<br>LOG <sub>e</sub> X | This key 70 causes the natural logarithm of the number in the Work Register to be displayed in the Work Register. Although the logarithm is initially generated in the Log Register, the Log Register is cleared when the logarithm is displayed in the Work Register.                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ex                                         | This key 72 causes the number in the Work Register to be treated as a natural logarithm and displays the anti-logarithm thereof in the Work Register. Although the initial contents of the Work Register are transferred into the Log Register in order to generate the anti-logarithm, the Log Register is cleared when the anti-logarithm is displayed in the Work Register.                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 74                                         | This key 74 causes the square root of the number in the Work Register to be displayed in the Work Register. One-half the logarithm of the number is initially generated in the Log Register, and then the anti-logarithm thereof is generated and displayed in the Work Register. The Log Register is left in a cleared condition.                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 76                                         | This key 76 causes the square of the number in the Work Register to be displayed in the Work Register. Twice the logarithm of the number is initially generated in the Log Register, and then the anti-logarithm thereof is generated and displayed in the Work Register. The Log Register is left in a cleared condition.                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 30                                         | DUPLEX ACCUMULATION CONTROLS<br>PROD<br>ACCUM (switch).<br>ENTRY<br>ACCUM (switch).                                                                                                                                                                                                                                                                                                                                                                                                                                                  | This switch 80 causes the results of multiplications or divisions to be added automatically into the Left Accumulator. This switch 82 causes the automatic summation of the first numbers entered (multiplicand or dividend) for each of a series of multiplications or divisions. The resulting sum is stored in the Right Accumulator.                                                                                                                                                                                                                                                                           |

| 40                                         | MULT<br>ACCUM (switch).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | This switch 84 causes the automatic summation of the second numbers keyed in for each of a series of multiplications or divisions (multiplier or divisor). The resulting sum is stored in the Right Accumulator. If both the ENTRY ACCUM switch 82 and the MULT ACCUM switch 84 are operated, the Right Accumulator stores the sum of all the operands used in the series of multiplications and divisions. (Both the first numbers entered and the second numbers keyed in.)                                                                                                                                      |

| 50                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 55                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FIG. 3 is an over-all block diagram of the system logic of the calculator. The input commands which determine the operations to be performed by the calculator and the numerical data to be operated upon are both entered into the calculator by means of switches at the keyboard console. The keyboard console switching circuits 302 generate output signals in accordance with the operation of said switches. Certain of these output signals are applied over lines 303 directly to the Control Unit 304; others on lines 305 are used to control the state of the K register 306, a five-bit input buffer. |

| 60                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | The calculator Memory Unit 308 comprises a 16 x 16 core magnetic core plane which stores sixty-four individually addressable decimal digits, each such digit being stored in binary coded decimal form in four magnetic cores. These sixty-four digits make up four 16-digit core registers, designated respectively A <sub>0</sub> (Right Accumulator 5), A <sub>1</sub> (Left Accumulator 4), L (Log Register 6), and W (Work or Display Register 7).                                                                                                                                                            |

| 65                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Six bits of address information are used to address any one of the sixty-four four-bit decimal digits in the Memory Unit. Two of these six bits, designated XG <sub>1</sub> and XG <sub>2</sub> (respectively line 310 and line 312) are register-address                                                                                                                                                                                                                                                                                                                                                          |

| 70                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

bits used to specify one of the four core registers in accordance with the coding shown in Table II.

TABLE II.—MEMORY REGISTER ADDRESS CODING

| XG <sub>1</sub> | XG <sub>2</sub> | Addresses                                        |

|-----------------|-----------------|--------------------------------------------------|

| 0               | 0               | W, Register 7 (Work or Display).                 |

| 0               | 1               | A <sub>0</sub> , Register 5 (Right Accumulator). |

| 1               | 0               | L, Register 6 (Log).                             |

| 1               | 1               | A <sub>1</sub> , Register 4 (Left Accumulator).  |

The remaining four bits of address information are digit-address bits used to specify one of the sixteen digits making up the addressed register. These four digit-address bits may be taken from the 1-side of the R counter flip-flops 314, the 0-side of the R counter flip-flops 316, or the 1-side of the four least significant T counter flip-flops T<sub>1</sub>, T<sub>2</sub>, T<sub>4</sub>, and T<sub>8</sub> (lines 318). The choice is determined by the C switch 320. This switching arrangement permits the calculator to scan the four memory registers in three distinct modes of operation. When the 1-side of the T counter flip-flops are switched in by the C switch 320, the memory reads or writes the addressed register one digit at a time from right (least significant bit, bit 0) to left (most significant bit, bit 15) as the T counter 322 is counted up. Similarly, when the 1-side of the R counter flip-flops are switched in, the memory reads or writes successive digits from right to left as the R counter 324 is counted up. Finally, when the 0-side (complement side) of the R counter is switched in, the memory reads or writes from left to right (from bit 15 to bit 0) as the R counter is counted up.

The two XG register-address bits (lines 310 and 312) and the four digit-address bits (the latter taken from the C switch output) are applied to X and Y selection networks 326 and 328, respectively. The XG<sub>1</sub> bit and two digit-address bits are applied to the X selection network; the XG<sub>2</sub> bit and the remaining two digit-address bits are applied to the Y selection network. The X and Y selection networks in turn generate sixteen select signals (eight X-select signals and eight Y-select signals) which energize appropriate X and Y drive lines within the core plane. Any given configuration of these sixteen selection signals selects four of the 256 cores in the 16 x 16 core plane. The four selected cores correspond to one of the sixty-four binary-coded decimal digits comprised by the Memory Unit core plane.

During write operations the specific information to be written into the four addressed cores making up the addressed digit is taken from one of five alternate four-bit data sources, the choice between these five data sources is determined by the D switch 330. The first of the five sources is the K register 306. Only the four least significant bits of this register K<sub>8</sub>, K<sub>4</sub>, K<sub>2</sub>, and K<sub>1</sub> are used to hold numerical data that is to be written in memory (this data is brought into the D switch on lines 331). The second source of data (lines 332) is a fixed code 1-1-1-1 (code 15) which indicates that no numerical data is stored in the digit position so coded. The third source of data (lines 334) is the output of the Arithmetic Unit 336. The fourth source of data (lines 338) is the contents of the four-bit G register 340. The fifth and final source of data (lines 342) that may be written into the addressed memory digit is the contents of the four-bit E register 344.

When an addressed digit is read out of memory through lines 346 it is initially stored in the E register memory output buffer 344. From the E register the data read out from the addressed memory digit may be transferred along lines 348 to a second buffer register, the G register 340, it may be applied along lines 350 to the Display Unit 352, or it may be routed through lines 356 and thus used as one of the two operands that are applied to the four stage binary adder 358 in Arithmetic Unit 336. The display position at which a given digit of data appears is determined by the contents of the T counter 322; the

contents of T are applied to the display through lines 354.

Arithmetic Unit 336 always takes the first of its two operands from the E register 344. The second operand is taken from one of three alternate sources; the choice between these three sources is determined by the B switch 360. The first of the three sources is the G register 340. The contents of G are applied to the B switch through lines 362. The second source is the R counter 324. The 1's complement of the R counter contents are applied to the B switch through lines 364. The third and final source is the log generator 384. The output of the log generator is applied to the B switch through lines 368.

Each digit received by the B switch is applied to 9's complement matrix 370. If a subtraction is to be performed, the 9's complement matrix is enabled by signal CP at 372; the 9's complement matrix then forms the 9's complement of the digit received from the B switch. If an addition is to be performed, rather than a subtraction, the CP signal is not asserted, and the 9's complement matrix passes the digit received from the B switch unchanged.

The output digit from the 9's complement matrix 370 is applied to 4-stage binary adder 358 where it is summed with the contents of E register 344 and the contents of the CAS carry flip-flops 378. The resulting sum is applied to binary to binary-coded-decimal converter 374 which generates the final output digit from the Arithmetic Unit, the digit representing the digit in the E register increased (for addition operations) or reduced (for subtraction) by the B switch output digit.

If the output from converter 374 is greater than nine, a carry signal is produced on line 376, and said carry is used to set CAS carry flip-flop 378 in preparation for the processing of the next digit. The calculator effects subtraction operations by adding the 10's complement of the subtrahend (the 9's complement augmented by 1) to the minuend. The 1 that converts the 9's complement to 10's complement is generated by setting the CAS carry flip-flop 378 before processing the initial digit of the subtraction operation. This is accomplished by passing the CP signal through gate 380 when the gate is enabled by the r<sub>0</sub> signal on line 382. The r<sub>0</sub> signal is asserted only when the R counter 324 contains 0, i.e. during the processing of the first (least significant) digit of the subtraction operation.

The log generator 384 is controlled by the contents of the T counter 322 and the R counter 324. The T counter contents (on lines 386) determine which of 12 different logarithms stored in the log generator is to be used. The R counter contents (in lines 388) determine which digit of the selected constant is to be generated at a given time.

The Control Unit 304 contains the control counters, flip-flops, and logic networks that produce the sequenced signals necessary to initiate and control the various commands that the calculator performs in response to keyboard input. The start and stop controls 390 control the starting and stopping of each key-initiated command. The KB and KE flip-flops form a synchronizing network that synchronizes the randomly timed operation of a keyboard key to the internal clock of the calculator. The RST flip-flop is set by the CLEAR ALL signal from the keyboard. When set, RST causes the generation of a plurality of reset pulses that return the system logic to an appropriate initial state and clear all registers.

The timing control logic 392 includes the system P clock logic as well as the Q flip-flop which determines when the R counter may be stepped.

The subcycle counters 394 include the R counter 324, an associated S flip-flop 325, and the T counter 322 and 323. These components govern the timing of the various operations making up each of the major system cycles.

The B counter 395 advances the calculator logic from one major system cycle to another in accordance with the requirements of the current command.

A plurality of control flip-flops 396 are used for storing control information during the progress of the various system commands.

The states of the control counters and flip-flops are logically combined with other control signals in a plurality of decoders and other control logic networks 398.

All of the foregoing logical elements are illustrated and described in greater detail in the remaining figures and associated text.

FIGURE 4 is a block diagram of the calculator's Memory Unit 308 with its associated input and output circuitry. The C switch 320 determines the source of the four digit-address bits. The C switch contains three gates 402, 404, and 406. When gate 402 is enabled by the assertion of SC<sub>0</sub> signal at input 408 the 1-side outputs of the four R counter (324) flip-flops (R<sub>1</sub>, R<sub>2</sub>, R<sub>4</sub>, and R<sub>8</sub>) are used as the digit-address. When gate 404 is enabled by the assertion of the SC<sub>1</sub> signal at input 410, the 0-side outputs of the four R counter flip-flops (R̄<sub>1</sub>, R̄<sub>2</sub>, R̄<sub>4</sub> and R̄<sub>8</sub>) are used as the digit-address. When gate 406 is enabled by the assertion of the SC<sub>2</sub> signal at input 412, the 1-side outputs of the four T counter flip-flops (T<sub>1</sub>, T<sub>2</sub>, T<sub>4</sub> and T<sub>8</sub>) are used as the digit-address. If none of the three signals SC<sub>0</sub>, SC<sub>1</sub>, or SC<sub>2</sub> are asserted, the digit address is 0 (decimal point position). The XG<sub>1</sub> signal (line 310) and the XG<sub>2</sub> signal (line 312) determine which of the four 16-digit core registers is to be addressed as indicated above.

The XG<sub>1</sub> signal and two of the four C switch outputs are applied to the X-select driver 326. The X-select driver contains a binary-to-octal decoder 414, and a set of eight bi-directional core-drivers D<sub>0</sub> through D<sub>7</sub> (416). For each of the eight possible configurations of the three input bits applied to the X-select driver 326 one of the eight outputs of binary-to-octal decoder 414 is asserted. The asserted output enables the associated core driver which is then turned on in one direction by the read-drive signal on line 418, and in the opposite direction by the write-drive signal on line 420. The resulting read and write drive pulses are applied to the core plane via the appropriate X-drive core-selection line 422. Each X-drive core-selection line threads eight sets of four cores, thereby half-selecting eight four-bit digits.

Similarly, the XG<sub>2</sub> signal and the remaining two of the four C switch outputs are applied to the Y-select driver 328. That driver functions in essentially the same manner as the X-select driver. Its output read and write drive pulses are applied to the core plane via the appropriate Y-drive core-selection line 424. Each Y-drive core-selection line also threads eight sets of four cores, thereby half-selecting eight four-bit digits. The intersection of the active X-drive core-selection line and the active Y-drive core-selection line uniquely addresses one set of four cores, namely that four-bit set of cores making up the single addressed digit. At the occurrence of the read-drive signal on line 418, data is read out from the addressed digit; at the occurrence of the write drive signal on line 420, data is written back into the addressed digit.

The four bits of data to be written into the addressed digit are determined by the four digit-inhibit signals on lines 426 (DG<sub>1</sub>, DG<sub>2</sub>, DG<sub>4</sub>, and DG<sub>8</sub>). When any one of these signals is asserted, a 0 is written into the corresponding core bit of the addressed digit at the write-drive signal. If a given digit-inhibit signal is not asserted, a 1 is written into the corresponding core bit of the addressed digit at the write-drive signal.

At the read-drive signal, the outputs generated by the four core bits of the addressed digit are applied to four sense amplifiers 428 (SA<sub>1</sub>, SA<sub>2</sub>, SA<sub>4</sub>, and SA<sub>8</sub>). The sense amplifiers corresponding to cores which contained 1's prior to the read-drive signal produce output signals on lines 430 (SE<sub>1</sub>, SE<sub>2</sub>, SE<sub>4</sub>, and SE<sub>8</sub>). Unless the SGG inhibit signal (line 434) is asserted, these SE output signals transfer the same data that was stored in the four cores of the addressed digit through inhibit gate 432 into the E register memory output buffer 344.

The E register 344 is cleared by the occurrence of ERP reset pulse (line 436). This pulse is initiated by the P<sub>1</sub> clock pulse (line 438) whenever the RW signal (line 442) is asserted and thereby enables gate 440. The same P<sub>1</sub> clock pulse is also applied to gate 444 over line 446, thereby advancing the contents of E register 344 into the G register 340. The G register is cleared by GR on line 437.

The contents of the E register are decoded by logical NOR gates 448 and 450 to determine whether or not E contains code 15 (1-1-1-1) and code 0 (0-0-0-0). If the E register contains 15, DE<sub>15</sub> is asserted on line 452. The output of NOR gate 448 is also applied to inverter 454 to produce the complement signal  $\overline{DE}_{15}$  ("not" DE<sub>15</sub>), which signal is asserted whenever the E register does not contain code 15. If the E register contains 0, DE<sub>0</sub> is asserted at line 456; if it does not contain 0, inverter 458 causes the assertion of  $\overline{DE}_0$ .

(In all figures of this specification the same triangular symbol designated by reference numerals 454 and 458 of FIG. 4 is used to signify means producing logical inversion or the equivalent thereof; and throughout the present description signal designations with superscribed lines are used to signify the logical complements of said signal designations absent the superscribed lines.)

FIGURE 5 is a block diagram of the data-input logic which controls the four digit-inhibit signals applied on lines 426 (DG<sub>1</sub>, DG<sub>2</sub>, DG<sub>4</sub>, and DG<sub>8</sub>) which in turn control the four bits of input data that are written into the addressed digit of the memory during the write-drive signal. The D switch 330 determines the source of the four input data bits.

The D switch contains five gates 502, 504, 506, 508, and 510. When gate 502 is enabled by the assertion of the SD<sub>0</sub> signal at input 512, the outputs from the Arithmetic Unit (AD<sub>1</sub>, AD<sub>2</sub>, AD<sub>4</sub>, and AD<sub>8</sub>) are used as the source of the input data to be written into the addressed memory digit. The four inputs from the Arithmetic Unit are combined by NOR gate 511 to determine whether the sum or difference digit generated is or is not a zero. The AD<sub>0</sub> signal is asserted if the sum or difference digit is zero, the signal is not asserted if the sum or difference digit is not a zero. When gate 504 is enabled by the assertion of SD<sub>1</sub> at input 514, the contents of the E register memory output buffer are rewritten into the addressed digit. When gate 506 is enabled by the assertion of SD<sub>3</sub> at input 516, code 15 (1-1-1-1) is used as input data. When gate 508 is enabled by SD<sub>6</sub> at input 518, the contents of the four least significant bits of the K register (K<sub>1</sub>, K<sub>2</sub>, K<sub>4</sub>, and K<sub>8</sub>) provide the input data. When gate 510 is enabled by SD<sub>7</sub> at input 520, the contents of the G register provide the input data. If none of the five input signals SD<sub>0</sub>, SD<sub>1</sub>, SD<sub>3</sub>, SD<sub>6</sub>, or SD<sub>7</sub> are asserted, the input data is code 0 (0-0-0-0).

Inhibit gates 522, 524, 526, 528, and 530 ensure that the input data is only permitted to pass at the appropriate portions of the read-write cycle. These gates are disabled by the  $\overline{P}_{34}$  signal (line 532) at all times except during the generation of the P<sub>3</sub> and P<sub>4</sub> clock pulses. While the inhibit gates are disabled, no digit-inhibit signals (lines 426) may be generated. During P<sub>3</sub> and P<sub>4</sub> time, when the inhibit gates are not disabled, the four bits of input data from the enabled gate 502, 504, 506, 508, or 510 are passed through as input data bits on lines 534 (DG<sub>1</sub>, DG<sub>2</sub>, DG<sub>4</sub>, DG<sub>8</sub>).

The DG input data bits which are 1's do not produce any inhibit current and so result in the writing of 1's in the corresponding cores of the addressed digit. The D input data bits which are 0's do cause the corresponding inhibit amplifiers 536 (IA<sub>1</sub>, IA<sub>2</sub>, IA<sub>4</sub>, and IA<sub>8</sub>) to be turned on, thus generating digit-inhibit signals on lines 426 (DG<sub>1</sub>, DG<sub>2</sub>, DG<sub>4</sub>, and DG<sub>8</sub>) which prevent the writing of 1's in the associated cores of the addressed digit, and which cause 0's to be written in those cores.

FIGURE 6 is a diagrammatic view of the Memory Unit core plane 308, illustrating the geometrical relationship of the component magnetic cores and the associated core windings. The core plane is a square 16 x 16 core matrix made up of four smaller square 8 x 8 core arrays 602, 5 604, 606, and 608. Each of the eight X-drive core-selection lines ( $X_0$  through  $X_7$ ) is shown in the figure as passing through one vertical column of eight cores in each of the four 8 x 8 core arrays. For example, the X-drive core-selection line  $X_0$  is shown as passing through (and thus half-selecting) the left-hand column of eight cores in each of the four 8 x 8 arrays. The X-select read and write drive pulses enter  $X_0$  at 10 610, pass through thirty-two (4 x 8) half-selected cores and exit to a suitable terminating load 612. Similarly, each of the eight Y-drive core-selection lines ( $Y_0$  through  $Y_7$ ) is shown in the figure as passing through one horizontal row of eight cores in each of the four 8 x 8 arrays. For example, the Y-drive core-selection line  $Y_0$  is shown as passing through (and thus half-selecting) the uppermost row of 15 eight cores in each of the four arrays. The Y-select read and write drive pulses enter at 614, pass through thirty-two (4 x 8) half-selected cores and exit to a suitable terminating load 616. Note that  $X_0$  and  $Y_0$ , the two core-selection lines that are shown in full in FIG. 6, intersect at one core in each of the four core planes. These four cores, 25 618, 620, 622, and 624 are the four fully-selected cores making up the single four-bit binary coded decimal digit that is addressed by  $X_0$  and  $Y_0$ . Each of the sixty-four possible combinations of one of the eight X-drive core selection lines ( $X_0$  through  $X_7$ ) with one of the eight Y-drive core selection lines ( $Y_0$  through  $Y_7$ ) will 30 address one of the sixty-four four-bit digits stored in 16 x 16 core plane 308. Each of these sixty-four digits includes one core from each of the four 8 x 8 core 35 arrays.

The four digit-inhibit signals (lines 426) ( $\overline{DG_1}$ ,  $\overline{DG_2}$ ,  $\overline{DG_4}$ , and  $\overline{DG_8}$ ) are each applied to a separate inhibit-winding. Each of these four inhibit-windings threads all of the sixty-four cores in one of the four 8 x 8 arrays. For example, the  $\overline{DG_1}$  inhibit winding is shown in the figure as threading all sixty-four of the cores in array 40 602. The  $\overline{DG_1}$  digit-inhibit signal enters at line 626, passes back and forth through all eight horizontal rows of cores, and exits to a suitable terminating load 628. Each of the three remaining digit-inhibit signals is passed through a similar inhibit winding threading all sixty-four of the cores in one of the three remaining 8 x 8 core arrays (604, 606, and 608). In this manner each of the four digit-inhibit signals controls the data that is written into one of the four bits of the addressed digit. When a given inhibit signal is activated, no core in the associated array can have a 1 written into it by the X-select and Y-select write-drive pulses. Since all sixty-four cores in the 8 x 8 array are threaded by the inhibit signal it does not matter at which core among the sixty-four the two write-drive pulses happen to intersect. No core in the array is permitted to receive a 1; consequently, a 0 must be written into the selected core.

Core plane 308 contains four separate sense windings. Each of these four sense windings threads all of the sixty-four cores in one of the four 8 x 8 arrays. For example, the single sense winding illustrated in FIG. 6 is shown as passing diagonally back and forth through all sixty-four of the cores in array 606. Similarly, each of the three remaining sense windings threads all sixty-four of the cores in one of the three remaining arrays (602, 604, and 608). Both ends of each sense winding are coupled by suitable means to one of the four sense amplifiers 428 (SA<sub>1</sub>, SA<sub>2</sub>, SA<sub>4</sub>, and SA<sub>8</sub>).

In this manner each of the four sense windings senses the data that is stored in one of the four bits of the addressed digit. If a given core contains a 1, and is located at the intersection of the pair of X-drive and Y-drive 75

core-selection lines that receive read-drive pulses, then that core changes state and generates an output signal upon the corresponding sense winding. Since all sixty-four cores in the 8 x 8 array are threaded by the sense winding it does not matter at which core the two read-drive pulses happen to intersect. If the selected core contains a 0, no output signal is generated upon the sense winding. However, if the selected core contains a 1, an output signal is applied to the sense winding. From the sense winding, the output signal is coupled to the corresponding sense amplifier 428. That sense amplifier then produces an SE output signal on one of the lines 430.

The result of this arrangement is: (1) that each four-bit digit is individually addressable; (2) that each of the four bits in the addressed digit may be controlled during write operations by one of the four digit-inhibit signals on one of the lines 426; and (3) that during read operations each of the four bits in the addressed digit generates an independent output signal on one of the lines 430.