|

The ZIP Parallel Interface: Nibble Mode

Nibble Handshake

Nibble mode is input only, since data out is via the normal byte register.

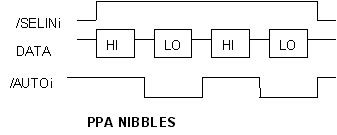

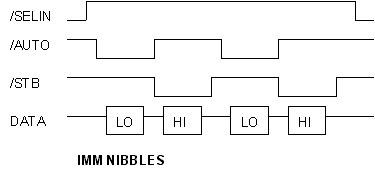

Neither IMM nor PPA are fully IEEE compatible.

| zip | ieee | ||

| Status Register bit | LO/HI | ||

| nBUSY | 7 | ~3/~7 | 3/7 |

| nACK | 6 | 2/6 | -- |

| PAPER | 5 | 1/5 | 2/6 |

| ONLINE | 4 | 0/4 | 1/5 |

| nFAULT | 3 | -- | 0/4 |

The bit arrangements for nibble mode have been knowingly designed for an IBM PC interface whereas IEEE is OEM agnostic.

In an IBM PC, the status register reflects the signals listed in bits 7->3. The hardware of the PC interface inverts the BUSY signal. Therefore, the zip interface differs as follows:

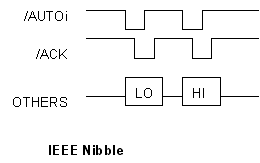

True IEEE nibble mode timing.

nFAULT and PAPER remain low while data is available from peripheral.

|

|

As can be seen, both types of zip 'nibble' mode, differ markedly from the ieee standard.