# **NANOCOMPUTER<sup>®</sup>**

# **TRAINING**

# **SYSTEM**

# **TECHNICAL**

# **MANUAL**

**2<sup>nd</sup> EDITION**

## W A R N I N G ! !

We don't want to spoil your enjoyment of this new world of computing but we must warn you of new dangers when using these complex and sensitive electronic components.

### THE CIRCUIT BOARDS

Although the boards are made of tough fibre-glass, the fine circuit tracks on both sides can be damaged by physical shocks or flexing/bending the board. Take care when first unpacking and when plugging or unplugging not to put too severe a strain on the circuit boards.

### THE COMPONENTS

Many of the components on the boards are MOS (Metal-Oxide-Silicon) IC's. These IC's are sensitive to static electricity.

Do not unplug any IC's from the board without taking the proper precautions. We recommend you only handle MOS circuits on a metal topped table which is earthed, use only earthed soldering irons and avoid clothing materials which generate static electricity.

Don't, of course, operate the circuit boards on a metal surface which could short circuit components.

When handling the NBZ80 or NEZ80 boards, particularly when inserting or removing external connections ensure that there are no high voltages present which can damage the circuit components.

Take care and you will enjoy the new world of the Z80.

## NANO COMPUTER TRAINING SYSTEM

|                                                   |         |

|---------------------------------------------------|---------|

| 1. Introduction                                   | pag. 12 |

| 1.1. CLZ80/NC board                               | 13      |

| 1.2. NKZ80 keyboard display                       | 16      |

| 1.3. NEZ80 experiment board                       | 18      |

| 1.4. NBZ80-S Nanocomputer super                   | 19      |

| 2. Installation of system                         | 21      |

| 2.1. A.C. power connection                        | 22      |

| 2.2. System switch-on and reset                   | 22      |

| 3. CLZ80/NC board circuit description             | 23      |

| 3.1. CPU                                          | 23      |

| 3.2. Gamma-bus interface                          | 24      |

| 3.3. EPROM/ROM                                    | 25      |

| 3.4. ROM control                                  | 25      |

| 3.5. RAM                                          | 25      |

| 3.6. RAM timer                                    | 25      |

| 3.7. RAM control                                  | 26      |

| 3.8. Memory selection                             | 26      |

| 3.9. Peripheral selection                         | 27      |

| 3.10. Flag input                                  | 28      |

| 3.11. Input/Output ports A, B, C, D               | 29      |

| 3.12. Interrupt                                   | 29      |

| 3.13. Control of cassette recorders               | 29      |

| 3.14. Clock generator                             | 30      |

| 3.15. Serial interface                            | 30      |

| 3.16. Initialization control                      | 30      |

| 4. Connectors, cables and links of CLZ80/NC board | 31      |

| 4.1. Connectors                                   | 31      |

| 4.2. Cables                                       | 34      |

| 4.3. Links                                        | 35      |

| 5. Signal specifications of CLZ80/NC board        | 39      |

| 5.1. Gamma-bus interface                          | 39      |

| 5.1.1. Signal description                         | 42      |

| 5.1.2. Electrical characteristics                 | 44      |

| 5.1.3. Interconnection rules                      | 45      |

| 5.1.4. Timing                                     | 48      |

|                                                         |         |

|---------------------------------------------------------|---------|

| 5.2. PIO interface (Parallel Input/Output)              | pag. 53 |

| 5.2.1. Signal descrption                                | 54      |

| 5.2.2. Electrical characteristics                       | 56      |

| 5.2.3. Interconnection rules                            | 58      |

| 5.2.4. Timing                                           | 58      |

| 5.3. Magnetic unit interface                            | 58      |

| 5.3.1. Signal description                               | 58      |

| 5.3.2. Electrical characteristics                       | 59      |

| 5.3.3. Recording format                                 | 59      |

| 5.4. Serial interface                                   | 60      |

| 5.4.1. Signal description                               | 61      |

| 5.4.2. Electrical characteristics                       | 61      |

| 6. NKZ80 Keyboard-Display, circuit description          | 63      |

| 6.1. Display and keyboard                               | 64      |

| 7. NEZ80 Experiment board - circuit description         | 65      |

| 7.1. Use of experiment board                            | 66      |

| 7.2. Description of user signals                        | 66      |

| 7.3. Electrical characteristics of user signals         | 68      |

| 8. NC-Z Operating system and NE-Z experiment program    | 70      |

| 8.1. RAM test program                                   | 70      |

| 8.2. Keyboard/display test program                      | 72      |

| 8.3. NE-Z experiment program                            | 73      |

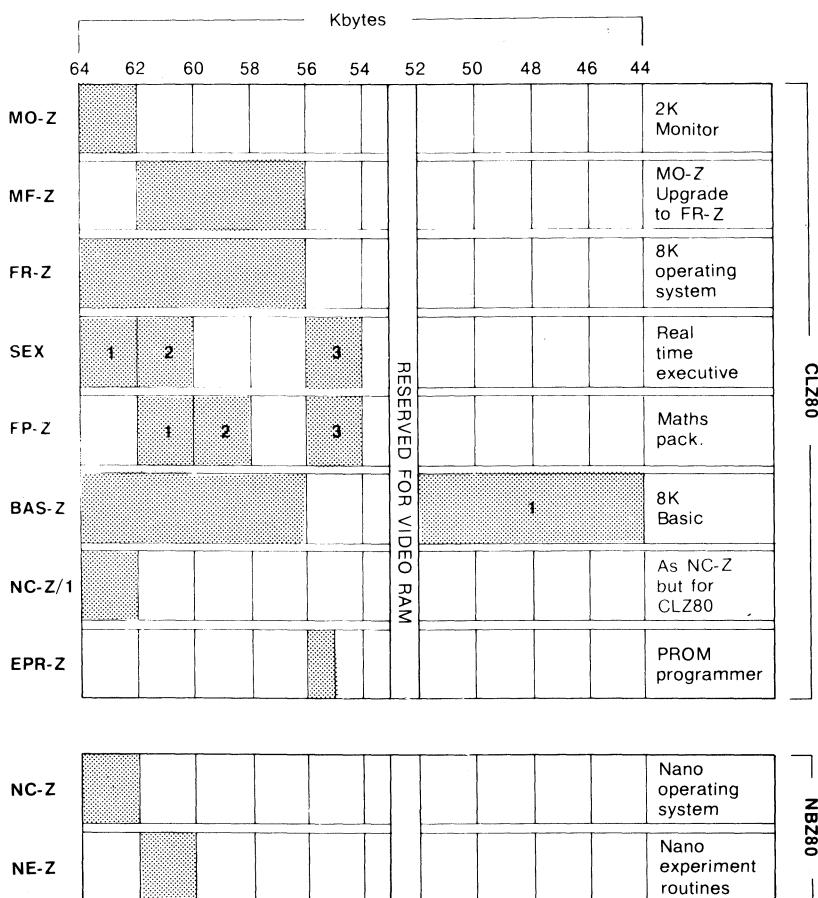

| 8.4. EPROM/ROM system lay-out                           | 73      |

| 9. Operating description - key operation                | 74      |

| 9.1. Examples of register loading                       | 76      |

| 9.2. Example of program creation, execution and control | 79      |

| 9.3. DUMP and LOAD on cassette                          | 83      |

| 9.4. DUMP and LOAD on serial terminal                   | 84      |

| 10. Expansion of the system.                            | 85      |

| 10.1. Hardware expandibility                            | 85      |

| 10.2. Software expandibility                            | 86      |

ENCLOSURES

- \* Electrical diagrams, list and lay-out CLZ80/NC components

- \* Dimensions of CLZ80/NC and NEZ80 boards and of keyboard/display

- \* Electrical diagrams, list and lay-out of NEZ80 components

- \* DN 314

- \* DN 340

## NANOCOMPUTER<sup>®</sup> TRAINING SYSTEM

Welcome to the world of the best 8-bit microprocessor, the SGS-ATES Z80(\*) .

The Z80 family of LSI components consists of :

Z80 CPU - Central processing Unit

Z80 PIO - Peripheral Input/Output

Z80 CTC - Counter Timer Circuit

Z80 SIO - Serial Input/Output

Z80 DMA - Direct Memory Access

The Nanocomputer Training System was designed, using members of this family, for education and training on the Z80 microprocessor.

The system covers :

- \* programming in Z80 assembler language

- \* digital electronics for microcomputers

- \* interfacing between CPU, memories, PIO and CTC.

A full set of documentation in three volumes, covering all these subjects, is provided with the system to meet all the needs of the student and educator.

® Nanocomputer is a registered trade mark of SGS-ATES.

(\*) Z80 is a registered trade mark of Zilog Inc.

The Nanocomputer training system components, hardware and software support are:

---

| Type | Description |

|------|-------------|

|------|-------------|

---

### Hardware

|          |                                                                                                                                                                                                                           |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NBZ80    | z80 based Nanocomputer formed by :<br>- CLZ80/NC board with 4Kb of RAM, 8Kb of EPROM with monitor programs (NC-Z9)<br>- NKZ80 keyboard-display<br>- Technical manual<br>- Vol. 1 "Z80 Microprocessor Book 1 Programming"  |

| NBZ80-A  | As the NBZ80 plus the power supply NSZ80                                                                                                                                                                                  |

| NBZ80-B  | As the NBZ80 plus the NPZ80 card frame (including power supply)                                                                                                                                                           |

| NBZ80-S  | As the NBZ80-B plus the NEZ80 board, the KlZ80 wire kit and Vol. 3 "Z80 Microprocessor Book 3 Interfacing"                                                                                                                |

| UPZ80-S  | Upgrading kit : allows upgrading from NBZ80 to NBZ80-S<br>Includes : - NEZ80 board<br>- NPZ80 supply and card frame<br>- W15Z80 connection cable<br>- Vol. 3 "Z80 Nanobook Interface"<br>- KlZ80 wire kit for experiments |

| NBZ80-HL | As the NBZ80-S system plus the video terminal, aphanumeric keyboard and guide to BASIC language                                                                                                                           |

| UPZ80-HL | Upgrading kit : allows upgrading from NBZ80-S to NBZ80-HL                                                                                                                                                                 |

| NEZ80    | Interface hardware experiment board                                                                                                                                                                                       |

| TVZ80    | 12" video monitor for use with the video terminal                                                                                                                                                                         |

| RCZ80    | Cassette recorder with automatic control (requires cable W10Z80 for connection to system)                                                                                                                                 |

| SSZ80    | Serial printer. Centronics model 779 for standard 8 1/2" paper with 80 - 132 coloums (60 - 96 char/sec)                                                                                                                   |

---

| Type                         | Description                                                                                                                                                              |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>A c c e s s o r i e s</b> |                                                                                                                                                                          |

| NSZ80                        | Mini supply for the NBZ80                                                                                                                                                |

| NPZ80                        | Card frame for CLZ80/NC and NEZ80 boards with supply incorporated                                                                                                        |

| KNZ80                        | Conversion kit. Allows conversion of a CLZ80/NC board to a CLZ80 4/2 microcomputer. Includes : UART, DC-DC converter, control PROM, MO-Z monitor on EPROM and connector. |

| NKZ80                        | Keyboard-display complete with connection cable                                                                                                                          |

| K1Z80                        | Cable kit for connecting circuits to NEZ80 board.                                                                                                                        |

| K2Z80                        | Passive semiconductor components for NEZ80 board                                                                                                                         |

| K3Z80                        | Three 40-pin sockets for NEZ80                                                                                                                                           |

| K4Z80                        | Connectors for upgrading Gamma-bus on NEZ80 board                                                                                                                        |

| K5Z80                        | Active and passive components kit for experiments described in training book Vol. 2 "Z80 Microprocessor Book 2 Digital Electronics"                                      |

| W6Z80                        | Cable for connecting NBZ80-HL to antenna input of a commercial TV                                                                                                        |

| W8Z80                        | As W6Z80 but for input of a TV monitor                                                                                                                                   |

| W10Z80                       | Cable for connecting a cassette recorder to the NBZ80/NBZ80-S/ NBZ80-HL                                                                                                  |

| W12Z80                       | Cable for connection of printer SSZ80 to the NBZ80-HL system                                                                                                             |

| W15Z80                       | Cable for connecting NEZ80 to CLZ80/NC PIO ports C and D.                                                                                                                |

| Type                   | Description                                                                                                   |

|------------------------|---------------------------------------------------------------------------------------------------------------|

| <b>S o f t w a r e</b> |                                                                                                               |

| NC-Z                   | 2K monitor for NBZ80 supplied on two M2708 EPROMs or one M2316E ROM.                                          |

| NE-Z                   | 2K experiment software for the NBZ80-S and NBZ80-HL systems. Available on two M2708 EPROMs or one M2316E ROM. |

| BAS-Z/N                | 8K BASIC interpreter for the NBZ80-HL system. Available on 4 M2716 EPROMs                                     |

| NCHESS                 | 4K chess program supplied in two EPROM/ROM's. Six levels of play.                                             |

#### **M a n u a l s**

- 1 Z80 Microprocessor Book 1 Programming

- 2 Z80 Microprocessor Book 2 Digital Electronics

- 3 Z80 Microprocessor Book 3 Interfacing

Enquiries about all of these components, accessories and books should be made to your local SGS-ATES distributor or Sales Office.

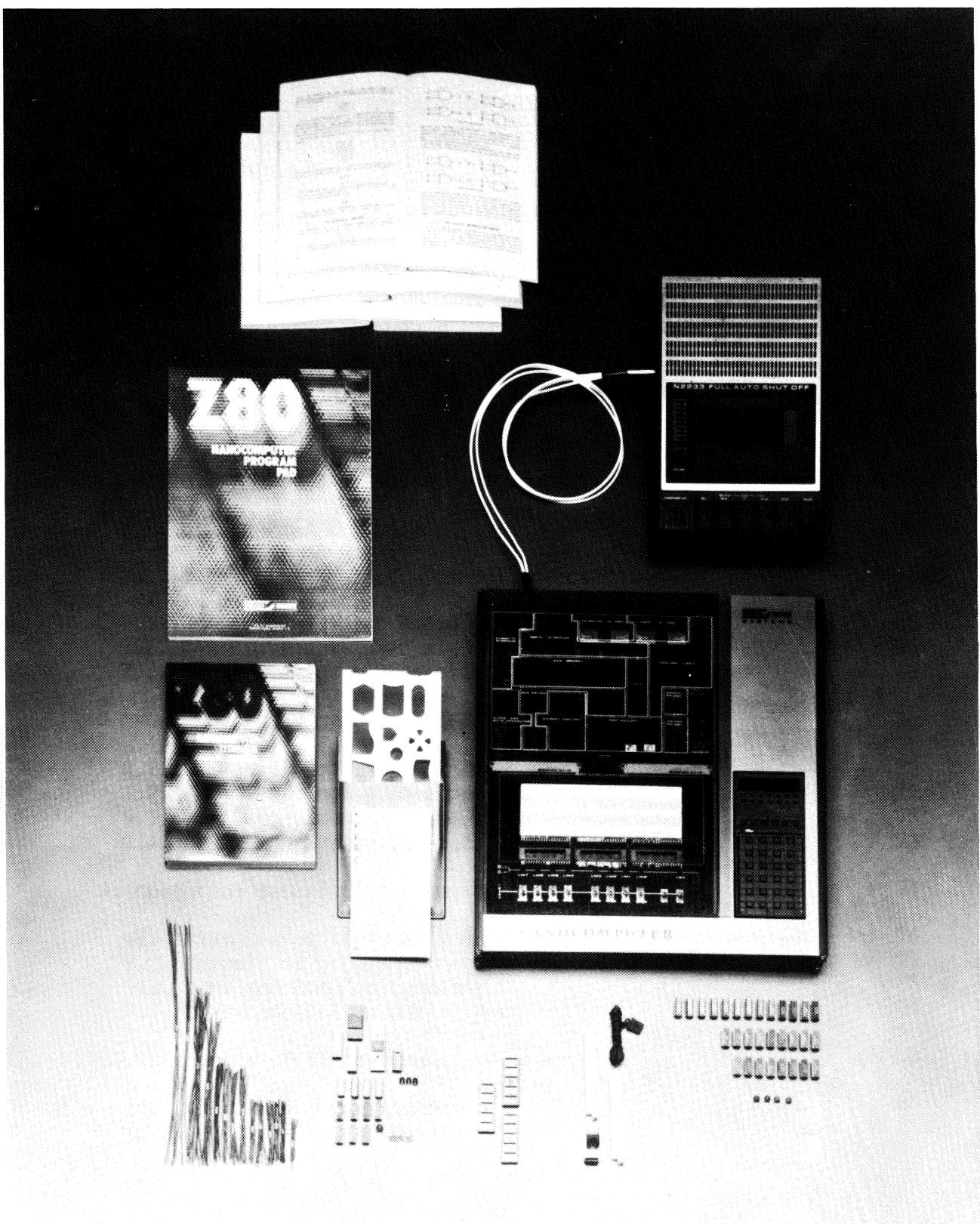

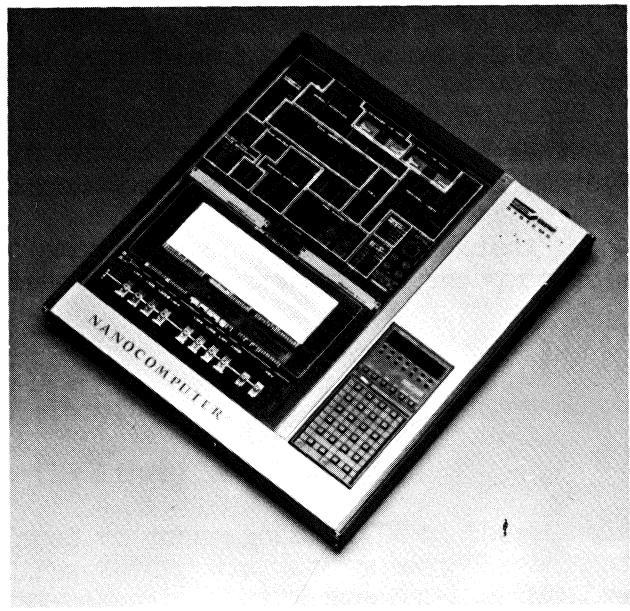

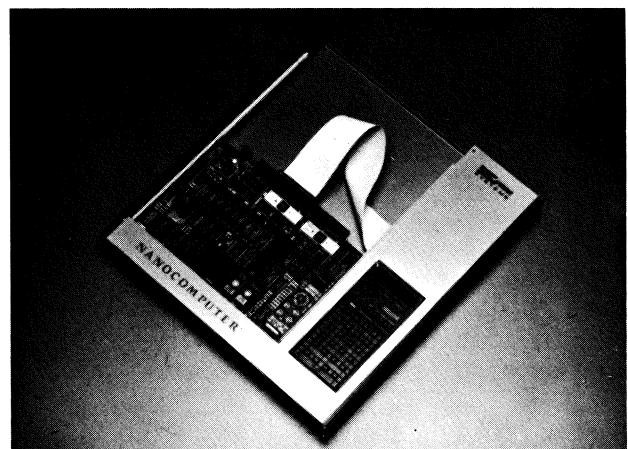

NBZ80

NBZ80-A

NBZ80-B

NBZ80-S

## (1) INTRODUCTION TO NANOCOMPUTER TRAINING SYSTEM

The Nanocomputer Training System consists of :

The CLZ80/NC board containing a small but complete microcomputer with Z80CPU, 4K bytes (4K x 8 bit) of dynamic RAM, 2K bytes of EPROM or ROM (and two or three other sockets for another 2K or 6K depending on the types of EPROM/ROM used), 2 x Z80 PIO chips giving 32 lines of input/output and a buffered Gamma-bus compatible interface.

The input/output of the Nanocomputer is provided by the NKZ80 keyboard display (pocket calculator style) including a display with 8 hexadecimal digits, 14 indicators, 16 hexadecimal keys and 14 keys for various control functions.

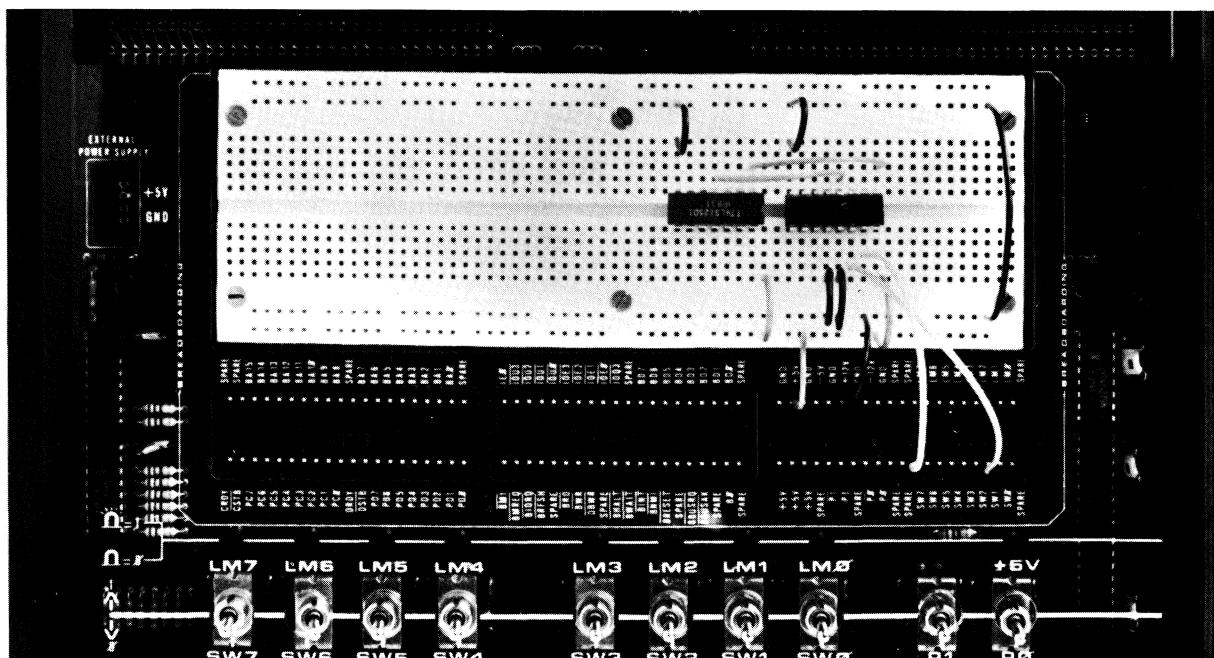

The NEZ80 experiment board containing a special solderless breadboard, connectors to the Gamma-bus signals, 8 logic switches, 8 logic level LED display lamps and two pulsers. The NEZ80 board interfaces to the CLZ80/NC board on the Gamma-bus structure.

The NPZ80 card cage, for boards CLZ80/NC and NEZ80, with AC power supply incorporated.

The RCZ80 cassette recorder with connection cable W10Z80, two NE-Z ROMs with programmed experiments and various component kits.

Together these parts form a complete NBZ80-S (Super) or Nanocomputer Training System, as shown in the photograph on the previous page.

Note that 'Gamma-bus' is the name of the SGS-ATES standard European Z80 microcomputer bus structure and is used in all of our microcomputer products.

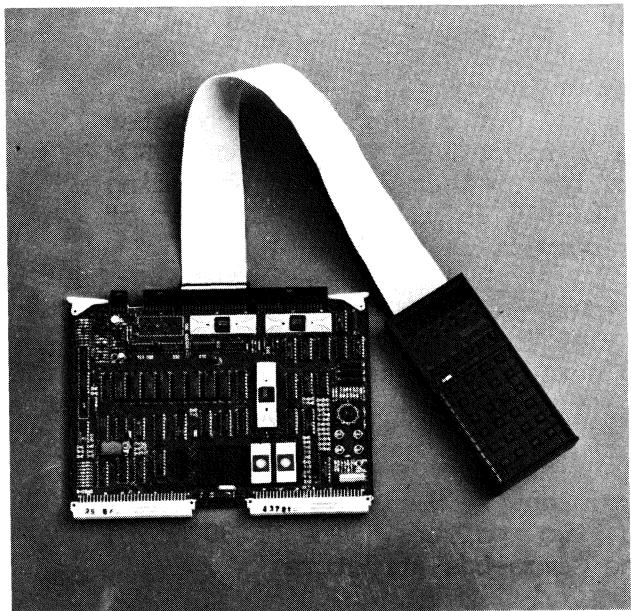

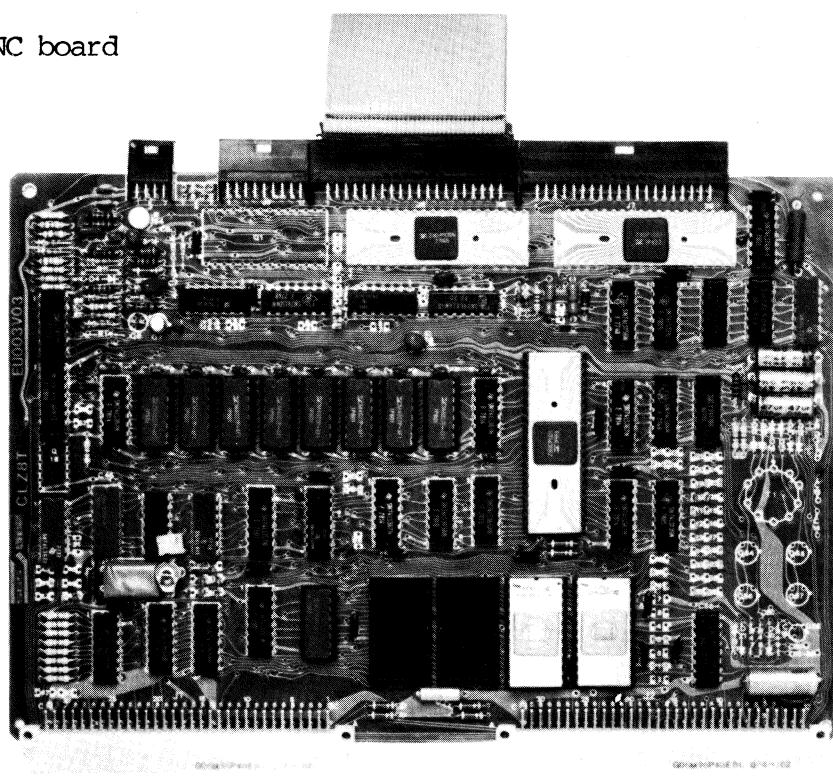

(1.1) CLZ80/NC board

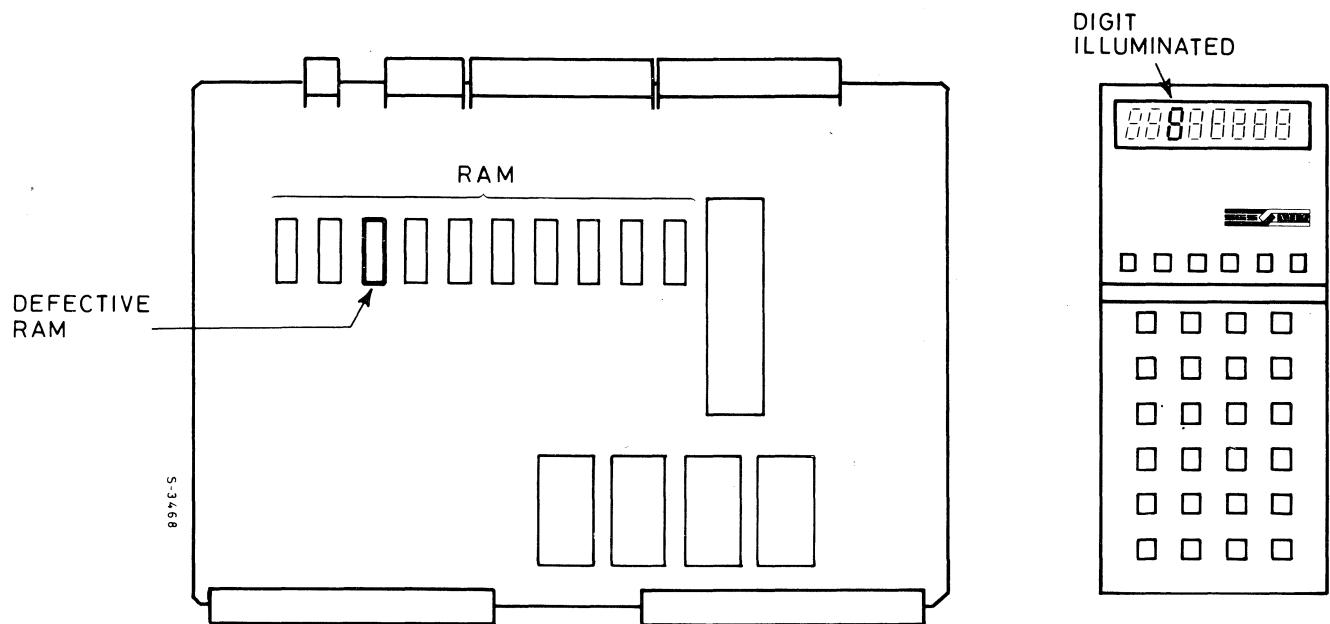

CLZ80/NC BOARD PHOTOGRAPH

The CLZ80/NC board of the NBZ80 Nanocomputer is in double Eurocard format with a Z80 CPU. The microcomputer is assembled on a double sided printed circuit board.

The board carries 4K RAM and 2K EPROM or ROM but can be expanded to up to 16K RAM and 8K EPROM/ROM by modifying some links on the board. The CLZ80/NC board is also laid out for easy upgrading to a CLZ80 microcomputer using kit KNZ80 which adds a USART, DC-DC converter and other components as well as the MO-Z monitor software.

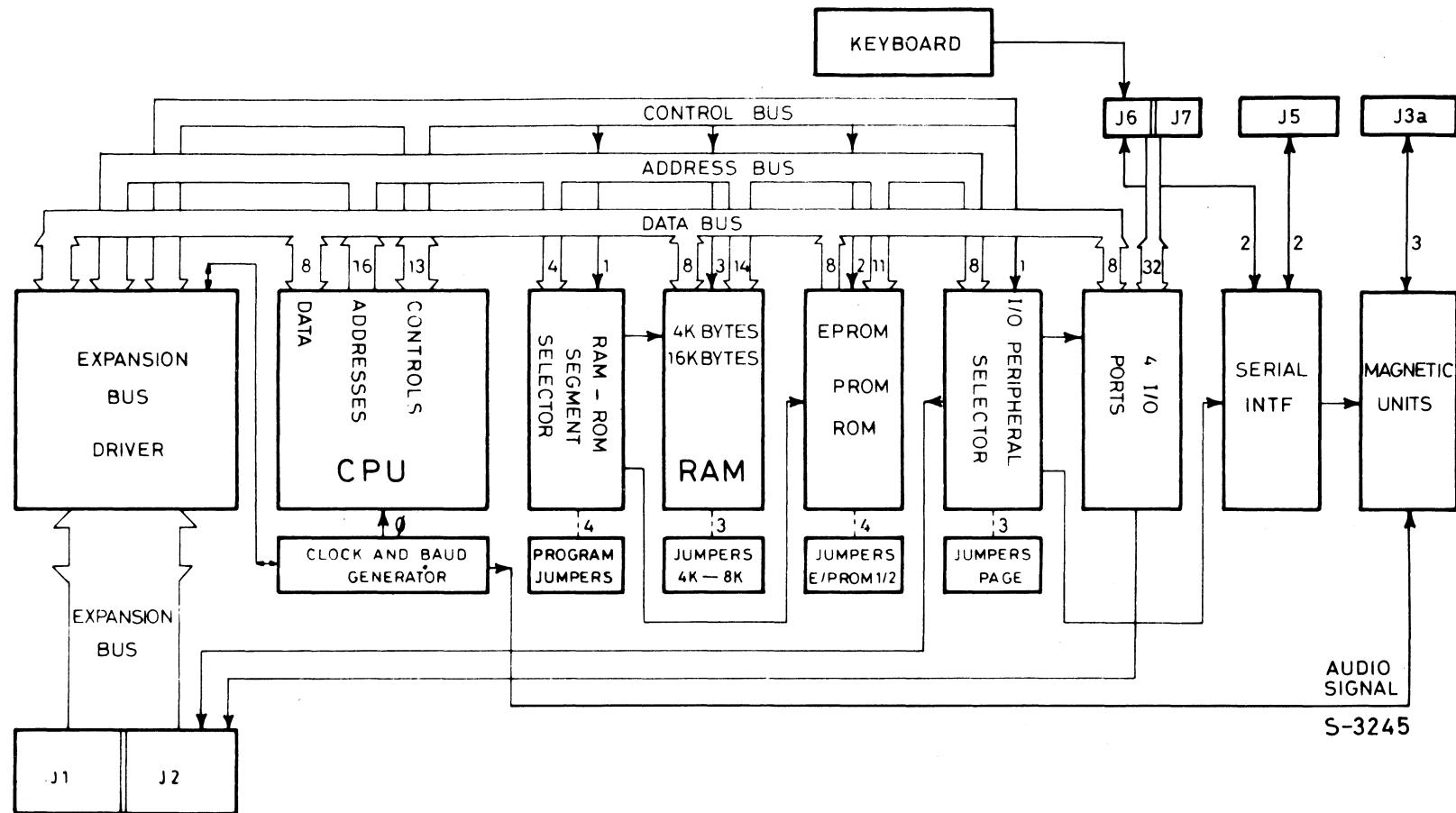

The internal bus structure consists of three buses :

Data Bus (8 bits)

Address Bus (16 bits)

Control bus (13 lines)

The signals from these buses are interfaced to connectors J1/J2 of the Gamma-bus by bidirectional buffers and drivers. The Z80CPU is connected directly to the internal buses. The signal for the NMI (Non-Maskable Interrupt) comes from the BREAK key of the keyboard via connector J6. The RESET signal comes in the same way from the RESET key. The Z80 CPU uses a 2.4756MHz clock (the odd frequency is because in the upgraded CLZ80 version this clock signal is divided down to obtain the various transmission and reception speeds (baud rates) for

## CLZ80-NC BLOCK DIAGRAM

serial communications with the USART).

The ROM and RAM memories can be mapped anywhere in the range 0-FFFF(Hex), 0-64K(Dec), address space by the RAM and ROM memory segment selector. The various partitions are selected by links on the board.

The addresses of the ports of the PIO's are determined by the "device select" and can be mapped via links in segments of 32 addresses inside the space 0-FF (Hex) 0-256 (Dec).

The user who wants to use the board with his own programs (without NC-Z monitor) has freedom of memory mapping and address assignment of I/O ports.

The reset circuit provides a small program in ROM with a jump instruction which is executed by the CPU when the Reset key is pressed. The Reset key resets the CPU (see Z80CPU Technical Manual for details) and activates the Reset Circuit. The jump made is to the start address of the NC-Z operating system program memorized in EPROM or ROM.

An interface circuit for a serial terminal suitable for communications in RS-232 mode, in 20mA current loop or at TTL levels is provided. Using the TTY<->CASS switch on the keyboard display it is also possible to select the Audio Cassette interface.

The serial signals for both "TTY" and "CASS" are generated by the software and the input/output is taken from the PIO (Q2) port A.

A control signal for start-stop of the cassette recorder is provided by the software. The standard NBZ80 Nanocomputer with NC-Z software controls the RCZ80 cassette recorder connected to connector J3.

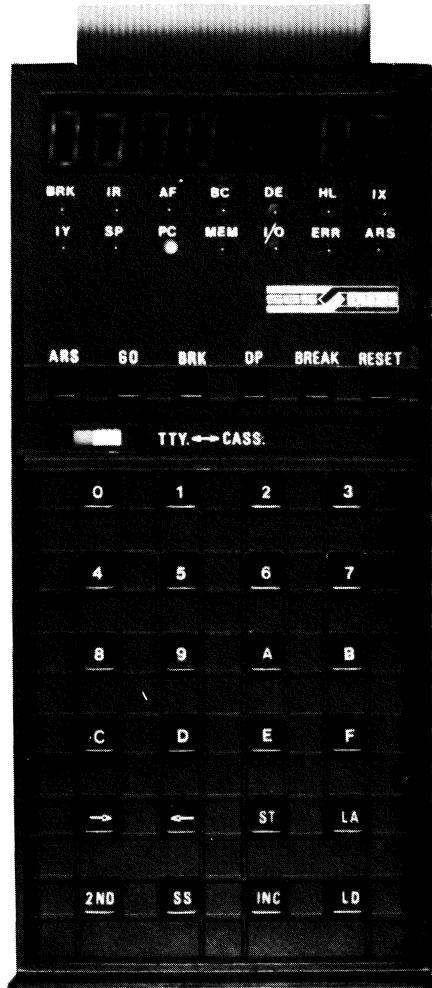

## (1.2) NKZ80 KEYBOARD/DISPLAY

The NBZ80 Nanocomputer with NC-Z software program uses the portable NKZ80 keyboard/display as input/output unit.

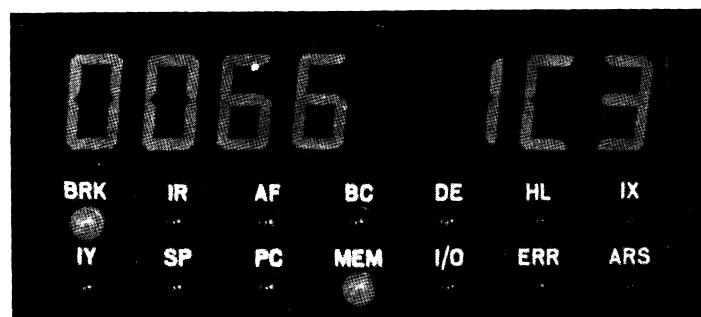

The keyboard display enables the user to communicate in hexadecimal machine language with the microcomputer.

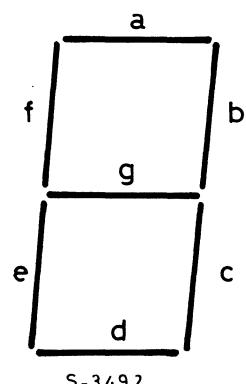

The 8-digit display provides data and address information.

The single LEDs indicate the registers displayed. The keys allow the input of data and addresses as well as the activation of various control functions.

The keyboard/display is connected to connector J6 of the CLZ80/NC board. The female connector on the flat cable has pin 1 identified by an arrow.

## NKZ80 KEYBOARD/DISPLAY

### \*\*\* IMPORTANT \*\*\*

If the female connector is inserted the wrong way round the keyboard/display can be damaged. There are arrowheads on the connectors indicating the correct orientation.

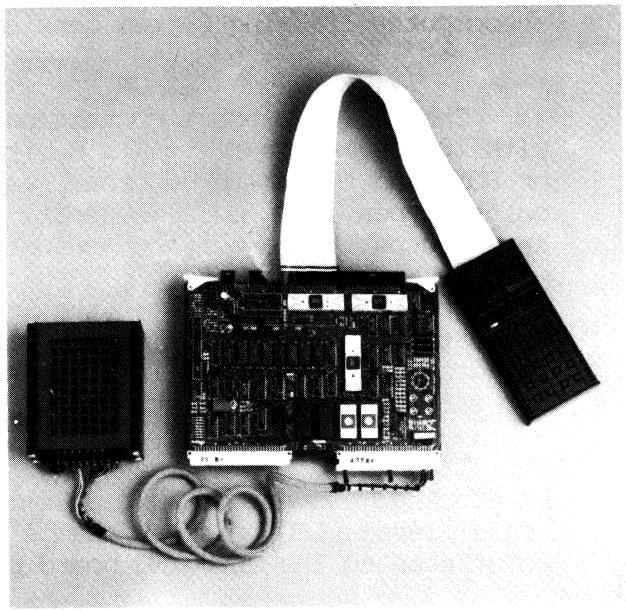

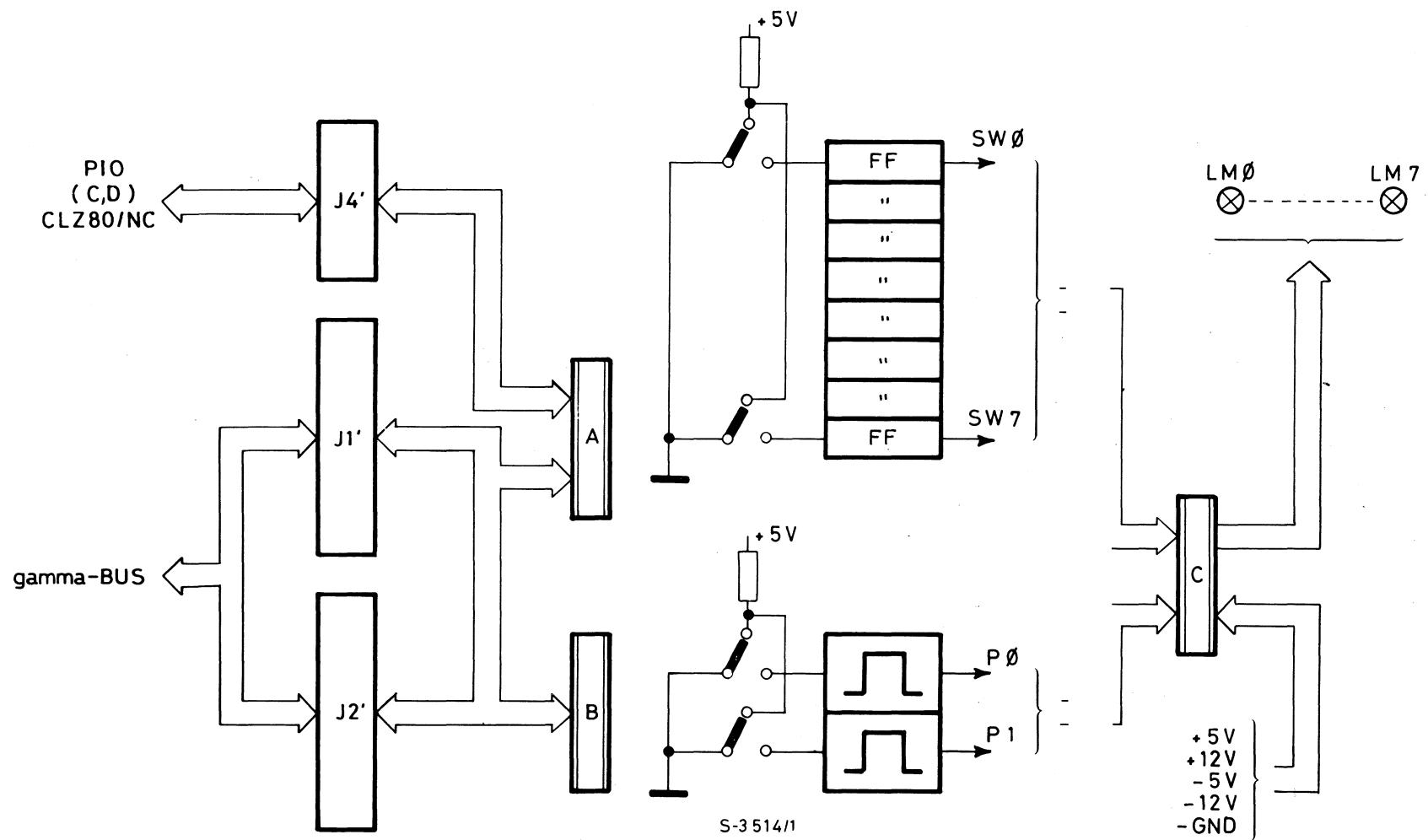

### (1.3) NEZ80 EXPERIMENT BOARD

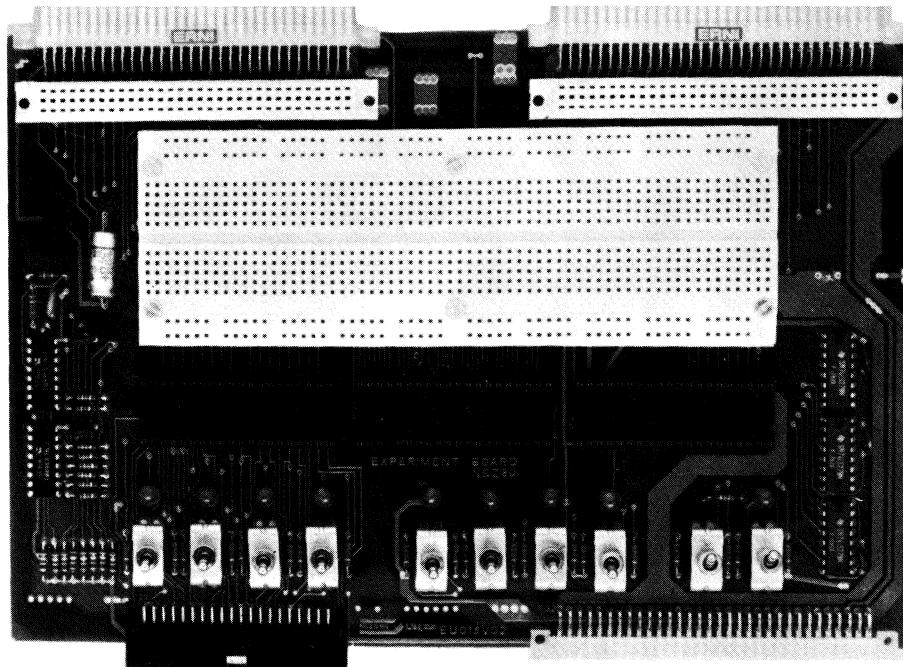

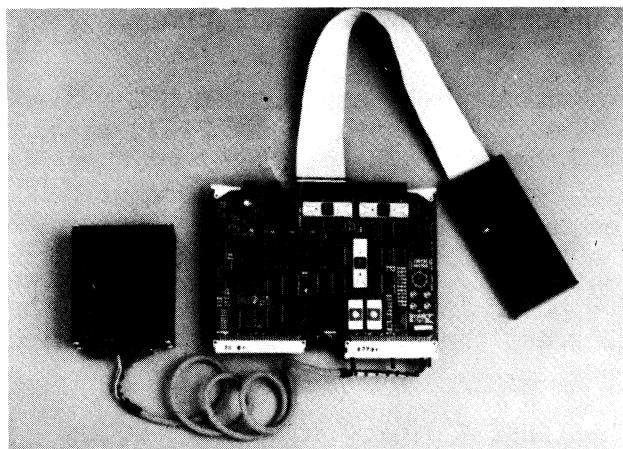

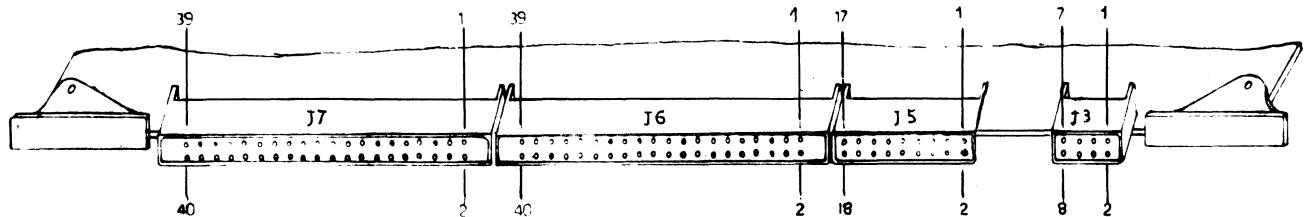

NEZ80 BOARD PHOTOGRAPH, WITH SOCKETS K4Z80 FITTED

The NEZ80 experiment board has been designed to allow the user to carry out interface experiments using the signals available on the CLZ80/NC Gamma-bus together with an 8-bit word generated by 8 switches and two positive or negative strobe pulses generated by two spring loaded switches. It is also possible to display the logic level of 8 signals by means of LED lamps.

The NEZ80 board is in double eurocard format with a double side printed circuit board and contains :

- a solderless board on which to insert user connections and components

- 8 debounced logic switches

- 8 LED logic indicators and drivers

- 2 debounced pulsers

- 2 sockets for experiment Gamma-bus to board interfacing

- 1 socket for signal interfacing and supplies

The signals coming from the CLZ80/NC Gamma-bus through connectors J1 and J2 are wired to two 40-pin sockets on the board.

The signals on J4 coming from the PIO (ports C and D) of the CLZ80/NC board via a multiway cable are also connected to the 40-pin sockets.

The 8 switches with debounce logic provide TTL logic levels '1' or '0' on the 40-pin sockets. Eight logic inputs to the LED drivers are available on the 40-pin sockets where logic level '1' = LED 'ON' and logic level '0' = LED 'OFF'.

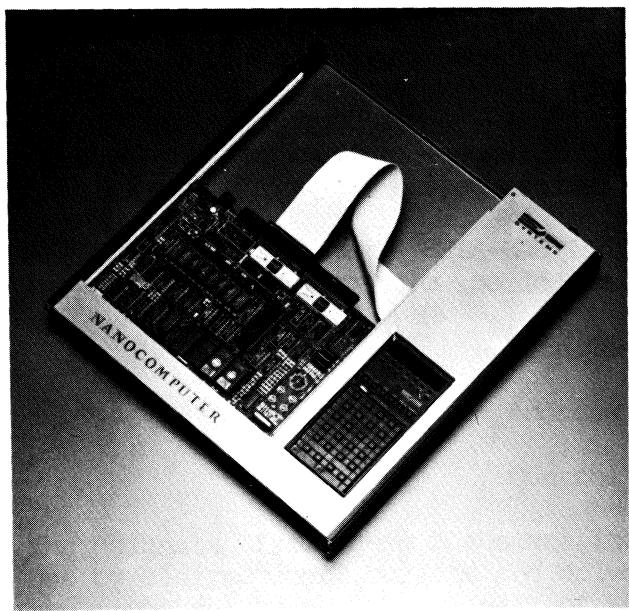

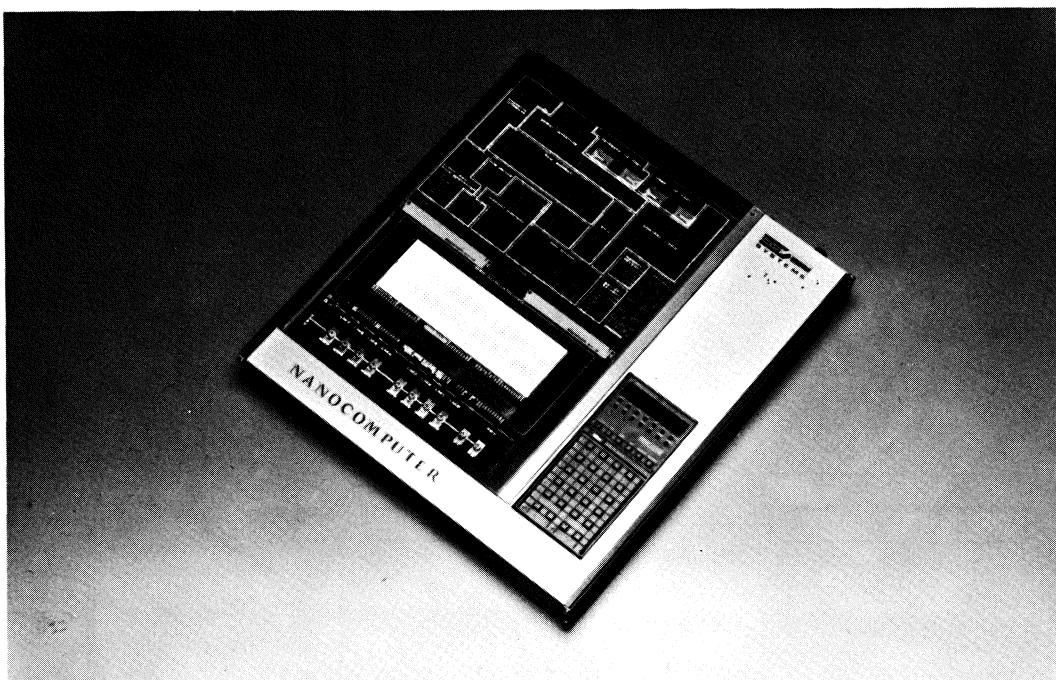

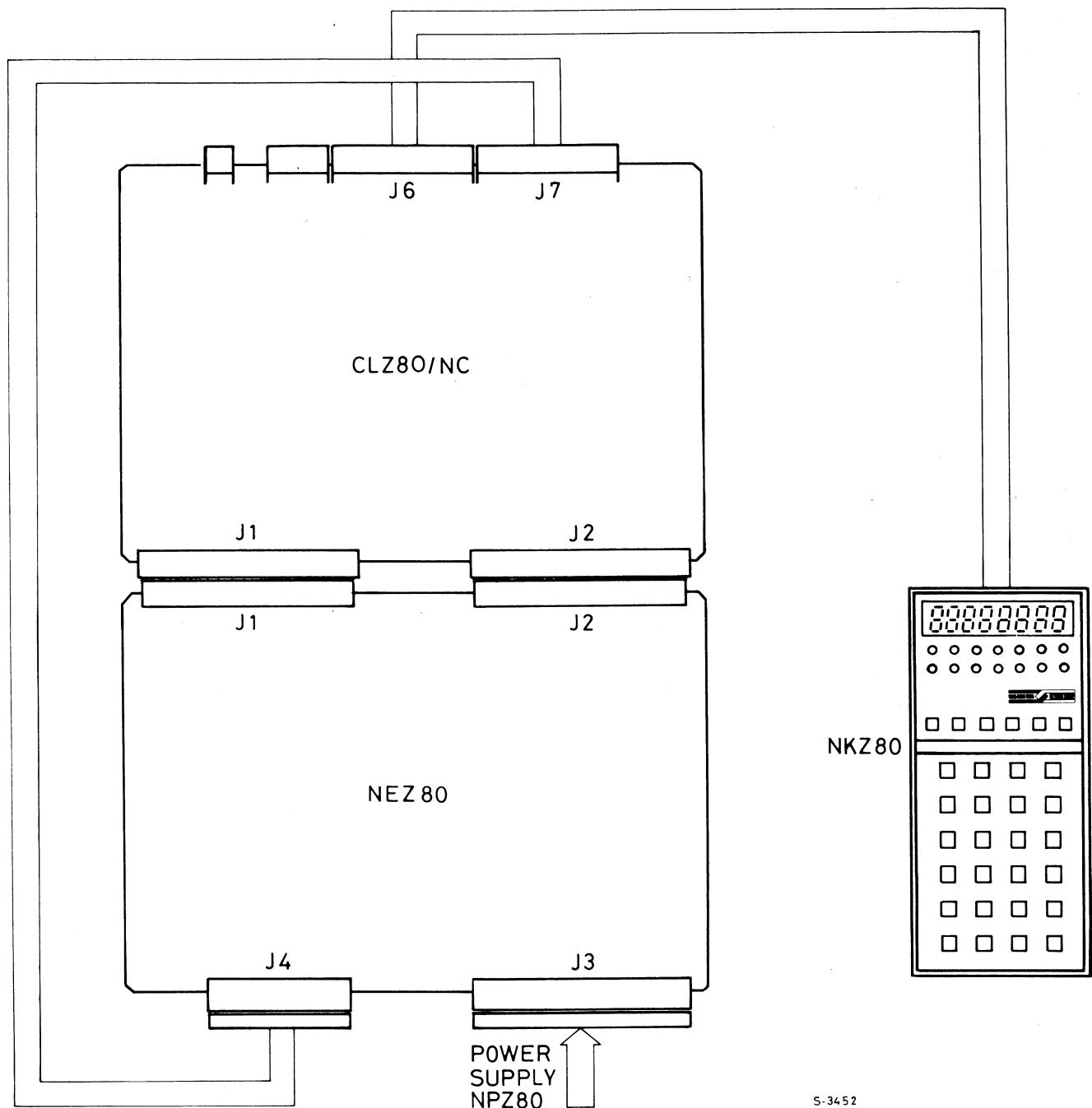

#### (1.4) NANOCOMPUTER SUPER NBZ80-S

NBZ80-S PHOTOGRAPH

The Nanocomputer super NBZ80-S is a system formed by

|                  |                                     |

|------------------|-------------------------------------|

| CLZ80/NC + NKZ80 | Nanocomputer with keyboard display  |

| NEZ80            | Experiment board                    |

| NPZ80            | Card frame with supply incorporated |

The two cards CLZ80/NC and NEZ80 are inserted in series into the flat card frame NPZ80.

A flexible multiway cable is used to carry PIO signals from connector J7 on the CLZ80/NC board to the NEZ80 board connector J4.

This cable has pin 1 of the female connector identified by an arrow. One end of the cable should be plugged into NEZ80 J4 before this board is mounted in the

card frame.

The supply for the NEZ80 board is provided on connector J3.

S-3452

## (2) INSTALLATION OF THE SYSTEM

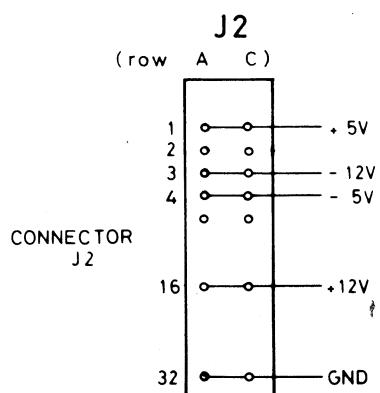

For the single CLZ80/NC board a supply with the following ratings is required :

|             |       |

|-------------|-------|

| + 5V +/- 5% | 800mA |

| - 5V +/- 5% | 200mA |

| +12V +/- 5% | 100mA |

| -12V +/- 5% | 100mA |

It is recommended to use the NSZ80 supply, which has an output cable provided and plugs directly into J2 (CLZ80/NC).

### NBZ80A AND NBZ80B CONNECTIONS

If other supplies are used a suitable female connector is required to carry the supply to connector J2 of the Nanocomputer as shown

S-3526

### POWER CONNECTIONS

For the NBZ80-S verify that the boards are mounted correctly in the card frame and the Data input/Display station and PIO/NEZ80 cables are connected before powering up the Nanocomputer.

#### (2.1) AC MAINS CONNECTION

The NPZ80 and NSZ80 supplies have European standard cable. The supplies are internally adjusted for 220 - 240V operation (or 110 - 120V operation, if specifically requested by the user).

The supply connections are :

|              |                |

|--------------|----------------|

| Green/Yellow | EARTH          |

| Brown        | SUPPLY live    |

| Blue         | SUPPLY neutral |

It is strongly recommended that an earth connection be used at all times.

#### (2.2.) SYSTEM SWITCH-ON AND RESET

When the connections have been made

**CHECK THEM AGAIN!**

Then apply power to the system. If the NEZ80 board is included in the system the LED indicating the +5V supply will light. Press the RESET button once or twice to 'wake up' the Nanocomputer.

The display should light with 0000 in the first 4 digits from the left and a number displayed in the first 2 digits from the right. The PC LED indicator should be lit. If the display does not come on properly try again. Should the trouble persist call your supplier for help.

### (3) CLZ80/NC - CIRCUIT DESCRIPTION

The schematic diagram of the CLZ80/NC Nanocomputer board is included at the end of this book in a fold-out form (EEU00325 and EEU00326). Also included is a component layout diagram (EEU00327). EEU00325 shows the CPU, Gamma-Bus interface, EPROM/ROM and RAM with relative control and timing circuits and the pin connections for J1 and J2. EEU00326 shows the input/output ports, interface circuits (RS232, TTL, 20mA current loop & cassette recorder interface) the initialization and clock generation circuits as well as the pin connections for J3, J5, J6 and J7 and the tables showing the links for selecting various configurations.

#### (3.1.) CPU

The Z80 CPU Q29 address bus outputs AD0 to 15 are connected to the 3-state buffers T74LS365/7 Q40/41/42. The local CPU is able to address the buffered address lines BAD0-15 (also called BA0-15 on the Experiment Board NEZ80) when BUSAK is not true. This is always the case for the Nanocomputer system but if the board were included in a system with more processors then another CPU could access the local memory after a BBUSRQ and acknowledgement by the local CPU (BUSAK true). The data bus D0-7 is buffered by T74LS365/7 Q44/46/30 for input and output transfers. These gates are enabled by DBOUT and DBIN described later.

The CPU HALT output is buffered by T74LS367 Q39 and the signal BHALT is available on the Gamma-Bus at J1-18C and on the Experiment board. The output drive is sufficient to drive a LED monitor lamp to indicate a software HALT State.

The CPU BWAIT (wait) input comes directly from the Gamma-Bus J2-26C. There is a pull-up resistor R52 of 910 ohms to +5V so BWAIT should be activated only by an open collector gate.

The CPU BINT (interrupt) input is derived from the PIO chips via the wired-or open collector gates, T7417 Q32 (EEU00326) or from an external interrupt input on the Gamma-bus J2-24c. There is a pull-up resistor R46 of 910 ohm to +5V so this input should be activated only by an open collector gate.

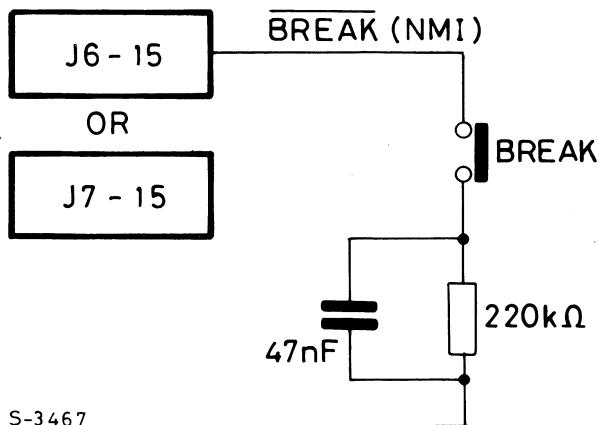

The CPU BNMI (non maskable interrupt) comes from the Gamma-bus J2-23c and from the BREAK signal via the open collector buffer T7417 Q32. There is a pull-up resistor R45 of 910 ohm to +5V so BNMI should be activated only by an open collector gate.

The open collector buffer T7417 Q3 drives the BNMI input from the BREAK signal. The BREAK signal is generated by the keyboard 'Break' key which connects the BREAK input J6-18c to ground via a 47nF capacitor. This, together with the resistor R32 of 33 ohm, produces the narrow (<400nS) NMI pulse needed by the

CPU.

The CPU RESET signal is generated from the BRESET input on J1-28c. J6-4 or J7-4. In the Nanocomputer system the 'RESET' key on the keyboard connects J6-4 via a 47nF capacitor to ground to produce a reset pulse. This pulse is inverted by the T74LS14 Q11 and stretched by the 1KpF capacitor on the output of the inverter Q11 pin 2 to generate the CPU reset pulse. Other reset signals can be sent to this line via open collector gates. The BRESET line is protected from overvoltage transients by D8/C7/D9. It is pulled up by a 910 ohm resistor R17 to +5V so this input should be activated by open collector IC drivers only.

Finally the CPU BBUSRQ (Bus request) comes from the Gamma-Bus J2-25c. There is a pull-up resistor R53 of 910 ohm to +5V so BBUSRQ should be activated only by an open collector gate.

The 2.4576 MHz CPU clock comes from the clock generator F4702 Q34.

### (3.2.) Gamma-Bus interface

The Gamma-Bus interface is a complete set of buffered input/output signals that enable the board to be used in bus orientated microcomputer systems. For a complete definition of the pin connections see chapter 5 and for the signal specifications and timing see also chapter 5.

The T74LS365 and 367 gates Q40/41/42/45/46 and Q30/39 provide the bus buffering for the Gamma-bus signals.

The address bus BAD0-15 (the same as BA0-15) and the memory and I/O control signals BMREQ, BIORQ, BRD, BWR, BMI and BRFSH are disabled only by the local CPU BUSAK output.

The data bus outputs BD0-7 are enabled by DBOUT and the data bus inputs by DBIN. These two signals are derived from the decoder T74LS156 Q12 which adjudicates the various requests both internal and external (via BUSAK) for access to the bidirectional data and address buses.

The system clock (= 2.4576 MHz) and the FCU signal (equal to clock/8 = 307.2kHz), which is used in the upgraded systems (CLZ80) to drive the DC-DC power supply converters, are available on the Gamma-bus buffered by T74LS367 Q39.

The interrupt enable output IE0 J1-13c is derived from the two Z80 PIO chips and can be used to extend the interrupt priority daisy chain with the on - board PIOs always defined as having highest (Q2) and next highest (Q3) priority.

The partially decoded signals IOQ0-3, IOE0-3 and IOU0-3 are described later under Device Select decoding.

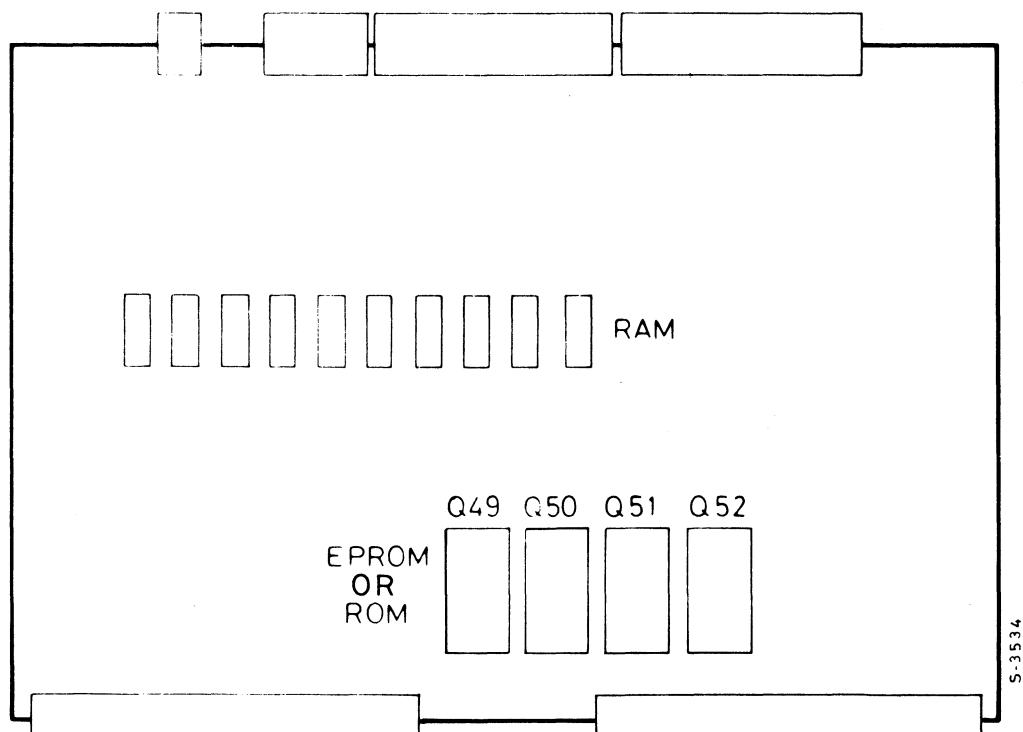

### (3.3.) EPROM/ROM

The Nanocomputer board is designed for using either 1Kx8 or 2Kx8 memories, for example M2708, M2716 or M2316E types. Both EPROMs, requiring multiple supplies, or ROMs, using single +5V supplies, can be used.

The sockets Q49-52 carry the memory chips and the electrical connections are selected by the jumpers, 1 to 8.

The CLZ80/NC board may be supplied in one of two versions, using either two M2708 (1Kx8) EPROMs for the NC-Z program, or using an M2316E (2Kx8) ROM. The alternative jumper connections are shown in the table which also gives the type of device supplied and the links.

The memories are addressed by the buffered address lines BADO-10 and the data is read onto the internal data bus D0-7. In this way an off-board circuit (CPU or DMA for example) can read the memories as well as the local CPU (after enabling the data bus to the outside).

### (3.4.) ROM CONTROL

Section A of the T74LS139 Q58 decoder is used to select, via jumpers 9 or 10, whether the ROM address segmentation is 4 or 8K. The CLZ80/NC board is supplied with 4K segmentation for M2708 or 8K for M2316E, but either can be changed if the user wants to insert another type of memory. The address of the segment is fixed by the MEMORY SELECT (see below).

### (3.5.) RAM

The CLZ80/NC board provides 4Kx8 dynamic RAM (upgradeable to 16K) with refresh by the Z80CPU. The RAM chips M4027 Q20-27 require multiplexed addressing which is provided by MA0-5 (& MA6 for 16K chips) from RAM CONTROL. These lines provide two addresses to the RAMs for each memory read or write operation, one for ROW and one for COLUMN of the RAM memory. Latching of the row and column addresses is by the inputs RAS and CAS. These signals are generated by RAM TIMING.

The RAM data inputs are connected to the internal data bus D0-7. The outputs M00-7 are buffered onto the internal data bus by the 3-state gates T74LS367 Q19 and Q28. These 3-state gates are enabled by the LETRA signal (lettura RAM = read RAM) from RAM TIMING. Writing to the RAM is made by the WRM signal.

### (3.6.) RAM TIMING

In a Z80 system a memory access is signalled by a MREQ output and an RD or WR signal. When using dynamic RAMs the Z80 CPU also provides refresh address on A0-A6 and a control signal RFSH which must be used to enable only the ROW addresses of the RAM (via RAS).

The lower part of the timing circuit formed by Q33 generates the RAS signal following the input PAGRA (Page of RAM) from MEMORY SELECT. After a delay due to the propagation time of T74LS04 Q36 and two T74LS04 Q36 the SELAD signal is produced which goes to RAM CONTROL to switch the address from ROW to COLUMN on MA0-6 (7). After a further delay, for the multiplexer Q37, Q47 to switch and the RAM address set-up time, the ICAS signal is generated.

The ICAS signal is passed through the multiplexer T74LS157 Q37 which gives a further delay before outputting the CAS signal on output ZD to the RAMS.

If only a memory refresh is required then the T74LS02 Q33 NOR gate with inputs BMREQ and BRFSH generates an input to the next gate pin 2 which generates RAS. The SELAD and ICAS signals are however inhibited by the application of BRFSH to the gate T74LS00 Q35.

To read the RAM output data onto the data bus a LETRA signal is generated by T74LS00 Q35 pin 8. This signal is generated by BRD and PAGRA but is inhibited by the presence of PROMSEL. The reason for this is that PROMSEL is generated when the RESET PROM Q48 is outputting data and this must not clash with RAM outputs. The RAM and the Reset PROM can have the same address space (0000-0002) so the Reset signal, which clears the T74LS74 Q4, generates PROMSEL (active high) and switches the active data stream from the RAM to the Reset PROM.

Finally the RAM timing for write signal WRM. The generation of WRM is delayed in case an off-board CPU or DMA wants to write to the internal RAM. In this case the data will not be present until the decoder T74LS156 Q12 has enabled DBIN to bring the BDO - 7 data into D0-7. To overcome this decoding delay and ensure the RAM data is set up, the BWR signal is delayed by the capacitor of 100pF C8 on the output of T74LS04 Q36 pin 10. This delay has no effect on internal CPU write cycles as there is always an adequate timing margin with the Z80 CPU operating at 2.5MHz.

### (3.7.) RAM CONTROL

The two multiplexers T74LS157 Q37 and Q47 switch the buffered address lines for row and column addressing of the RAM memory. The jumpers 39 to 44 select the correct address lines for 4K or 16K RAMs according to the table .

### (3.8.) MEMORY SELECT

In the Nanocomputer the EPROM or ROM is located in the upper address area between 60K and 64K and the RAM is located in the lower address area between 0 and 4K.

The NC-Z monitor is designed for ROM and RAM located at these positions, however for completeness the tables show the position for the links 11-26 for alternative memory mapping.

### (3.9.) DEVICE SELECT

The Z80 CPU addresses up to 256 I/O parts (by a decode of BAD0 to 7) and by activating the IORQ and either RD or WR signals. This means that the I/O ports can have the same addresses as memory locations (for which MREQ is active).

On the CLZ80/NC board partial decoding is provided for the I/O ports. The signals IOQ0-3 and IOE0-3 from T74LS138 (Q53) are decodes of the address lines BAD2 to BAD7 giving active signals for page 0 addresses in the range 0 to 31 as follows :

| Addresses | Active (low) | Addresses | Active (low) |

|-----------|--------------|-----------|--------------|

| 0 - 3     | <u>IOQ0</u>  | 16 - 19   | <u>IOE0</u>  |

| 4 - 7     | <u>IOQ1</u>  | 20 - 23   | <u>IOE1</u>  |

| 8 - 11    | <u>IOQ2</u>  | 24 - 27   | <u>IOE2</u>  |

| 12 - 15   | <u>IOQ3</u>  | 28 - 31   | <u>IOE3</u>  |

In the CLZ80/NC using NC-Z software it is incorrect to select a page other than page 0 since the keyboard would no longer be addressed by the NC-Z monitor software.

The user however, with his own software, might need to select another page so by means of jumpers according to the table the decoded page can be changed in blocks of 32 addresses. The internal composition of each page remains unchanged.

The signals IOU0-3 from T74LS139 Q38 are decodes of BAD0, BAD1 enabled by BIORQ which are thus active only for I/O operations but not for memory access. These signals are decoded if BIORQ is active :

| Addresses | Active      |

|-----------|-------------|

| 0         | <u>IOU0</u> |

| 1         | <u>IOU1</u> |

| 2         | <u>IOU2</u> |

| 3         | <u>IOU3</u> |

5-3484

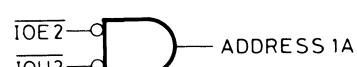

Obviously each single peripheral address can be decoded by a simple two input gate :

Some addresses however are already assigned to devices as shown in the table below :

|             | <u>IOU0</u> | <u>IOU1</u> | <u>IOU2</u> | <u>IOU3</u> |                |

|-------------|-------------|-------------|-------------|-------------|----------------|

| <u>IOQ0</u> | 00          | 01          | 02          |             | <b>FLAG IN</b> |

| <u>IOQ1</u> | Data A      | Data B      | Cont.A      | Cont.B      | PIOQ2          |

| <u>IOQ2</u> | Data C      | Data D      | Cont.C      | Cont.D      | PIOQ3          |

| <u>IOQ3</u> | 0C          | 0D          | 0E          | 0F          |                |

| <u>IOE0</u> | 10          | 11          | 12          | 13          |                |

| <u>IOE1</u> | 14          | 15          | 16          | 17          |                |

| <u>IOE2</u> | 18          | 19          | 1A          | 1B          |                |

| <u>IOE3</u> | 1C          | 1D          | 1E          | 1F          |                |

### (3.10.) FLAG INPUT

An unusual feature of the NBZ80 design is the ability to read the status of the PIO 'Ready' lines.

The PIO Ready lines are :

| PIO signal   | CLZ80/NC sig. | NEZ80 sig. |

|--------------|---------------|------------|

| PIO(Q2) ARDY | FLPA          | -          |

| BRDY         | FLPB          | -          |

| PIO(Q3) ARDY | FLPC          | CRDY       |

| BRDY         | FLPD          | DRDY       |

The I/O address 03H (H = Hexadecimal) is decoded by the 'OR' gate T74LS32 Q16 pin 2 (EEU00326) and with the BRD signal generates LETF (Lettura Flag= read flags). This signal is applied to the 3-state buffers T74LS367 Q28 and Q19 (EEU00325) to gate the state of the PIO flags onto the data bus during the read cycle.

| Flag        | DB bit |

|-------------|--------|

| FLPA        | D0     |

| FLPB        | D1     |

| FLPC (CRDY) | D2     |

| FLPD (DRDY) | D3     |

### (3.11.) INPUT/OUTPUT PORTS A-B-C-D

The two Z80 PIOs on the CLZ80/NC board provide 32 lines of I/O.

The PIO address input for selection of gates A or B or C or D are direct from address bus BAD0 - BAD1 and the chip enable CE is a direct connection to IOQ1 and IOQ2.

The Input/Output data for the PIO Q2 are available on connector J6 and for PIO Q3 on J7.

In the Nanocomputer system the PIO Q2/J6 is connected to the keyboard.

The keyboard provides the following links :

| signal |     | connected to |      |

|--------|-----|--------------|------|

| J6-21  | PA5 | ICAS1        | J6-5 |

| J6-19  | PA6 | ICAS2        | J6-6 |

| J6-17  | PA7 | RxD          | J6-7 |

| J6-23  | PA4 | TxD          | J6-3 |

### (3.12.) INTERRUPT

The PIO Q2 IEI (Interrupt Enable Input) is connected to +5V making this the highest priority in the interrupt daisy chain. IOE1 is the daisy chain output of the first PIO Q2. The two PIO output signals IOE1 and IOE2 are combined to form a single output IEO by T74LS08 Q15. The INTAB output from PIO Q2 and the INTCD from PIO Q3 are combined to activate the BINT line by T7417 Q32.

### (3.13.) CASSETTE CONTROL

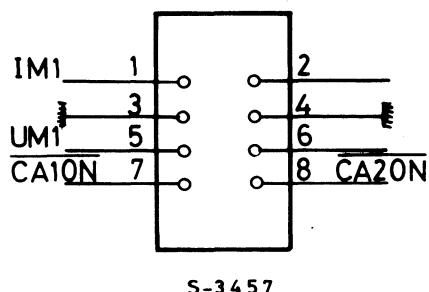

The motor on/off of the audio cassette recorder is controlled by T7416 Q8. The ICAS signals come via the keyboard, plugged into J6, from the PIO Q2A.

| PIO (Q2) | Signal | Cassette control |

|----------|--------|------------------|

| PA5      | ICAS1  | <u>CALON</u>     |

| PA6      | ICAS2  | <u>CA2ON</u>     |

However only CALON is used by the Nanocomputer. When CALON is low (PA5 high, ICAS1 high) the motor is stopped.

### (3.14.) CLOCK AND BAUD GENERATOR

The F4702 Q34 oscillator at 2.4576 MHz is the master clock.

The divided outputs are :

SICK - Serial interface clock ( $f = 9.6\text{kHz}$  for the 600 baud setting of jumpers 45 and 51), used by Nanocomputer to generate an audio signal of  $4.8\text{kHz}$

FCU - Signal used by DC-DC converters (when fitted) at  $f = 307\text{kHz}$ .

The Multiplexer T74LS157 Q44, used very little on the NBZ80 board, is used to switch the baud rate between 110 - 9600 baud serial I/O and 600 baud Audio I/O when the board is upgraded to a CLZ80 Microcomputer and uses a USART.

### (3.15.) SERIAL INTERFACES

There are three types of serial interface at RS232,  $20\text{mA}$  current loop and TTL levels. These are supplied by circuits T74LS14 Q11, T74LS04 Q9 and T74LS00 Q10 for input and by T74LS04 Q31 Q9, T74LS32 Q13, T7416 Q8 and BSX36 Q7 for output. The jumpers set the interface standard according to the table.

A second interface is for an audio cassette. The output signal UML of  $4.8\text{ KHz}$  is generated by the T74LS74 Q17 which divides SICK by 2. This signal is gated by the transmit data signal TXD. The audio level can be adjusted by potentiometer R54. The nominal amplitude of UML is  $200\text{mV}$  p-p from a impedance of  $100\text{ ohm}$ .

The audio input is to the OUTPUT RECORDER RECTIFIER which is a full wave peak detector using two op-amps LS147 Q5. The input impedance is about  $20\text{ Kohms}$  and a signal of  $300\text{-}400\text{mV}$  is required. The received data signal INM leaving amplifiers Q5 goes to the data selector T74LS00 Q10 via the schmidt trigger gate T74LS14 Q11. The signal MAG which switches the system from serial I/O to Audio Cassette comes from the keyboard on J6-1. MAG low = Audio cassette.

### (3.16.) INITIALIZATION CONTROL

To make the Z80 CPU execute a jump instruction to the entry point of the NC-Z program when the Reset key is pressed the PROM 6331 Q48 contains the op.codes

C3 02 FC (FC02 = entry point address).

When the RESET signal is active the 2 stage shift register made up of T74LS74 Q4 is reset and the PROM Q48 is enabled (PROMSEL signal low). The contents of Q48 locations 0, 1 and 2 are read by the CPU onto the data bus in three successive op-code fetch M1 cycles thus executing a jump to NC-Z program. After the three op-codes for the jump have been fetched and there have been three M1 pulses the '0' input on pin 2 will have been shifted along to the output pin 9 and PROMSEL is deactivated.

#### (4) CONNECTORS, CABLES AND BOARD LINKS ON THE CLZ80/NC

##### (4.1.) CONNECTORS

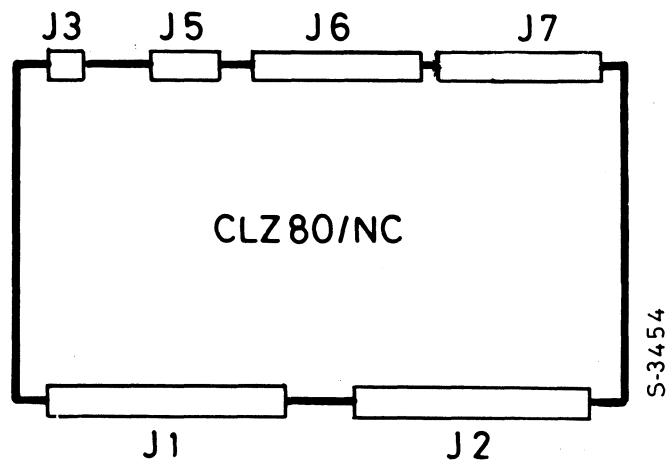

The CLZ80/NC board has six multiple connectors as shown in diagram EEU00327.

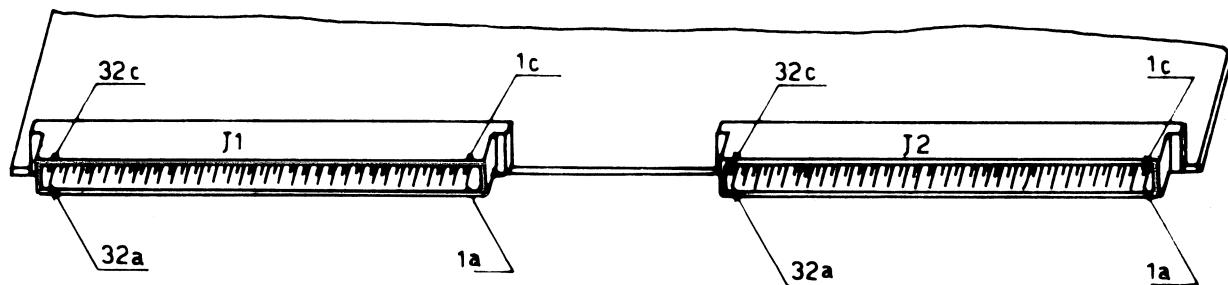

The two connectors on the lower

edge of the board, J1 and J2, are

standard Euroconnectors with two

rows (a and c) of 32 pins each.

These connectors are used for the

Gamma-bus interface and power

supply input.

#### CLZ80/NC BOARD CONNECTORS

Along the top of the board are 4 connectors as follows :

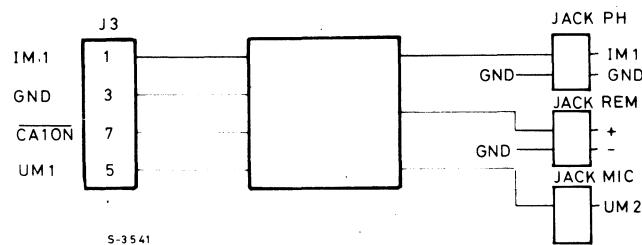

J3 Audio cassette input/output and control signals

J5 Serial terminal interface

J6 PIO Q2 input/output and system control signals. The keyboard/display is connected to this connector.

J7 PIO Q3 Input/output and system control signals. The signals from J7 are taken via a flat flexible cable to connector J4 of the experiment board.

Mating plugs are available in two kits for J1 to J7 as follows :

| Connector      | Kit                     | Description                                                     |

|----------------|-------------------------|-----------------------------------------------------------------|

| J1, J2         | C2Z80<br>C3Z80<br>C4Z80 | Two female connectors - wire wrap<br>- PCB mounting<br>- solder |

| J3, J5, J6, J7 | C1Z80                   | Set of shells and 120 pins for these connectors                 |

S-3456

S-3456

CONNECTIONS OF J1 & J2

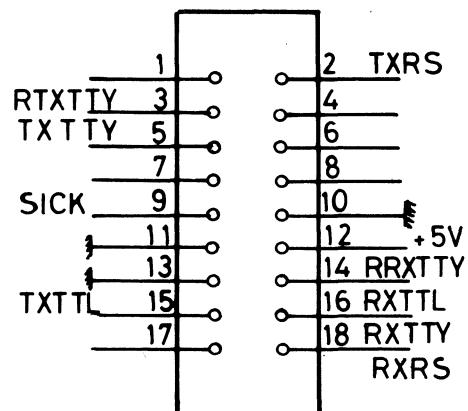

J 3

J 5

S-3458

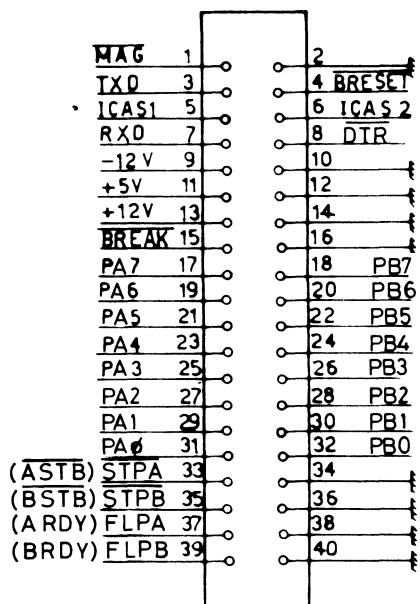

J 6

S-3459

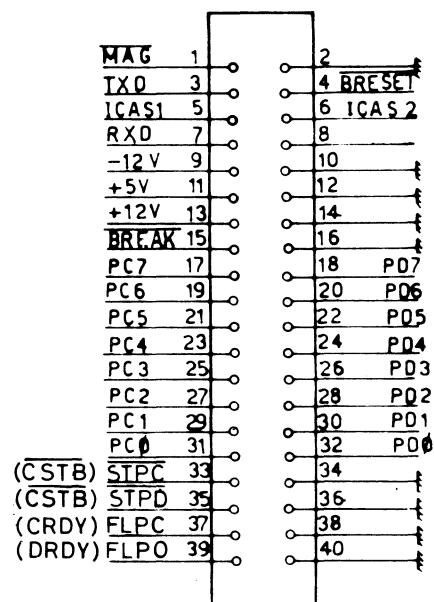

J 7

S-3460

CONNECTIONS OF J3, J5, J6 & J7

#### (4.2.) CABLES

Some ready made cables are available for connection to the CLZ80/NC board and peripherals.

W10Z80 Cable for connecting the RCZ80 cassette recorder to the CLZ80/NC board.

W15Z80 Cable for connection of the PIO Q3 signals (ports C & D) from the CLZ80/NC board J7 to the NEZ80 board J4.

CONNECTION OF A RECORDER TO J3 - W10Z80

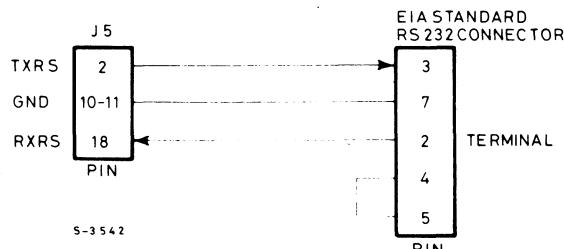

RS232 standard EIA interface cable is not available however connections for this use are as follows :

RS232 CABLE CONNECTIONS TO J5

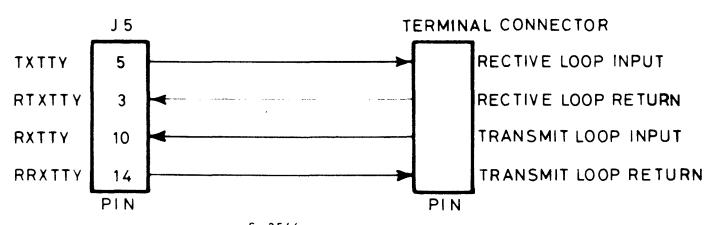

The cable for connecting the CLZ80/NC J5 to a TTY terminal with 20mA current loop must has the following connections :

20mA LOOP CONNECTIONS TO J5

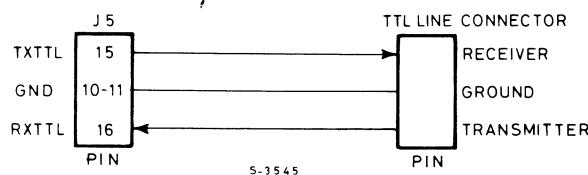

The cable for connecting the CLZ80/NC J5 to a TTL level peripheral has the following connections.

TTL INTERFACE CONNECTION TO J5

#### (4.3.) BOARD LINKS

The CLZ80/NC board can be adapted for :

(1) RAM type : 4K (M4027) or 16K (M4116) with RAM address in the range 0000-FFFF(Hex)

EPROM/ROM type : 1K (M2708) or 2K (M2716 or M2316E) with address in the range 0000-FFFF(Hex).

(2) Serial communication standards

- RS232

- 20mA current loop

- TTL

(3) Generation of blocks of 32 I/O addresses in the range :

|       |   |     |

|-------|---|-----|

| 0     | - | 31  |

| 32    | - | 63  |

| ..... |   |     |

| 224   | - | 255 |

A board layout showing the link positions is given at the end of this technical manual. The links are joined by a blob of solder across the exposed track areas.

## MEMORY TYPE

The RAMs used on the CLZ80/NC board are 4K M4072s but these can be replaced by 16K M4116s and the links changed

according to table 4.

The EPROMs/ROMs used on the CLZ80/NC board are either two M2708s (1K) or one M2316E (2K) for both NC-Z and NE-Z

programs.

The links for these or other ROMs are shown in table 1.

The address sequence for the EPROM/ROM sockets is shown in table 3A.

## MEMORY ADDRESSING

The RAM address for the 4K or 16K RAMs

TABLE 1

| EPROM-PROM-ROM SELECT |  | JUMPERS    |  |

|-----------------------|--|------------|--|

| 2708                  |  | 1 - 3 - 6  |  |

| 6381                  |  | 2 - 4 - 7  |  |

| 2716-1(2)             |  | 68 - 5 - 8 |  |

| 2716                  |  | 1 - 5 - 8  |  |

| 2316E                 |  | 1 - 5 - 8  |  |

TABLE 2

| 4K EPROM PROM-ROM PARTITION START-END |          | JUMPERS      |            |            |            |

|---------------------------------------|----------|--------------|------------|------------|------------|

| J<br>U<br>M<br>P<br>E<br>R<br>S       | 9        | 9            | 9          | 9          |            |

|                                       | 26       | 25           | 24         | 23         |            |

|                                       | 30<br>15 | 0K<br>4K     | 4K<br>8K   | 8K<br>12K  | 12K<br>16K |

|                                       | 30<br>16 | 16K<br>20K   | 20K<br>24K | 24K<br>28K | 28K<br>32K |

|                                       | 30<br>17 | 32K<br>w 36K | 36K<br>40K | 40K<br>44K | 44K<br>48K |

|                                       | 30<br>18 | 48K<br>52K   | 52K<br>56K | 56K<br>60K | 60K<br>64K |

TABLE 3

| 8K EPROM PROM-ROM PARTITION START-END |          | JUMPERS   |            |            |            |

|---------------------------------------|----------|-----------|------------|------------|------------|

| J<br>U<br>M<br>P<br>E<br>R<br>S       | 15       | 16        | 17         | 18         |            |

|                                       | 10       | 10        | 10         | 10         |            |

|                                       | 27<br>30 | 0K<br>8K  | 16K<br>24K | 32K<br>40K | 48K<br>56K |

|                                       | 28<br>29 | 8K<br>16K | 24K<br>32K | 40K<br>48K | 56K<br>64K |

TABLE 3A

| 1K EPROM/ROM |     | 2K EPROM/ROM |     |              |

|--------------|-----|--------------|-----|--------------|

| 1            | Q49 | 1            | Q49 |              |

| 2            | Q50 | 2            | Q50 |              |

| 3            | Q51 | 3            | Q51 | low address  |

| 4            | Q52 | 4            | Q52 | high address |

TABLE 4

| RAM CONNECTIONS            |      | JUMPERS      |  | SIZE    |

|----------------------------|------|--------------|--|---------|

| D<br>E<br>V<br>I<br>C<br>E | 4027 | 39 - 40 - 41 |  | 4K x 8  |

|                            | 4116 | 42 - 43 - 44 |  | 16K x 8 |

can be selected using the links shown in tables 5 and 6.

The EPROM/ROM address for 4 x M2708 (4K EPROM) or 4 x M2316 (8K ROM) or other

types can be selected using the links shown in tables 2 and 3.

#### I/O ADDRESSING

The board can generate partial I/O addresses in 32 address blocks. Each block can be selected by the links shown

in table 7.

#### SERIAL I/O

Standards of serial I/O can be selected using the links shown in table 8.

TABLE 5

| 4K - RAM<br>PARTITION<br>START-END |    | JUMPERS    |            |            |            |

|------------------------------------|----|------------|------------|------------|------------|

|                                    |    | 22         | 21         | 20         | 19         |

| J<br>U<br>M<br>P<br>E<br>R<br>S    | 11 | 0K<br>4K   | 4K<br>8K   | 8K<br>12K  | 12K<br>16K |

|                                    | 12 | 16K<br>20K | 20K<br>24K | 24K<br>28K | 28K<br>32K |

|                                    | 13 | 32K<br>36K | 36K<br>40K | 40K<br>44K | 44K<br>48K |

|                                    | 14 | 48K<br>52K | 52K<br>56K | 56K<br>60K | 60K<br>64K |

TABLE 6

| 16K - RAM<br>PARTITION |           | JUMPERS    |            |            |          |

|------------------------|-----------|------------|------------|------------|----------|

|                        |           | 31<br>11   | 31<br>12   | 31<br>13   | 31<br>14 |

| START-END              | 0K<br>16K | 16K<br>32K | 32K<br>48K | 48K<br>64K |          |

|                        |           |            |            |            |          |

TABLE 7

| INITIAL<br>DEVICE-CODE<br>SELECTOR |    | JUMPERS |       |       |       |

|------------------------------------|----|---------|-------|-------|-------|

|                                    |    | 36-37   | 34-38 | 36-66 | 35-38 |

| J<br>U<br>M<br>P<br>E<br>R<br>S    | 32 | Ø       | 32    | 64    | 96    |

|                                    | 33 | 128     | 160   | 192   | 224   |

TABLE 8

| ASCII<br>SERIAL<br>INTERFACE | TRANSMISSION<br>LINE TYPE |                |       |

|------------------------------|---------------------------|----------------|-------|

|                              | TTY                       | RS232          | TTL   |

| JUMPERS                      | 65<br>54<br>58            | 60<br>54<br>59 | 58    |

| SERIAL INPUT                 | RXTTY                     | RXRS           | RXTTL |

| RETURN                       | RRXTTY                    | GND            | GND   |

| SERIAL OUTPUT                | TXTTY                     | TXRS           | TXTTL |

| RETURN                       | RTXTTY                    | GND            | GND   |

The transmission rate is software selected by loading memory locations as follows :

| Baud rate | 0FAE(Hex) | 0FAF(Hex) | Notes       |

|-----------|-----------|-----------|-------------|

| 600       | 9A        | 00        | Reset value |

| 300       | 35        | 01        |             |

| 110       | 55        | 03        |             |

The Audio signal generated by the Baud Rate generator F4702 Q34 is fixed by links 45 and 51 to the input of multiplexer T74LS157 Q44. Links 51 and 45 give a SICK signal of 9.6 kHz and an audio output signal of 4.8 kHz.

## (5) SIGNAL SPECIFICATIONS OF CLZ80/NC BOARD

This chapter identifies all the external connections of the CLZ80/NC board, defines all the signals present on the board connectors and gives their electrical characteristics and interconnection rules.

### (5.1.) Gamma-bus interface

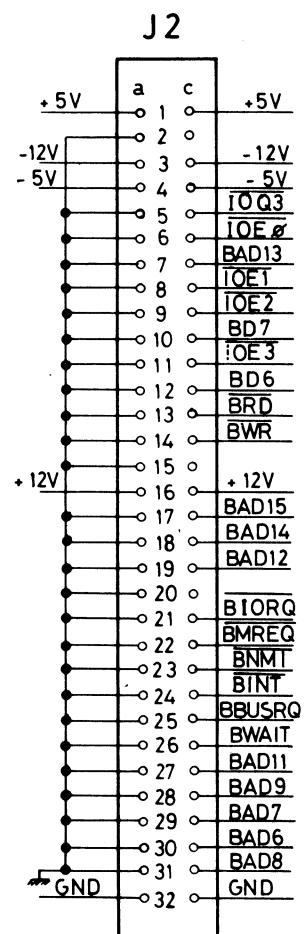

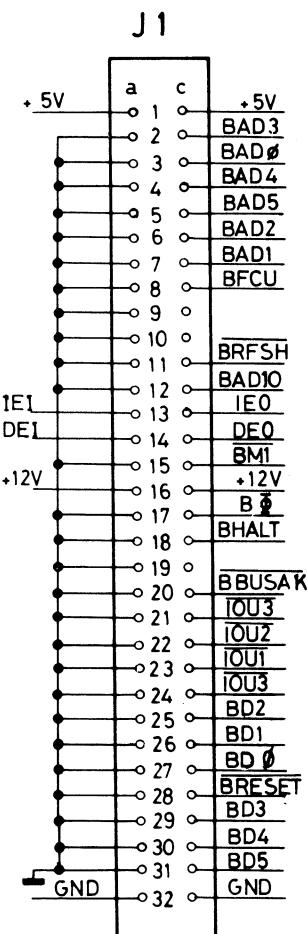

The Gamma-bus interface signals are available on connectors J1 and J2.

#### CONNECTIONS OF J1 & J2

This interface bus has been designed to provide optimum noise and speed performance and wide adaptability when expanding the microcomputer system. Many of the pins on connectors J1 and J2 are interconnected to form a grounded shield for the bus signals. When the bus is extended on a mother board, each signal is shielded by two ground lines.

The following tables show the pin connections, the signal name, the identity of input or output and the category (see para 5.1.2.) of the electrical specification.

CONNECTOR J1

| Row 'a' |        |        |     | Row 'c' |               |        |     |

|---------|--------|--------|-----|---------|---------------|--------|-----|

| pin     | signal | In/out | cat | pin     | signal        | In/out | cat |

| 1       | + 5V   | in     | -   | 1       | +5V           | in     | -   |

| 2       | GND    | -      | -   | 2       | BAD3          | in/out | 1   |

| 3       | GND    | -      | -   | 3       | BAD0          | in/out | 1   |

| 4       | -      | -      | -   | 4       | BAD4          | in/out | 1   |

| 5       | -      | -      | -   | 5       | BAD5          | in/out | 1   |

| 6       | -      | -      | -   | 6       | BAD2          | in/out | 1   |

| 7       | -      | -      | -   | 7       | BAD1          | in/out | 1   |

| 8       | -      | -      | -   | 8       | BFCU          | out    | 3   |

| 9       | -      | -      | -   | 9       | N/C           |        |     |

| 10      | -      | -      | -   | 10      | N/C           |        |     |

| 11      | -      | -      | -   | 11      | <u>BRFSH</u>  | out    | 1   |

| 12      | GND    | -      | -   | 12      | <u>BAD10</u>  | in/out | 1   |

| 13      | IEI    | in     | 5*  | 13      | IE0           | out    | 5   |

| 14      | DEI    | in     | 5*  | 14      | <u>DE0</u>    | out    | 5*  |

| 15      | GND    | -      | -   | 15      | <u>BML</u>    | out    | 1   |

| 16      | +12    | in     | -   | 16      | +12V          | in     | -   |

| 17      | GND    | -      | -   | 17      | <u>B0</u>     | out    | 3   |

| 18      | -      | -      | -   | 18      | <u>BHALT</u>  | out    | 3   |

| 19      | -      | -      | -   | 19      | N/C           | -      | -   |

| 20      | -      | -      | -   | 20      | <u>BBUSAK</u> | out    | 3   |

| 21      | -      | -      | -   | 21      | <u>IOU3</u>   | out    | 5   |

| 22      | -      | -      | -   | 22      | <u>IOU2</u>   | out    | 5   |

| 23      | -      | -      | -   | 23      | <u>IOU1</u>   | out    | 5   |

| 24      | -      | -      | -   | 24      | <u>IOU0</u>   | out    | 5   |

| 25      | -      | -      | -   | 25      | BD2           | in/out | 2   |

| 26      | -      | -      | -   | 26      | BD1           | in/out | 2   |

| 27      | -      | -      | -   | 27      | BD0           | in/out | 2   |

| 28      | -      | -      | -   | 28      | <u>BRESET</u> | in     | 4   |

| 29      | -      | -      | -   | 29      | BD3           | in/out | 2   |

| 30      | -      | -      | -   | 30      | BD4           | in/out | 2   |

| 31      | GND    | -      | -   | 31      | BD5           | in/out | 2   |

| 32      | 0V     | -      | -   | 32      | 0V            | -      | -   |

CONNECTOR J2

| Row 'a' |        |        |     | Row 'c' |        |        |     |

|---------|--------|--------|-----|---------|--------|--------|-----|

| pin     | signal | in/out | cat | pin     | signal | in/out | cat |

| 1       | + 5V   | in     | -   | 1       | + 5V   | in     | -   |

| 2       | GND    | -      | -   | 2       | N/C    | -      | -   |

| 3       | - 12V  | in     | -   | 3       | - 12V  | in     | -   |

| 4       | - 5V   | in     | -   | 4       | - 5V   | in     | -   |

| 5       | GND    | -      | -   | 5       | IOQ3   | out    | 5   |

| 6       | -      | -      | -   | 6       | IOE0   | out    | 5   |

| 7       | -      | -      | -   | 7       | BAD13  | in/out | 1   |

| 8       | -      | -      | -   | 8       | IOE1   | out    | 5   |

| 9       | -      | -      | -   | 9       | IOE2   | out    | 5   |

| 10      | -      | -      | -   | 10      | BD7    | in/out | 2   |

| 11      | -      | -      | -   | 11      | IOE3   | out    | 5   |

| 12      | -      | -      | -   | 12      | BD6    | in/out | 2   |

| 13      | -      | -      | -   | 13      | BRD    | in/out | 1   |

| 14      | -      | -      | -   | 14      | BWR    | in/out | 1   |

| 15      | GND    | -      | -   | 15      | N/C    |        |     |

| 16      | + 12V  | in     | -   | 16      | + 12V  | in     | -   |

| 17      | GND    | -      | -   | 17      | BAD15  | in/out | 1   |

| 18      | -      | -      | -   | 18      | BAD14  | in/out | 1   |

| 19      | -      | -      | -   | 19      | BAD12  | in/out | 1   |

| 20      | -      | -      | -   | 20      | N/C    |        |     |

| 21      | -      | -      | -   | 21      | BIORQ  | out    | 1   |

| 22      | -      | -      | -   | 22      | BMREQ  | out    | 1   |

| 23      | -      | -      | -   | 23      | BNMI   | in     | 1   |

| 24      | -      | -      | -   | 24      | BINT   | in     | 4   |

| 25      | -      | -      | -   | 25      | BBUSRQ | in     | 4   |

| 26      | -      | -      | -   | 26      | BWAIT  | in     |     |

| 4       |        |        |     |         |        |        |     |

| 27      | -      | -      | -   | 27      | BAD11  | in/out | 1   |

| 28      | -      | -      | -   | 28      | BAD9   | in/out | 1   |

| 29      | -      | -      | -   | 29      | BAD7   | in/out | 1   |

| 30      | -      | -      | -   | 30      | BAD6   | in/out | 1   |

| 31      | -      | -      | -   | 31      | BAD8   | in/out | 1   |

| 32      | 0V     | in     | -   | 32      | 0V     | in     | -   |

Notes :

GND = Signal shield ground

0V = power supply ground or common

(\*) Signals IEI, DEI and DEO are permanently connected to +5V on the NBZ80 board.

N.C. = No connection

#### (5.1.1.) Signal descriptions for Gamma-bus interface

All signals with a (bar) are active low, all others are active high. For further information on the signals in a Z80 CPU based microcomputer system see the Z80CPU Technical Manual.

BAD0 - 15 Address bus, input or output. 16 lines driven by 3-state buffers which are only disabled by the BUSAK, bus acknowledge, signal generated by the local CPU.

The external address inputs can only be applied following a BUSRQ, bus request and BUSAK signal response.

Lines BAD0-7 can be used for peripheral addressing (up to 256 max) as an alternative to the partial decodes IOE, IOQ and IOU. The lines BAD0-6 carry the refresh memory address when BRFSH is active.

BD0-7 Data bus, input or output. 8 lines with 3-state drivers and receivers enabled by DBOUT and DBIN signals. These lines carry all the system data transfers.

BMI Machine cycle 1 output. A 3-state buffered output which is only disabled by BUSAK active and indicating the Z80CPU op. code fetch cycle.

BMREQ Memory request output. A 3-state buffered output which is only disabled by BUSAK active and indicates a memory access for read or write. When BMREQ is active BAD0-15 hold a valid address for memory.

BIORQ Input/Output request output. A 3-state buffered which is only disabled by BUSAK active and indicates a peripheral access for read or write. When BIORQ is active BAD0-7 hold a valid address for the peripheral and IOE, IOQ, IOU hold a valid partially decoded address for an I/O part.

BRD Read output. A 3-state buffered output which is only disabled by BUSAK active and indicates that the memory or I/O part should place data on the data-bus for the local CPU to read.

BWR Write output. A 3-state buffered output which is only disabled by BUSAK active and indicates that the data bus will supply the data to

be written into the memory or into the peripheral by the local CPU. Note that there is a small timing shift on this signal. BWR becomes valid about 60ns before the data on the data bus becomes valid.

RFSH Refresh output. A 3-state buffered output which is only disabled by BUSAK active and indicates that the address lines BAD0-6 (BAD7=H) hold a valid refresh address for dynamic RAMs. During the refresh cycle the BMREQ signal is also active.

BHALT Halt output. A buffered output that is active when the CPU executes a software HALT instruction

BWAIT Wait input. An input signal direct to the CPU WAIT input with a 910 ohm pull-up resistor to +5V.

BINT Interrupt input. An input direct to the CPU INT input with a 910 ohm pull-up resistor to +5V.

BNMI Non-maskable interrupt input. An input direct to the CPU NMI input with a 910 ohm pull-up resistor to +5V.

BRESET Reset input. Reset of the CLZ80/NC board which resets the CPU and activates the initialization control circuit for a restart jump to the NC-Z program entry point.

BBUSRQ Bus request input. An input direct to the CPU BUSRQ input with a 910 ohm pull-up resistor to +5V.

BBUSAK Bus acknowledge output. A buffered output from the CPU BUSAK output. The BUSAK signal disables the BAD0-15, BMREQ, BIORQ, BRD, BWR, BMI and BFRSH 3-state output buffers so that an external circuit can access the on-board memories or I/O.

B0 Clock. A buffered output of the 2,4576 MHz clock.

BFCU Clock/8. A buffered output of the DC-DC convertor driver clock (307KHz).

IOQ0-3

IOE0-3 Partial peripheral address decode outputs.

These decode the BAD0-7 lines to provide blocks of 32 I/O addresses when used with IOU0-3.

IOU0-3 Partial peripheral address decode outputs timed by BIORQ and used with IOQ0-3 or IOE0-3 to generate peripheral addresses.

IEI Interrupt enable input to PIO Q2 IEI pin, connected internally to +5V thus making PIOQ2 part A the highest priority in any interrupt daisy chain.

IEO Interrupt enable output from PIO Q2/Q3, used to extend the interrupt daisy chain.

DEI,DEO Bus enable daisy chain. These signals are used only in larger systems to form a daisy chain defining the priority for bus requests. They are internally connected to +5V on the CLZ80/NC board.

#### (5.1.2.) Electrical specification

The table of signals on J1 and J2 making up the Gamma-bus show categories for each signal corresponding to the electrical specification.

For all Gamma-bus signals the drive and load currents (mA) for the categories are as follows :

| Cat | Description                        | Output    |      | Input        |      | 3-state<br>GIzol,zoh |

|-----|------------------------------------|-----------|------|--------------|------|----------------------|

|     |                                    | GIol      | GIoh | GIil         | Gihi |                      |

| 1   | Address bus<br>T74LS367 drivers    | 23<br>(1) | -2,6 | -0,8<br>(2)  | 0,2  | +/-0,02              |

| 2   | Data bus<br>T74LS367 buffers       | 23<br>(3) | -2,6 | -0,42<br>(4) | 0,06 | -                    |

| 3   | Buffered outputs<br>T74LS367       | 23        | -2,6 | -            | -    | -                    |

| 4   | Resistor pull-up<br>910 ohm to +5V | -         | -    | -4,6         | -    | -                    |

| 5   | Decoder outputs<br>T74LS138, 139   | 7,5       | -0,4 | 0,36         | -    | -                    |

#### Notes :

GIol = Current absorbed by output which is low

GIoh = Current supplied by output which is high

GIzol,zoh = Current supplied or absorbed by disabled output in the third state

GIil = Current supplied by an input at a low state voltage

Gihi = Current absorbed by an input at a high state voltage

The current values are maximums and :

- (1) BUSAK not active

- (2) BUSAK active

- (3) Input data

- (4) Input data

- means current out of pin, + means current into pin

The voltage levels for all the Gamma-bus signals are :

|        |                                       |

|--------|---------------------------------------|

| Output | high level > 2.4V<br>low level < 0.5V |

| Input  | high level > 2.0V<br>low level < 0.8V |

Description of the categories :

cat1 The address Bus and some control signals.

Output active (when BUSAK non-active) : these lines are outputs from T74LS367 buffers but are loaded by some on-board circuits which reduce the full T74LS367 drive capability to the value shown.

Input active (when BUSAK active) : these lines drive the on-board ROM & RAM address lines and decoders and the Peripheral Device select decoders. BAD0-1 also drive the PIO chips Q1 and Q2. The load presented is as shown in the table.

cat2 The data bus.

This is 3-state but the load presented in the input state and the inactive state is the same since it is the input current and output leakage of one T74LS367.

The drive in the output state is almost the full T74LS367 output capability as shown in the table.

cat3 Outputs from T74LS367 buffers, giving the full T74LS367 drive capability. These outputs are always active.

cat4 Input for wired-or use with on board 910ohm pull-up resistors to +5V.

cat5 Outputs which are not buffered but come direct from the T74LS138 or 9 decoders and have a smaller drive capability.

All of the normal rules for input and output loading and driving must be respected when using the Gamma-bus signals.

#### (5.1.3) Rules for Gamma-BUS signal expansion.

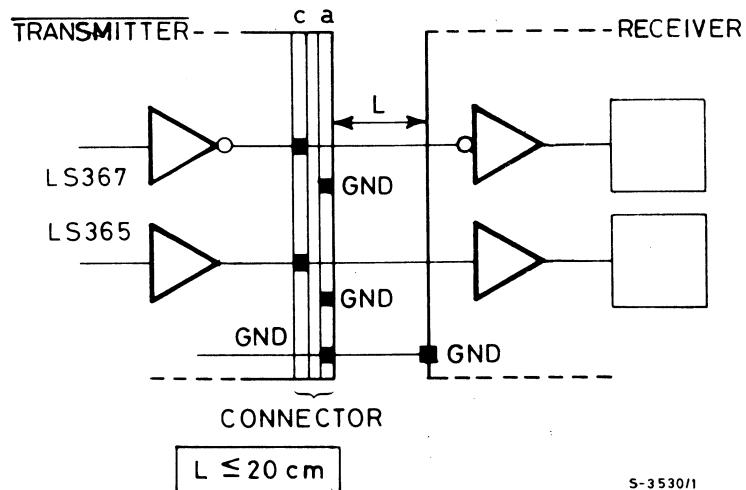

There is a maximum recommended length for connections to the Gamma-BUS signals in order to avoid problems of reflections or noise.

The methods recommended are as follows:

(1) Connections by single wires with a common ground return.

## CONNECTION TO THE GAMMA-BUS WITH SINGLE WIRES

For connections made on the Experiment Board NEZ80 the signal B0 (clock) should always be made with a twisted pair as shown below.

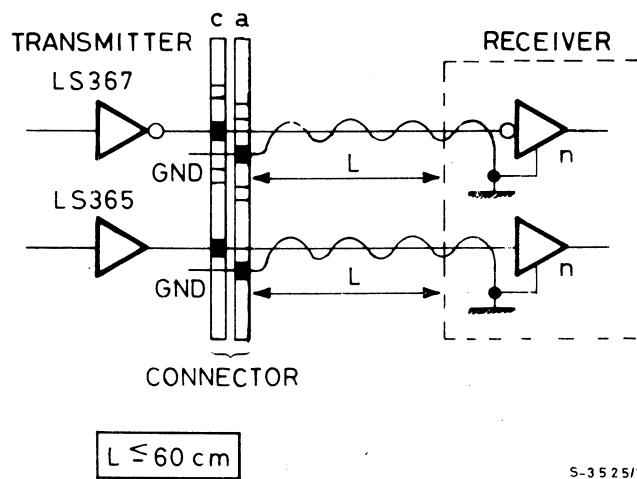

## (2) Connections with twisted pairs.

## CONNECTION TO THE GAMMA-BUS WITH TWISTED PAIRS

The ground connection should be made at both ends for each pair.

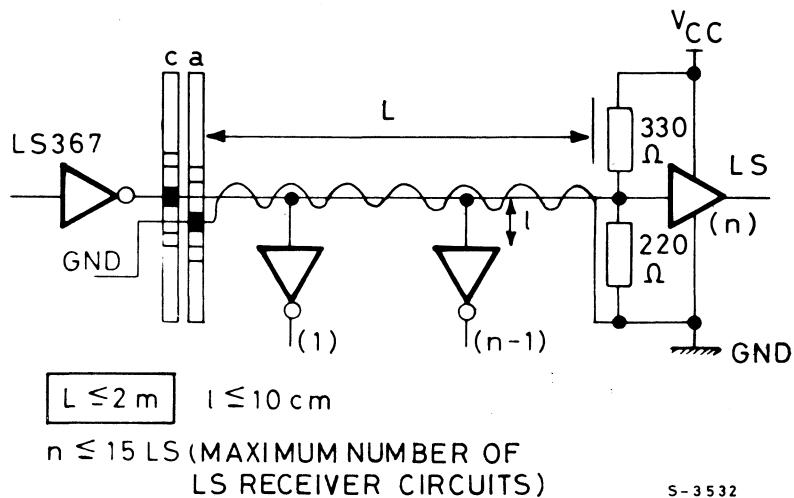

### (3) Connections with terminated lines.

### CONNECTION TO THE GAMMA-BUS WITH TERMINATED LINES

The line must be terminated at the far end. Additional outputs can be taken from the line at intermediate points.

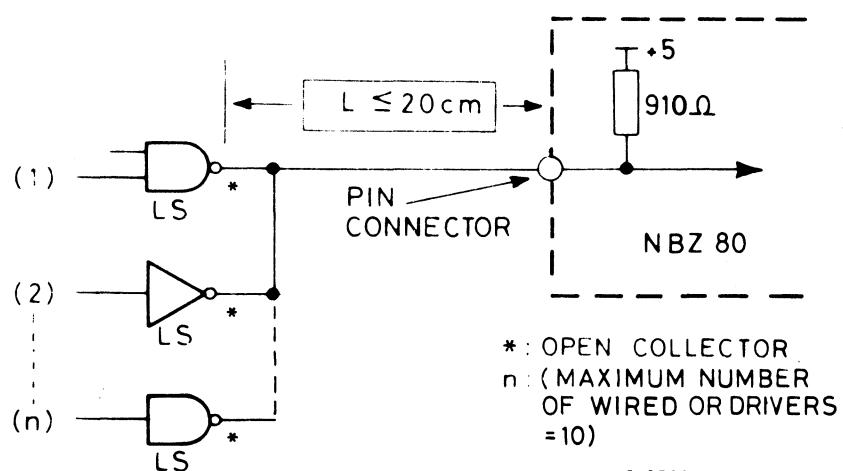

#### (4) Connection of Wired-OR circuits

S-3532

### CONNECTION OF WIRED-OR CIRCUITS

The maximum length of the connections is the same as (2) above.

S-3533/1

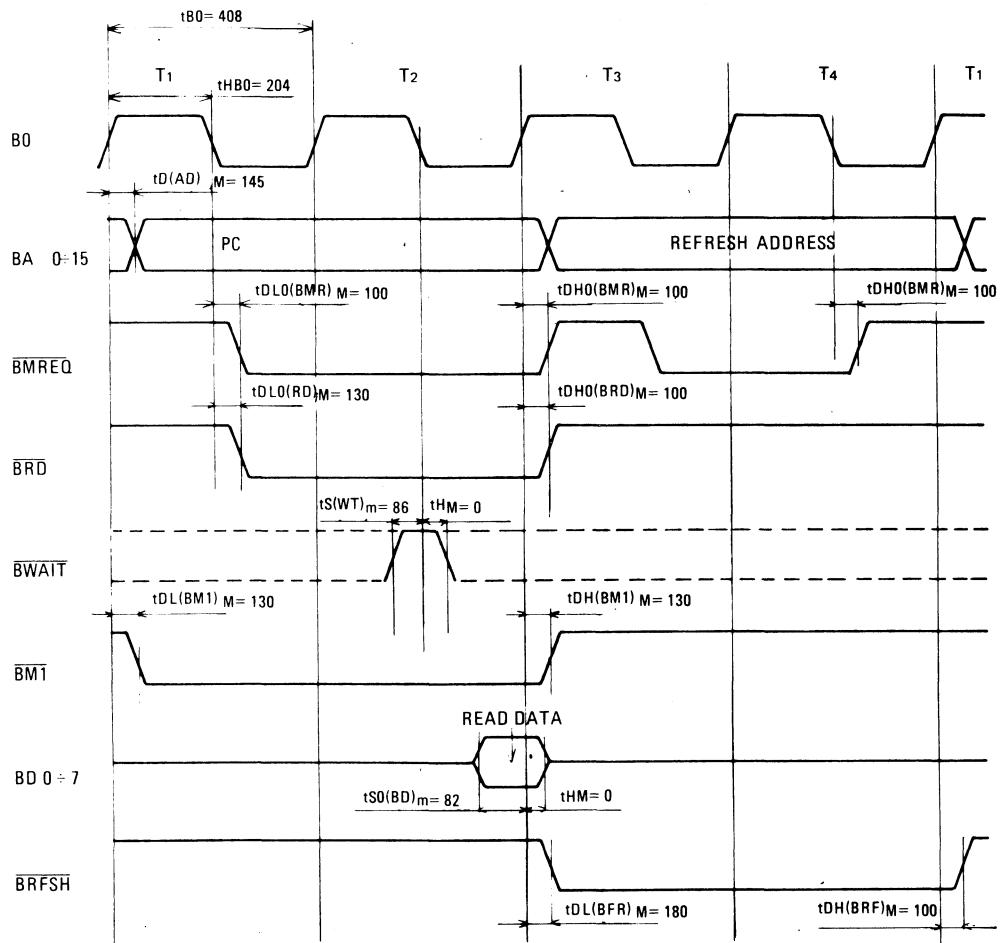

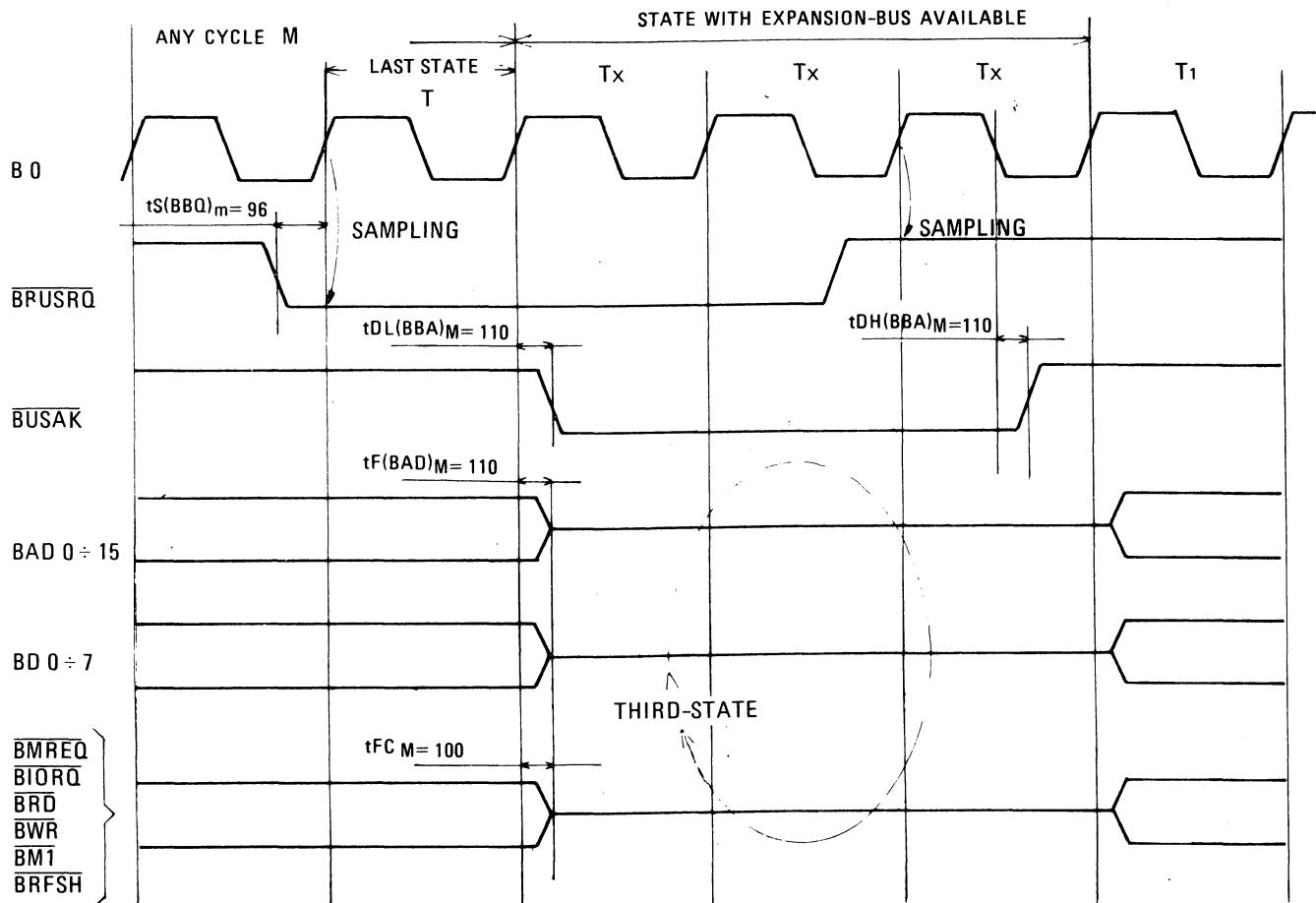

#### (5.1.4.) Timing of Gamma-bus signals

The timing of the signals on the Gamma-bus is not the same as for the Z80CPU chip because of delays introduced by the buffers and some of the decoder circuits.

Op.code fetch or M1 cycle.

#### OP CODE FETCH OR M1 CYCLE

The program counter contents are put on the address bus BA0-15 at the beginning of T1 cycle. Half a cycle later the BMREQ signal goes active indicating this is a memory request. BRD goes active at almost the same time to tell the memory to place its data on the data bus BD0-7.

The CPU reads the data at the end of T2/beginning-of-T3 and immediately disables BMREQ and BRD.

During T1/T2 BM1 is active indicating this is an op code fetch cycle.

During T3/T4 the CPU provides a refresh address for dynamic memories and activates BMREQ again and BRFSH.

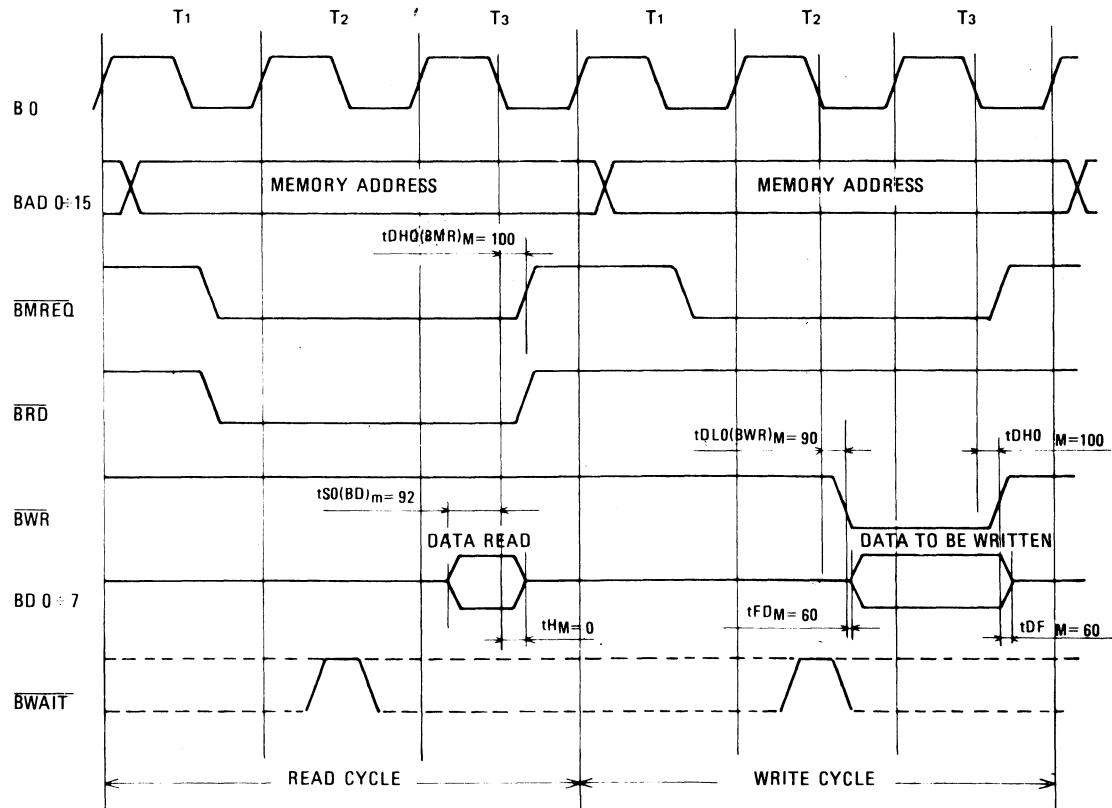

Memory read and write cycles.

#### MEMORY READ/WRITE CYCLES

The memory address is put on the address bus **BAD0-15** at the beginning of a read or write cycle.

For a read cycle **BMREQ** and **BRD** are activated in the middle of cycle **T1** and the data is read by the CPU in the middle of **T3**.

For a write cycle the **BMREQ** signal is active from the middle of **T1** but the **BWR** does not go active until the middle of the **T2** cycle. The delays in the T74LS156 Q12 decoder which activates **DBOUT** mean that the data to be written is not valid until after **BWR** is active. For this reason any memories connected to the Gamma-bus must apply a delay of 100-200 nS on **BWR** before using the signal for a RAM write command.

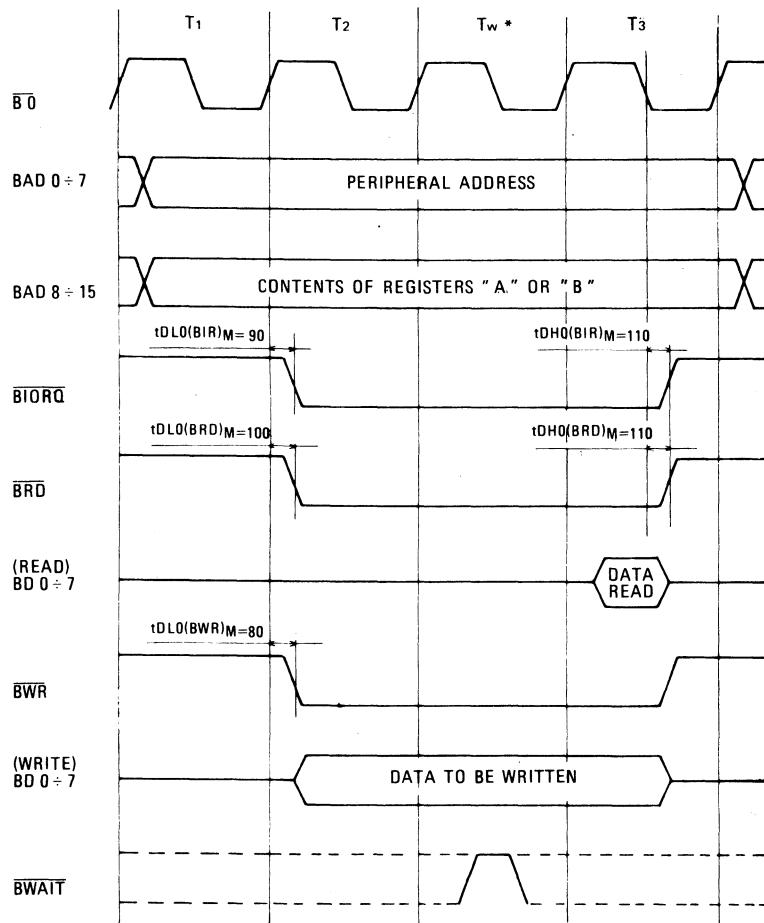

Peripheral read and write cycles.

PERIPHERAL READ/WRITE CYCLES

The peripheral address is placed on the address bus **BAD0-7** at the beginning of **T1** cycle. For a read or write cycle at the beginning of **T2** the **BIORQ**, **BRD** or **BWR** are active. The CPU outputs data to be written at the same time, but reads input data in the middle of **T3**.

The main difference to the memory cycles is the automatic insertion of a wait state not caused by a **BWAIT** signal. This special wait state is called **Tw\***.

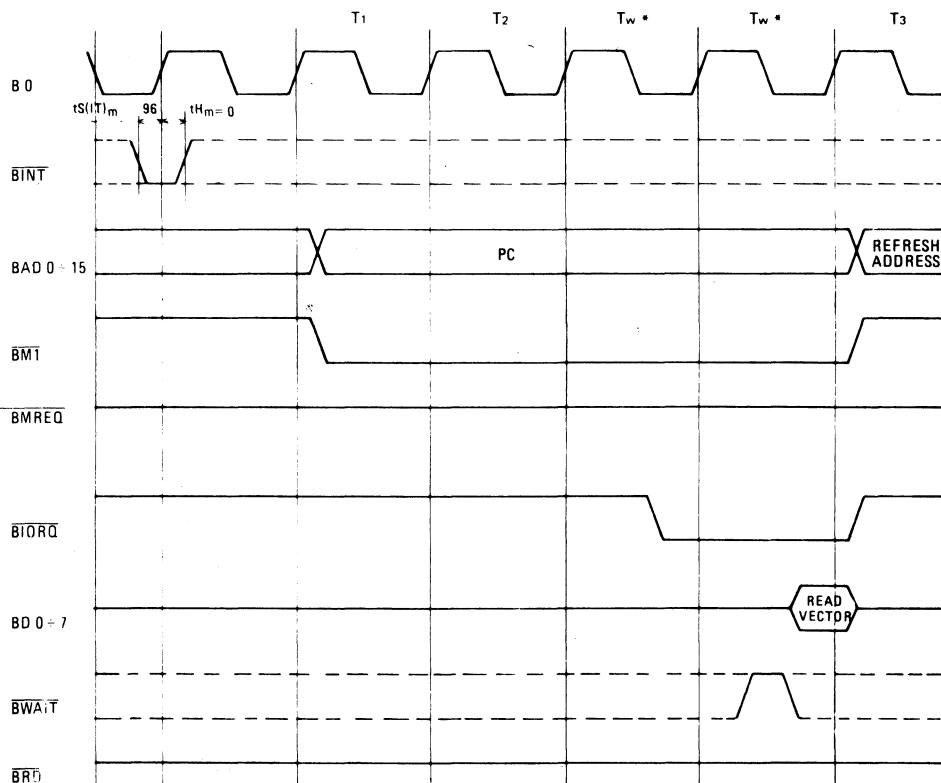

Interrupt and acknowledge cycles.

#### INTERRUPT/ACKNOWLEDGE CYCLE

The **BINT** line is sampled by the CPU during the positive edge of the last clock cycle of the execution of each instruction. An interrupt accepted by the CPU generates a special M1 cycle in which **BIORQ** is active instead of **BMREQ**. The PIO chip generating the interrupt responds to this by outputting the interrupt vector on the data bus lines **BDO-7**, which is subsequently read by the CPU at the beginning of  $T_3$ . Two wait cycles  $T_{w^*}$  are inserted automatically to allow for daisy chain ripple priority timing.

## Bus request and acknowledge

### BUS REQUEST/ACKNOWLEDGE CYCLE

A request for the buses is made at any time by activating BBUSRQ. The BUSRQ input on the CPU is sampled at the end of each M cycle just before the last T state. The bus drivers will be forced into the high impedance state at the end of the current M cycle and will remain in this state as long as BBUSRQ is active.

The dynamic RAM's are NOT refreshed by the local CPU during a Bus request/acknowledge cycle and this function must be taken over by the unit making the request.

### (5.2.) PIO Interface

The PIO interface signals are available on connectors J6 and J7.

The following tables give the pin connections, the signal name, the identity of Input or Output and the category of the electrical specification.

CONNECTORS J6 & J7

| pin | signal                | in/out | cat | pin | signal        | in/out | cat |

|-----|-----------------------|--------|-----|-----|---------------|--------|-----|

| 1   | <u>MAG</u>            | in     |     | 2   | <u>GND</u>    | -      | -   |

| 3   | TXD                   | in     | 1   | 4   | <u>BRESET</u> | -      | 4   |

| 5   | ICAS1                 | in     | 2   | 6   | ICAS2         | in     | 2   |

| 7   | RXD                   | out    | 3   | 8   |               | O/C    |     |

| 9   | -12V                  | out    | -   | 10  | GND           | -      | -   |

| 11  | +5V                   | out    | -   | 12  | GND           | -      | -   |

| 13  | +12V                  | out    | -   | 14  | GND           | -      | -   |

| 15  | <u>BREAK</u>          | in     | 4   | 16  | GND           | -      | -   |

| 17  | PA7                   | in/out | 5   | 18  | PB7           | in/out | 5   |

| 19  | PA6                   | in/out | 5   | 20  | PB6           | in/out | 5   |

| 21  | PA5                   | in/out | 5   | 22  | PB5           | in/out | 5   |

| 23  | PA4                   | in/out | 5   | 24  | PB4           | in/out | 5   |

| 25  | PA3                   | in/out | 5   | 26  | PB3           | in/out | 5   |

| 27  | PA2                   | in/out | 5   | 28  | PB2           | in/out | 5   |

| 29  | PA1                   | in/out | 5   | 30  | PB1           | in/out | 5   |

| 31  | PA0                   | in/out | 5   | 32  | PB0           | in/out | 5   |

| 33  | <u>STPA</u><br>(ASTB) | in     | 5   | 34  | GND           | -      | -   |

| 35  | <u>STPB</u><br>(BSTB) | in     | 5   | 36  | GND           | -      | -   |

| 37  | FLPA(ARDY)            | out    | 5A  | 38  | GND           | -      | -   |

| 39  | FLPB(BRDY)            | out    | 5A  | 40  | GND           | -      | -   |

Notes :

(1) The following signals are connected internally to the keyboard-display :

|     |     |       |

|-----|-----|-------|

| PA4 | ->> | TXD   |

| PA5 | ->> | ICAS1 |

| PA6 | ->> | ICAS2 |

| PA7 | <<- | RXD   |

#### (5.2.1.) PIO interface signal descriptions

A signal with a "(bar)" is active low, all others are active high.

For further information on the signals of the Z80PIO see the Z80PIO technical manual.

This is a summary of the PIO connector signals :

PA0-7, PB0-7 Input/output lines

16 lines of the parallel interface coming directly from the PIO Q2 port A (address 04H) and port B (address 05H). Some of the lines of port A are used by the keyboard/display.

PC0-7, PD0-7 Input/output lines

16 lines of parallel interface coming directly from PIO Q3 port C (address 08H) port D (address 09H).

These lines are directly available to the user on connector J7.

STPA, B, C, D

Strobe pulse (sync.) inputs.

These represent the sync signals coming from the PIO's, one for each port.

FLPA, B, C, D Ready pulse output.

Represents the data ready signals/coming from the PIO's one for each port.

RXD Receive data serial input.

Data coming from serial peripherals (terminal or audio cassette) is read through port A bit 7 (connection PA7 <<- RXD is made via the keyboard).

TXD Transmit data serial output.

The data output from the PIO port A bit 4 (connection PA4 ->> TXD is made via the keyboard) is sent to the peripheral (terminal or audio cassette).

MAG

Cassette select input.

This signal comes from the CASS/TTY switch located on the keyboard and transfers the data input (RXD) and output (TXD) from the serial terminal J5 (TTY) to the cassette recorder J3 (CASS). With MAG not active (high) the serial terminal (TTY) is selected.

**ICAS1,2** Cassette recorder control signal output.

These are the signals at the output of PIO (PA5, PA6) for start/stop of recorder motors. In the CLZ80/NC only ICAS1 is controlled by resident NC-Z program (connections PA5->>ICAS1 and PA6->>ICAS2 are made in the keyboard).

**BREAK**

Non-maskable interrupt, input.

Input for generating a non-maskable interrupt. The input pulse width required is 80-400ns. A 33 ohm pull-up resistor to +5V is incorporated on the CLZ80/NC board.

**BRESET**

Reset input.

A 910 ohm pull-up resistor to +5V is incorporated on the CLZ80/NC board.

(5.2.2.) Electrical characteristics of PIO interface

**WARNING**

Inputs/outputs PA,B,C,D(0-7), FLPA,B,C,D and STPA,B,C,D on connectors J6 and J7 are MOS inputs/outputs.

Care should be taken not to allow static electricity to damage the circuits. The Z80PIO chip has built-in protection against static electrical charge build-up but users must take the usual precautions when connecting to the MOS circuits.

The following table gives the load current and threshold voltage levels for each category.

| Cat | Description      | Threshold |      | Loading |         | Loading |         |

|-----|------------------|-----------|------|---------|---------|---------|---------|

|     |                  | Vl        | Vh   | output  | Iol Ioh | Input   | Iil Iih |

| 1   | LS input         | <0,8      | >2.0 | -       | -       | -0,36   | 0,02    |

| 2   | TTL input        | <0,8      | >2.0 | -       | -       | -1,6    | 0,04    |

| 3   | LS output        | <0,5      | >2.7 | 8,0     | -0,4    | -       | -       |

| 4   | Resistor pull up |           |      |         |         |         |         |

|     | <u>BREAK</u>     |           |      |         |         |         |         |

|     | (33ohm) (1)      | <0,8      | >2.0 | -       | -       | -130    | -       |

|     | <u>BRESET</u>    |           |      |         |         |         |         |

|     | (910ohm)         | <0,8      | >2.0 | -       | -       | -4,6    | -       |

| 5   | PIO input        | <0,8      | >2.0 | -       | -       | -0,01   | -0,01   |

|     | output(2)        | <0,4      | >2.4 | 2,0     | -0,25   | -       | -       |

| 5A  | PIO FLP output   | <0,4      | >2.4 | 1,6     | -0,23   | -       | -       |

|     |                  | V         | V    | mA      | mA      | mA      | mA      |

### Notes :

(1) This input should be used as follows :

This circuit produces the required narrow (80-400ns) pulse required for NMT.

S-3467

- (2) Port B of the PIO chips can drive  $I_{OH} > 1.5\text{mA}$  at  $V_{OH} = 1.5\text{V}$  for direct drive of darlington transistors.

- (3) Input  $\overline{MAG}$  has a load of  $I_{il} = -2.2\text{mA}$ ,  $I_{ih} = 0.06\text{mA}$

## Description of categories

Call Inputs to T/4LS gates on the board.

Cat2 Inputs to T74 gates on the board.

Cat3 Outputs from T74LS gates on the board.

Cat4 Resistive pull-up. Note the use of the line BREAK described above. If a BREAK input is required direct from a logic gate output the signal line BNMI on the Gamma-bus should be used, driven by an open collector gate output with a 80-400ns pulse.

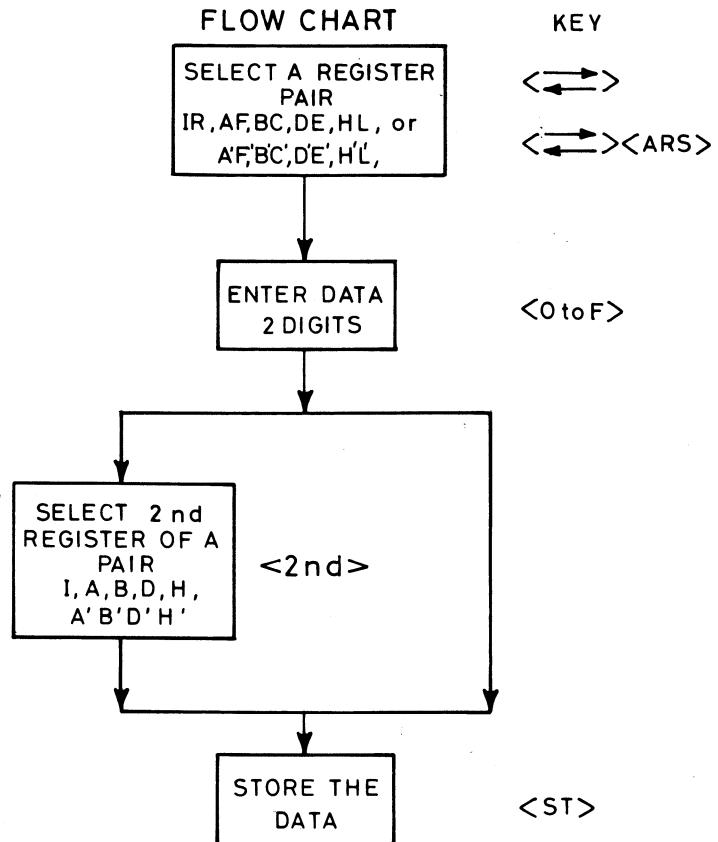

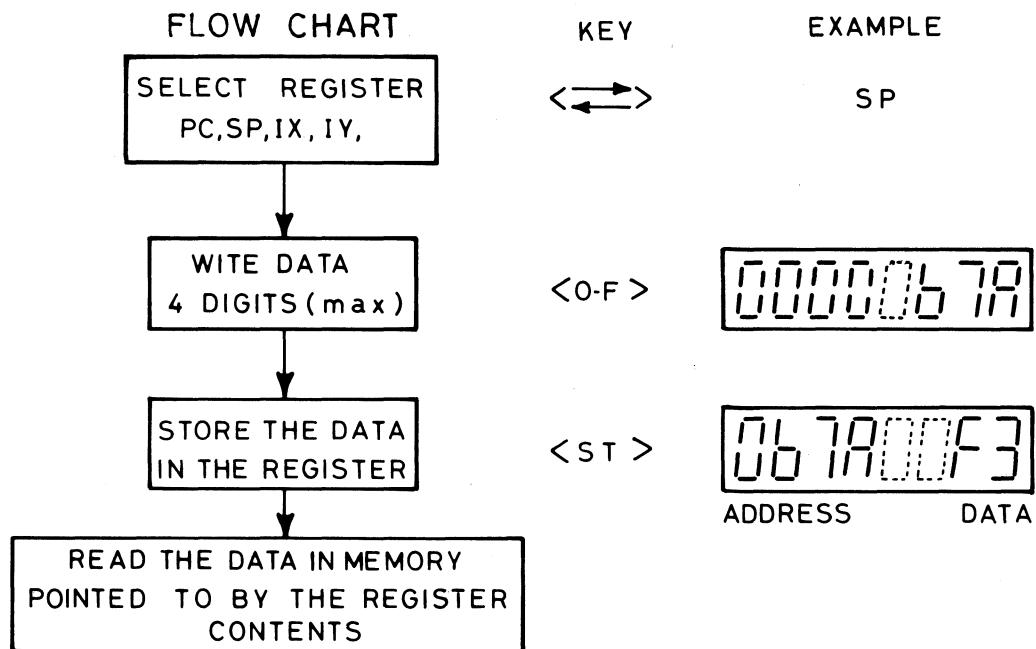

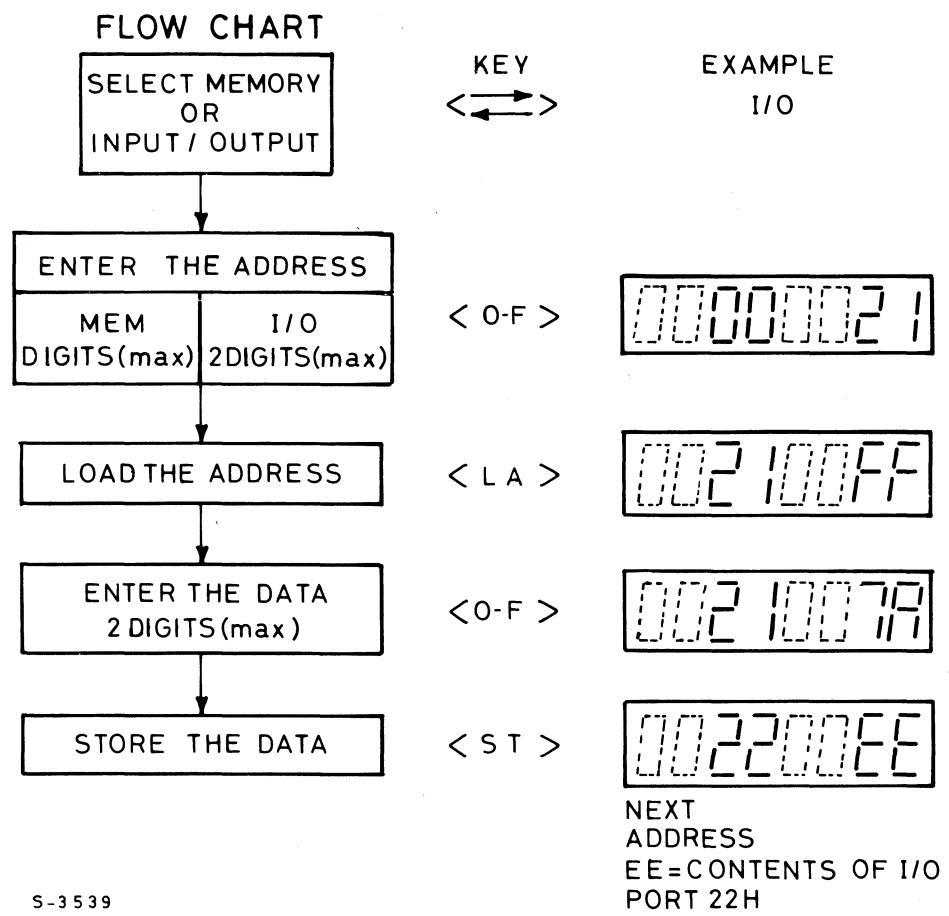

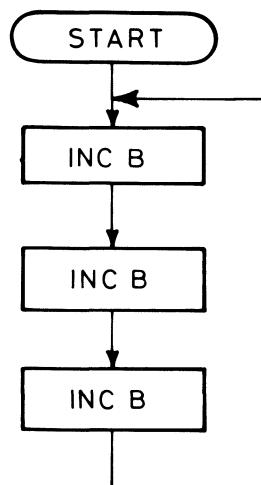

Cat5 PIO input/output signals - for further information see the Z80PIO data sheet and the Z80 technical manual.