**NIXDORF**

**COMPUTER**

**Titel:** Kunden-IC für SAS

**Verteiler:**

HW 8820

HW 8864

HW 8870

HW 8874

HW Mini

**Dokumentations-Stufe:**

- Vorschlag-Bericht-Studie-Protokolle

- Pflichtenheft (Eigenschaften)

- Pflichtenheft (Implementation)

- Dokumentation

- Anwenderbeschreibung-Bedienungsanleitung

- Sonstiges:

**Verantwortlich:** H. Vogt EH 13

**Bearbeiter:** H. Hölscher EH 132

**Einsprüche** bis zum:

Stellungnahme

an:

| Ausgabe/<br>Änderung | Blätter | Ersetzt<br>Ausgabe | Bemerkungen                      | Datum    | Verantwortlicher/Bearbeiter       |

|----------------------|---------|--------------------|----------------------------------|----------|-----------------------------------|

| 1/0                  | 26      |                    |                                  | 7.5.76   |                                   |

| 2/0                  | 26      | 1/0                |                                  | 13.8.76  |                                   |

| 3/0                  | 26      | 2/0                |                                  | 20.12.76 |                                   |

| 4/0                  | 21      | 3/0                |                                  | 1.6.77   |                                   |

| 4/1                  | 21      |                    | Austausch Blatt<br>1, 3, 4, 5, 7 | 28.11.77 | <i>Vogt<br/>Hölscher<br/>Vogt</i> |

2653.005

1-1-1-6-1

Projekt-Nr.:

Dokument-Nr.:

2

1

Blatt

nächstes Blatt

0. 1     Inhalt

0. 2     Literatur

0. 3     Kurzbeschreibung

1.     Technische Daten

1. 1     Elektr. Daten

1. 2     Pin-Belegung

1. 3     Innenschaltung der Ein-Ausgänge

2.     Funktion

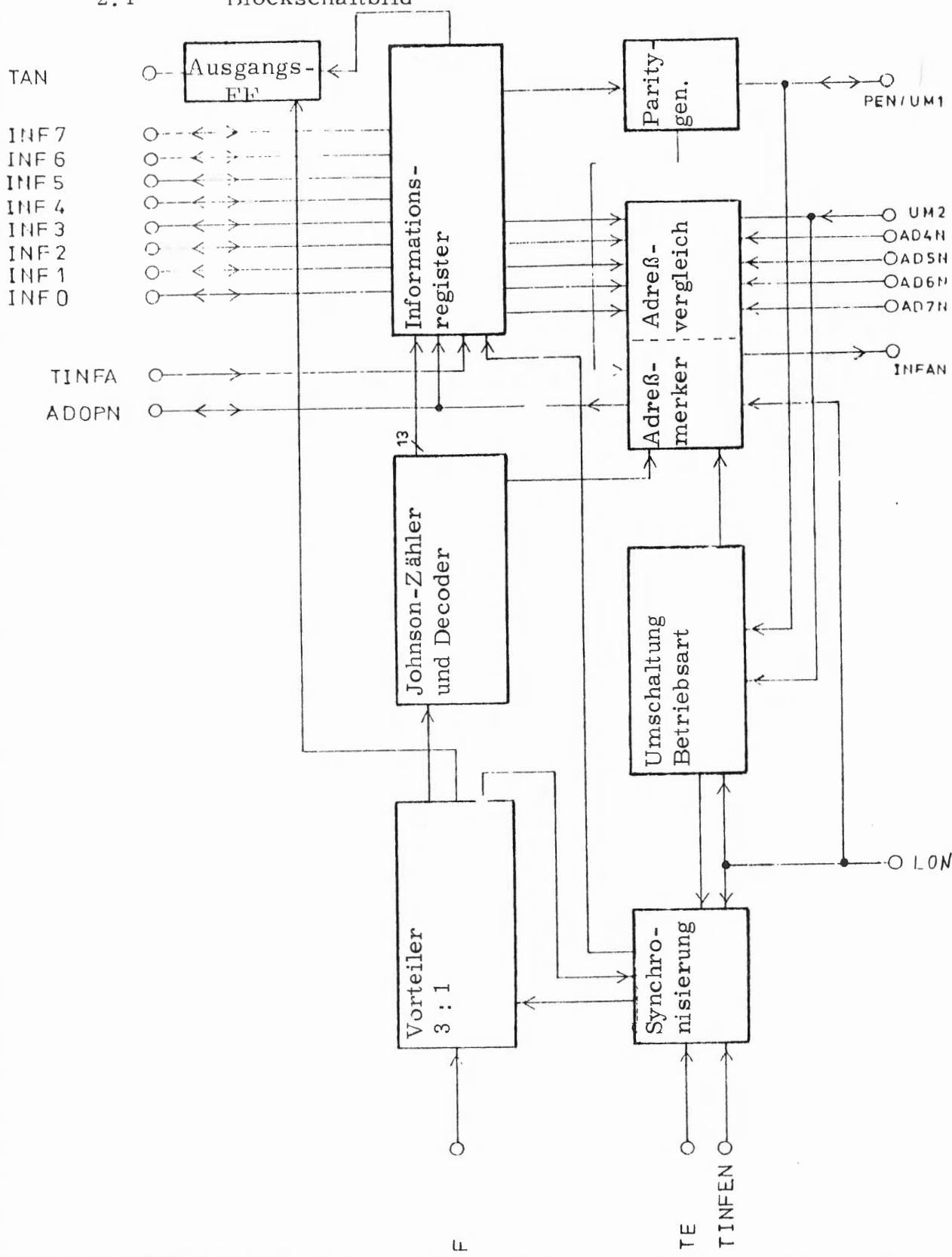

2. 1     Blockschaltbild

2. 2     Bedeutung der Signale

2. 3     Funktionsbeschreibung

2. 4     Umschaltung Betriebsart

2. 5     Interne Schaltung

2. 6     Interne Taktung

2. 7     Externe Taktung

|                   |                   |                              |         |                |       |

|-------------------|-------------------|------------------------------|---------|----------------|-------|

| 4/0<br>Ausg./Änd. | 1. 6. 77<br>Datum | 1-1-1-6-1<br>Dokument-Nummer | Kapitel | nächstes Blatt | Blatt |

|-------------------|-------------------|------------------------------|---------|----------------|-------|

## 0. 2 Literatur

Dok. -Nr. 1-1-1-5-1:

SAS, Serielle Arbeitsplatz-Schnittstelle

## 0. 3 Kurzbeschreibung

Zum Anschluß von Peripheriegeräten (Tastaturen, Displays, Drucker) ist die Serielle Arbeitsplatz-Schnittstelle eingeführt worden.

Die Einsparungen, die sich bei Verwendung einer seriellen Schnittstelle bei Steckern und Kabeln ergeben, bedingen einen höheren Logikaufwand (etwa 15 ICs). In diesem Bericht wird ein Kunden-Schaltkreis beschrieben, in dem alle für die Steuerung der SAS notwendigen Schaltungen zusammengefaßt sind.

Das IC enthält die Parallel-Serien-Wandlung und Parityerzeugung für den Sendebetrieb, die Serien-Parallel-Wandlung und Parityprüfung für Empfangsbetrieb und den Adressvergleich für Peripheriegeräte. Es ist umschaltbar für den Betrieb als Master in der ZE und als Slave im Peripheriegerät.

Das IC hat die Bezeichnung NC-FRD 1 B - SAS 1

Dieses Dokument enthält Datenblatt und Funktionsbeschreibung.

## 1. Technische Daten

### 1.1 Elektrische Daten

#### Maximalwerte

|                                     |                   |

|-------------------------------------|-------------------|

| Versorgungsspannung, Vcc            | 7 V               |

| Eingangsspannung                    | 6 V               |

| Arbeitstemperaturbereich (Umgebung) | 0°C bis 70°C      |

| Lagertemperaturbereich              | -65°C bis 150°C   |

| Löttemperatur (Lötbad)              | 245°C für 10 sec. |

#### Statische Werte

Bei Vcc = 5 V ± 10% und Umgebungstemperatur 0°C bis 70°C.

| Symbol | Parameter                 | Inputs/<br>Outputs                               | Testcon-<br>ditions     | Limits 1) |      |     |

|--------|---------------------------|--------------------------------------------------|-------------------------|-----------|------|-----|

|        |                           |                                                  |                         | Min       | Typ  | Max |

| Icc    | Supply current            |                                                  | Vcc = 5,5V              | 170       | 225  | mA  |

| VI     | Input clamp voltage       | all inputs                                       | II = -5mA               |           | -1.2 | V   |

| VIH    | High-level input voltage  | all inputs                                       |                         | 2.0       | 6.0  | V   |

| VIL    | Low-level input voltage   | all inputs                                       |                         | -0.8      | 0.8  | V   |

| Voh    | High-level output voltage | all outputs                                      | IOH = -80µA             | 2.4       |      | V   |

| VOL    | Low-level output voltage  | TAN,<br>INFAN                                    | IL = 7,5mA              |           | 0.5  | V   |

|        |                           | other outputs                                    | IL = 1,6mA              |           | 0.5  | V   |

| Iih    | High-level input current  | all inputs                                       | IH = 2.4 V              |           | 40   | µA  |

| ILL    | Low-level input current   | inputs: F<br>TE, LON, TINFA,<br>INFO ÷ INF 7     | IL = 0.4 V<br>cc = 5.5V |           | -1.6 | mA  |

|        |                           | TINFEN,<br>PFN/UM1,<br>ADOPN, UM2<br>AD4N ÷ AD7N |                         |           | -40  | µA  |

|        |                           |                                                  |                         |           | -1.0 | mA  |

| IOH    | High-level output current | all outputs                                      |                         | -80       |      | µA  |

| OL     | Low-level output current  | TAN, INFAN                                       |                         | 7,5       |      | mA  |

|        |                           | other outputs                                    |                         | 1,6       |      | mA  |

#### 1. Typ. Werte bei Vcc = 5 V und 25°C Umgebungstemperatur

|                   |                   |                              |         |                     |            |

|-------------------|-------------------|------------------------------|---------|---------------------|------------|

| 4/1<br>Ausg./Änd. | 28.11.77<br>Datum | 1-1-1-6-1<br>Dokument-Nummer | Kapitel | 5<br>nächstes Blatt | 4<br>Blatt |

|-------------------|-------------------|------------------------------|---------|---------------------|------------|

### Dynamische Werte

Bei  $V_{CC} = 5 \text{ V} \pm 5\%$  und Umgebungstemperatur  $0^\circ\text{C}$  bis  $70^\circ\text{C}$

| Symbol               | Parameter       | Inputs / Outputs | Testconditions             | Limits |     |     | Units |

|----------------------|-----------------|------------------|----------------------------|--------|-----|-----|-------|

|                      |                 |                  |                            | Min    | Typ | Max |       |

| $f_{CL}$             | Clock frequency | Input F          | $\frac{t_w}{T_{CL}} = 0,5$ |        |     | 12  | MHz   |

| $\frac{t_w}{T_{CL}}$ | Duty Cycle      | Input F          | $f_{CL} = 10 \text{ MHz}$  | 0,4    |     | 0,6 | --    |

Die logische Funktion des gesamten Schaltkreises muß bei  $V_{CC} = 5 \text{ V} \pm 20\%$  und einer Umgebungstemperatur von  $0^\circ\text{C} \div 55^\circ\text{C}$  gewährleistet sein.

### Thermische Werte

Max. Sperrschichttemperatur  $145^\circ\text{C}$

Übergangswiderstand Sperrschicht/Umgebung  $70^\circ\text{C}/\text{W}$

|            |          |                 |         |                |       |

|------------|----------|-----------------|---------|----------------|-------|

| 4/1        | 28.11.77 | 1-1-1-6-1       |         | 6              | 5     |

| Ausg./Änd. | Datum    | Dokument-Nummer | Kapitel | nächstes Blatt | Blatt |

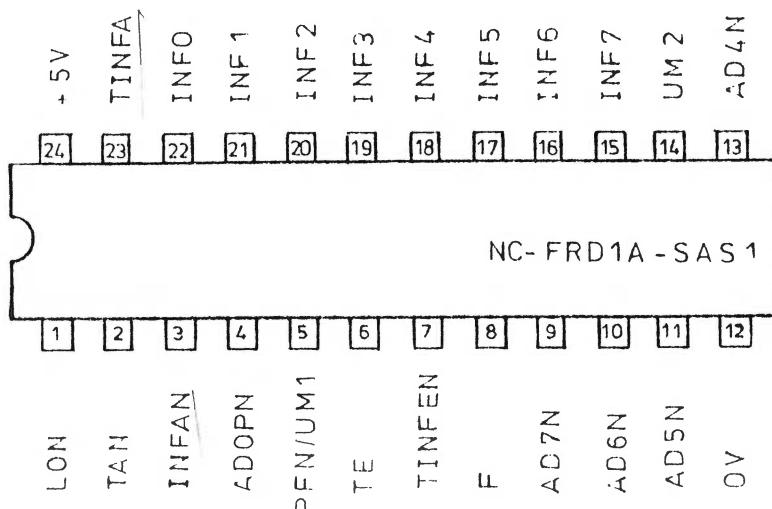

1. 2

Pin-Belegung

Ansicht: von oben

Gehäuse: 24 Pin Dual-in-line, Plastic

|            |        |                 |         |                |       |

|------------|--------|-----------------|---------|----------------|-------|

| 4/0        | 1.6.77 | 1-1-1-6-1       |         | 7              | 6     |

| Ausg./Änd. | Datum  | Dokument-Nummer | Kapitel | nächstes Blatt | Blatt |

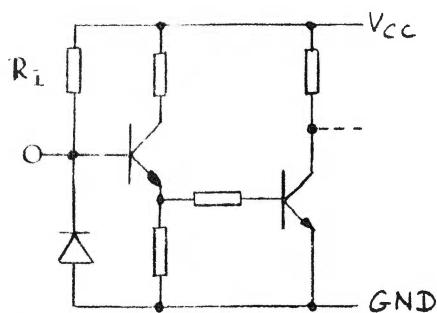

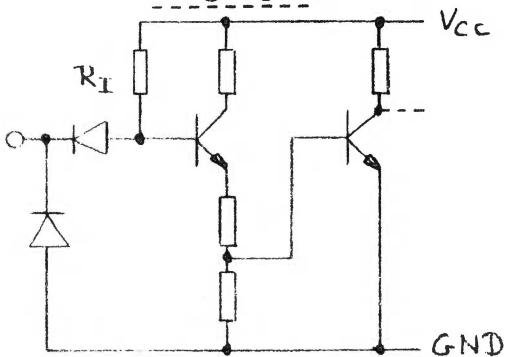

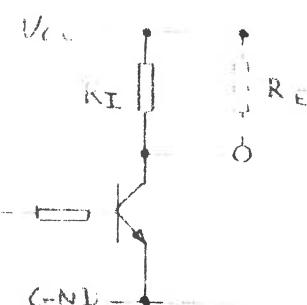

## 1.3 Innenschaltung der Ein- und Ausgänge

## 1. Eingänge

| Signal | $R_I$ |

|--------|-------|

| LON    | --    |

| TINFA  | --    |

| TE     | --    |

| UM 2   | 8 K   |

| ADxN   | 8 K   |

## 2. Eingang F

| Signal | $R_I$ |

|--------|-------|

| F      | 4 K   |

## 3. Ein/Ausgänge

| Signal  | $R_I$ | $R_E$ |

|---------|-------|-------|

| ADOPN   | 8 K   | 3 K   |

| PFN/UM1 | 8 K   | 3 K   |

| TINFEN  | 8 K   | 3 K   |

| INFX    | --    | 10 K  |

## 4. Ausgänge

| Signal | $R_I$ | $R_E$ |

|--------|-------|-------|

| TAN    | 8 K   | 1 K   |

| INFAN  | 8 K   | 3 K   |

## 2. Funktion

## 2.1 Blockschaltbild

Alle Rechte aus diesen Unterlagen und Ihrem Inhalt behalten wir uns vor (BGB, UWG, LitUrHGl).

Unberechtigte Verwertung, Weitergabe oder Vervielfältigung von Unterlagen oder deren Inhalt verpflichtet zu Schadenersatz.

|                   |                 |                              |   |         |                     |            |

|-------------------|-----------------|------------------------------|---|---------|---------------------|------------|

| 4/0<br>Ausg./Änd. | 1.6.77<br>Datum | 1-1-1-6-1<br>Dokument-Nummer | F | Kapitel | 9<br>nächstes Blatt | 8<br>Blatt |

|-------------------|-----------------|------------------------------|---|---------|---------------------|------------|

## 2.2 Bedeutung der Signale

|                 |                                                                                                                                           |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| <u>UM 1*</u>    | Umschaltung zwischen den Betriebsarten<br>Zentraleinheit, Peripheriegerät mit 4 Zeilen<br>und Peripheriegerät mit 8 Zeilen.               |

| <u>UM 2</u>     | In Peripheriegeräten mit 4 Zeilen wird UM 2<br>als Adreßbit verwendet.                                                                    |

| <u>AD 4 N</u>   | Geräteadresse (Adreßcodierschalter)                                                                                                       |

| <u>÷ AD 7 N</u> |                                                                                                                                           |

| <u>F</u>        | Eingangstakt, 10 MHz $\pm 0,1\%$                                                                                                          |

| <u>TE</u>       | Eingang vom Empfänger der SAS                                                                                                             |

| <u>TAN</u>      | Ausgang zum Treiber der SAS                                                                                                               |

| <u>INFO</u>     | Informationsbus, parallele                                                                                                                |

| <u>- INF 7</u>  | Eingangs- bzw. Ausgangsinformation                                                                                                        |

| <u>  INFAN</u>  | Meldung eines angekommenen AG - bzw.<br>EG-Zyklus                                                                                         |

| <u>ADOPN</u>    | Meldung eines angekommenen AD- bzw. OP-<br>Zyklus                                                                                         |

| <u>PFN *</u>    | Meldung eines angekommenen Zyklus mit<br>Parityfehler                                                                                     |

| <u>  TINFA</u>  | Takt, durch den die empfangene Information<br>auf den Bus geschaltet wird.                                                                |

| <u>TINFEN</u>   | Takt, durch den ein Zyklus auf der SAS ge-<br>startet wird. Im Peripheriegerät fordert<br>das IC mit TINFEN die Eingabeinformation<br>an. |

| <u>LON</u>      | Eingang für Einschaltlöschen.                                                                                                             |

\* UM 1 und PEN liegen auf einem gemeinsamen Pin.

|            |        |                 |         |                |       |

|------------|--------|-----------------|---------|----------------|-------|

| 4/0        | 1.6.77 | 1-1-1-6-1       |         | 10             | 9     |

| Ausg./Änd. | Datum  | Dokument-Nummer | Kapitel | nächstes Blatt | Blatt |

2.3 Funktionsbeschreibung2.3.1 Betrieb als Master in der ZE

Zum Start eines AG-Zyklus auf der SAS schaltet die ZE zusammen mit dem Startsignal TINFEN die zu sendene Information auf die Leitungen INF0 bis INF7. Alles weitere läuft selbstständig im IC ab.

Um einen AD- oder OP-Zyklus zu starten, muß zusätzlich das Signal ADOPN geschaltet werden.

Ist als Antwort auf einen AD-Zyklus ein EG-Zyklus angekommen, wird dieser auf Parityfehler überprüft. Ist Parity falsch, gibt das IC den Takt PFLON.

Ist Parity richtig, erscheint der Takt INFAN. Daraufhin kann die ZE mit dem Signal TINFA die Information anfordern, die dann während TINFA auf die Leitungen INF0 bis INF7 geschaltet wird.

## 2.3.2

Betrieb als Slave im Peripheriegerät

Nach Empfang eines Adresszyklus prüft das IC die angekommene Adresse auf ungerade Parität und vergleicht die Adresse mit der Geräteadresse, die an den Anschlüssen AD4N bis AD7N und ( bei 4 Zeilen) UM 2 anliegt. Über die Umschaltkontakte UM 1 und UM 2 wird vorgegeben, ob die oberen 4 bzw. 5 Adressbits verglichen werden ( siehe 1.2, 2.1, und 2.2). Bei Ungleichheit wird der eventuell gesetzte Merker Adresse gelöscht.

Bei Gleichheit der Adresse setzt das IC den internen Merker Adresse und schaltet den Takt ADOPN.

Bei einem Parityfehler wird der Adressmerker auf jeden Fall gelöscht. Es erscheint kein Taksignal an den Ausgängen des IC. Mit Beginn des Signals ADOPN kann das Peripheriegerät den Takt TINFA schalten. Während der Dauer dieses Taktes schaltet das IC die empfangene Adresse auf die Leitungen INFØ bis INF7.

INFØ ist dabei "0".

Nach Ablauf des AD-Zyklus schaltet das IC das Signal TINFEN. Das Gerät muß während dieses Taktes die Information des folgenden EG-Zyklus auf den Informationsbus legen. Das IC startet daraufhin einen EG-Zyklus auf der SAS.

Empfängt das IC von der SAS AG- oder OP-Zyklen, reagiert es nur, wenn der interne Adressmerker gesetzt ist. Bei Parityfehlern in der angekommenen Information schaltet es das Signal PFLON und löscht den Adressmerker. Ist die Information in Ordnung, wird bei AG-Zyklen das Signal INFAN, bei OP-Zyklen das Signal ADOPN geschaltet.

Während des Empfangs des Signals TINFA legt das IC die empfangene Information auf den Informationsbus. Bei OP-Zyklen ist INFØ dabei gleich "1".

|            |        |                 |         |                |       |

|------------|--------|-----------------|---------|----------------|-------|

| 4/0        | 1.6.77 | 1-1-1-6-1       |         | 12             | 11    |

| Ausg./Änd. | Datum  | Dokument-Nummer | Kapitel | nächstes Blatt | Blatt |

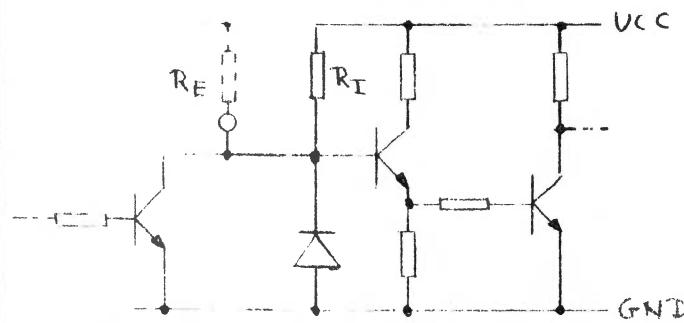

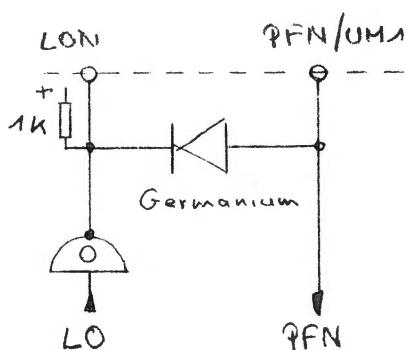

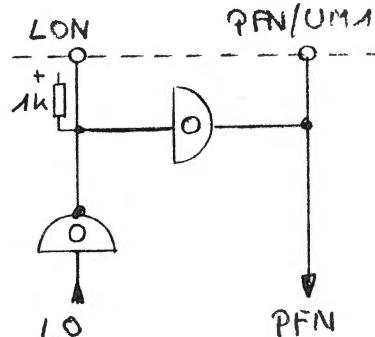

## 2.4 Umschaltung Betriebsart

Die Betriebsart des IC's wird durch die Signale UM 1 und UM 2 bestimmt:

| Betriebsart                         | UM 1 | UM 2   |

|-------------------------------------|------|--------|

| Master                              | L    | H      |

| Slave, 4 Zeilen, 5 Bit AD-Vergleich | H    | AD 3 N |

| Slave, 8 Zeilen, 4 Bit AD-Vergleich | L    | L      |

Das Signal UM 1 liegt mit dem Signal PFN auf einem gemeinsamen Pin. Deshalb darf UM 1, wenn für die Betriebsart ein "L" erforderlich ist, nur mit dem Signal LON zusammen heruntergezogen werden. Mit der positiven Flanke von LON wird UM 1 in ein internes Flipflop übernommen. Dafür ist zu gewährleisten, daß UM 1 nicht vor LON von "L" auf "H" wechselt.

Dies wird durch eine der beiden folgenden Schaltungen erreicht. Zusätzlich muß verhindert werden, daß ein externes PF-Flipflop durch UM 1 gesetzt wird.

Wird UM 1 als "H"-Signal benötigt, ist keine Beschaltung notwendig.

Im Slave mit 4 Zeilen wird UM 2 als Eingang für das Adreßbit AD 3 N verwendet.

Schaltung A:

Schaltung B:

|            |        |                 |         |                |       |

|------------|--------|-----------------|---------|----------------|-------|

| 4/0        | 1.6.77 | 1-1-1-6-1       |         | 13             | 12    |

| Ausg./Änd. | Datum  | Dokument-Nummer | Kapitel | nächstes Blatt | Blatt |

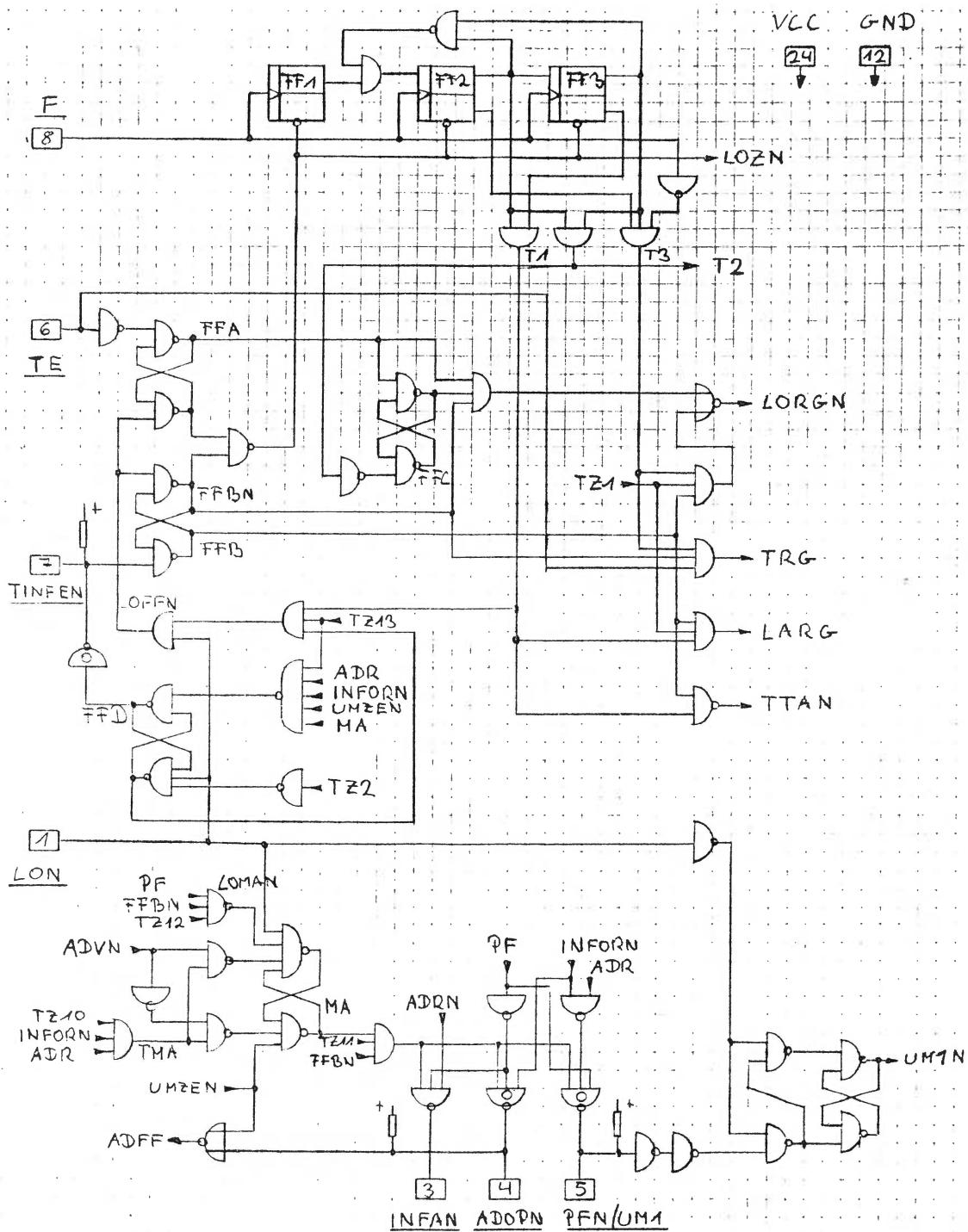

2.5

## Interne Schaltung

Teil 1

Alle Rechte aus diesen Unterlagen und ihrem Inhalt behalten wir uns vor (BGB, UWG, LItUrhG). Unberechtigte Verwertung, Weitergabe oder Vervielfältigung von Unterlagen oder deren Inhalt verpflichtet zu Schadenersatz.

|                   |                 |                              |  |                      |             |

|-------------------|-----------------|------------------------------|--|----------------------|-------------|

| 4/0<br>Ausg./Änd. | 1.6.77<br>Datum | 1-1-1-6-1<br>Dokument-Nummer |  | 14<br>nächstes Blatt | 13<br>Blatt |

|-------------------|-----------------|------------------------------|--|----------------------|-------------|

## Teil 2

Alle Rechte aus diesen Unterlagen und ihrem Inhalt behalten wir uns vor (BGB, UWG, LittUrhG).

Unberechtigte Verwertung, Weitergabe oder Vervielfältigung von Unterlagen oder deren Inhalt verpflichtet zu Schadensersatz.

|            |        |                 |         |                |       |

|------------|--------|-----------------|---------|----------------|-------|

| 4/0        | 1.6.77 | 1-1-1-6-1       | Kapitel | 15             | 14    |

| Ausg./Änd. | Datum  | Dokument-Nummer |         | nächstes Blatt | Blatt |

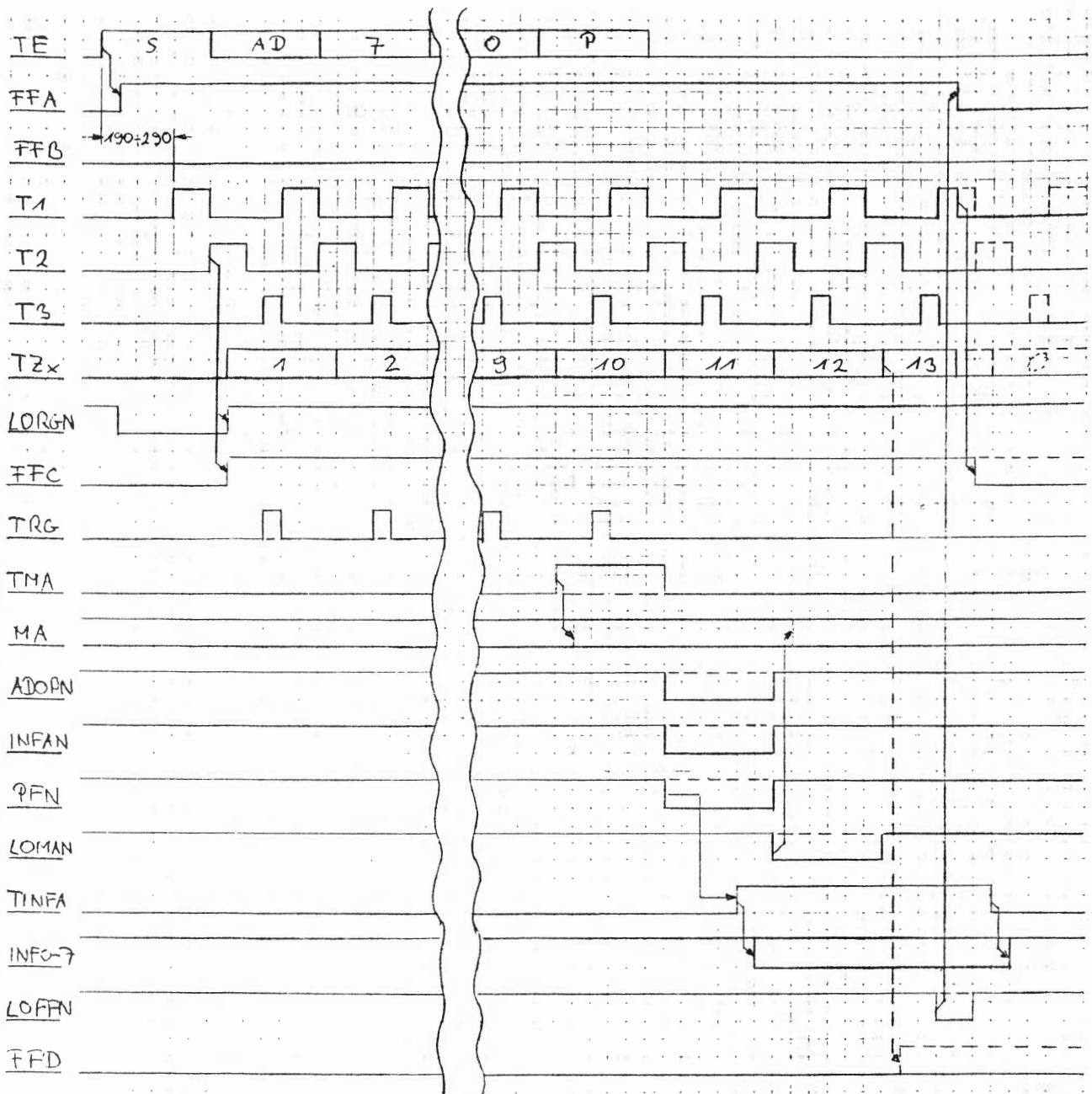

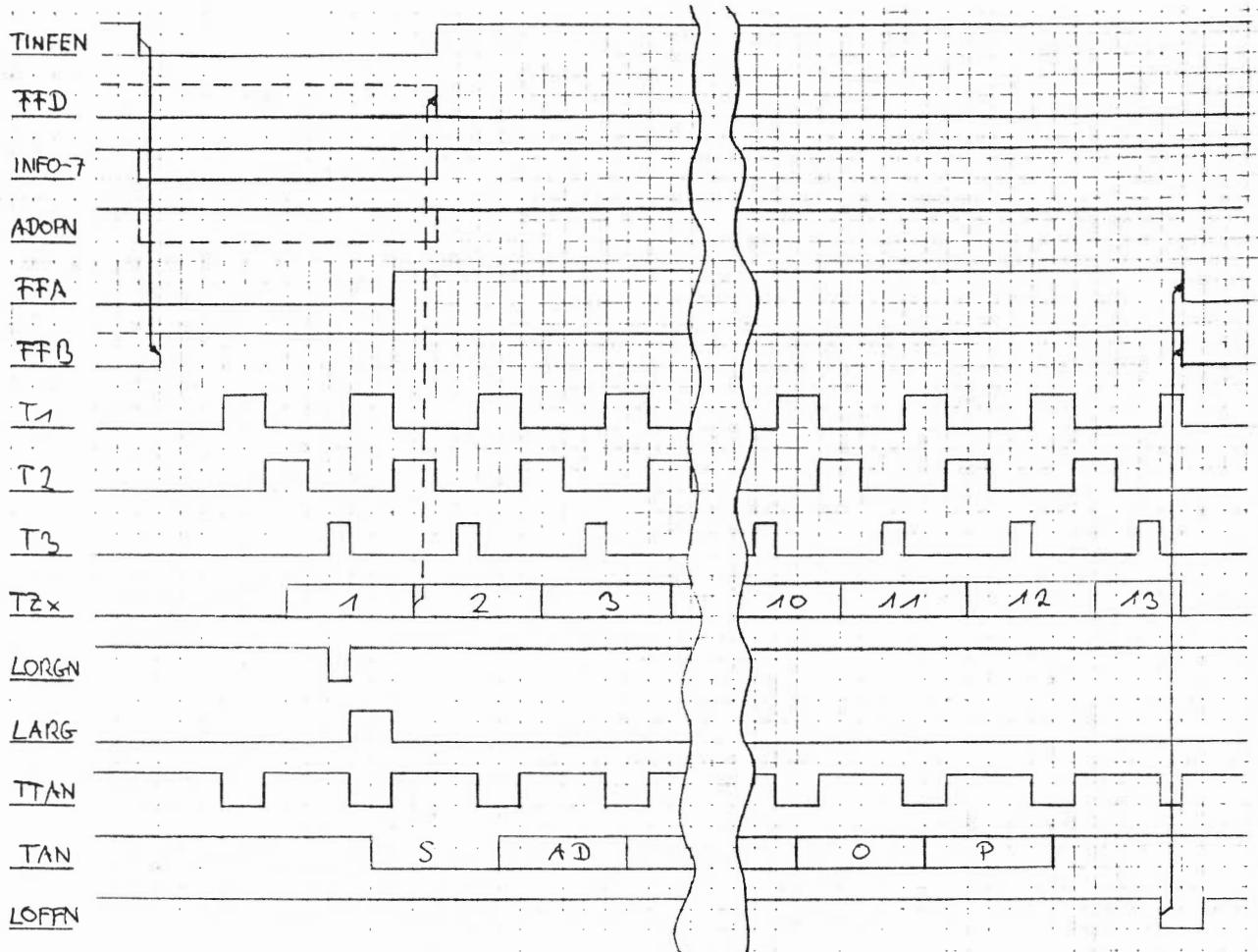

2.6

Interne Taktung

Empfangen

Alle Rechte aus diesen Unterlagen und ihrem Inhalt behalten wir uns vor (BGB, UWG, LitUrhG).

Unberechtigte Verwertung, Weitergabe oder Vervielfältigung von Unterlagen oder deren Inhalt verpflichtet zu Schadenersatz.

|                   |                 |                              |  |                      |             |

|-------------------|-----------------|------------------------------|--|----------------------|-------------|

| 4/0<br>Ausg./Änd. | 1.6.77<br>Datum | 1-1-1-6-1<br>Dokument-Nummer |  | 16<br>nächstes Blatt | 15<br>Blatt |

|-------------------|-----------------|------------------------------|--|----------------------|-------------|

Senden

|                   |                 |                              |  |                      |             |

|-------------------|-----------------|------------------------------|--|----------------------|-------------|

| 4/0<br>Ausg./Änd. | 1.6.77<br>Datum | 1-1-1-6-1<br>Dokument-Nummer |  | 17<br>nächstes Blatt | 16<br>Blatt |

|-------------------|-----------------|------------------------------|--|----------------------|-------------|

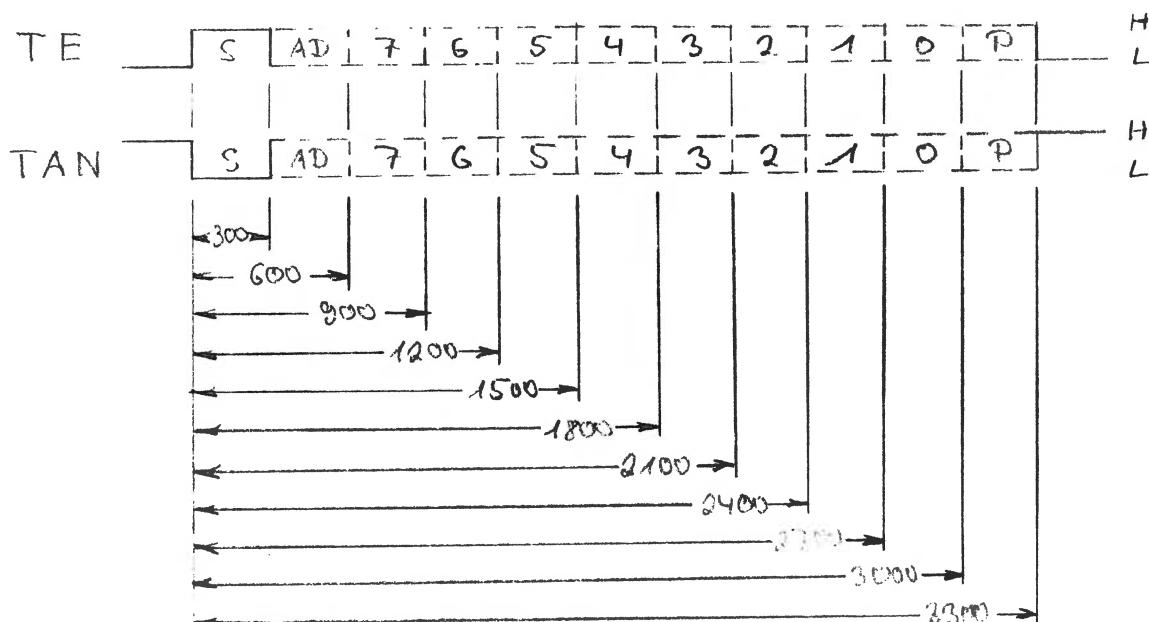

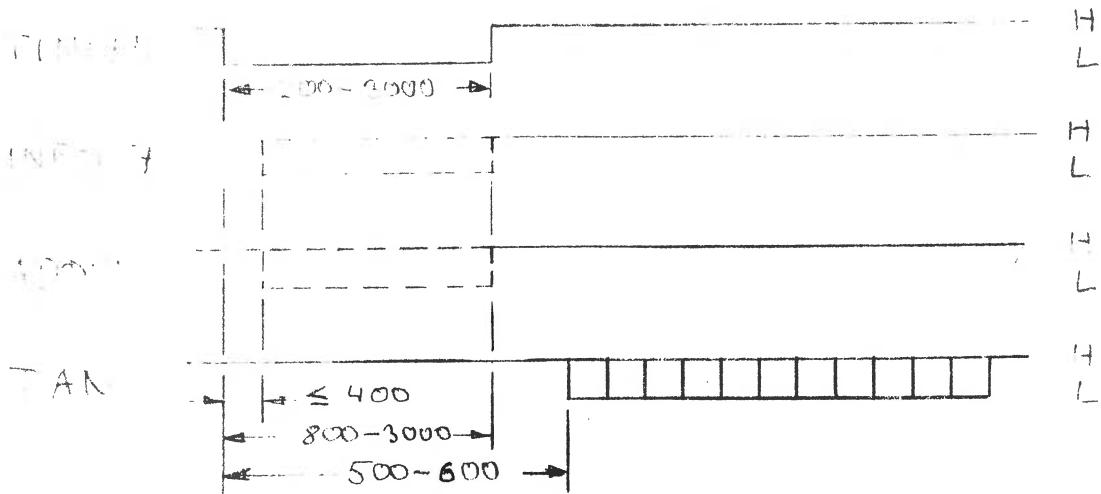

2.7 Externe TaktungZeiten der seriellen Daten an TE bzw. TAN

Zeiten in nsec.

Für TE gelten die Zeiten mit einer Toleranz von  $\pm 40$  nsec,

für TAN von  $\pm 20$  nsec.

Taktplan: Master sendet AD, OP, AG

|                  | ADOPN | INFO |

|------------------|-------|------|

| Master sendet AD | L     | L    |

| Master sendet OP | L     | H    |

| Master sendet AG | H     | X    |

Zeiten in nsec.

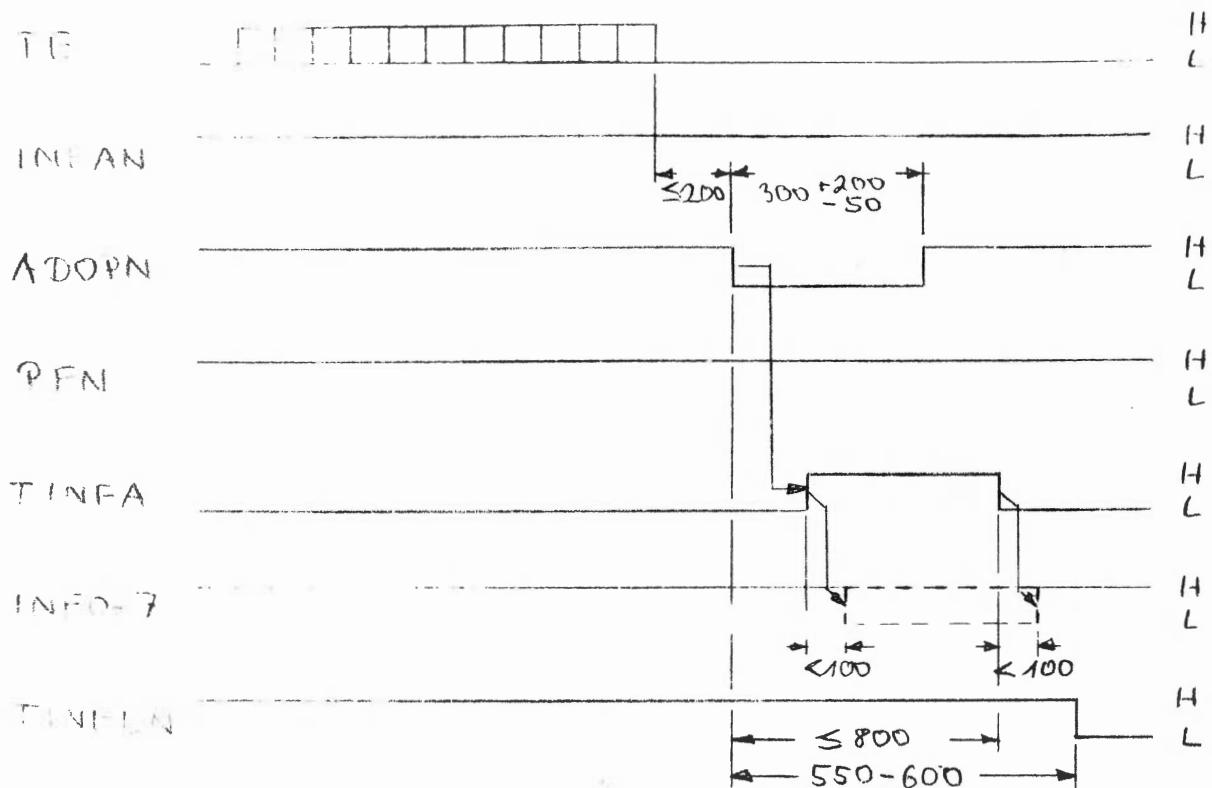

Taktplan: Slave empfängt AD

ADOPN und TINFIN erscheinen nur bei Adreßgleichheit und positiver Parityprüfung. Gleichzeitig wird der Adreßmerker gesetzt.

Zeiten in nsec.

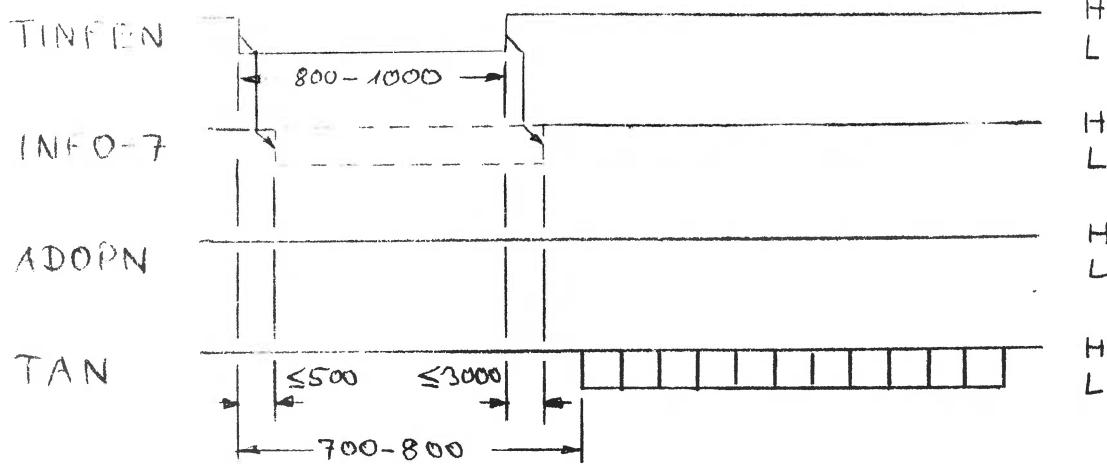

Taktplan: Slave sendet EG

TINFEN : siehe „Slave empfängt AD.“

Zeiten in nsec.

|            |        |                 |         |                |       |

|------------|--------|-----------------|---------|----------------|-------|

| 4/0        | 1.6.77 | 1-1-1-6-1       |         | 21             | 20    |

| Ausg./Änd. | Datum  | Dokument-Nummer | Kapitel | nächstes Blatt | Blatt |

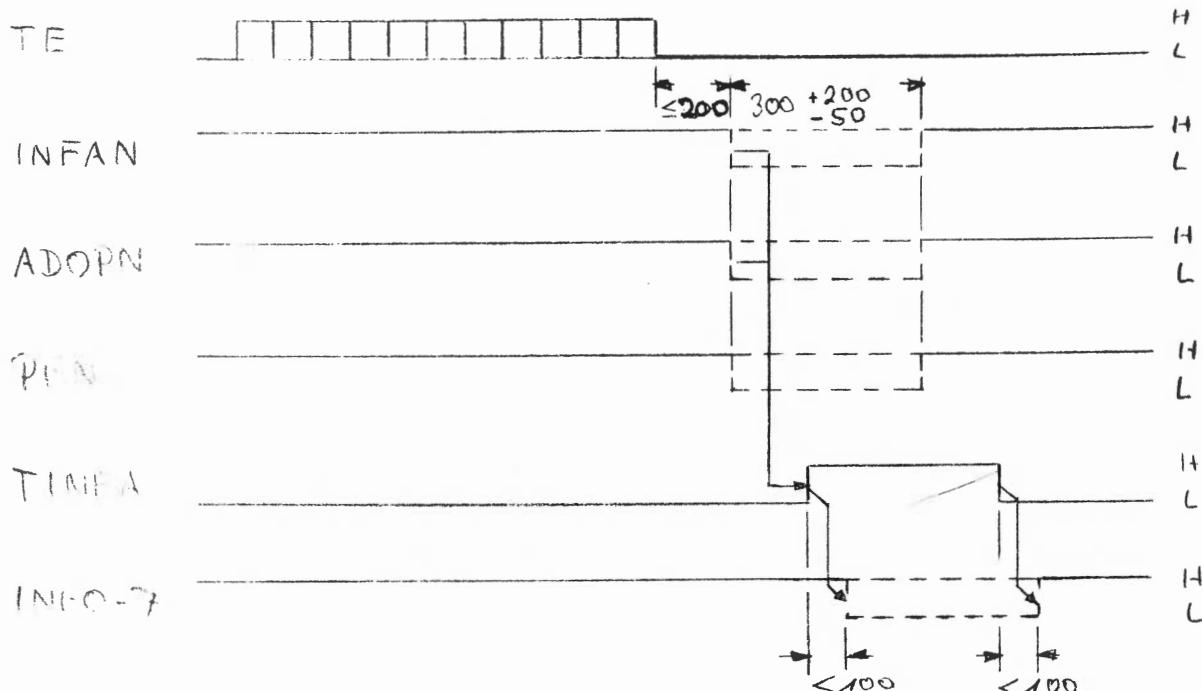

Taktplan: Master empfängt EG,

Slave empfängt AG, OP

Zeiten in nsec.

|                             | INFAN | ADOPN | PFN |

|-----------------------------|-------|-------|-----|

| Master empfängt EG ohne PF  | L     | H     | H   |

| Master empfängt EG mit PF   | H     | H     | L   |

| Slave * empfängt AG ohne PF | L     | H     | H   |

| Slave empfängt AG mit PF    | H     | H     | L   |

| Slave empfängt OP ohne PF   | H     | L     | H   |

| Slave empfängt OP mit PF    | H     | H     | L   |

\* Im Slave erscheinen die Ausgangstakte nur, wenn der Adressmerker gesetzt ist. Nach einem Signal PFN im Slave wird der interne Merker gelöscht.

|            |        |                     |         |                |       |

|------------|--------|---------------------|---------|----------------|-------|

| 4/0        | 1.6.77 | 1-1-1-6-1           |         | --             | 21    |

| Ausg./Änd. | Datum  | Dokument-Nr./Innner | Kapitel | nächstes Blatt | Blatt |