TELEFUNKEN

COMPUTER

## Eigenschaften des RD 441

SYSTEM TR 440

## **TR 440** **Eigenschaften des RD 441**

### **EINFÜHRUNG**

**Stand Januar 1972**

Unter RD 441 wird die Zentraleinheit (Rechner, digital) eines TR 440-Rechensystems verstanden, diejenige Funktionseinheit also, die die eigentliche Rechenleistung erbringt.

Mit einer angemessenen Ausstattung an peripheren Einheiten und zusammen mit den aus dem Teilnehmer-Betriebssystem und dem Programmiersystem bestehenden Grundprogrammen bildet die Zentraleinheit universell anwendbare Rechensysteme, insbesondere das **Teilnehmer-Rechensystem (Time-Sharing-System)**.

TELEFUNKEN COMPUTER GmbH

775 Konstanz

Max-Stromeyer-Str. 116

Postfach 142

Bestell-Nr. : 440.A1.04

Ausgabe: 0272-VS1/Pi

Vervielfältigungen und Nachdruck, auch

auszugsweise, bedürfen unserer Zustimmung

## VORBEMERKUNGEN

Diese Schrift soll weniger die Gesamtkonzeption, den Aufbau, konstruktive oder funktionelle Besonderheiten, als vielmehr die für den Systemprogrammierer wesentlichen Eigenschaften der Zentraleinheit RD 441 im Rahmen des TR 440 Teilnehmer-Rechensystems erläutern.

Zum besseren Verständnis der Eingliederung der Zentraleinheit in TR 440-Rechensysteme wird die Lektüre der Kurzbeschreibung

[1] TR 440 Teilnehmer-Rechensystem

empfohlen, aber nicht vorausgesetzt.

Auf der gleichen Informationsebene wie die der vorliegenden Schrift sind die wichtigsten Eigenschaften der übrigen Komponenten der TR 440-Rechensysteme erläutert in

[2] TR 440 Teilnehmer-Betriebssystem

[3] TR 440 Programmiersystem

Für die Peripherie, die mit dem RD 441 zusammen eine Rechenanlage bilden, sei auf zahlreiche Informationsblätter und auf die Broschüre

[4] TR 440 Daten

verwiesen, soweit die in der Schrift [1] angegebenen Werte nicht ausreichen.

Der Befehlsumfang für den RD 441 wird zum Nachschlagen in der Schrift

[5] TR 440 Große Befehlsliste

und sehr ausführlich mit allen Nebenwirkungen der Befehle in

[6] TR 440 Befehlslexikon

beschrieben.

## INHALTSVERZEICHNIS

|          |                                                              |    |

|----------|--------------------------------------------------------------|----|

| 1.       | ÜBERBLICK                                                    |    |

| 1. 1.    | Einführende Beschreibung des RD 441                          | 1  |

| 1. 2.    | Die Wortstruktur des RD 441                                  | 3  |

| 2.       | RECHNERKERN                                                  |    |

| 2. 1.    | Das Rechenwerk                                               | 9  |

| 2. 2.    | Das Befehlswerk                                              | 11 |

| 2. 3.    | Die Adressierungsmodi                                        | 17 |

| 3.       | ZENTRALSPÉICHER                                              |    |

| 3. 1.    | Speicherorganisation                                         | 19 |

| 3. 1. 1. | Speichermodulen und Adressenverschränkung                    | 19 |

| 3. 1. 2. | Seiten und Kacheln                                           | 20 |

| 3. 1. 3. | Hardwareseitige Belegung der Speicher-<br>kachel 0           | 22 |

| 3. 2.    | Die Speicherzuteilung                                        | 23 |

| 3. 2. 1. | Aufteilung und Belegung von Prozeß-<br>leitblöcken           | 24 |

| 3. 2. 2. | Adressierung der Seiten-Kachel-Tabelle<br>im Prozeßleitblock | 26 |

| 3. 3.    | Die Speicheransteuerung                                      | 28 |

| 3. 4.    | Der Indexspeicher                                            | 32 |

| 4.       | EA-WERK                                                      |    |

| 4. 1.    | Die Speicherkachel 1                                         | 35 |

| 4. 2.    | Der EAW-Befehl                                               | 36 |

| 4. 3.    | EA-Vorgang                                                   | 37 |

| 4. 4.    | Register des EA-Werks                                        | 37 |

|          |                                                                    |    |

|----------|--------------------------------------------------------------------|----|

| 5.       | UNTERBRECHUNGSSYSTEM                                               |    |

| 5. 1.    | Die Eingriffe                                                      | 41 |

| 5. 1. 1. | Die Eingriffsarten                                                 | 41 |

| 5. 1. 2. | Das Eingriffswort                                                  | 42 |

| 5. 1. 3. | Hardwareseitige Vorgänge beim<br>Eintreffen eines Eingriffs        | 43 |

| 5. 1. 4. | Die Eingriffssperre                                                | 45 |

| 5. 2.    | Die Alarne                                                         | 45 |

| 5. 2. 1. | Die Alarmarten und ihre Einteilung<br>in Gruppen                   | 46 |

| 5. 2. 2. | Die Alarmsperren                                                   | 48 |

| 5. 2. 3. | Hardwareseitige Vorgänge bei Eintreffen<br>eines Alarms            | 48 |

| 5. 3.    | Die Unterbrechung von Befehlen                                     | 50 |

| 6.       | MAKROS UND SSR-BEFEHLE                                             |    |

| 6. 1.    | Hardwareseitige Vorgänge bei Er-<br>kennen eines Leercodes (Makro) | 53 |

| 6. 2.    | Hardwareseitige Vorgänge bei Er-<br>kennen eines SSR-Befehls       | 54 |

| 7.       | BILDVERZEICHNIS                                                    | 56 |

| 8.       | SACHVERZEICHNIS                                                    | 57 |

## 1.

## ÜBERBLICK

1.1.

Einführende Beschreibung des RD 441

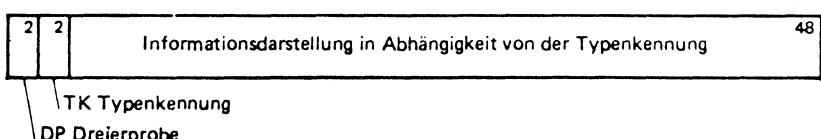

Der Digitalrechner RD 441 (zentraler Rechner von Rechenanlagen TR 440) ist eine Eindreßmaschine, die Information wortweise parallel verarbeitet. Ein Wort besteht aus 52 Binärstellen, von denen je 2 für hardwareseitige Typenkennung und Dreierprobeneprüfung, die verbleibenden 48 für die eigentliche Informationsdarstellung verwendet werden.

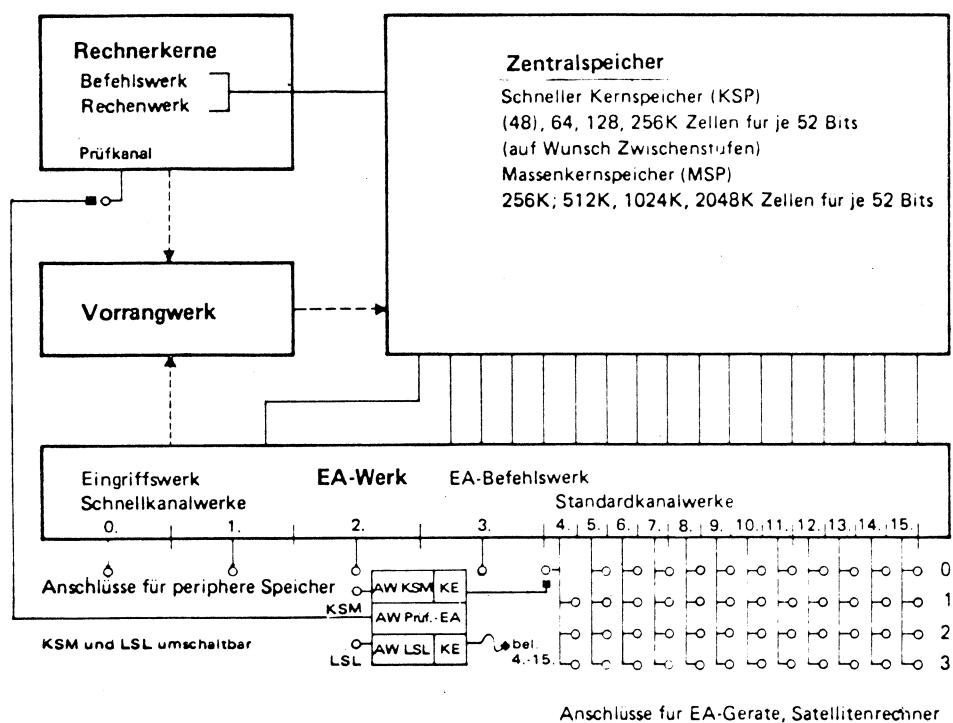

Unabhängig vom jeweiligen Ausbau wird der RD 441 gegliedert in die Hauptbestandteile:

Rechnerkern,

Zentralspeicher (Speicherwerk),

Vorrangwerk und

EA-Werk (Eingabe/Ausgabe-Werk);

deren funktioneller Zusammenhang in Bild 1 grob veranschaulicht ist. Untergeordnete Werke oder Bestandteile der nächsten Ebene sind im Bild durch die nächst kleinere Schrift kenntlich gemacht. Kanalwerke und Geräteanschlüsse (Übergabestellen) im Bild entsprechen dem Vollausbau des RD 441.

Bild 1 Digitalrechner RD 441 - Werke im Zusammenhang

Verschiedene Ausbauumfänge des RD 441 unterscheiden sich in der Kapazität des Zentralspeichers sowie in der Ausstattung des EA-Werks mit Kanalwerken unterschiedlicher Leistung, Zusammensetzung und Anzahl. Der RD 441 kann außerdem mit einem zweiten Rechnerkern ausgestattet werden.

#### Rechnerkern

Der Rechnerkern ist untergliedert in Befehlswerk, Rechenwerk und Mikroprogramme, mit denen die rund 240 fest verdrahteten Befehle realisiert werden. Je zwei Befehle (mit Ausnahme der EAW-Befehle) belegen ein Ganzwort, wobei verschiedene Befehlsformate möglich sind. Neben Festpunkt- und Gleitpunktoperationen einfacher und doppelter Genauigkeit sind Transportoperationen, boolesche Operationen, Indexoperationen, Modifizier-, Ersetz- und Registeroperationen, Tabellendurchsuchoperationen, Zeichentransporte sowie eine Reihe von Verzweigungsoperationen im Befehlsvorrat enthalten. Zur Adressierung im Hauptspeicher sind vier verschiedene Adressierungsmodi verdrahtet.

#### Zentralspeicher

Aufgabe des Zentralspeichers ist es, als sogenannter Hauptspeicher ständig benötigte Teile der Grundprogrammausstattung und Benutzerprogramme bei deren Läufen zu unmittelbarer Verfügung des Rechnerkerns aufzunehmen. Der Zentralspeicher gliedert sich in einen schnellen Kernspeicher (KSP) und einen Massenkernspeicher (MSP), zwei Ferritkernspeicher mit unterschiedlichen Zeiteigenschaften.

Der schnelle Kernspeicher ist aus Modulen mit je 16 K Speicherzellen (für Worte aus 52 Bits) zusammengesetzt. Jeder Modul verfügt über eigene Funktionssteuerung. Der schnelle Kernspeicher ist lieferbar in Stufen von (48 K), 64 K, 128 K und 256 K Zellen, entsprechend 3, 4, 8 und 16 Modulen (sowie auf Wunsch in Zwischengrößen). Die Zykluszeit des einzelnen KSP-Moduls beträgt 0,9  $\mu$ s. Bei mehreren KSP-Modulen realisierte Adressenverschränkung und Zyklenüberlappung führt in Abhängigkeit von der Zahl der Speichermodulen und damit in Abhängigkeit von der Ausbaustufe zu einer wesentlich verkürzten Zykluszeit des Gesamtspeichers.

Der Massenkernspeicher, dessen Modulen (MSP-Modulen) eine Zykluszeit von 2,1  $\mu$ s besitzen, kann nachträglich eingebaut bzw. erweitert werden. Er hat die Ausbaustufen 512 K, 1024 K oder 2048 K, wobei es sich um 1, 2 oder 4 Modulen zu je 512 K handelt. Vorgesehen sind außerdem Modulen zu 256 K. Auch der Massenkernspeicher ist also aus voneinander unabhängigen Speichermodulen aufgebaut, was wieder eine gewisse Reduzierung der effektiven Zykluszeit zur Folge haben kann.

#### Vorrangwerk

Das Vorrangwerk koordiniert auf den Speicher gerichtete Zugriffswünsche des Rechnerkerns und verschiedener Teile des EA-Werks abhängig vom Rang des jeweiligen Zugreifers und davon, ob die dabei angesprochenen Speichermodulen frei sind. Das Vorrangwerk ist an sich vom Rechnerkern und vom EA-Werk unabhängig und steht dem Zentralspeicher am nächsten (gleichsam in der Rolle eines Pförtners). Aus Gründen einer übersichtlichen Systematik als gesondertes Werk angesehen, ist es aus technischen Gründen zusammen mit einem Teil des EA-Werks realisiert.

## EA-Werk

Das EA-Werk hat als Ganzes die Aufgabe, den gesamten, unabhängig vom Rechnerkern betriebenen EA-Verkehr abzuwickeln. Es besteht aus dem EA-Befehlswerk, das bis zu 5 Befehle simultan ausführen kann, sowie maximal 4 Schnellkanalwerken und 12 Standardkanalwerken. Jeder Standardkanal besitzt 4 Anschlußmöglichkeiten für EA-Geräte oder auch Satellitenrechner. Von einem Schnellkanal kann ein peripherer Speicher (als Hintergrundspeicher) angesteuert werden, womit über ein vollausgebautes EA-Werk maximal 52 periphera Geräte hardwareseitig betrieben werden können. Standardkanäle erlauben Übertragungsraten (bei 10 m Kabellänge) von 700 000 Bytes/s, Schnellkanäle Übertragungsraten von 3 000 000 Bytes/s (Bytes zu 8 Bits). Da jedem der Schnellkanalwerke ein eigenes EA-Befehlsregister zugeordnet ist, können die an sie angeschlossenen Geräte parallel betrieben werden. Für die Standardkanalwerke steht insgesamt ein Register im EA-Befehlswerk zur Verfügung, so daß die Standardkanäle im Zeitmultiplex betrieben werden.

## Prüfkanal, KSM und LSL

Neben den Kanalwerken des EA-Werks gibt es noch einen Prüfkanal am Rechnerkern zum Einschleusen des Betriebssystem-Urstartprogramms und zur Wartung. Der Prüfkanal ermöglicht es, bestimmte Befehle in die einzulesende Information einzustreuen, die sofort ausgeführt werden. Wie aus Bild 1 ersichtlich, werden die Kontrollschrifbmaschine (KSM) und ein Lochstreifenleser (LSL) über die erforderlichen Anpaßwerke (AW) und Korrespondenzeinrichtungen (KE) so an den Prüfkanal und an Standardkanalwerke angeschlossen, daß sie dazwischen umgeschaltet werden können. Für den Operateur wird die KSM - außer zu Ureingaben - auf Kanal 0 des Kanalwerks 4 geschaltet. Wird statt des zur Grundausstattung des Rechners gehörenden LSL für Elementareingabe ein schnell arbeitender LSL angeschlossen, so kann dieser auch über ein Standardkanalwerk betrieben werden (umschaltbar).

## 1.2. Die Wortstruktur des RD 441

Die wesentliche Informationseinheit ist das Ganzwort. Es ist 52 Bits lang, von denen die ersten beiden als Dreierprobenprüfstellen, die beiden folgenden zur Kennzeichnung des Worttyps verwendet werden (Typenkennung). Die restlichen 48 Bits dienen für die Aufnahme der eigentlichen Information.

Bild 2a Allgemeines Maschinenwort des RD 441

Die durch die Typenkennung 0 und 1 gekennzeichneten Worttypen werden gemeinsam als Zahlworte interpretiert. Jedes Zahlwort im Speicher enthält eine Binärstelle für die Marke, die durch das Programm eingesetzt und abgefragt werden kann. Wird ein markiertes Wort in ein Register übernommen, so wird die Marke abgespalten und in das Markenregister M übernommen. Die Markenstelle im Register wird vorzeichengleich gesetzt und dient als Überlauf-Auffangstelle.

Die im Speicher, im Rechenwerk und im Bereitadressen-Register auftretenden negativen Zahlwerte werden im (b-1)-Komplement dargestellt: in der Vorzeichen- und in den Ziffernstellen ist die binäre Null (0) mit der binären Eins (1) vertauscht und umgekehrt. Die Null besitzt daher die Darstellungen 0|000 ... 000 für +0 und L|LLL ... LLL für -0. Da dadurch eine negative Zahl in ihrer Komplementdarstellung z. B. als Ganzwort <1 um  $(1 - 2^{-46})$  zu groß ist, wird eine Summe aus zwei negativen Zahlen oder eine positive Differenz durch Einerrücklauf von der vordersten Stelle links zur Einerstelle um  $(1 - 2^{-46})$  verringert. Der Einerrücklauf bewirkt also, daß bei L-Überlauf der höchsten Vorzeichenstelle eine 1 zur Einerstelle addiert wird.

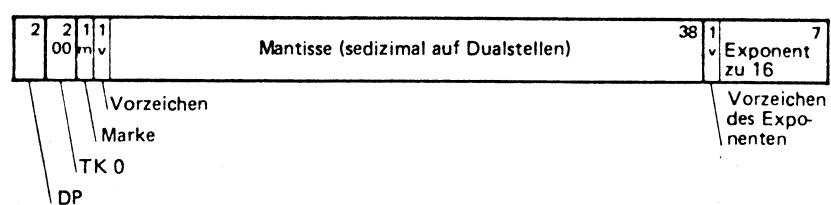

## Sedezimale Gleitpunktzahl

Die Gleitpunktdarstellung von Zahlen eignet sich vor allem für technisch-wissenschaftliche Berechnungen, bei denen sich sehr oft die Größenordnung der Zwischenergebnisse nicht abschätzen lassen bzw. der Specheraufwand (und damit auch der Rechenaufwand) bei Berücksichtigung aller möglichen Fälle viel zu hoch wäre, um wirtschaftlich noch vertretbar zu sein.

Die Gleitpunktdarstellung bietet die Möglichkeit, bequem mit Zahlen sehr verschiedener Größenordnung rechnen zu können, was freilich in einigen Zusammenhängen besondere Aufmerksamkeit gegenüber der Fehlerentwicklung dabei erfordert. Die Rechenergebnisse werden i. a. normalisiert, d. h. so geschiftet, daß Überläufe beseitigt und die vorhandenen Binärstellen vollständig ausgenutzt werden.

Beim RD 441 beträgt die einfache Rechengenauigkeit umgerechnet 10 Dezimalstellen.

Die Darstellung einer Gleitpunktzahl  $x$  erfolgt in der Form:

$$x = a \cdot 16^c$$

mit  $a \geq 0$  als 38 stelliger Mantisse und  $c$  als 7 stelligem Exponenten. Sedenzimal heißt die Darstellung, weil die Basis 16 ist. Einer Sedenzimalstelle entsprechen 4 Dual- bzw. Binärstellen.

### Bild 2b Sedenzimale Gleitpunktzahl (auf Dualstellen)

Die 38 Binärstellen der Mantisse haben von links nach rechts die Wertigkeiten  $2^{-1}$ ,  $2^{-2}$ , ...,  $2^{-38}$ . Es sind also Vielfache von  $2^{-38}$  bis zum Wert  $1 - 2^{-38}$  darstellbar.

Bei normalisierten Gleitpunktzahlen zur Basis 16 muß mindestens eine der vier höchstwertigen Binärstellen L sein. Damit ist der kleinste Betrag der Mantisse bei normalisierter Darstellung  $2^{-4}$ . Der Betrag des größten Mantissenwertes ist  $1 - 2^{-38}$ .

Die Binärstellen des Exponenten haben von links nach rechts die Wertigkeiten  $2^6, 2^5, \dots, 2^0$ , so daß der Exponent c den Bereich von  $-127 < c \leq +127$  überstreckt.

Normalisierte Gleitpunktzahlen x einfacher Genauigkeit liegen also stets im Bereich:

$$2^{-4} \cdot 16^{-127} \leq |x| \leq (2^0 - 2^{-38}) \cdot 16^{127} \quad \text{oder}$$

$$2^{-512} \leq |x| \leq 2^{508} - 2^{470} \quad \text{entsprechend}$$

$$7,458\ 341 \cdot 10^{-155} \leq |x| \leq 8,379\ 881 \cdot 10^{152}.$$

Die Gleitpunkt-Arithmetik setzt normalisierte Operanden voraus und liefert i. a. auch wieder normalisierte, in Abhängigkeit von der höchsten unwesentlichen Stelle gerundete Ergebnisse. Entsteht bei der Rechnung ein Exponent  $c > 127$ , so wird die richtige Mantisse, aber ein Exponent  $c-255$  gebildet und arithmetischer Alarm gemeldet. Eine Überschreitung des Exponentenbereichs nach unten wird nicht vollzogen.

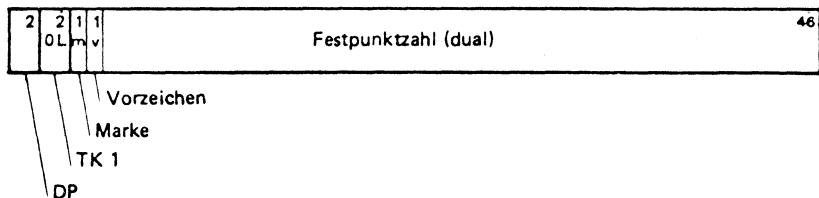

#### Duale Festpunktzahl

Diese Zahlendarstellung eignet sich besonders für Anwendungen, bei denen die Größenordnungen der Eingangsdaten, der Zwischenergebnisse und der Endergebnisse überschaubar sind.

Es steht im Belieben des Programmierers, die Lage des Dualpunkts festzusetzen. Für Additionen, Subtraktionen und Vergleiche ist jedoch auf gleiche Dualpunktstellung in den zu vergleichenden Größen zu achten. Gegebenenfalls ist vorher durch Schiften die Stellungsgleichheit herbeizuführen (Ausrichten).

Bild 2c Duale Festpunktzahl

Bei Rechnung mit dualen Festpunktzahlen beträgt die einfache Rechengenauigkeit 13 Dezimalstellen.

- Wird der Dualpunkt (das Komma) linksbündig vor die erste (höchste) Dualstelle gesetzt, dann sind Zahlen z im Bereich von

$$-(1 - 2^{-46}) < z < +(1 - 2^{-46}) \quad \text{entsprechend}$$

$$-(1 - 1,421\ 086 \cdot 10^{-14}) \leq z \leq +(1 - 1,421\ 086 \cdot 10^{-14})$$

darstellbar.

- Wird der Dualpunkt (das Komma) rechtsbündig hinter die letzte (niedrigste) Dualstelle gesetzt, dann sind Zahlen z im Bereich von

$$-(2^{46} - 1) \leq z \leq 2^{46} - 1 \quad \text{entsprechend}$$

$$-70\ 368\ 744\ 177\ 663 \leq z \leq +70\ 368\ 744\ 177\ 663$$

darstellbar.

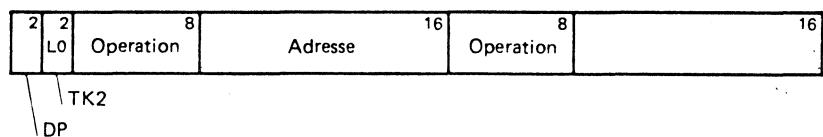

Befehlspaar

(Befehle für Rechnerkern)

Ein Maschinenwort nimmt zwei Maschinenbefehle auf. Jeder Befehl hat einen 8 Binärstellen langen Operationsteil (-Code) und einen 16 Binärstellen langen Adreßteil.

Bild 2d Befehlspaar - Einadressenbefehle

Von den 256 möglichen Operationscodes auf 8 Bits sind ca. 240 fest verdrahtet, die restlichen stehen für softwaremäßig festzulegende Befehle (besonders Makros) zur Verfügung. Da ein Ganzwort also stets aus zwei Befehlen bestehen kann, können mit 1 K, nämlich 1024 Ganzwörtern 2048 Befehle dargestellt werden.

Mit einem 16-Bit-Adreßteil lassen sich genau 65 536 Befehle adressieren (Halbwortadressierung) oder anders ausgedrückt, durch den 16-Bit-Adreßteil können die Adressen aller 64 K Befehle unterschieden werden, die in 32 K Speicherzellen (für je ein Ganzwort) abgelegt sein können. Dieser so überstreichbare Adressenbereich wird auch "16-Bit-Adressenraum" genannt (entsprechend einer Großseite aus 32 K zusammenhängend gespeicherten Ganzworten).

Damit mehr als 32 K Ganzwörte direkt adressiert werden können, arbeitet das Befehlswerk (Adressenregister und Befehlszähler) mit 22-Bit-Adressen, hervorgehend aus nach links verlängerten 16-Bit-Adressen.

(Vgl. [5], Modifizierbefehle)

Mit einer 22-Bit-Adresse ist eine direkte Adressierung von  $2^{22}$  Halbworten möglich, bei Erweiterung des RD 441 mit einem Massenkernspeicher können also insgesamt 2048 K Ganzwörte direkt adressiert werden.

Aus dem Speicher wird stets ein Befehls-Ganzwort ausgelesen und zunächst der Befehls mit der geraden Adresse (linkes Halbwort) entschlüsselt und ausgeführt, dann der mit der ungeraden Adresse. Bei Sprung auf einen Befehl mit ungerader Adresse wird nach dem Auslesen des Ganzwortes unmittelbar der Befehl mit der ungeraden Adresse entschlüsselt und ausgeführt.

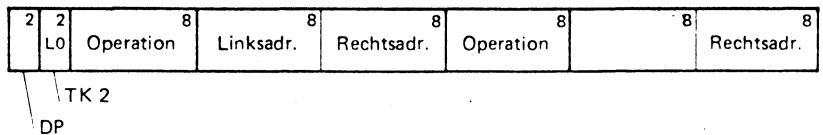

Der Adreßteil eines Befehls kann in eine Links- und in eine Rechtsadresse von je 8 Binärstellen unterteilt werden.

Bild 2e Befehlspaar - Zweiadressenbefehle

Dieses Format wird bei der Adressierung von Index-Zellen zur Angabe von Parametern und Spezifikationen, bei Doppelcodebefehlen usw. verwendet (Es können auch beide Befehlsformate in einem Wort auftreten).

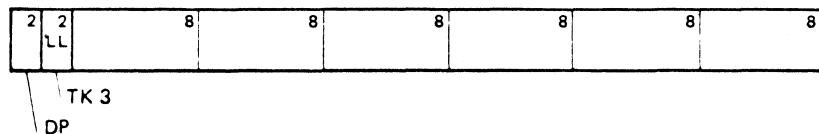

Textwort

(alphanumerisches Wort)

Ein Zentralcodezeichen des RD 441 besteht aus 8 Bits, das ist eine Oktade. Somit können 6 Oktaden (Bytes) in einem Ganzwort untergebracht werden.

Bild 2f Textwort - 6 Bytes (Oktaden)

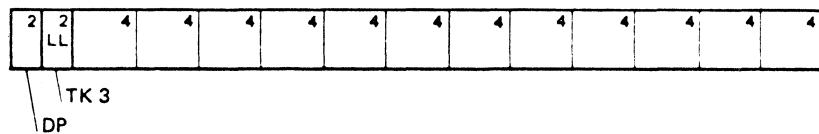

Mittels der Befehle BNZ und CNZ sind zusätzlich die folgenden Wortformate interpretierbar:

Bild 2g Textwort - 12 Tetraden

Bild 2h Textwort - 8 Hexaden

Bild 2i Textwort - 4 Viertelworte

## RECHNERKERN

Unter Rechnerkern wird ein Prozessor zum Rechnen (im weitesten Sinne) verstanden, ohne Speicher (abgesehen von Registern) und gesondert vom EA-Werk. Ein Rechnerkern des RD 441 besteht aus Rechenwerk und Befehlswerk einschließlich Mikroprogrammwerk. Es ist möglich, zwei Rechnerkerne einzubauen.

### 2.1. Das Rechenwerk

Das Rechenwerk führt die durch einen Befehl geforderten Rechenoperationen durch. Es arbeitet unabhängig vom EA-Werk und vom Speicher sowie bei reinen Rechenoperationen auch unabhängig vom Befehlswerk, so daß während der Ausführung einer nur das Rechenwerk belegenden Operation das Befehlswerk schon den im Programm nächsten Befehl aus dem Speicher abrufen und entschlüsseln kann. Über ein zum Rechenwerk gezähltes Sammelregister (das auch Verteilaufgaben hat) stehen Rechenwerke und Befehlswerke mit dem Zentralspeicher in Verbindung. Es puffert die in beiden Richtungen transportierten Operanden und Befehle. Das Rechenwerk enthält folgende Register:

| Bezeichnung | Kurzbez. | Anzahl<br>Binärst. | Name des Registers                       |

|-------------|----------|--------------------|------------------------------------------|

|             |          |                    |                                          |

| RA          | A        | 52                 | Akkumulator                              |

| RB          |          | 52                 | Akkumulator-Hilfsregister                |

| RC          |          | 52                 | Rückstellregister für RB                 |

| RQ          | Q        | 52                 | (Multiplikator-)Quotienten-Register      |

| RP          |          | 52                 | (Multiplikator-)Quotienten-Hilfsregister |

| RU          |          | 52                 | Übertragsregister                        |

| RV          |          | 48                 | Übertrags-Hilfsregister                  |

| RD          | D        | 52                 | Multiplikanden-Register                  |

| RH          | H        | 52                 | Hilfsregister                            |

| RY          | Y        | 8                  | Schifzähler                              |

| RZ          |          | 8                  | Hilfsregister für RY                     |

| RX          |          | 8                  | Exponentenzähler                         |

| RW          |          | 8                  | Hilfsregister für RX                     |

| RM          | M        | 1                  | Markenregister                           |

| RS          |          | 52                 | Sammelregister                           |

| RT          |          | 52                 | Rückstellregister für RS                 |

= dem Programmierer durch Maschinenbefehle zugänglich.

Die Funktionen der Rechenwerksregister sind im einzelnen:

RA Akkumulator

RB Akkumulator Hilfsregister

RC Rückstellregister für RB

Im Akkumulator werden die meisten Rechenoperationen ausgeführt. Er enthält vor der Ausführung eines Befehls, der das Rechenwerk beansprucht, einen Operanden, nach Befehlausführung das Ergebnis. Der Akkumulator kann unter Zuhilfenahme von RB vielfältige Transporte ausführen. Für interne Vorgänge wird von RB das Rückstellregister RC benötigt.

RQ (Multiplikator-) Quotienten-Register

RP Hilfsregister

RQ enthält bei Division und Multiplikation das Ergebnis oder einen Teil des Ergebnisses. Zusammen mit dem Akkumulator RA kann RQ zu einem Register doppelter Länge verbunden werden. Das Hilfsregister RP ist für interne Abläufe erforderlich.

RU Übertragungsregister

RV Übertragungs-Hilfsregister

Das Register RU nimmt Überträge für Operationen im RA, RB und RD auf. Das Übertragungs-Hilfsregister RV ist für numerische Rechenvorgänge erforderlich.

RD Multiplikandenregister

RD nimmt in der Regel den zweiten Operanden nach der Ausführung einer Rechenwerksoperation auf.

RH Hilfsregister

Das Register RH dient als zugriffszeitfreie Speicherzelle. Es nimmt Vergleichsgrößen für Vergleiche mit dem Inhalt des Akkumulators auf und ermöglicht das Aufsummieren der Ergebnisse mehrerer Multiplikationsoperationen (akkumulierende Multiplikation).

RY Schifzähler

RZ Hilfsregister

Der Schifzähler RY tritt in Aktion bei den eigentlichen Schifbefehlen, bei Gleitpunktoperationen, beim Normalisierungsbefehl und beim Umschlüsselbefehl. Das Hilfsregister RZ ist für interne Vorgänge erforderlich.

RX Exponentenzähler

RW Hilfsregister

Im Exponentenregister RX wird bei Gleitpunktoperationen die Errechnung des Exponenten zur Basis 16 durchgeführt. Das Hilfsregister RW wird dabei zusätzlich benötigt.

RM Markenregister

Bei der Übernahme eines markierten Zahlwertes aus dem Speicher in ein Register wird das Markenbit abgespalten und in das Markenregister übertragen. Das Markenbit des Zahlwertes wird im Register als Überlauflaufstelle benutzt und deshalb beim Einspeichern nach der Abspaltung gleich dem Vorzeichenbit gesetzt.

RS Sammelregister

RT Rückstellregister für RS

Jeder Transport aus oder in den Kernspeicher erfolgt über das Sammelregister RS. Der Operand eines Rechenwerksbefehls wird bereits während der Entschlüsselung des Befehls im Befehlswerk im Sammelregister RS bereitgestellt. Das Rückstellregister wird zusätzlich benötigt. RS ist sowohl vom Rechenwerk als auch vom Befehlswerk aus zugänglich.

2.2.

Das Befehlswerk

Das Befehlswerk (Leitwerk) arbeitet mit dem ihm zugeordneten Mikroprogrammwerk unabhängig von den übrigen Werken (Rechenwerk, Zentralspeicher, Vorrangwerk, EA-Werk). Innerhalb des Befehlswerks wird mit relativen (unvollständigen) Adressen gearbeitet. Erst bei einer Speicheransteuerung werden diese relativen Adressen über die Seitenadressregister durch absolute (vollständige) Adressen ersetzt, wenn nicht Systemmodus (siehe 2.3) eingeschaltet ist oder ein Sprung im oder in den Spezialmodus erfolgt. Transporte in das Befehlswerk gehen über das Sammelregister RS.

Das Befehlswerk des RD 441 enthält folgende Register:

| Bezeichnung<br>Kurzbez.        | Anzahl<br>Binärst. | Name des Registers |                                                        |

|--------------------------------|--------------------|--------------------|--------------------------------------------------------|

|                                |                    |                    |                                                        |

| BA                             | 24                 |                    | Adressenregister                                       |

| BZ                             | 24                 |                    | Zusatzadressenregister                                 |

| BC                             | 8                  |                    | Coderegister                                           |

| BD                             | 8                  |                    | Zusatzcoderegister                                     |

| BB B                           | 24                 |                    | Bereitadressenregister                                 |

| BH                             | 24                 |                    | Adressenhilfsregister für BB                           |

| BJ                             | 24                 |                    | Rückstellregister für BH                               |

| BF F                           | 24                 |                    | Befehlsfolgeregister<br>(Befehlszähler)                |

| BL L                           | 16                 |                    | Leitadressenregister                                   |

| BLZ1                           | 5                  |                    | Leitadressenzusatzregister 1                           |

| BLZ2                           | 5                  |                    | Leitadressenzusatzregister 2                           |

| BP1                            | 24                 |                    | Seitenassoziativregister 1                             |

| BP2                            | 24                 |                    | Seitenassoziativregister 2                             |

| BP3                            | 24                 |                    | Seitenassoziativregister 3                             |

| BP4                            | 24                 |                    | Seitenassoziativregister 4                             |

| BXB X                          | 22                 |                    | Indexbasisregister                                     |

| BXBZ                           | 11                 |                    | Indexbasiszusatzregister                               |

| BI1                            | 34                 |                    | Indexassoziativregister 1                              |

| BI2                            | 34                 |                    | Indexassoziativregister 2                              |

| BI3                            | 34                 |                    | Indexassoziativregister 3                              |

| BI4                            | 34                 |                    | Indexassoziativregister 4                              |

| BK <sub>1-8</sub><br>(links)   | K <sub>1-8</sub>   | 8                  | Merklicherregister<br>(linke Hälfte von BK)            |

| BK <sub>9-16</sub><br>(rechts) |                    | 8                  | Wahlschalterregister<br>(rechte Hälfte von BK)         |

| BU U                           | 8                  |                    | Unterprogrammregister<br>(Unterprogrammordnungszähler) |

| BV                             | 8                  |                    | Hilfsregister für BU                                   |

| BW W                           | 16                 |                    | Wecker                                                 |

| BG G                           | 24                 |                    | Uhr                                                    |

Fortsetzung auf nächster Seite

| Bezeichnung |          | Anzahl   | Name des Registers          |

|-------------|----------|----------|-----------------------------|

|             | Kurzbez. | Binärst. |                             |

| BTZ1        |          | 6        | Schleifenzähler             |

| BTZ2        |          | 6        | Taktzähler                  |

| BT          | T        | 24       | Testregister (Prüfregister) |

| BTV         |          | 12       | Vergleichsregister          |

= dem Programmierer durch Maschinenbefehle zugänglich

Die Funktionen der Befehlswerksregister sind:

BA Adressenregister

BC Coderegister

BZ Zusatzadressenregister

BD Zusatzcoderegister

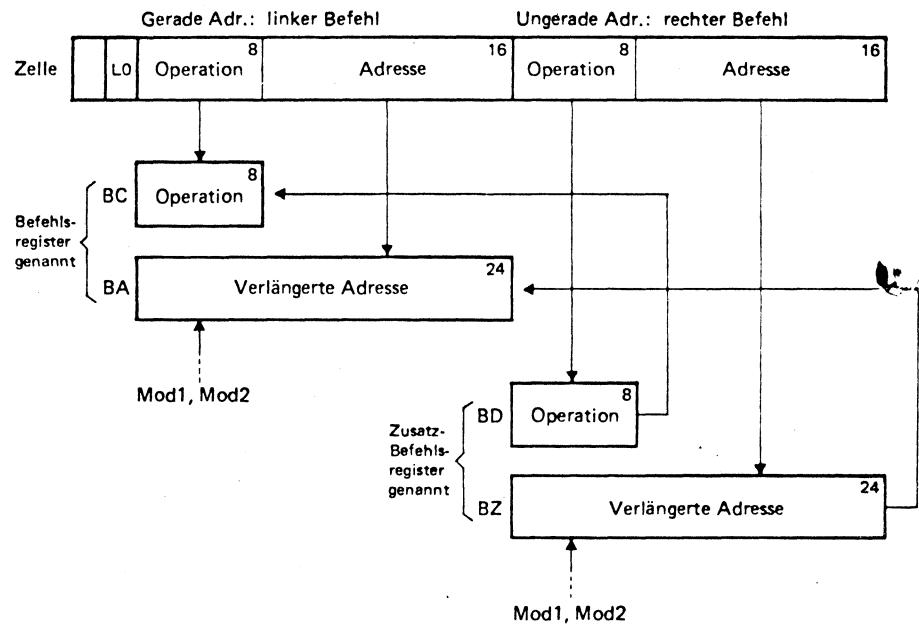

Beim Auslesen von Befehlen aus dem Kernspeicher wird, wie in allen anderen Fällen auch, auf ein Ganzwort (gerade Adresse) zugegriffen. Ein Ganzwort mit Typenkennung 2 besteht aus 2 Befehlen, von denen derjenige aus dem Halbwort mit gerader Adresse (linkes Halbwort) in BC und BA, der andere in BD und BZ übernommen wird. Die Adressen werden dabei durch die Modifiziergrößen Mod1 und Mod2 auf 24-Bit-Adressen verlängert. Für die Vorbesetzung der Modifiziergrößen existieren entsprechende Befehle im Repertoire des RD 441. Zur Ausführung des Befehls aus dem rechten Halbwort (ungerade Adresse) werden die Inhalte von BC und BA durch die von BD und BZ überschrieben (vergl. Bild 3).

Bild 3 Rechter Befehl in das Befehlsregister

BB Bereitadressen-

register

BH Adressenhilfs-

register

Das Bereitadressenregister hat 24 Binärstellen, davon eine Vorzeichenstelle. Es nimmt z. B. die Indexgröße auf, mit der im Adressenregister BA Adreßrechnungen ausgeführt werden. Für die Adressenrechnung können alle 24 Stellen einschließlich der Vorzeichenstelle in Anspruch genommen werden. Der Einer-rücklauf erfolgt von der ersten zur 24sten Stelle. Zur Speicheransteuerung werden lediglich die letzten 22 Binärstellen genommen. Das Adressenhilfsregister BH dient dem internen Ablauf.

BF Befehlsfolge-

register

Das Befehlsfolgeregister hat 24 Binärstellen und enthält nach Ablauf der Abrupphase eines Befehls die Adresse des nächsten abzuhandelnden Befehlswortes. Beim Durchlaufen der ersten Abrupphase eines Befehls wird das Befehlsfolgeregister um 1 erhöht, auch bei Sprungbefehlen. Nach Ausführung des Befehls mit der ungeraden Adresse wird das nächste Befehlsganzwort in die Register BC, BA, BD und BZ übernommen.

Um innerhalb einer Großseite ohne Modifizierung des Befehls springen zu können, werden nur die rechten 16 Bits des Befehlsfolgeregisters verändert, die vorderen Binärstellen des Befehlsfolgeregisters adressieren die Großseite und bleiben erhalten. Nur durch die Befehle SE, SUE und VMO bei entsprechender Spezifikation sowie bei MABI und MU, wenn der Zweitcode ein Sprungbefehl ist, werden auch die linken 8 Binärstellen aus dem Adressenregister in das Befehlsfolgeregister übernommen, was Sprünge in andere Großseiten ermöglicht.

Da ein zusammenhängendes Programm ohne zugehörige Daten nur selten den Adressenraum eine Großseite (32 K) überschreiten wird, werden in der Regel auch nur die rechten 16 Binärstellen des Befehlsfolgeregisters verändert.

Nach der Ausführungsphase eines Sprungbefehls enthält das Befehlsfolgeregister die Zieladresse, bei der fortfahren werden soll. Bei Sprung in ein Unterprogramm mit dem Befehl SU wird die Adresse des dem Sprungbefehl folgenden Befehls, die Rückkehradresse, in einer Indexzelle festgehalten, beim Befehl SFB im Bereitadressenregister. Ein Sprung auf ein Wort mit  $TK \neq 2$  wird nicht ausgeführt, das Befehlsfolgeregister wird nicht verändert und es wird Befehlsalarm ausgelöst.

BL Leitadressen-

register

BLZ1 Leitadressen-

zusatzregister 1

BLZ2 Leitadressen-

zusatzregister 2

Das für 16 Binärstellen ausgelegte Leitadressenregister dient mit den beiden ihm zugeordneten Leitadressenzusatzregistern von je 5 Binärstellen Länge der Adressierung der Zellen des Leitblocks und der Speicheransteuerung im Normal-, Abwickler- und Spezialmodus (siehe 2.3). Die Funktion dieser Register ist in Abschnitt 3.3 ausführlich erklärt.

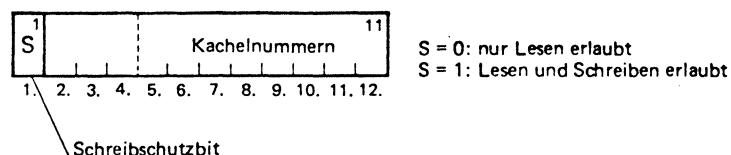

BP1, BP2, BP3, BP4

Seitenassoziativregister

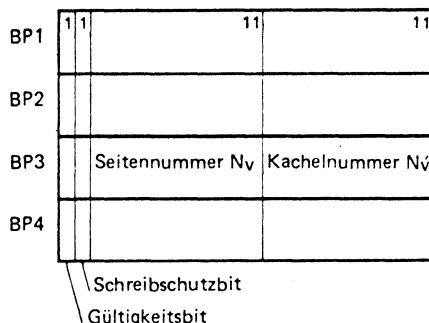

Die vier Seitenassoziativregister sind je 24 Binärstellen lang. Sie enthalten in den Stellen 3 bis 13 die linken 11 Bit relativer Seitenadressen (Seitennummern  $N_V$ ) eines nicht im Systemmodus arbeitenden Programms, in den Stellen 14 bis 24 die linken 11 Bits der Adresse der Kachel (Kachelnummer  $N'_V$ ), die der Seite mit der links

stehenden Adresse zugewiesen ist. Die erste Stelle im Register zeigt an, ob der Inhalt der Zelle gültig ist (Gültigkeitsbit), die zweite zeigt an, ob die Information in der Kachel schreibgeschützt ist (Schreibschutzbit).

Bild 4 Die Seitenassoziativregister

Beim Übertragen der Kachelnummer aus einem Viertelwort der Kacheltabelle im Leitblock wird das Schreibschutzbit mit übernommen. Bei Neueinstellung der Bereichsgrenzen  $\Delta_1$  und  $\Delta_2$  und der Leitadresse werden die Gültigkeitsbits gelöscht.

Der Komplex aus vier Assoziativregistern für Seitenadressen (ebenso auch für Indexadressen), auch "Zuordner" genannt, ist mit einem Alterungsmechanismus ausgestattet, der aus sechs untereinander verbundenen Flipflops gebildet ist. Er kennzeichnet die Register jeweils nach der zeitlichen Reihenfolge der Nutzung ihrer Inhalte. Das zuletzt benutzte Register (eigentlich dessen Inhalt) gilt dabei als das jüngste, das am längsten nicht angesprochene als das älteste. Assoziativregister werden nicht über eine Adresse aufgerufen, sondern mit einem Teil ihres Inhalts, dem Kenninhalt. Bei Übereinstimmung in einem der Register wird der entsprechende Nutzinhalt, in diesem Fall die Kachelnummer  $N'_v$ , zur Verfügung gestellt (siehe Abschnitt 3.2.2).

BI1, BI2, BI3, BI4

Indexassoziativregister

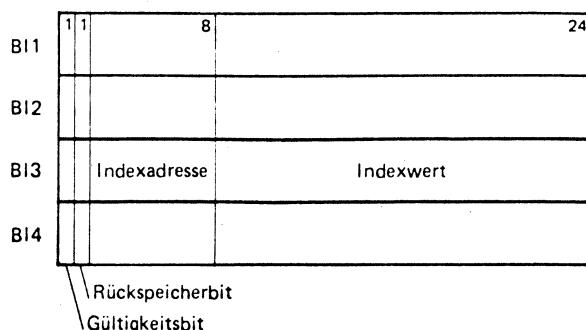

Die vier Assoziativregister mit je 34 Binärstellen bilden einen primären Indexspeicher, der gleichfalls ein Zuordner wie der vorstehend beschriebene ist. In den Binärstellen 3 bis 10 steht jeweils eine von 256 Indexadressen und in den folgenden 24 Stellen der Inhalt dieser Indexzellen, die Indexgröße. Die erste Stelle in den Registern zeigt an, ob der Inhalt des Indexregisters gültig ist (Gültigkeitsbit). Die zweite Stelle enthält das Rückspeicherungsbit. Es wird gesetzt, wenn die Indexgröße verändert wird und zeigt damit an, daß beim Aufgeben dieses Indexregisters oder vor Überschreiben die Indexgröße in die zugehörige Speicherzelle zurückzuspeichern ist.

Bild 5 Index assoziativ register

Das Arbeiten mit den Indexassoziativregistern und das Zusammen-

spiel mit dem Indexbasisregister ist in 3.4. beschrieben.

**BXB Indexbasisregister

BXBZ Indexbasiszusatz-

register**

Durch die Befehle BCI n (n = Ganzwortadresse) und ZI m (m = Halbwortadresse) wird an beliebiger Stelle im Hauptspeicher ein Indexzellenbereich von 256 Halbworten deklariert. Die absolute Anfangsadresse dieses Indexzellenbereichs, die Indexbasis-

adresse, wird im Indexbasisregister (BXB), das 22 Binärstellen hat, festgehalten. Die 256 Indexzellen (Halbwortzellen) werden re-

lativ zur Indexbasisadresse gezählt.

Bei Überschreiten einer Kachelgrenze durch den Indexzellenbereich wird die Adresse der Kachel, die die Fortsetzung des Indexzellen-

bereichs enthält, im Indexbasiszusatzregister festgehalten.

**BK Merklicher- und

Wahlschalterregister**

Das 8 Binärstellen umfassende Merklicherregister dient der Aufnahme von Steuerzeichen (Merklichern), die während eines Programmlaufs erzeugt und für spätere Abfragen aufbewahrt werden. Das Wahlschalterregister umfaßt ebenfalls 8 Binär-

stellen und kann am Bedienpult manuell eingestellt werden.

**BU Unterprogramm-

register

BV Hilfsregister**

Das Unterprogrammregister BU nimmt bei einem Sprung mit dem Befehl SU in ein Unterprogramm die Nummer (Adresse relativ zur Indexbasisadresse) derjenigen Indexzelle auf, in die die Rücksprung-

adresse abgelegt wird.

Für rechnerinterne Vorgänge ist BU ein Hilfsregister BV zugeordnet.

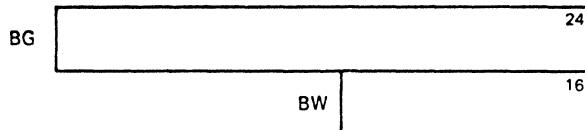

BG Uhrregister

Das Uhrregister ist ein 24-stelliges Zählregister für die Zählung relativer Zeitabschnitte. Es zählt aufwärts in Zähleinheiten von  $10\ \mu\text{s}$  und überzählt folglich alle  $2^{24} \cdot 10^{-5}\text{s}$ , also alle 2,7962 min.

Bild 6 Uhrregister und Weckerregister

BW Weckerregister

Das 16 Binärstellen umfassende Weckerregister gestattet die Voreinstellung eines bestimmten Zeitpunkts, zu dem ein Weckeralarm gemeldet werden soll. Der Alarm tritt ein, wenn die rechten 16 Stellen des Uhrregisters mit dem Inhalt des Weckerregisters übereinstimmen. Der Weckeralarm tritt mindestens alle 0,65536 s auf.

BTZ1 Schleifenzähler

BTZ2 Taktzähler

Diese beiden je 6 Binärstellen umfassenden Register sind dem Befehlsfolgeregister zugeordnet und übernehmen Aufgaben bei Prüf- und Wartungsläufen.

BT Prüfregister

BTV Vergleichsregister

Das Prüfregister und das Vergleichsregister dienen zur Durchführung von Prüf- und Wartungsläufen im Wartungsmodus. Befehlsfolgeregister BF, Schleifenzähler BTZ1 und Taktzähler BTZ2 können mit dem Inhalt dieser beiden Register verglichen werden.

## 2.3. Die Adressierungs- modi

Der RD 441 arbeitet in verschiedenen Adressierungsmodi und ermöglicht so eine Programmierung auf entsprechend vielen Stufen. Die Umschaltung von einem Modus in einen anderen erfolgt durch Eingriffe und Alarme, sowie durch bestimmte Befehle.

Es gibt die folgenden Adressierungsmodi:

- Systemmodus

- Spezialmodus

- Normalmodus

- Abwicklermodus

- Wartungsmodus

### Systemmodus

Im Systemmodus, auch als absoluter Adressierungsmodus bezeichnet, werden die Kernspeicherzellen durch absolute 22-Bit-Adressen angesteuert. Damit sind 4096 Halbzellen, also ein Speicher von 2048 K Zellen adressierbar. Alle den Speicher ansprechenden Befehle besitzen absolute Adresse, das Befehlsfolgeregister schaltet in absoluten Adressen fort. Bei Unterbrechung im Systemmodus werden einige Befehlswerksregister und die Steuerflipflops in der Speicherkachel 0 abgelegt.

### Spezialmodus

Im Spezialmodus, einem speziellen Adressierungsmodus, adressieren alle den Speicher ansprechenden Befehle relativ zu einer Anfangsadresse, die über BL ermittelt wird. Die Seitennummer wird über einen Leitblock, in dem die zugeordnete Kachelnummer (zum Begriff Kachel siehe 3.1.2) enthalten ist, ersetzt. Das Befehlsregister schaltet jedoch in absoluten Adressen fort. Bei Unterbrechung im Spezialmodus werden einige Befehlswerks-Register und die Steuerflipflops hardwareseitig in den zugehörigen Leitblock abgespeichert. Der Spezialmodus wird durch bestimmte Zustände zweier Flipflops dargestellt.

### Normalmodus

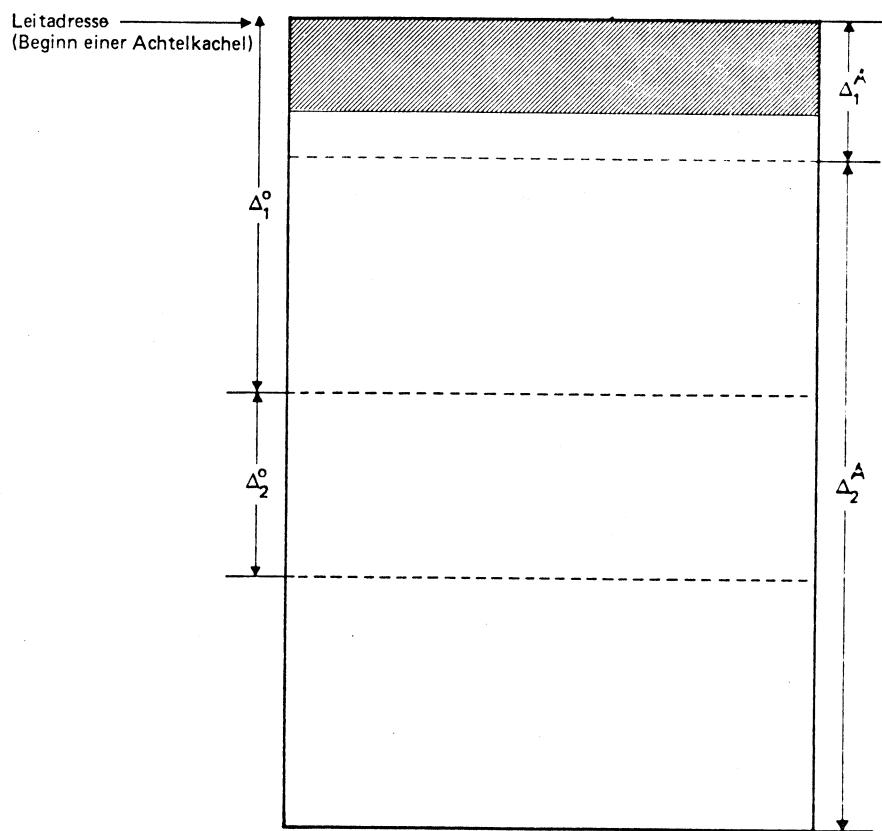

Der Normalmodus ist ein relativer Adressierungsmodus. Alle den Speicher ansprechenden Befehle und die Sprungbefehle adressieren relativ zu einer Adresse 0, die über BL ermittelt wird (siehe 3.3). Das Befehlsfolgeregister schaltet in relativen Adressen fort. Die Seitennummer wird durch eine Kachelnummer ersetzt. Im Normalmodus wird nur ein bestimmter Adressenbereich aus dem 22-Bit-Adressenraum überstrichen. Die Kachelnummern, die zu diesem Bereich gehören, sind in einer Kacheltabelle, deren Beginn relativ zum Leitblock-Anfang durch eine Größe  $\Delta_1$ , und deren Länge durch eine Größe  $\Delta_2$  gegeben ist, enthalten. Die Werte  $\Delta_1$  und  $\Delta_2$  sind im entsprechenden Leitblock in der Halbzelle mit der relativen Adresse 64 enthalten. Bei Unterbrechungen werden einige Befehlswerks-Register im Leitblock hardwareseitig abgelegt.

Abwicklermodus

Der Abwicklermodus ist ein im zulässigen Adressenbereich erweiterter relativer Adressierungsmodus. Er unterscheidet sich vom Normalmodus durch andere Grenzangaben  $\Delta_1 A$  und  $\Delta_2 A$ , die im Leitblock in der Halbzelle mit der relativen Adresse 65 stehen.

Wartungsmodus

Für Prüf- und Wartungsläufe existiert ein eigener Modus. Im Wartungsmodus sind einige der nicht mit TAS-Befehlen belegten Befehlscodes zulässig. Einige der in den anderen Modi nicht adressierbaren Register können im Wartungsmodus angesprochen werden. Der Wartungsmodus wird durch ein mit dem Befehl VPU einstellbares Steuerbit eingeschaltet (siehe "TR 440-Befehlslexikon").

## ZENTRALSPPEICHER

3.1.

Speicherorganisation

Der Zentralspeicher ist größtenteils Hauptspeicher (wortweise adressierbar). Lediglich 256 K Zellen des Massenkernspeichers (von max. 2056 K), deren Adressenraum sich mit dem des schnellen Kernspeichers überlappt, kann Ergänzungsspeicher sein (nicht wortweise adressierbar).

Der Hauptspeicher ist in vier Grundausbaustufen lieferbar:

|                |                                  |

|----------------|----------------------------------|

| Ausbaustufe 1: | 48 K Zellen für je ein Ganzwort  |

| Ausbaustufe 2: | 64 K Zellen für je ein Ganzwort  |

| Ausbaustufe 3: | 128 K Zellen für je ein Ganzwort |

| Ausbaustufe 4: | 256 K Zellen für je ein Ganzwort |

Die Grundausbaustufen lassen sich mit 16 K-Modulen zu beliebigen Zwischenstufen ausbauen, für die allerdings die folgenden Ausführungen über Adressenverschränkung (und effektive Zykluszeiten) nicht oder nur teilweise gültig sind.

Mittels eines Massenkernspeichers ist ein weiterer Ausbau des Hauptspeichers bis zu maximal 2048 K direkt adressierbaren Speicherzellen möglich.

3.1.1.

Speichermodulen und

Adressenverschränkung

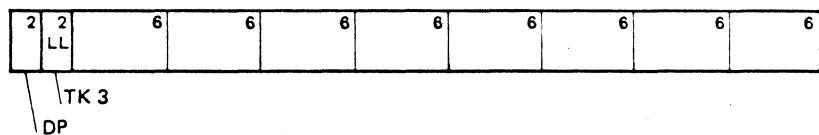

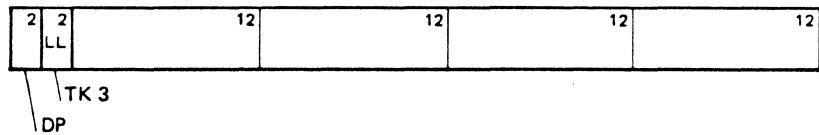

Der Zentralspeicher ist modular aufgebaut; jeder Speichermodul nimmt 16 K Ganzworte auf; d. h. je nach Speicherausbau sind 3, 4, 8 oder 16 bzw. bei Anschluß des Massenkernspeichers entsprechend mehr Speichermodulen vorhanden. Ein besonderes Charakteristikum des Speichers liegt in der Adressenverschränkung, d. h. 4, 8 oder 16 bzw. mehr (je nach Ausbaustufe) adressenmäßig aufeinanderfolgende Speicherzellen liegen in verschiedenen Modulen. 1024 konsekutiv adressierbare Speicherzellen bilden eine Speicherkachel (kurz: Kachel). Die Ganzworte 0...1023 gehören demzufolge zu Speicherkachel 0, die Ganzworte 1024...2047 zu Speicherkachel 1 usw. Jede Speicherkachel hat infolge der Adressenverschränkung teil an allen Modulen. Die Zuordnung zwischen Speicherzellenadressen und Speichermodulen erfolgt über eine je nach Ausbaustufe verschiedenen großen Zahl der in der Wertigkeit niedrigsten Adreßbits.

Jeder Speichermodul besitzt eine eigene Funktionssteuerung. Ist sie durch einen Zugriff auf eine Zelle innerhalb dieses Moduls belegt, so ist bis zum Ablauf der Zykluszeit von 0,9  $\mu$ s kein weiterer Zugriff auf diesen Modul möglich, wohl aber auf eine Zelle aus einem anderen freien Speichermodul. Rechnerkerne (maximal zwei) und EA-Kanalwerke können damit so lange parallel arbeiten, wie sie auf verschiedene Modulen zugreifen. Die effektive Zykluszeit ist deshalb abhängig vom Ausbau des Hauptspeichers und kann nur statistisch angegeben werden. Sie kann ab 8 Speichermodulen zeitweise 0,125  $\mu$ s betragen. Liegt jedoch im Mittel geringfügig höher.

Unter **Zykluszeit** eines Speichers (Moduls) wird die maximale Zeit, nach der im günstigsten Fall eine Speicherzelle wieder aufgerufen werden kann, verstanden. Demgegenüber ist die **Zugriffszeit** die jeweilige Zeit, die zwischen Aufruf des Speichers und Verfügbarkeit der Information im Register vergeht (0,3  $\mu$ s).

#### Leitblock

Für das folgende werden Programme, die im Normal- oder Abwicklermodus arbeiten, willkürlich "Prozesse" genannt. Jeder Prozeß besitzt einen Leitblock, der nicht seinem Adressenraum angehört und der stets auf einer Achtelkacheladresse beginnt. Die Kacheladresse der ersten Zelle des Leitblocks ist die Leitadresse.

Der Leitblock wird durch Bereichsangaben  $\Delta_1$  und  $\Delta_2$  unterteilt. Die Bereichsangaben bestimmen den erreichbaren Adressenraum im Normal- bzw. Abwicklermodus. Die Bereichsangaben können vom Betriebssystem verändert werden. Für Normal- und Abwicklermodus gelten in der Regel verschiedene Bereichsangaben.

Programme, die im System- oder Spezialmodus arbeiten, werden im folgenden willkürlich "Betriebssystem" genannt, wobei sich dieser Begriff nicht mit dem Begriff des Betriebssystems innerhalb der TR 440-Software deckt. Im Systemmodus ist der gesamte Adressenraum ohne jede Einschränkung adressierbar.

Der Programmierer arbeitet normalerweise mit relativen Adressen und Seitennummern. Es ist notwendig, zwischen diesen programmrelativen Begriffen einerseits und den (absoluten) Speicheradressen und Kacheln andererseits zu unterscheiden. Die Bits 3 bis 13 der Seitenadresse werden als Seitennummer, die Bits 3 bis 13 der Kacheladresse als Kachelnummer bezeichnet (siehe 3.1.2).

Aus dem Kernspeicher werden stets Ganzworte ausgelesen, die zunächst in das Sammelregister RS übertragen werden. Aus RS können je nach der Wirkung des Befehls jedoch auch Teile eines Ganzworts geholt werden, so daß auch von Halbwort, Viertelwort und Byte- oder Silben-Adressierung gesprochen werden kann.

#### 3.1.2. Seiten und Kacheln

Je 2048 adressenmäßig aufeinanderfolgende Halbworte, entsprechend 1024 konsekutiv adressierten Ganzworten, bilden eine Seite. Die Halbworte mit den Adressen 0 bis 2047 bilden die erste Seite (0), die mit den Halbwortadressen 2048 bis 4095 die zweite Seite (1) usw. Je 32 hintereinanderliegende Seiten bilden eine Großseite, d. h. in Großseite 0 liegen die Seiten 0 bis 31 mit den Halbwortadressen 0 bis 65 535, in Großseite 1 die Seiten 32 bis 63 usw.

Einer Seite eines Prozesses wird genau eine Kachel im Speicher zugewiesen. Im allgemeinen werden jedoch aufeinanderfolgenden Seiten nicht auch aufeinanderfolgende Kacheln zugewiesen. Das ist unabhängig von der Belegungssituation im Rechner.

Die Kachel 0 ist teilweise reserviert für hardwaremäßige Absicherungen bei Unterbrechungen durch Eingriffe, Alarme, SSR- und Makrosprünge für die zwei möglichen Rechnerkerne. Die Kachel 1 ist reserviert für Information, die der Steuerung des EA-Verkehrs dient, so daß eine freie Kachel Zuweisung erst ab Kachel 2 möglich ist.

Durch einen Zuordnungsvorgang, der unter Zuhilfenahme der sogenannten Kacheltabelle im Leitblock durchgeführt wird, werden den programmrelativen Seitennummern absolute Kachelnummern zugeteilt (paging).

Rechnerkern 0

| Specherkachel 0 |                                                            | Speicherhalbzelle                | Bemerkungen                                             |

|-----------------|------------------------------------------------------------|----------------------------------|---------------------------------------------------------|

| Adresse         | 0                                                          | Eingriffswort                    |                                                         |

| 2               |                                                            | Sprungziel b. Alarm ohne Al.sp.1 | Sprungz.b.Al., wenn Al.sp.1 ges.ist                     |

| 4               |                                                            | Indexbasisadresse                | Sprungziel bei Eingriff                                 |

| 6               |                                                            | Sprungziel bei SSR               | Sprungziel bei Makro                                    |

| 8               |                                                            | —                                | —                                                       |

| 10              |                                                            | BB                               | BA                                                      |

| 12              |                                                            | BF                               | Steuerbits                                              |

| 14              |                                                            | —                                | —                                                       |

| 16              |                                                            | —                                | —                                                       |

| 18              |                                                            | BB                               | BA                                                      |

| 20              |                                                            | BF                               | Steuerbits                                              |

| 22              |                                                            | —                                | —                                                       |

| 24              |                                                            | RS                               |                                                         |

| 26              |                                                            | BB                               | BA                                                      |

| 28              |                                                            | BF                               | Steuerbits                                              |

| 30              | Code                                                       | Steuerbits                       | BH                                                      |

| 32              |                                                            | RS                               |                                                         |

| 34              |                                                            | BB                               | BA                                                      |

| 36              |                                                            | BF                               | Steuerbits                                              |

| 38              | Code                                                       | Steuerbits                       | BH                                                      |

| 40              |                                                            | RS                               |                                                         |

| 42              |                                                            | BB                               | BA                                                      |

| 44              |                                                            | BF                               | Steuerbits                                              |

| 46              | Code                                                       | Steuerbits                       | BH                                                      |

| 48              |                                                            |                                  |                                                         |

| 50              |                                                            |                                  |                                                         |

| 52              |                                                            |                                  |                                                         |

| 54              |                                                            |                                  |                                                         |

| 56              |                                                            |                                  |                                                         |

| 58              |                                                            |                                  |                                                         |

| 60              |                                                            |                                  |                                                         |

| 62              | 3 7 8 12                                                   | 27 31,32 36                      |                                                         |

| 64              | BLZ2 BLZ1                                                  | —                                | BLZ2 BLZ1 —                                             |

|                 | wenn Abwickler-Flip-Flop<br>nicht gesetzt<br>(Normalmodus) |                                  | wenn Abwickler-Flip-Flop<br>gesetzt<br>(Abwicklermodus) |

| 512             | für Rechnerkern 1, wie für Rechnerkern 0                   |                                  |                                                         |

| 1023            |                                                            |                                  |                                                         |

Die unbenannten Plätze werden hardwareseitig nicht belegt.

Die Halbzellen 2 bis 7, 64 und 65 sowie bei einem zweiten Rechnerkern die entsprechenden Halbzellen in der zweiten Viertelkachel müssen vorbesetzt werden.

Bild 7 Einteilung der Specherkachel 0

### 3.1.3. Hardwareseitige Belegung der Speicherkachel 0

Bei einer Unterbrechung durch Eingriffe, Alarme, SSR-Sprünge oder Sprünge in ein Makro wird der Inhalt eines Teils der Befehlswerksregister und eine Reihe von Bits, die den Zustand bestimmter Steuerflipflops kennzeichnen, hardwaremäßig abgespeichert. Abhängig vom eingestellten Adressierungsmodus erfolgt die Abspeicherung in die Speicherkachel 0 oder in einen Prozeßleitblock (siehe 3.2.1). Im grundsätzlichen Aufbau stimmt die Belegung der ersten 24 Ganzwortzellen der Speicherkachel 0 mit der ersten 24 Ganzwortzellen eines Prozeßleitblocks überein.

Bei einem Eingriff wird zusätzlich das Eingriffswort (siehe 5.1.2) in die Speicherkachel 0 abgelegt. Die Sprungadressen für die Weiterbehandlung der verschiedenen Fälle und die einzustellende Indexbasisadresse sind im Leitblock in Kachel 0 vor-gegeben. Bei einer Unterbrechung durch Eingriffe, Alarme, SSR-Sprünge oder Makros wird hardwaremäßig über die entsprechenden Halbwortzellen 2, 3, 5, 6 oder 7 verzweigt

Die unbenannten Plätze in Kachel 0 werden hardwareseitig nicht belegt. Die Halbzellen 2 bis 7, 64 und 65 sowie bei einem zweiten Rechnerkern die entsprechenden Halbzellen in der zweiten Viertelkachel müssen vorbesetzt werden.

Die Bedeutung der Steuerbits ist folgende:

Bei Unterbrechung durch Eingriff, Alarm, SSR- oder Makrosprung werden neben einigen Befehlswerksregistern auch die Zustände einer Reihe von Flipflops in Steuerbits abgespeichert. Diese Steuerbits werden im rechten Halbwort des dritten Ganzworts in der jeweiligen Viererwortgruppe abgelegt.

Die angeführte Bedeutung der Steuerbits ist deren Hauptbedeutung. Infolge mehrfacher Ausnutzung der Steuerbits durch die Mikroprogramme ergibt sich in manchen Fällen eine abweichende Bedeutung.

| Bit | Bedeutung                          |

|-----|------------------------------------|

| 48  | Systemmodus (48 + 47 Spezialmodus) |

| 47  | Normalmodus                        |

| 46  | Abwicklermodus                     |

| 45  | Dreierproben-Alarm                 |

| 44  | Wecker-Alarm                       |

| 43  | Eingriffssperre                    |

| 42  | Stop-Alarm                         |

| 41  | Befehls-Alarm                      |

| 40  | BV-Register-Alarm                  |

| 39  | Speicherschutz-Alarm               |

| 38  | Arithmetischer Alarm               |

| 37  | Typenkennungs-Alarm                |

| Bit | Bedeutung                         |

|-----|-----------------------------------|

| 36  | Stop nach Abrupphase (siehe 5.3 ) |

| 35  | Wartungsmodus                     |

| 34  | Modus 16 (TR 4-Modus)             |

| 33  | Stop vor Abrupphase (siehe 5.3 )  |

Die Bits 32 bis 25 enthalten im wesentlichen Aussagen über die Art der unmittelbar vorangegangenen Befehle, z. B. Modifizierbefehle

Bei Unterbrechung durch Eingriff oder Alarm stehen im linken Halbwort des 4ten Ganzworts der jeweiligen Viererwortgruppe folgende Steuerbits:

| Bit | Bedeutung                                   |

|-----|---------------------------------------------|

| 24  | Technischer Fehler                          |

| 23  | Rechneralarm von Rechnerkern 0              |

| 22  | Rechneralarm von Rechnerkern 1              |

| 19  | Hauptalarm (Stromausfall bzw. -abschaltung) |

Die Bits 18 bis 9 sind Zustandsbits, deren detaillierte Erläuterung im Rahmen dieser Schrift zu weit führte. Die Bits 1 bis 8 enthalten den Befehlscode des unterbrochenen Befehls.

### 3.2. Die Speicherzuteilung

Beim Laden eines Prozesses oder von Teilen des Prozesses muß im Kernspeicher des RD 441 ein entsprechender Speicherraum zugewiesen werden. Dabei werden die einzelnen Seiten des Prozesses, die Befehle, Konstanten usw. enthalten, in Kacheln (Gefäßen für Seiten) des Kernspeichers abgelegt. Die zugewiesenen Kacheln, die durch ihre Kachelnummer bestimmt sind, können beliebig über den Kernspeicher verstreut liegen. So kann z. B. der Seite 5 eines Prozesses die Kachel 99, der Seite 8 die Kachel 112 zugewiesen werden sein.

Diese Seiten-Kachel-Zuordnung wird in einer Tabelle festgehalten, welche für jeden Prozeß vom Betriebssystem angelegt wird. Die Seiten-Kachel-Tabelle ist Bestandteil des sogenannten Prozeßleitblocks, der maximal einen Speicherraum von 1024 Ganzwortzellen einnimmt. Der Prozeßleitblock umfaßt neben der Seiten-Kachel-Tabelle eine Anzahl Angaben in dafür reservierten Hilfszellen. Der Prozeßleitblock beginnt immer auf einer Achtelkachel. Die Adresse des ersten Halbworts der betreffenden Achtelkachel wird Leitadresse genannt. Die 8 Bits niedrigster Wertigkeit der Adresse dieses Halbworts sind immer gleich 0, so daß zur eindeutigen Beschreibung der Leitadresse die 16 höchstwertigen Bits ausreichen. Ist einem Prozeß vom Betriebssystem die Regie übertragen worden, so ist für diese Zeit die betreffende Leitadresse im 16 Bits fassenden Leitadressenregister BL enthalten.

### 3.2.1. Aufteilung und Belegung von Prozeßleitblöcken

Der Prozeßleitblock hat in den Halbwortzellen 0 bis 65 (relativ zur Leitadresse) eine Reihe von Aufgaben in Hilfszellen, die z. T. für hardwareseitige Vorgänge benötigt werden, z. T. unbesetzt sind. Im anschließenden Teil enthält er die Seiten-Kachel-Zuordnungstabelle.

Der Inhalt des Leitblocks kann nur im Systemmodus verändert werden.

Bild 8 Aufteilung des Leitblocks

$\Delta_1^0$  ,  $\Delta_1^A$  :

Beginn der Seiten-Kachel-Tabelle für Normalmodus ( $\Delta_1^0$ ) bzw. Abwicklermodus ( $\Delta_1^A$ )

$\Delta_2^0$  ,  $\Delta_2^A$ :

Länge der Seiten-Kachel-Tabelle für Normalmodus ( $\Delta_2^0$ ) bzw. Abwicklermodus ( $\Delta_2^A$ )

Im Normalmodus kann nur auf den Inhalt der Kacheln zugegriffen werden, deren Nummern im Bereich  $\Delta_2^0$  des Prozeßleitblocks eingetragen sind.

Im Abwicklermodus kann nur auf den Inhalt der Kacheln zugegriffen werden, deren Nummern im Bereich  $\Delta_2^A$  des Prozeßleitblocks eingetragen sind.

Sowohl im Normal- als auch im Abwicklermodus können die ersten 128 Ganzwortzellen mit dem Befehl BLEI gelesen werden.

| Leitadresse |                    | Bemerkungen  |      |

|-------------|--------------------|--------------|------|

| +0          | —                  | —            |      |

| 2           | —                  | —            |      |

| 4           | Indexbasis         | —            |      |

| 6           | Sprungziel bei SSR | —            |      |

| 8           | —                  | —            |      |

| 10          | BB                 | BA           |      |

| 12          | BF                 | Steuerbits   |      |

| 14          | —                  | —            |      |

| 16          | —                  | —            |      |

| 18          | BB                 | BA           |      |

| 20          | BF                 | Steuerbits   |      |

| 22          | —                  | —            |      |

| 24          | RS                 |              |      |

| 26          | BB                 | BA           |      |

| 28          | BF                 | Steuerbits   |      |

| 30          | Code               | Steuerbits   | BH   |

| 32          | RS                 |              |      |

| 34          | BB                 | BA           |      |

| 36          | BF                 | Steuerbits   |      |

| 38          | Code               | Steuerbits   | BH   |

| 40          | RS                 |              |      |

| 42          | BB                 | BA           |      |

| 44          | BF                 | Steuerbits   |      |

| 46          | Code               | Steuerbits   | BH   |

| 48          |                    |              |      |

| 50          |                    |              |      |

| 52          |                    |              |      |

| 54          |                    |              |      |

| 56          |                    |              |      |

| 58          | $\Delta_2^0$       | $\Delta_1^0$ |      |

| 60          | ↓                  | ↓            |      |

| 62          | 3 7 8 12           | 27 31 32 36  |      |

| 64          | BLZ2               | BLZ1         | BLZ2 |

|             |                    |              |      |

|             |                    |              |      |

|             |                    |              |      |

|             |                    |              |      |

Bild 9 Hardwareseitig zugeordnete Zellen im Prozeßleitblock

3. 2. 2.

Adressierung der Seiten-Kachel-Tabelle im Prozeßleitblock

Zweckmäßigerweise stellt man sich die Seiten-Kachel-Tabelle als in Viertelworte (Silben zu 12 Bits) unterteilt vor.

Der schnelle Kernspeicher des RD 441 nimmt bei Maximalausstattung 256 K Worte auf, d. h. es sind die Kacheln mit den Nummern (Adressen) 0 bis 255 möglich. Zur Darstellung dieser Adressen sind 8 Bits erforderlich.

Von den verbleibenden 4 Bits eines jeden Viertelworts dient eines dazu, den Schreibschutz, der für jede Kachel möglich ist, zu realisieren. Unter Einbeziehung der restlichen 3 Bits können Kacheladressen bis zu 4095 dargestellt werden (für Massenkernspeicher). Demnach hat jedes Viertelwort in der Seiten-Kachel-Zuordnungstabelle folgendes Format:

Bild 10 Viertelwort in Seiten-Kachel-Tabelle

Jeder Prozeßleitblock umfaßt bis zu 1024 Ganzworte.

Damit besteht jeder Prozeßleitblock aus 8 Achtelkacheln.

Eine Achtelkachel besteht aus (Definition) 8 Teilleitblöcken, jeder Teilleitblock aus 16 Ganzworten bzw. 32 Halbworten bzw. 64 Viertelworten.

In den Halbworten 64 und 65 stehen die Bereichsangaben  $\Delta_1^0$ ,  $\Delta_2^0$ ,  $\Delta_1^A$ ,  $\Delta_2^A$  für den Normal- und Abwicklermodus. Die Bereichsangaben bestehen aus je 5 Bits, so daß damit jeweils 32 Adressen möglich sind.

Die Seiten-Kachel-Tabelle kann frühestens im Teilblock 0 beginnen (theoretischer Wert, da BLZ1 3 enthalten muß, siehe 3. 2. 1). Sie muß spätestens mit Teilleitblock 31 beginnen (BLZ1 = 31).

Da  $0 \leq BLZ2 \leq 31$  gilt, können insgesamt max. 32 Teilleitblöcke überstrichen werden. Einem Prozeß können also z. B. im Normalmodus maximal  $32 \cdot 64$  Viertelworte für die Seiten-Kachel-Tabelle zur Verfügung gestellt werden, d. h. er kann maximal  $32 \cdot 64 = 2048$  K belegen.

Der kleinste einem Prozeß im Leitblock zuteilbare Speicherraum beträgt 1 Teilblock = 64 Viertelworte mit 64 Kachelnummern. Da jedoch nicht alle Viertelworte der Seiten-Kachel-Tabelle besetzt sein müssen, benötigt der Prozeß im Kernspeicher nur diejenigen Kacheln, deren Nummern in der Tabelle eingetragen sind, sowie den Raum, den das Betriebssystem speziell für diesen Prozeß anlegt.

Dieselbe Kachelnummer kann mehrfach im Leitblock verzeichnet sein.

Der Teilleitblock 63 kann nie durch einen Teil der Seiten-Kachel-Tabelle belegt sein, da diese Tabelle spätestens mit Teilleitblock 31 beginnt und höchstens 32 Teilleitblöcke lang sein kann, d. h. spätestens mit dem Teilleitblock 62 einschließlich endet.

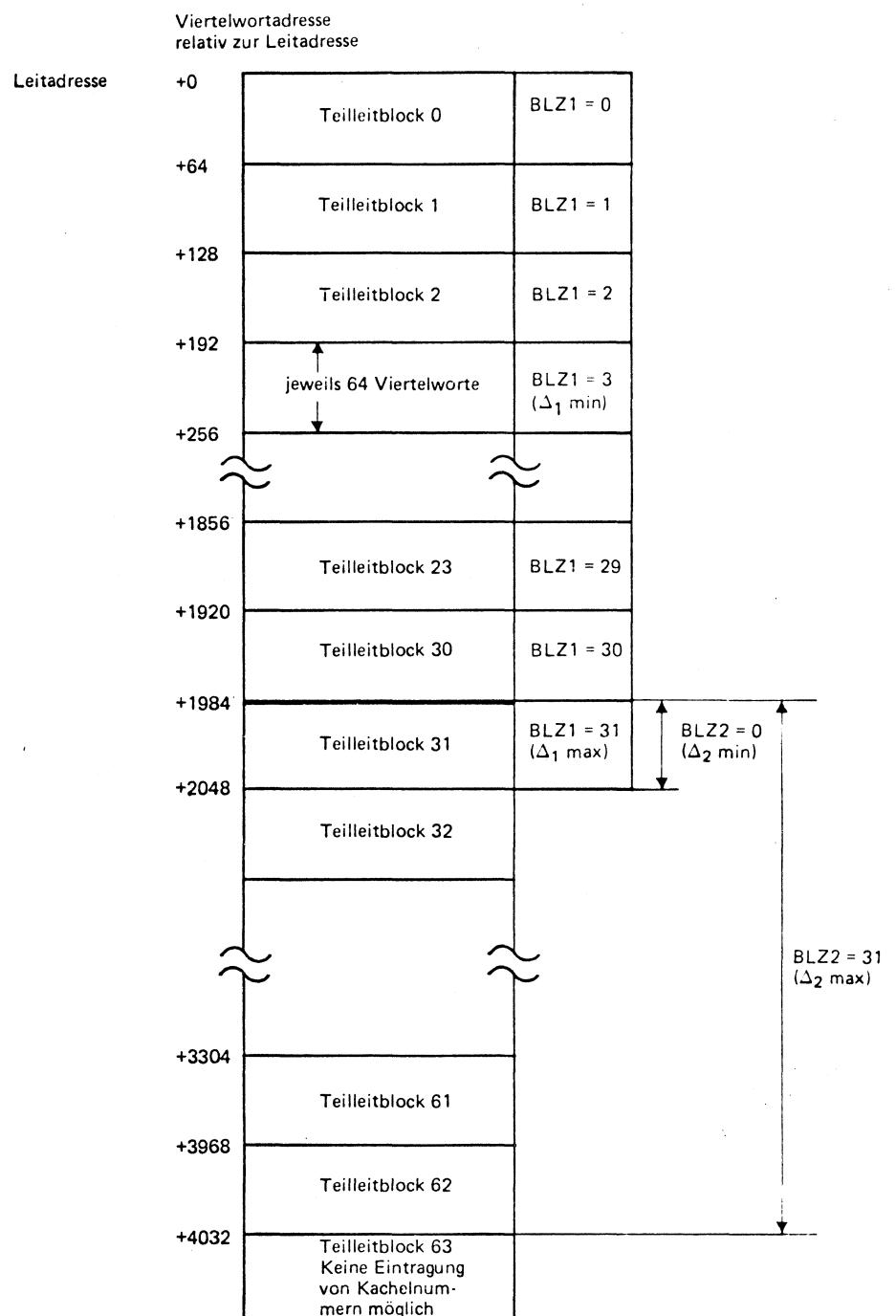

Bild 11 Aufteilung des Prozeßleitblocks in Teilleitblöcke

### 3.3. Die Speicheransteuerung

Mit Hilfe der Seiten-Kachel-Tabelle muß im Normal- bzw. Abwicklermodus bei jeder Speicheransteuerung festgestellt werden, auf welcher Kachel sich diejenige Seite des Prozesses befindet, auf die zugegriffen werden soll.

Die Seiten-Kachel-Tabelle beginnt in einem bestimmten Teilleitblock entsprechend dem vorgegebenen  $\langle BLZ1 \rangle$ . Im ersten Viertelwort dieses Teilleitblocks ist die Nummer derjenigen Kachel eingetragen, in die die Seite 0 des betreffenden Prozesses eingespeichert wurde. Das zweite Viertelwort enthält die Kachelnummer von Seite 1, das erste Viertelwort des folgenden Teilleitblocks enthält die Kachelnummer von Seite 64 usw.

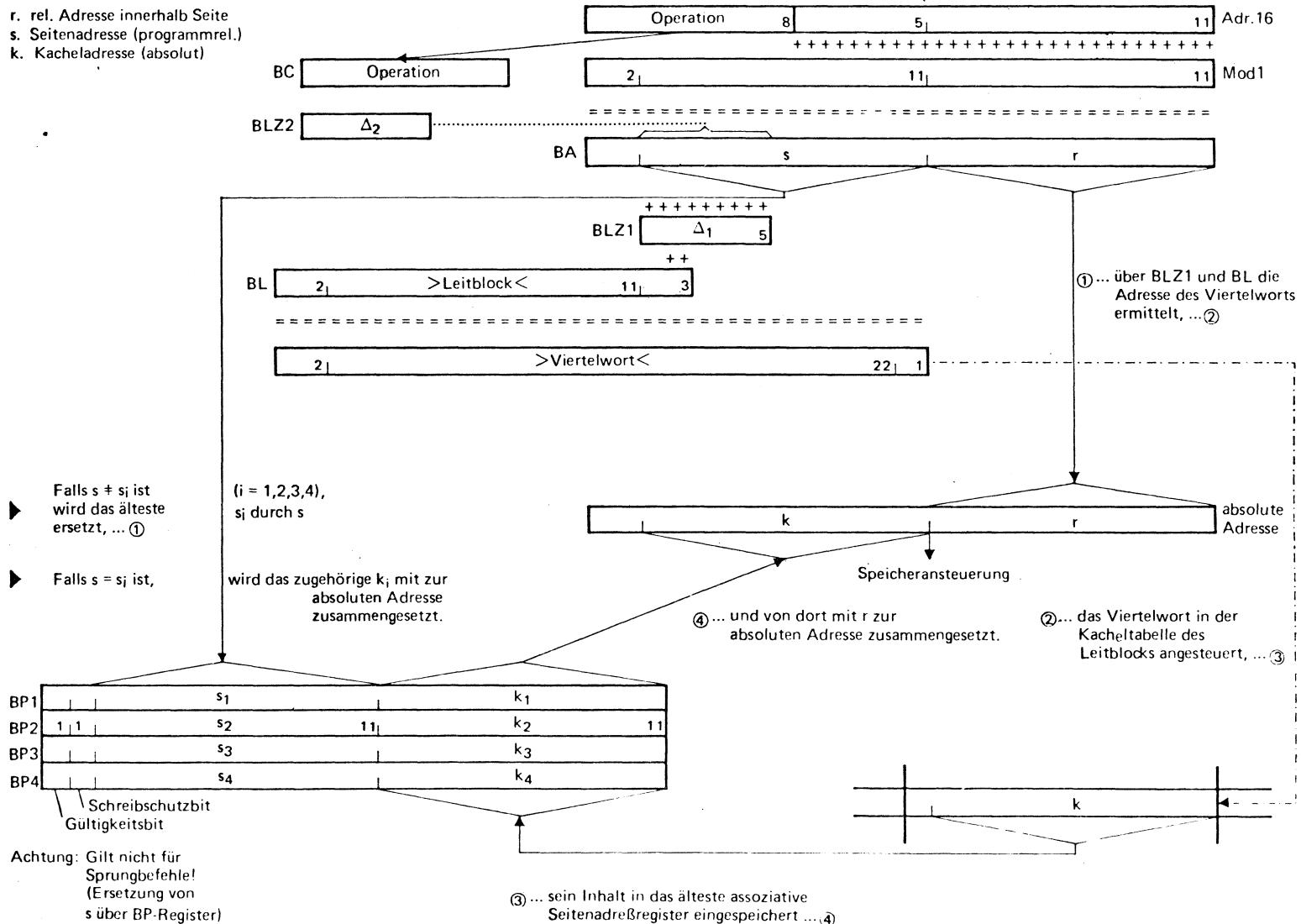

In der Abrupphase entsteht aus der programmrelativen 16-Bit-Adresse nach Modifizierung mit Mod 1 und Mod 2 eine 24-Bit-Adresse. Davon adressieren die letzten 11 Bits relativ zum Anfang der Seite. Sie bleiben unverändert und adressieren nach Ersetzung der Seitennummer durch die Kachelnummer denselben Speicherplatz in der Kachel wie vorher in der Seite.

Die linken 13 Bits, von denen die beiden vordersten für die Speicheransteuerung ohne Bedeutung sind, definieren die programmrelative Seitennummer.

Diese aus 11 Bits bestehende Seitennummer wird nun zur Speicheransteuerung wie folgt benutzt:

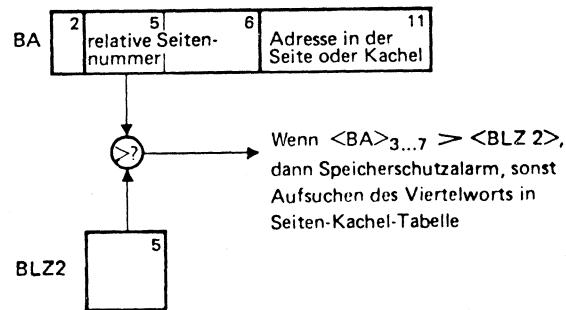

Der Inhalt der Speicherhalbzelle 64 (bzw. 65) des Prozeßleitblocks wird in die Register  $BLZ1$  und  $BLZ2$  des Befehlswerks gebracht. Der Inhalt von  $BLZ2$  wird anschließend mit den höchsten 5 Bits der im Adressenregister BA enthaltenen Seitennummer verglichen.

Bild 12 Seitennummern-Vergleich und Auswertung

Ist  $\langle BA \rangle 3 \dots 7$  größer als  $\langle BLZ2 \rangle$ , so wird Speicherschutzalarm ausgelöst. Ist das nicht der Fall, dann wird das der relativen Seitennummer entsprechende Viertelwort in der Seiten-Kachel-Zuordnungstabelle folgendermaßen angesteuert:

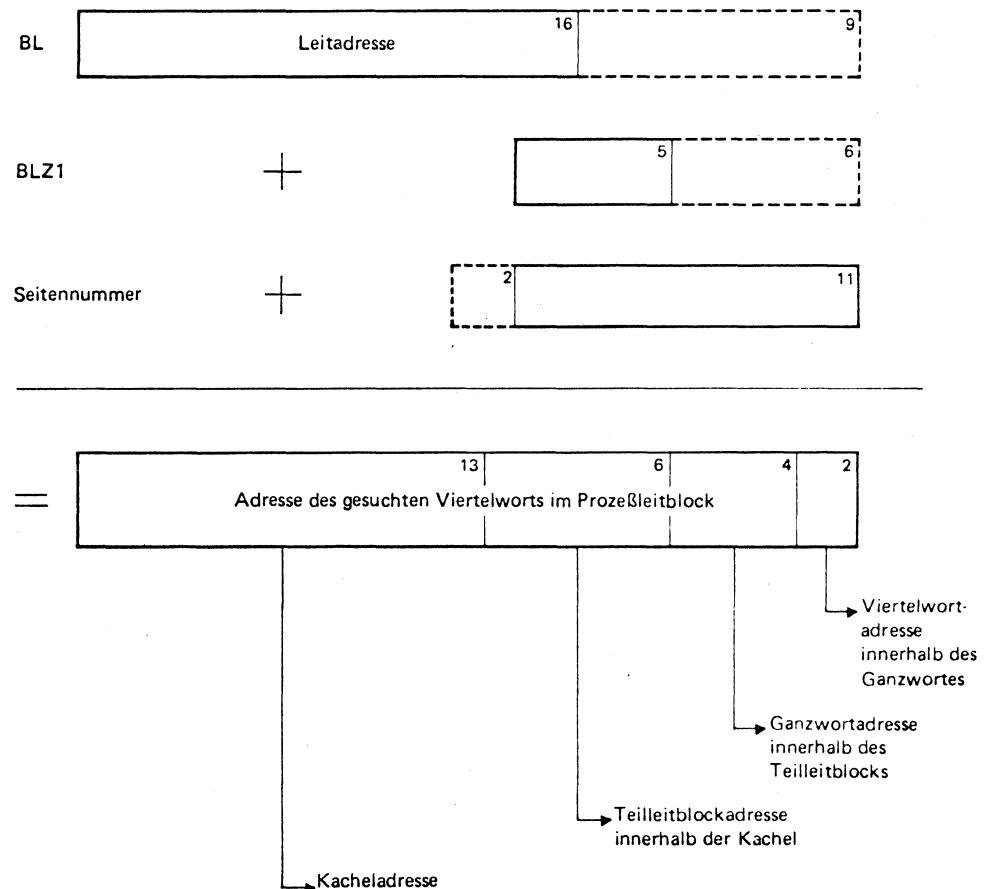

Bild 13 Viertelwort-Ansteuerung in Seiten-Kachel-Tabelle

Das gefundene Viertelwort enthält die gesuchte Kachelnummer, durch die die Seitennummer ersetzt wird.

Da die Ergebnisadresse absolut adressiert und Viertelworte anspricht, handelt es sich um eine 25-Bit-Adresse.

Das oberste Bit im angesteuerten Viertelwort enthält das Schreibschutzbit (siehe 3.2.2) und wird bei dem beschriebenen Ersetzungsvorgang entsprechend berücksichtigt.

Enthält das gefundene Viertelwort keine Kachelnummer (Kachelnummer 0), so wird Speicherschutzalarm ausgelöst.

Das beschriebene Verfahren hat den Nachteil, daß der Speicher zweimal angesteuert werden muß, um den Inhalt einer Adresse auszulesen.

Zuerst muß der Inhalt eines Viertelworts im Prozeßleitblock, der ja im Kernspeicher eingetragen ist, ausgelesen werden. Dann wird mit Hilfe der gefundenen Kachelnummer die endgültige Speicheradresse gebildet, deren Inhalt in einem zweiten Zugriff ausgelesen wird.

Seitenassoziativ-

register

Wenn sehr oft über eine längere Zeit in wenigen Seiten gearbeitet wird bzw. eine Seite abgearbeitet wird, so läßt sich der beschriebene Vorgang durch Benutzung von Seitenassoziativregistern (siehe auch 2.2, Bild 4) wesentlich beschleunigen.

Beim RD 441 sind vier Seitenassoziativregister vorhanden, in denen jeweils die vier zuletzt angesprochenen Seitennummern mit den zugehörigen Kachelnummern eingetragen sind.

Bei einer Speicheransteuerung wird zuerst geprüft, ob die programmrelative Seitennummer bereits in einem "gültigen" der vier Seitenadreßregister steht. Ist das der Fall, so wird die Ersetzung mit der entsprechenden Kachelnummer durchgeführt und damit unter Berücksichtigung des Schreibschutzborts die Speicheransteuerung vorgenommen.

Enthält keines der gültigen Seitenadreßregister die zu ersetzende Seitennummer, dann wird die Kachelnummer wie oben beschrieben aufgefunden und zusammen mit der zugehörigen Seitennummer in das älteste, d. h. am längsten nicht angesprochene der vier Seitenadreßregister eingetragen.

Wenn ein Prozeß die Regie aufgibt, so werden die Gültigkeitsbits auf ungültig gesetzt.

Im Bild 14 wird nochmals die Speicheransteuerung zusammenfassend aufgezeigt.

Bild 16 Ersetzung der programmrelativen 16-Bit-Adresse mit der Kacheladresse

### 3.4. Der Indexspeicher

Durch die Befehle BCI n und ZI m wird ein Bereich von 256 Halbwortzellen des Kernspeichers als sekundärer Indexspeicher deklariert.

Die Adresse des Anfangs des Bereichs wird im 22 Bits umfassenden Indexbasisregister abgelegt. Diese Anfangsadresse unterliegt keiner Beschränkung, so daß der Fall eintreten kann, daß der Bereich in einer anderen Kachel fortgesetzt wird, die im allgemeinen nicht die physikalisch auf die erste Kachel unmittelbar folgende ist. Da hierbei jedoch der Indexbereich in der zweiten Kachel sicher auf der Adresse 0 fortgesetzt wird, ist zur Erfassung dieses Sachverhalts ein nur 11 Bits großes Indexbasiszusatzregister erforderlich.

Vor dem Anlegen eines Indexbereichs wird geprüft, ob die Anfangsadresse und die Endadresse in zugewiesenen und nicht schreibgeschützten Kacheln liegen. Ist das nicht der Fall, wird Speicherschutzalarm ausgelöst.

Bei Adressierung einer Indexzelle wird die Indexadresse (8 Bits) zur Indexbasisadresse addiert und damit der Speicher angesteuert.

Zur Beschleunigung der Indizierung wird als primärer Indexspeicher der Zuordner aus 4 Indexassoziativregistern verwendet, der die vier zuletzt benutzten Indexadressen und die zugehörigen Indexgrößen enthält (siehe 2.2, Bild 5).

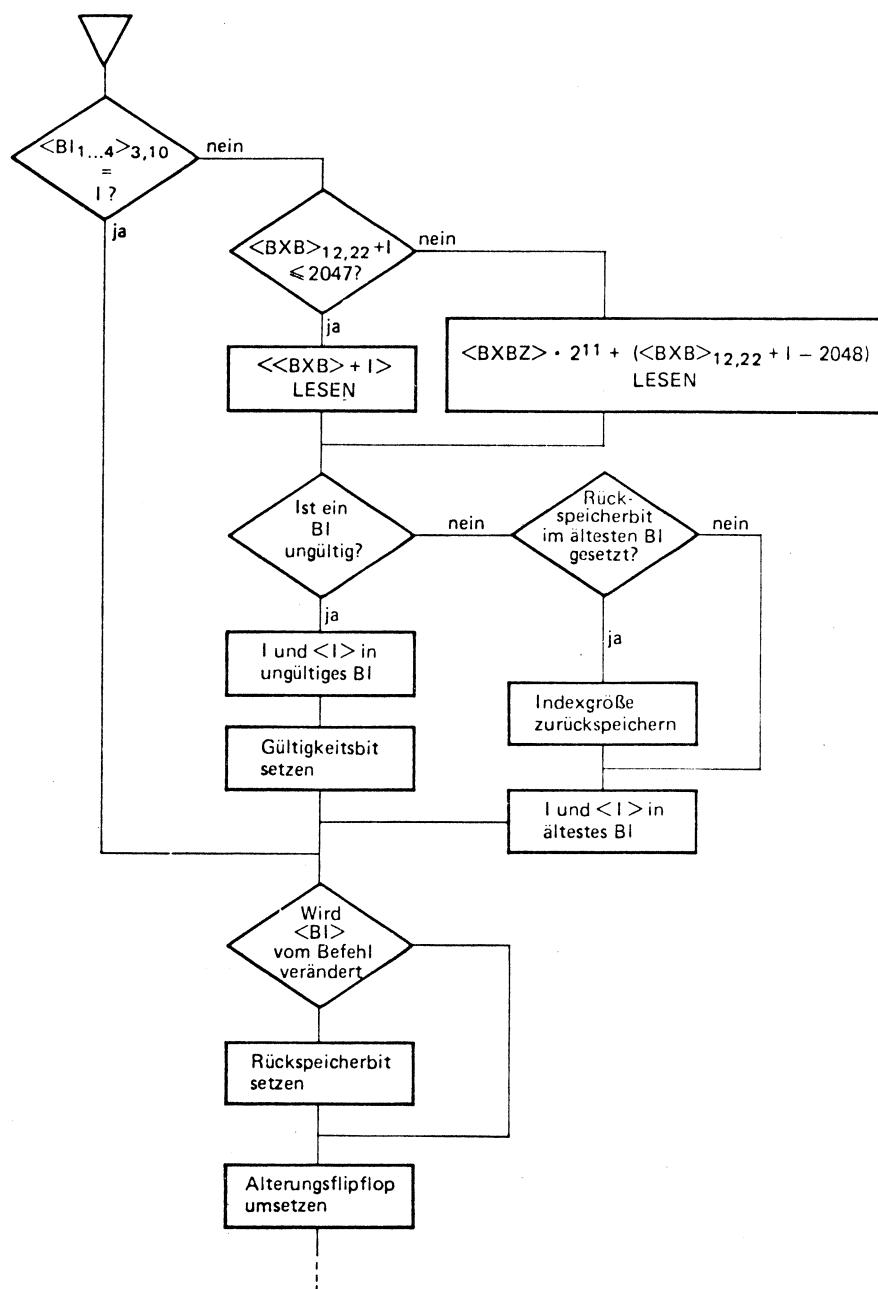

Vor der Speicheransteuerung wird zunächst geprüft, ob die eingesprochene Indexadresse in einem gültigen der vier Indexassoziativregister steht. Ist das der Fall, so wird die Indexgröße (24 Bits) direkt ausgelesen. Im anderen Fall wird der Speicher wie beschrieben mit der Indexbasisadresse (bzw. Indexbasiszusatzadresse) und der Indexadresse angesteuert. Indexadresse und Indexgröße werden dann in ein ungültiges oder das älteste, am längsten nicht mehr angesprochene, Indexregister eingetragen. Zuvor wird anhand des Rückspeicherbits entschieden, ob die zu überschreibende Indexgröße im Indexregister verändert wurde. Ist das der Fall, so wird die Indexgröße vor Einspeichern der neuen Werte in den Indexbereich zurückgespeichert. Das Rückspeicherbit wird bei jeder Veränderung einer Indexgröße gesetzt.

Bild 15 zeigt den beschriebenen Sachverhalt als Signalflußplan.

Bild 15 Indexspeicheransteuerung

## DAS EA-WERK

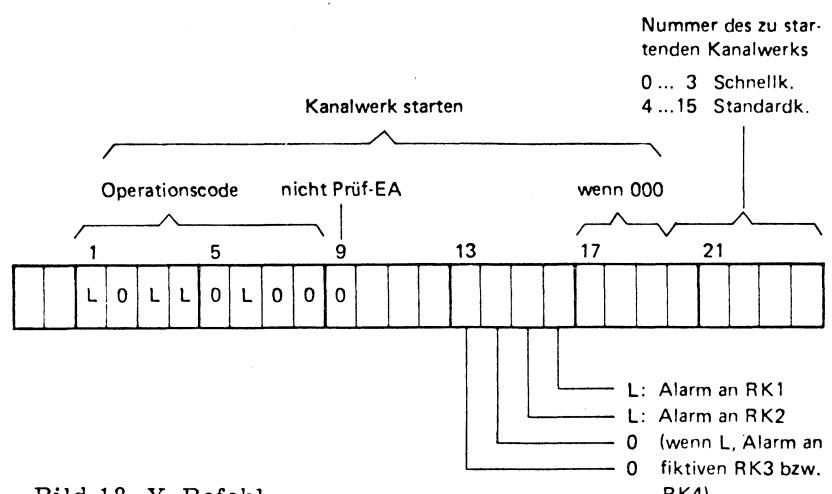

Das EA-Werk besteht aus dem EA-Befehlswerk, den Standard- und Schnellkanalwerken und dem Eingriffswerk.

Das EA-Befehlswerk entschlüsselt die EAW-Befehle und steuert den Datentransfer zwischen Speicher und Kanalwerk.

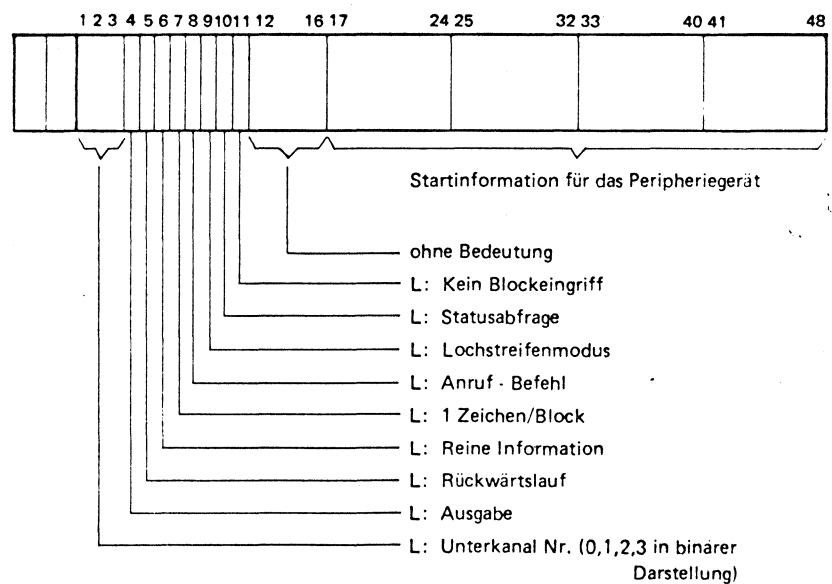

Die Kanalwerke steuern und kontrollieren den Datentransfer mit den peripheren Geräten. Der RD 441 kann mit bis zu 4 Schnell- und 12 Standardkanalwerken ausgestattet werden. Jeder Standardkanal besitzt vier Unterkanäle (Anschlußmöglichkeiten), jeder Schnellkanal besitzt einen Unterkanal, jedoch ein zusätzliches Pufferregister.

Das Eingriffswerk verlangt auf Anstoß eines Kanalwerks, des EA-Befehlswerks oder eines Peripheriegeräts eine Programmunterbrechnung in einem Rechnerkern. Dabei wird vom Eingriffswerk ein Eingriffswort abgespeichert, aus dem der Anlaß des Eingriffs (Unterbrechverlangens) bzw. der Unterbrechung nach Zustandekommen erkennbar ist.

Ein EA-Vorgang wird vom Rechnerkern mit einem Rechnerkernbefehl gestartet. Der angestoßene Vorgang läuft dann simultan zu Rechnerkernoperationen ab. Das Ende des EA-Vorgangs wird dem Rechnerkern durch eine Programmunterbrechnung mitgeteilt.

Der EA-Vorgang ist vor dem Start durch Bereitstellung von EAW-Befehlen, Startinformation, Laden der Kanalbefehlszelle und Laden der Kanalzuordnungszelle vorzubereiten.

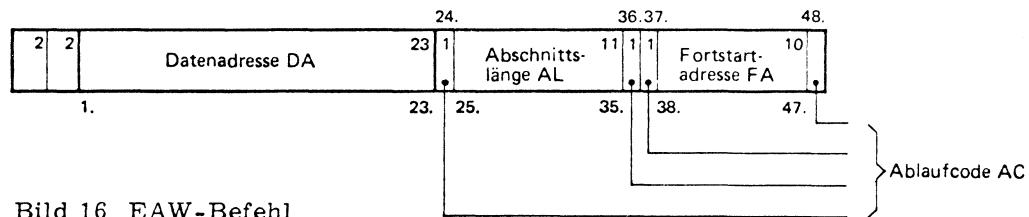

Bild 16 EAW-Befehl

4.1.

Die Speicherkachel 1

Die Kachel 1 ist dem EA-Verkehr fest zugeordnet. Sie ist folgendermaßen eingeteilt:

Ganzwort-

adresse:

|     |                                   |

|-----|-----------------------------------|

| 0   | Kanalbefehlszelle für Kanal 0     |

| 2   | " " "                             |

| .   | .                                 |

| .   | .                                 |

| 30  | Kanalbefehlszelle für Kanal 15    |

| 32  | .                                 |

| .   | .                                 |

| .   | .                                 |

| 62  | .                                 |

| 64  | Kanalzuordnungszelle für Kanal 0  |

| .   | " " " 1                           |

| .   | .                                 |

| .   | .                                 |

| 94  | Kanalzuordnungszelle für Kanal 15 |

| .   | .                                 |

| .   | .                                 |

| 128 | Befehlsketten                     |

| .   | .                                 |

| .   | .                                 |

| .   | .                                 |

Die Datenadresse DA gibt zunächst den Anfang des Abschnitts an. Sie wird während des Transfers laufend erhöht. Gleichzeitig wird die Abschnittslänge AL vom Anfangswert heruntergezählt. Wenn die Abschnittslänge AL = 0 geworden ist, wird der Inhalt der Fortstartadresse FA als neuer EAW-Befehl geholt.

Der Ablaufcode, AC, gliedert und begrenzt den EA-Vorgang und bewirkt unter Umständen programmierte Eingriffe. Es werden 4 Befehle mit verschiedenen AC unterschieden:

| 24 | 36 | 37 | 48 | AC | EAU-Befehl       |

|----|----|----|----|----|------------------|

| X  | 0  | 0  | 0  |    | Stopbefehl       |

| X  | 0  | 0  | L  |    | Fortstartbefehl  |

| X  | 0  | L  | L  |    | Durchstartbefehl |

| X  | L  | L  | L  |    | Neustartbefehl   |

#### 4.2. Der EAW-Befehl

Die drei Befehle mit Bit 48 = L steuern mit ihrer laufenden Adresse DA bei Abschnittslänge AL  $\neq$  0 die Ein- oder Ausgabe je eines Abschnitts. Nach dessen Übertragung wird unter der Fortstartadresse FA des abgearbeiteten Befehls entweder der EAW-Befehl für den nächsten Abschnitt oder ein Stopbefehl gefunden.

Ist in dem folgenden Befehl Bit 24 = L gesetzt, so wird ein programmiert Eingriff erzeugt. Jeder Rechnerkern kann auf diese Weise vom Fortgang des EA-Vorgangs laufend unterrichtet werden. Im übrigen wird der nachfolgende Befehl so abgearbeitet, wie die drei anderen Operationsbits bestimmen.

##### Stopbefehl

Bei Ausführung dieses Befehls wird der EA-Vorgang beendet, es erfolgt ein Stopingriff.

##### Fortstartbefehl

Er wird ins EA-Befehlswerk übernommen und abgearbeitet. Durch eine Folge von Fortstartbefehlen ist gestreutes Lesen und gesammeltes Schreiben möglich.

##### Durchstartbefehl

Mit dem neuen Abschnitt wird ein neuer Block begonnen, d.h. eine Blocklücke erzeugt oder erwartet. Dieser Befehl ermöglicht z. B. das Schreiben mehrerer Blöcke auf ein Magnetband in einem EA-Vorgang.

##### Neustartbefehl

Der vom Neustartbefehl adressierte Abschnitt wird als Startinformation für einen neuen EA-Vorgang für das betrachtete Kanalwerk interpretiert, der dann ohne Start vom Rechnerkern sofort anläuft. Dabei kann ein beliebiger Unterkanal des Kanalwerks ausgewählt werden.

##### Die Kanalbefehlszellen

Jedem Kanalwerk ist eine Kanalbefehlszelle zugeordnet, in der jeweils derjenige EAW-Befehl steht, der vom Kanalwerk gerade bearbeitet wird. Vor dem Start ist die Kanalbefehlszelle des anzusprechenden Kanalwerks mit einem EAW-Befehl zu laden, dessen Fortstartadresse, FA, auf den ersten EAW-Befehl des eigentlichen EA-Programms verweist, und dessen Abschnittslänge AL = 0 ist.

#### 4.3. EA-Vorgang

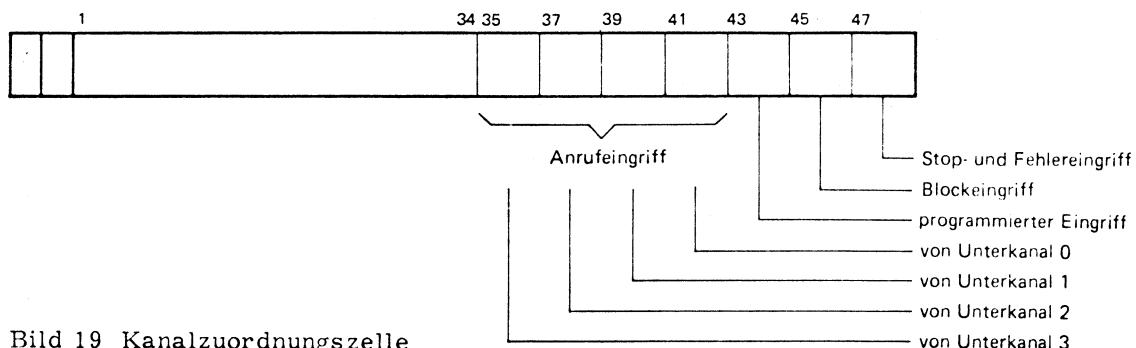

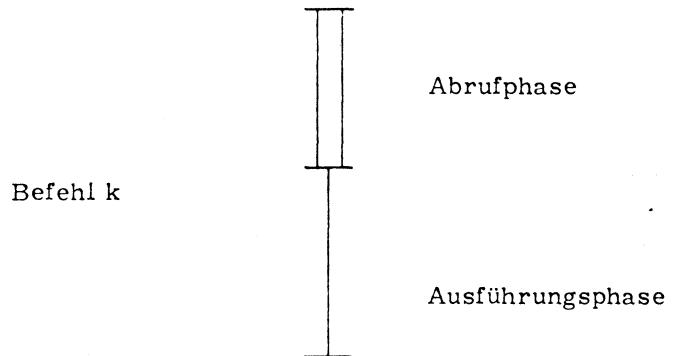

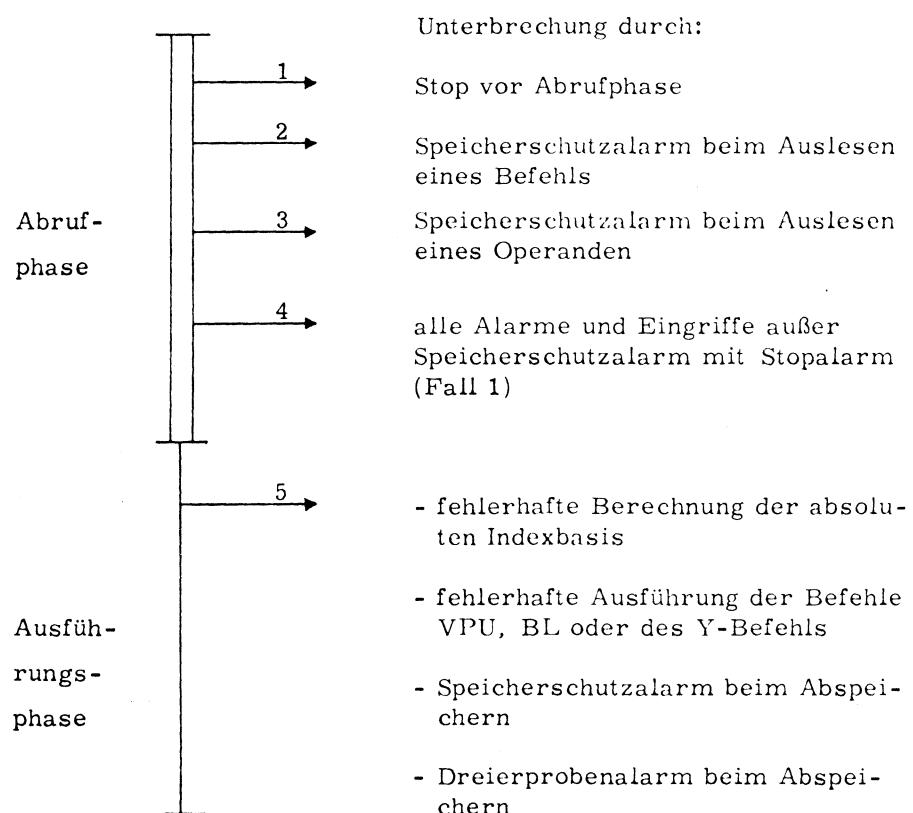

##### Startinformation