Institut für Technische Informatik

Universität Stuttgart

Pfaffenwaldring 47

D-70569 Stuttgart

Diplomarbeit Nr. 3245

# **Adaptive simulationsbasierte Diagnose von Verzögerungsfehlern in kombinatorischen Schaltungen**

Eric Schneider

**Studiengang:** Informatik

**Prüfer:** Prof. Dr. Hans-Joachim Wunderlich

**Betreuer:** Dipl.-Inf. Stefan Holst

**begonnen am:** 15. September 2011

**beendet am:** 16. März 2012

**CR-Klassifikation:** B.8.1, C.4, J.6

# Vorwort

Strukturen mit Dimensionen von wenigen Nanometern, wie man sie in modernen Chips findet, können nur noch mit erheblichem Aufwand in komplexen Herstellungsprozessen produziert werden. Hierbei können, in Abhängigkeit von Prozess-Parametern und Design, Defekte auftreten, die das Zeitverhalten der Schaltung beeinflussen und sowohl rein zufälliger, als auch systematischer Natur sein können. Durch die stetig steigenden Taktfrequenzen häuft sich dabei die Gefahr, dass kleine Verzögerungsfehler auftreten, welche im Vergleich zu statischen Fehlern nur unter Echtzeit-Bedingungen sichtbar werden.

Um die Chipausbeute bei der Herstellung zu erhöhen und Qualitätsanforderungen zu gewährleisten, ist Diagnose deshalb von essentieller Bedeutung. Defekte müssen lokalisiert und anfällige Stellen in fehlerhaften Schaltkreisen ausfindig gemacht werden. Dadurch können das Design und der Herstellungsprozess optimiert und die Kosten pro fehlerfreien Chip bei der Entwicklung gesenkt werden.

Die genaue Diagnose der kleinen Verzögerungsfehler stellt jedoch eine große Herausforderung dar, da das Verhalten und die Simulation dieser Fehler sehr komplex sind, und diese nicht mehr effektiv mit einfacheren Fehlermodellen, wie dem Transitionsfehlermodell [WLRI87] abgedeckt werden können. Zudem erschweren Variationen innerhalb der Schaltkreise die Diagnose.

Das Ziel dieser Arbeit ist die Entwicklung eines Verfahrens zur Diagnose von kleinsten Verzögerungsfehlern, welches Defektstellen effizient lokalisieren und die Defektgrößen der Fehler abschätzen kann. Dabei soll ein simulationsbasierter Ansatz mit einem Zeitsimulator verwendet werden, um die Fehler präzise auszuwerten und stabile Ergebnisse bei Präsenz von Variationen zu ermöglichen.

## Ziel

- Entwicklung eines Verfahrens zur Diagnose von einzelnen kleinsten Verzögerungsfehlern:

- Implementierung von gängigen fehlermodellunabhängigen Methoden zur Reduzierung der initialen Kandidaten.

- Entwicklung einer simulationsbasierten Analyse zur Identifikation der Fehlers.

- Evaluierung des vorgestellten Verfahrens und Diskussion der Resultate.

## Gliederung

Dieses Dokument ist folgendermaßen gegliedert:

**Kapitel 1 – Grundlagen:** Dieses Kapitel dient der Erläuterung der verwendeten Definitionen und Hintergründe.

**Kapitel 2 – Small Delay Fehlermodell:** Dieses Kapitel gibt eine kurze Einführung in das verwendete Fehlermodell. Zusätzlich werden gängige Diagnoseverfahren vorgestellt und diskutiert, sowie Hintergründe zur Diagnose vom SMALLDELAY Fehlern erläutert.

**Kapitel 3 – Adaptive simulationsbasierte Diagnose:** In diesem Kapitel werden die Schritte der entwickelten Diagnosemethode vorgestellt. Diese setzt sich aus zwei Teilen – einer strukturellen und einer simulationsbasierten Analyse – zusammen. Des Weiteren wird das Bewertungsverfahren der Fehlerkandidaten erläutert.

**Kapitel 4 – Ergebnisse:** Hier wird der Aufbau der durchgeführten Experimente vorgestellt, sowie die Ergebnisse präsentiert und diskutiert.

Am Schluss folgt eine Zusammenfassung.

# Inhaltsverzeichnis

|                                                              |    |

|--------------------------------------------------------------|----|

| Liste verwendeter Symbole                                    | 7  |

| Abbildungsverzeichnis                                        | 9  |

| Tabellenverzeichnis                                          | 9  |

| Algorithmenverzeichnis                                       | 10 |

| <b>1</b> Grundlagen                                          | 11 |

| 1.1 Erklärung grundlegender Begriffe . . . . .               | 11 |

| 1.2 Verzögerungsfehler und Modelle . . . . .                 | 13 |

| 1.3 Logische Diagnose kombinatorischer Schaltungen . . . . . | 15 |

| 1.3.1 Cause-Effect Verfahren . . . . .                       | 15 |

| 1.3.2 Effect-Cause Verfahren . . . . .                       | 15 |

| 1.4 POINTER Diagnose . . . . .                               | 16 |

| 1.5 Wave Zeitsimulator . . . . .                             | 17 |

| <b>2</b> SMALLDELAY Fehlermodell                             | 19 |

| 2.1 Hintergrund . . . . .                                    | 19 |

| 2.2 Diagnose von Verzögerungsfehlern . . . . .               | 20 |

| 2.2.1 Critical Path Tracing für Verzögerungsfehler . . . . . | 20 |

| 2.2.2 Weitere Verfahren . . . . .                            | 22 |

| 2.3 POINTER Diagnose mit Resimulation . . . . .              | 23 |

| 2.4 Neuer Ansatz . . . . .                                   | 24 |

| <b>3</b> Adaptive simulationsbasierte Diagnose               | 27 |

| 3.1 Strukturelle Analyse . . . . .                           | 27 |

| 3.1.1 Räumliche Einschränkung der Kandidaten . . . . .       | 28 |

| 3.1.2 Zeitliche Einschränkung der Kandidaten . . . . .       | 31 |

| 3.2 Simulationsbasierte Analyse . . . . .                    | 34 |

| 3.2.1 Aufbau . . . . .                                       | 35 |

| 3.2.2 Adaptive Simulation . . . . .                          | 35 |

| 3.3 Bewertung der Kandidaten . . . . .                       | 40 |

| 3.3.1 <i>Reward &amp; Penalty</i> . . . . .                  | 40 |

| 3.3.2 Berücksichtigung der Signal-Stabilität . . . . .       | 41 |

|                                                |    |

|------------------------------------------------|----|

| 3.4 Zusammenfassung . . . . .                  | 43 |

| 4 Ergebnisse . . . . .                         | 45 |

| 4.1 Aufbau der Experimente . . . . .           | 45 |

| 4.2 Diagnose von Verzögerungsfehlern . . . . . | 49 |

| 4.2.1 Stabilität des Verfahrens . . . . .      | 52 |

| 4.3 Evaluierung . . . . .                      | 54 |

| 5 Zusammenfassung . . . . .                    | 57 |

| A ADAMA dfdiagnose . . . . .                   | 59 |

| B Notizen zur Implementierung . . . . .        | 63 |

| Literaturverzeichnis . . . . .                 | 71 |

# Liste verwendeter Symbole

|                                               |                                                                            |

|-----------------------------------------------|----------------------------------------------------------------------------|

| $\Delta^T(o), \Delta_{min}^T, \Delta_{max}^T$ | Slack eines Ausgangs $o$ , Kleinster bzw. größter Slack an einem Knotens   |

| $\delta_f$                                    | Defektgröße eines SMALLDELAY-Fehlers                                       |

| $\Delta_{err}$                                | Fehler/Abweichung der Defektgröße                                          |

| $\delta_{est}, \delta_{fin}$                  | Erste Abschätzung der Defektgröße und Korrektur                            |

| $\delta_{min}(s), \delta_{max}(s)$            | Kleinste/Größte Defektgröße eines Knoten $s$                               |

| $\omega_\sigma, \omega_t$                     | Gewichte für die Evidenz-Komponenten                                       |

| $\omega_U, \omega_U(o)$                       | Fehlerwahrscheinlichkeit eines Ausgangs in der Umgebung $U$                |

| $\Pi$                                         | Testmustersatz, Testsatz                                                   |

| $\pi$                                         | Testmuster, Verzögerungstest                                               |

| $\sigma_f, \iota_f, \tau_f$                   | Komponenten der Globalen Evidenz eines Fehlers $f$                         |

| $\sigma_{f,\pi}, \iota_{f,\pi}, \tau_{f,\pi}$ | Komponenten der Evidenz eines Fehlers $f$ für ein Testmuster $\pi$         |

| $A, B, Z$                                     | Eingänge und Ausgang eines Gatters                                         |

| $A_T$                                         | Zusätzlicher Zustandsvektor eines Signals für mehrwertige Logik            |

| $A_V$                                         | Zustandsvektor eines Signals mit booleschen Werten                         |

| $D_s$                                         | Defektgrößen-Intervall eines Knoten $s$                                    |

| $e(f, \Pi)$                                   | Globale Evidenz                                                            |

| $e(f, \pi)$                                   | Evidenz eines Testmusters $\pi$                                            |

| $EA, LS$                                      | Ankunfts-, Stabilisierungszeit eines Signals                               |

| $f$                                           | (SMALLDELAY-)Fehler                                                        |

| $G, G(V, E)$                                  | Kombinatorischer Schaltkreis, Netzliste mit Knotenmenge $V$ und Kanten $E$ |

| $I$                                           | Menge an Schaltungseingängen                                               |

| $i, j, k$                                     | Indizes                                                                    |

| $LB, UB$                                      | Untere/Obere Grenze eines Defektintervalls                                 |

| $N$                                           | Anzahl der Knoten bzw. Gatter im Schaltkreis                               |

| $n, g$                                        | Ein Knoten bzw. Gatter                                                     |

| $O, o$                                        | Menge an Schaltungsausgängen, ein Ausgang                                  |

| $q$                                           | Quantisierungsfaktor                                                       |

| $S, s$                                        | Initiale Kandidaten, Kandidat                                              |

|        |                                        |

|--------|----------------------------------------|

| $T, t$ | Abtastzeit, Zeitpunkt                  |

| $U$    | Umgebung/Bereich um die Abtastzeit $T$ |

# Abbildungsverzeichnis

---

|     |                                                           |    |

|-----|-----------------------------------------------------------|----|

| 1.1 | Schema einer Fehlersimulation                             | 12 |

| 1.2 | Aktivierung eines Verzögerungsfehlers                     | 14 |

| 1.3 | Beispiel der Waveform-Repräsentation                      | 18 |

| 2.1 | Beispiel SmallDelay-Fehlermodell                          | 19 |

| 2.2 | Haftfehler Repräsentanten bei nicht robuster Propagierung | 24 |

| 2.3 | Diagnoseansatz – Übersicht                                | 25 |

| 3.1 | Beispiel: Critical Path Tracing                           | 29 |

| 3.2 | Strukturelle Fehler-Äquivalenz                            | 31 |

| 3.3 | Überschätzung der Defektgröße                             | 34 |

| 3.4 | Aufbau der simulationsbasierten Diagnose                  | 35 |

| 3.5 | Sigma und Iota einer Kandidatenmenge                      | 37 |

| 3.6 | Selektive Simulation                                      | 39 |

| 3.7 | Signal Stabilität                                         | 41 |

# Tabellenverzeichnis

---

|     |                                                               |    |

|-----|---------------------------------------------------------------|----|

| 2.1 | Wahrheitstabelle eines NAND-Gatters in sechswertiger Logik.   | 21 |

| 4.1 | Daten der untersuchten Schaltkreise                           | 46 |

| 4.2 | Rang, Rang-Gruppe und Mittel-Rang                             | 48 |

| 4.3 | Diagnose-Ergebnisse ISCAS '85 und '89                         | 49 |

| 4.4 | Diagnose bei vollständiger Quantisierung der Defektintervalle | 50 |

| 4.5 | Diagnose-Ergebnisse ITC '99 und NXP                           | 51 |

| 4.6 | Diagnose bei Variation der Nominalverzögerungen               | 53 |

| 4.7 | Diagnose auf kompaktierten Antworten                          | 54 |

| 4.8 | Zusammenfassung Experimente                                   | 55 |

|     |                               |    |

|-----|-------------------------------|----|

| B.1 | Liste der verwendeten Symbole | 65 |

|-----|-------------------------------|----|

## Algorithmenverzeichnis

---

|     |                                                          |    |

|-----|----------------------------------------------------------|----|

| B.1 | Evaluierung eines Gatters in sechswertiger Logik (PPSFP) | 66 |

| B.2 | Critical Path Tracing für einen Test (PPSFP)             | 67 |

| B.3 | Rückpropagierung der $D$ -Markierung (PPSFP)             | 68 |

| B.4 | Waveform Integral                                        | 70 |

# 1 Grundlagen

## 1.1 Erklärung grundlegender Begriffe

### Netzlisten

Eine **Netzliste** ist ein gerichteter *azyklischer* Graph  $G(V, E)$  über einer Knotenmenge  $V$ , sowie einer Kantenmenge  $E$ , und dient der Beschreibung kombinatorischer Schaltkreise auf Logik-Ebene. Dabei repräsentiert jeder Knoten  $n \in V$  ein bestimmtes Gatter des Schaltkreises. Die einzelnen Kanten  $(x, y) \in E$  modellieren jeweils eine direkte Verbindung zwischen zwei Logikgattern  $x, y \in V$ , bei denen der Ausgang von  $x$  mit einem Eingang von  $y$  verknüpft ist. Dabei ist  $x$  ein direkter Vorgänger im *Fan-In* von  $y$  – umgekehrt ist  $y$  ein direkter Nachfolger im *Fan-Out* von  $x$ . Die Menge der Knoten ohne direkten Vorgänger (Nachfolger) bezeichnet die Menge der primären Eingänge (Ausgänge) eines Schaltkreises und wird im Folgenden mit  $I$  ( $O$ ) notiert.

Um mit Hilfe von Netzlisten den Wert eines beliebigen Gatters  $n \in V$  im Schaltkreis zu bestimmen, wendet man dessen assozierte Funktion  $\varphi(x_0, x_1, \dots, x_{k-1})$  auf die Werte der direkten Vorgänger an. Aufgrund der Datenabhängigkeiten setzt dies voraus, dass alle Vorgänger zuvor berechnet wurden und deren Werte bekannt sind. Eine Möglichkeit dies zu gewährleisten, ist die Evaluierung der einzelnen Knoten in  $V$  in topologisch sortierter Reihenfolge von Schaltungseingängen zu Ausgängen, indem  $V$  in sogenannte *Ebenen* (Level)  $L_0, L_1, \dots, L_{k-1}$  partitioniert wird, sodass für alle Knoten  $x \in L_i, y \in L_j$  gilt:  $(x, y) \in E \Rightarrow i < j$ .

### Defekte, Fehler und Fehlermodelle

Als **Defekt** bezeichnet man eine Störung bzw. Veränderung in der physischen Struktur des Schaltkreises, die z.B. durch Verunreinigungen im verwendeten Material, durch auftretende Variationen im Herstellungsprozess oder durch einen fehlerhaften Entwurf entstanden sind. Solche Defekte können die Schaltung derart beeinflussen, dass das Verhalten von der Spezifikation abweicht. Um dieses Fehlverhalten aufgrund von Defekten beschreiben zu können, wird im Allgemeinen der Begriff „*Fehler*“ verwendet. Ein **Fehler** dient der logischen Abstraktion und Einschränkung des Defektausmaßes auf einer höheren Ebene und repräsentiert für gewöhnlich eine ganze Klasse unterschiedlicher physischer Defekte, die aber allesamt ein und das selbe Fehlverhalten verursachen.

Fehler werden nach einem bestimmten **Fehlermodell** spezifiziert, welches die Zahl der möglichen Defektszenarien auf eine endliche Menge beschränkt. So modelliert das bekannte *Haftfehlermodell* (Stuck-At) für jede *Fehlerstelle* (wie z.B. Gatter oder Leitungen) einen *StuckAt-0* und einen *StuckAt-1* Fehler, sowie den fehlerfreien Zustand, während man beim *Brückenfehlermodell* für eine *wired-AND*- oder *wired-OR*-Brücke an einer Stelle verschiedener Kombinationen für ein *Aggressor*-Signal zur Wahl haben kann. [BA02] bietet eine Übersicht von unterschiedlichen Fehlermodellen für verschiedene Abstraktionsebenen.

Darüber hinaus unterscheidet man zwischen *Einzel-* und *Mehrfachfehlermodellen*. In letzterem wird die Möglichkeit des gleichzeitigen Auftretens verschiedener Fehler berücksichtigt, was die Komplexität des Modells letztlich aufgrund der steigenden Zahl der Fehler-Kombinationen erhöht. Die Wahl des Fehlermodells bestimmt somit sowohl die Präzision, aber auch die Komplexität der modellierten Defekte.

### Fehlersimulation

Mit Hilfe von expliziter **Fehlersimulation** kann das Verhalten von Schaltkreisen unter Einfluss von Defekten gezielt getestet und beobachtet werden. Dadurch gewinnt man die Erkenntnis, ob ein Defekt in der Schaltung für bestimmte Eingabestimuli (Testmuster) einen Fehler am Ausgang produziert und welches Ausmaß dieser Fehler hat. Dieser Mechanismus kann dann für eine Reihe verschiedener Anwendungen verwendet werden [WWW06], wie der Bestimmung der *Fehlerabdeckung* von automatisch generierten **ATPG (Automatic Test Pattern Generator)** Testmustersätzen, oder im Rahmen einer *Fehlerdiagnose* z.B. durch die Generierung eines *Fehlerwörterbuchs*.

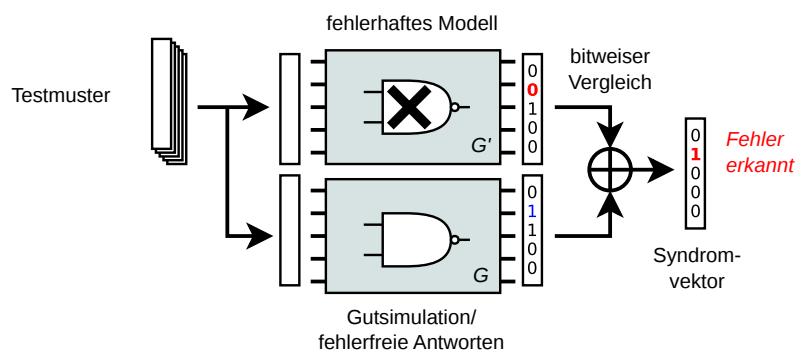

Abb. 1.1 zeigt die schematische Darstellung einer Fehlersimulation. Hier wird ein Testmuster an die primären Eingänge von zwei Instanzen eines Schaltkreises angelegt. Der untere Schaltkreis

**Abbildung 1.1:** Schema eines Fehlersimulation. – Die Antworten der fehlerhaften Schaltung  $G'$  werden mit denen der Spezifikation  $G$  verglichen.

$G$  repräsentiert eine Gutsimulation, die Referenzantworten gemäß der Spezifikation liefert. Schaltkreis  $G'$  wurde dagegen so modifiziert, dass das beabsichtigte Verhalten dem Einfluss eines bestimmten Fehlers entspricht. Diese Modifikation wird **Fehlerinjektion** genannt. Im Anschluss an die Simulation werden die Antwortmuster beider Schaltkreise von den primären Ausgängen abgelesen und miteinander verglichen. Durch eine bitweise XOR-Verknüpfung ( $\oplus$ ) der Antworten erhält man ein **Symptom**, welches Aufschluss darüber gibt, ob ein Ausgang fehlerhaft ist oder nicht. Die vereinigten Symptome eines ganzen Testmustersatzes bilden das **Syndrom** des Fehlers.

Damit ein Fehler von einem Testmuster sichtbar gemacht werden kann, müssen die folgenden Bedingungen erfüllt sein:

- Der Fehler muss über die primären Eingänge **aktiviert** werden (*fault excitation*).

- Der Fehler muss zu den primären Ausgängen **propagiert** werden (*fault propagation*).

Manche Fehler haben solch komplexe Aktivierungs- und Propagierungsbedingungen, sodass diese bei Verwendung von pseudozufallsgenerierten Testmustern nur mit einer sehr geringen Wahrscheinlichkeit sichtbar werden. Hierfür müssen ATPG-Tools zur Testmustergenerierung verwendet werden, um die Detektierbarkeit der Fehler und somit die Fehlerabdeckung der Testmustersätze zu verbessern.

## 1.2 Verzögerungsfehler und Modelle

Im Gegensatz zu den Defekten aus *statischen* Fehlermodellen, wie dem Haftfehlermodell, beeinflussen Verzögerungsdefekte nicht die logische Struktur der Schaltung, sondern das **Zeitverhalten** der einzelnen Gatter und Leitungen. Dabei können Signalwechsel (Transitionen) an den defekten Stellen verlangsamt werden, wodurch es vorkommen kann, dass bestimmte Transitionen im Schaltkreis die *Zeitanforderungen* der Schaltung überschreiten, die durch die geforderten Taktfrequenzen der Schaltung bestimmt sind. In der Regel verletzt ein Signal die Zeitanforderungen, wenn die Differenz von *Abtastzeit* und *Stabilisierungszeit* am Ausgang negativ ist. Diese Differenz wird auch **Slack** genannt. Zum Zeitpunkt der Abtastung können die Signalwechsel an den Ausgängen nicht mehr registriert werden, was typischerweise einen Fehler zur Folge hat.

Um Verzögerungsfehler testen zu können, muss der Fehler durch eine Signaltransition an der Fehlerstelle aktiviert werden. Zur Erzeugung dieser Transitionen, benötigt man Stimuli in Form eines *Verzögerungstests*, der aus einer Sequenz von zwei Testmustern, einem **Initialisierungsvektor (IV)** und einem **Propagierungsvektor (PV)**, besteht. Der IV initialisiert dabei die Eingänge und die restlichen Knoten der Schaltung mit einem Signalwert. Durch den PV finden dann Signalwechsel an bestimmten Eingängen statt, die als Transitionen durch den Schaltkreis propagiert werden.

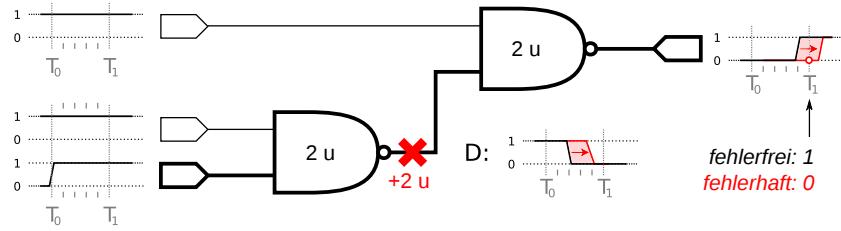

**Abbildung 1.2:** Beispiel eines Verzögerungstests. – Aktivierung und Propagierung eines Verzögerungsfehlers an der Leitung  $D$  mit  $IV = (110)$  und  $PV = (111)$ . Verzögerungen sind in Einheiten  $u$  angegeben.

### Fehler-Modelle

In der Literatur zu Test und Simulation taucht eine an Vielfalt möglichen Verzögerungsfehler-Modellen auf [KC98, MA98]. Zu den bekanntesten zählen dabei das *Transitionsfehlermodell* [WLRI87], das *Gatterverzögerungsmodell* [CIR87] und das *Pfadverzögerungsmodell* [Smi85]. Im Folgenden werden diese kurz vorgestellt:

**Transitionsfehler** Transitionsfehler modellieren für einen Test eine *unendliche* lokale Verzögerung an einer Leitung oder einem Gatter. Dabei wird zwischen Fehlern bei fallender (*Slow-to-Fall (STF)*) und steigender Flanke (*Slow-to-Rise (STR)*) unterschieden. In [WLRI87] wurde gezeigt, dass diese Transitionsfehler sehr effizient mit Hilfe von *temporären Haftfehlern* simuliert werden können und bei der Berechnung dabei keine Zeitinformation benötigen. So zeigt etwa ein aktiverter *STR*-Fehler an einem Gatter ein identisches Verhalten, wie ein *StuckAt-0* Fehler aus dem Haftfehlermodell. Dasselbe gilt auch für *STF* und *StuckAt-1* Fehler.

**Gatterverzögerungsfehler** Ein Gatterverzögerungsfehler nach [CIR87] liegt vor, wenn ein lokaler Defekt die Signalpropagierungszeiten eines Gatters – für entweder steigende oder fallende Flanken – zusätzlich um eine Defektgröße  $\delta_f$  erhöht und der Fehler an mindestens einem sensibilisierten Ausgang im Ausgangskegel sichtbar wird. Im Gegensatz zum Transitionsfehlermodell ([WLRI87]), wird hier das Zeitverhalten einzelner Gatter mit berücksichtigt und durch Intervalle abgeschätzt. [IRW90] definiert mit Hilfe der Slacks an den einzelnen Knoten für jede Fehlerstelle eine Mindestdefektgröße, um die Testbarkeit zu gewährleisten.

**Pfadverzögerungsfehler** In diesem Modell von [Smi85] wird angenommen, dass sich ein Verzögerungsdefekt im Schaltkreis global entlang der Leitungen eines kompletten Pfades von primär Eingang nach primär Ausgang aufteilt. Der Pfadverzögerungsfehler (PDF) tritt dann auf, sobald eine Transition entlang dieses Pfades vom Eingang zum Ausgang propagiert. Dabei wird anhand der Polarität der Transition am Eingang zwischen steigenden und fallenden PDFs unterschieden.

## 1.3 Logische Diagnose kombinatorischer Schaltungen

Bei der logischen Diagnose eines kombinatorischen Schaltkreises versucht man anhand der Testantworten eines fehlerhaften Chips, auf die Defektursache im Schaltkreis zu schließen. Während der Chipentwicklung ist dies von besonderem Interesse, da Fehler, die in verschiedenen Chips aufgrund systematischer Defekte häufiger auftreten, auf fehleranfällige Stellen in der Schaltung hindeuten können. Mit der logischen Diagnose versucht man deshalb diese fehleranfälligen Stellen im Schaltkreis zu **identifizieren**, um Maßnahmen zur Anpassung des Designs bzw. des Layouts einzuleiten und zukünftige Chips gegen die Fehler abzuhärten.

Die logische Diagnose kombinatorischer Schaltungen hat sich hauptsächlich in zwei unterschiedliche Paradigmen aufgespalten: Dies sind die sogenannten *Cause-Effect*- und *Effect-Cause*-Verfahren [WWW06].

### 1.3.1 Cause-Effect Verfahren

Bei **Cause-Effect** Verfahren versucht man anhand der Antworten simulierter Fehler (*Causes*) aus einem festgelegten Modell, das Syndrom (*Effect*) des zu diagnostizierenden Chips, dem sogenannten **DUD (Device under Diagnosis)**, zu untersuchen. Hierfür werden *typischerweise* sogenannte **Fehlerwörterbücher** verwendet, in denen die Testantworten aller modellierten Fehler zum Vergleich abgespeichert sind. Ein Nachteil dieses Verfahrens ist die Abhängigkeit der Größe des Wörterbuchs von der Zahl der modellierten Fehler, der Anzahl der Ausgänge im Schaltkreis, sowie der untersuchten Testmuster. Zudem können nur solche Fehler genau diagnostiziert werden, die vom gewählten Modell abgedeckt werden und somit vom Wörterbuch erfasst sind [WWW06]. Abweichungen, die im Fehlermodell nur implizit oder garnicht abgedeckt sind, können für die Diagnose irreführend sein und sogar soweit führen, dass diese nicht diagnostiziert werden können.

### 1.3.2 Effect-Cause Verfahren

**Effect-Cause** Verfahren verwenden einen umgekehrten Ansatz. Hierbei geht man der Fehlerursache des DUDs auf den Grund, indem das Syndrom anhand der Informationen über den Schaltkreis genauer analysiert und die mögliche Defektursache auf eine Menge an Fehlerkandidaten eingeschränkt wird. Ein Vorteil des Effect-Cause Ansatzes ist die allgemeine Unabhängigkeit von einem Fehlermodell, da keine expliziten Annahmen über Fehler gemacht werden [WWW06].

Ein bekanntes Verfahren ist das **Strukturelle Pruning** [WL89], auch *Backconing* genannt. Hierbei werden die möglichen Fehlerkandidaten auf den Schnitt der Eingangskegel aller fehlerhaften Schaltungsausgänge logisch eingegrenzt.

Das **SLAT Verfahren (Single Location At a Time)** aus [BHHS01, Hui04] verfolgt einen so-nannten „*Inject & Evaluate*“ Ansatz, bei dem Fehler unterschiedlichster Art mit Hilfe von einfacher Haftfehlersimulation lokalisiert werden. Hierbei werden für jeden fehlerhaften Test Haftfehler an Kandidatenstellen simuliert, um Testmuster mit einer sogenannten *SLAT-Eigenschaft* zu identifizieren. Bei einem Testmuster mit SLAT-Eigenschaft existiert ein Haftfehler, der das Syndrom durch einen *lokalen* Defekt für diesen Test erklären kann. Findet sich dabei keine Stelle, die alle Syndrome der fehlerhaften Tests durch SLAT-Mustern erklären kann, so wird die kleinstmögliche Menge an Fehlerstellen gesucht (*Multiplets*), die diese abdeckt.

## 1.4 POINTER Diagnose

Eine Diagnosemethode zur Analyse von Testantworten ist das **POINTER (Partially Overlapping Impact couNTER)** Verfahren aus [HW09], welches eine Erweiterung des SLAT-Verfahrens von [BHHS01, Hui04] bildet und sich zur *Effect-Cause* Diagnose von beliebigen Fehlern aus dem **CLF-Kalkül (Conditional Line Flip)** [Wun09] bewährt hat. Im CLF-Modell wird das Fehlverhalten eines Signals  $Z$  allgemein durch eine Bedingung mit beliebiger Komplexität modelliert, sodass  $Z_f = Z \oplus (\text{Bedingung})$ .

Zur Diagnose dieser Fehler verwendet das POINTER-Verfahren dabei Haftfehler, die in einer **Fehlermaschine (FM)** simuliert werden, um Referenzantworten zu generieren. Beim Vergleichen der Antworten mit dem DUD werden dabei für jeden Fehler und jedes untersuchte Testmuster sogenannte *Evidenzen* berechnet, die zur Bewertung der möglichen Fehlerkandidaten und zur Identifizierung der Defektstelle dienen. Die **Evidenz** eines Fehlers  $f$  für ein Testmuster  $\pi$  ist als Tupel  $e(f, \pi) = (\sigma_{f,\pi}, \iota_{f,\pi}, \tau_{f,\pi}, \gamma_{f,\pi})$  definiert, dessen Komponenten durch bitweises Vergleichen des Antwortmusters aus FM und DUD extrahiert werden:

- $\sigma_{f,\pi}$  ist die Anzahl der vom Referenzfehler  $f$  *erklärt*en fehlerhaften Ausgänge des DUDs.

- $\iota_{f,\pi}$  ist die Anzahl der von  $f$  falsch *vorhergesagten* fehlerhaften Antwortbits.

- $\tau_{f,\pi}$  ist die Anzahl der fehlerhaften Ausgänge im DUD, die vom Referenzfehler *nicht erklärt* werden können.

- $\gamma_{f,\pi}$  ( $= \min(\{\sigma_{f,\pi}, \iota_{f,\pi}\})$ ) ermöglicht eventuell Annahmen, ob ein Symptom von einem einzelnen oder von mehreren Haftfehlern erzeugt wurde.

Für einen ganzen Testmustersatz  $\Pi = \{\pi_0, \pi_1, \dots, \pi_{k-1}\}$  mit  $k$  Tests, werden die Evidenzen  $e(f, \pi)$  aller Antwortmuster  $\pi \in \Pi$  eines Referenzfehlers  $f$  komponentenweise aufsummiert, um die *globale* Evidenz  $e(f, \Pi)$  des Fehlers zu berechnen:

$$e(f, \Pi) = (\sigma_f, \iota_f, \tau_f, \gamma_f) = (\sum_{\Pi} \sigma_{f,\pi}, \sum_{\Pi} \iota_{f,\pi}, \sum_{\Pi} \tau_{f,\pi}, \sum_{\Pi} \gamma_{f,\pi}).$$

Nach Berechnung der globalen Evidenzen *aller* Fehlerkandidaten, werden diese mit Hilfe der folgenden **GSI (Gamma-Sigma-Iota)** Bewertungsfunktion sortiert:

1.  $\gamma_{f_1} > \gamma_{f_2} \Rightarrow \text{Rang}(f_1) > \text{Rang}(f_2)$ ,

2.  $\sigma_{f_1} > \sigma_{f_2} \Rightarrow \text{Rang}(f_1) < \text{Rang}(f_2)$ , wenn  $\gamma_{f_1} = \gamma_{f_2}$ ,

3.  $\iota_{f_1} > \iota_{f_2} \Rightarrow \text{Rang}(f_1) > \text{Rang}(f_2)$ , wenn  $\gamma_{f_1} = \gamma_{f_2}$  und  $\sigma_{f_1} = \sigma_{f_2}$ .

Dabei wird zunächst nach aufsteigendem  $\gamma_f$  sortiert, um jene Kandidaten an die Spitze der Liste zu bringen, die als einzelne *bedingte* Haftfehler das Syndrom des DUDs erklären können. Anschließend werden die Kandidaten mit gleichem  $\gamma_f$  in absteigender Reihenfolge nach der Anzahl der erklärten Bits  $\sigma_f$  sortiert. In einem letzten Schritt werden gleiche Kandidaten nach aufsteigenden  $\iota_f$  geordnet, um die Anzahl der Fehlvorhersagen zu minimieren.

Je niedriger der Rang eines Kandidaten ist, umso besser kann dieser das Syndrom des DUDs erklären und desto wahrscheinlicher verweist der Fehler auf die eigentliche Defektstelle.

## 1.5 Wave Zeitsimulator

In dieser Arbeit wird ein dynamischer Zeitsimulator namens „*Wave*“ verwendet, welcher von Stefan Holst entwickelt wurde, um die Schaltaktivität in Schaltkreisen zur Abschätzung der Leistungsaufnahme messen zu können.

Da die Simulation von Schaltkreisen stark parallelisierbar ist und dynamische Zeitsimulation im Vergleich zur Booleschen Logiksimulation einen hohen Rechenaufwand hat, macht dieser dabei Gebrauch von der NVIDIA®CUDA™ Architektur [NVI12], um den Simulationsprozess mit Hilfe von Parallelisierung auf CUDA™-fähigen Grafikkarten zu beschleunigen. Durch das *Many- Threading* Paradigma kann der Simulator vorhandenen Struktur- und Daten-Parallelismus bei der Simulation ausbeuten. Dabei kann dieser eine große Anzahl an Gattern für mehrere Testmuster auf verschiedenen Rechenkernen der **GPGPU (General Purpose Graphics Processing Unit)** parallel verarbeiten und evaluieren

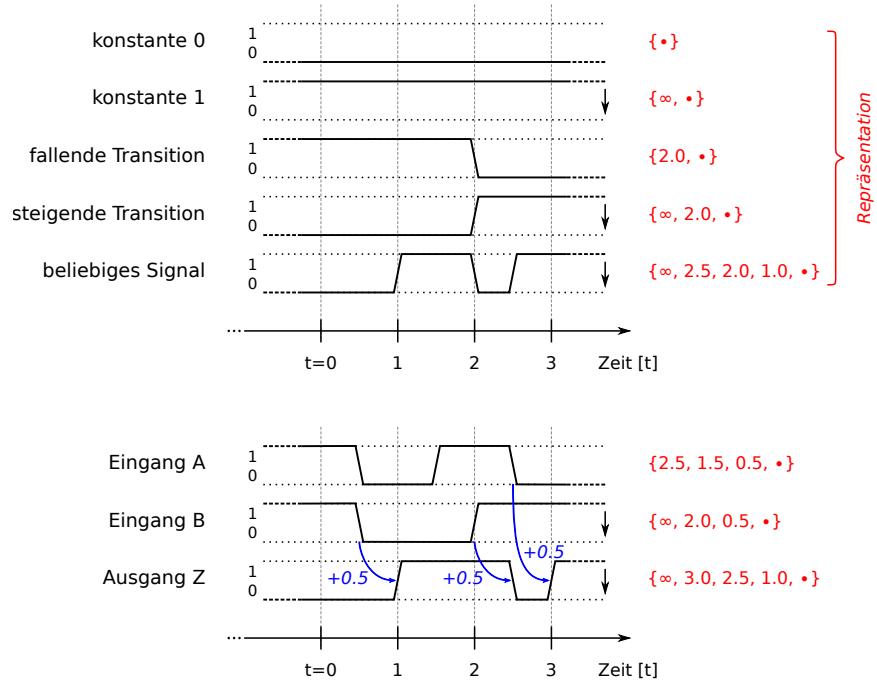

Der *Wave*-Simulationskern erlaubt dabei die präzise Modellierung und effiziente Evaluierung *vollständiger* Signalverläufe an Gattern durch sogenannte *Waveforms*. Ein **Waveform** beschreibt den Verlauf eines Signals anhand einer Liste von absteigend sortierten Zeitpunkten  $t_i \in \mathbb{R}_0^+$ , an denen jeweils Signalwechsel stattfinden. Nach Definition muss das durch das Waveform beschriebene Signal für  $t \rightarrow \infty$  einen Wert von '0' haben, weshalb gegebenenfalls eine *künstliche* Transition ( $\infty$ ) hinzugefügt werden muss. Durch die umgekehrte Reihenfolge bei der Auswertung der Transitionen können die Waveforms bezüglich der Speicherallokation effizienter berechnet werden.

In Abbildung 1.3 sind Beispiele von Signalverläufen mit der dazugehörigen Waveform- Repräsentation illustriert.

**Abbildung 1.3:** Beispiel der Waveform-Darstellung. – Das Symbol  $\bullet$  wird als Terminalzeichen verwendet, während mit  $\infty$  die Signalverläufe für  $t \rightarrow \infty$  künstlich auf '0' gesetzt werden. In der unteren Grafik wird ein NAND-Gatter mit einer Verzögerung von  $\delta = 0.5$  evaluiert.

Der Wave-Simulator verwendet eine GPGPU-gestützte Testmusterkonvertierung und ein schlankes Interface, um den Kommunikationsaufwand zwischen Host-CPU und GPGPU minimal zu halten und die Simulationszeit zu reduzieren. Bei jeder Auswertung können dabei unterschiedliche nominal Schaltzeiten und normalverteilte Variation der Gatterverzögerungen für steigende bzw. fallende Flanken berücksichtigt werden. Eine Puls-Filterung unterdrückt zusätzlich kurz aufeinanderfolgende Signalwechsel.

## 2 SMALLDELAY Fehlermodell

Dieses Kapitel stellt die Ergebnisse einer vorangegangenen Arbeit [Sch11] vor, auf die in dieser Arbeit zurückgegriffen wird. In [Sch11] wurde ein Modell für Verzögerungsfehler in Schaltkreisen entwickelt und der GPGPU-beschleunigte Wave-Zeitsimulator zur Simulation dieser Fehler erweitert. Des Weiteren wurde das POINTER Diagnoseverfahren für Verzögerungsfehler evaluiert und eine Methode vorgeschlagen, um die Diagnose unter Verwendung des Fehlersimulators zu verbessern.

Im Folgenden wird das implementierte Verzögerungsfehlermodell vorgestellt, welches in dieser Arbeit verwendet wird und der Ansatz zur Diagnose vorgestellt.

### 2.1 Hintergrund

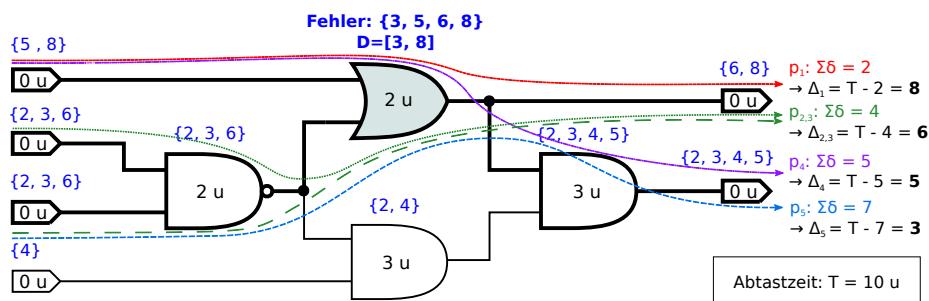

Das in dieser Arbeit verwendete Fehlermodell ist eine verallgemeinerte Variante des Gatterverzögerungsmodells, um kleinste Verzögerungsfehler (sogenannte SMALLDELAYS) zu repräsentieren [Sch11]. Hierbei handelt es sich um ein Einzelfehlermodell, in dem jeder Fehler  $f$  die Verzögerungszeit des assoziierten Gatters um eine Defektgröße  $\delta_f$  erhöht, sodass die Zeitbedingungen eines oder mehrerer Pfade des Schaltkreises **verletzt** werden. Die berechneten Defektgrößen werden hierbei anhand der nominalen Gatterschaltzeiten im Schaltkreis bestimmt und über die *Slacks* der verschiedenen Pfade durch einen Knoten berechnet (siehe Abb. 2.1).

**Abbildung 2.1:** Herleitung einzelner Defektgrößen  $\delta_f$  für einen Knoten im SMALLDELAY-Fehlermodell. – Die Slacks  $\Delta_{p_i}$  eines jeden Pfades  $p_i$  durch den Knoten dienen als mögliche Fehlergrößen.

Der **Slack**  $\Delta_p$  eines Pfades  $p$  ist definiert als die Differenz von Abtastzeit und der kumulativen Verzögerung  $\delta_p$  der einzelnen Gatter von  $p$ . Ist  $\Delta_p > 0$ , so sind die Zeitbedingungen des Pfades erfüllt<sup>1</sup>. Ein SMALLDELAY-Fehler der Größe  $\delta_f$  eines Knoten  $n$  verletzt die Zeitbedingungen aller Pfade  $p$  durch diesen, die eine kumulative Verzögerung von  $T - \delta_f$  oder mehr besitzen, da  $\Delta'_p = \Delta_p - \delta_f = (T - \delta_p) - \delta_f \leq T - T + \delta_f - \delta_f = 0$ . Dadurch hat jeder aus dem Modell hergeleitete Fehler an einem Knoten ein **einzigartiges** Fehlverhalten [Sch11]. Hierbei ist noch zu erwähnen, dass eine Verletzung der Zeitbedingungen entlang eines *sensibilisierten* Pfades nicht zwingend einen Fehler am Ausgang verursachen muss. Durch nicht robuste Signalpropagierung können sogenannte **Hazards** entstehen, die ein Signal über einen *begrenzten* Zeitraum invertieren. Dabei kann es passieren, dass Ausgangssignale, die von einem Hazard betroffen sind, mit einem *guten* Wert abgetastet werden und der Fehler nicht erkannt wird.

Bei einem SMALLDELAY-Fehler wird sich zudem nicht auf eine Polarität der Transitionen beschränkt, wodurch der Fehler einen physischen Defekt modelliert, der sowohl steigende als auch fallende Flanken durch die Defektstelle beeinflusst.

Da die Anzahl der Pfade in einem Schaltkreis im schlimmsten Fall exponentiell mit der Anzahl der Gatter steigen kann [WWW06] und die Initialisierung der vollständigen Fehlermenge aufgrund der hohen Fehlerzahl (siehe Tabelle 4.1 in Kapitel 4) sehr zeitaufwändig ist, wurde in [Sch11] eine Methode vorgeschlagen, um durch **Quantisierung** sogenannter **Defektgrößen-Intervalle** verschiedene Fehlergrößen zu extrahieren. Ein **Defektgrößen-Intervall**  $D_n$  beschränkt hierbei die *relevanten* Defektgrößen eines Knotens  $n$  mit Hilfe des kleinsten detektierbaren Defekts  $\delta_{min}$  und einer Transitionsfehlergröße  $\delta_{max}$ , welche durch den längsten und kürzesten Pfad durch diesen bestimmt sind. Als Transitionsfehlergröße eines Knotens wird hierbei die kleinstmögliche Defektgröße verwendet, die benötigt wird, um die Zeitbedingungen *aller* Pfade durch den Knoten zu verletzen.

## 2.2 Diagnose von Verzögerungsfehlern

### 2.2.1 Critical Path Tracing für Verzögerungsfehler

Ein häufig verwendetes Effect-Cause Verfahren bei der Diagnose kombinatorischer Schaltungen ist das **Critical Path Tracing (CPT)** von [AMM83], welches ursprünglich zur impliziten Fehlersimulation vorgeschlagen wurde und in [GLP92, GLP95] für die Diagnose von Verzögerungsfehlern erweitert worden ist. Im CPT werden für jeden Test die Signale fehlerhafter Ausgänge zu den Eingängen zurückverfolgt, um so die möglichen Fehlerkandidaten in der Schaltung *räumlich* einzuschränken. Dabei wird Anfangs eine Kandidatenliste mit allen Fehlerstellen des Schaltkreises initialisiert. Anschließend wird diese folgendermaßen reduziert:

<sup>1</sup>Signaltransitionen *zum Zeitpunkt der Abtastung* werden hier als eine Verletzung der Zeitbedingungen betrachtet.

| $\wedge$ | C0 | C1 | T0 | T1 | H0 | H1 |

|----------|----|----|----|----|----|----|

| C0       | C1 | C1 | C1 | C1 | C1 | C1 |

| C1       | C1 | C0 | T1 | T0 | H1 | H0 |

| T0       | C1 | T1 | T1 | H1 | H1 | T1 |

| T1       | C1 | T0 | H1 | T0 | H1 | T0 |

| H0       | C1 | H1 | H1 | H1 | H1 | H1 |

| H1       | C1 | H0 | T1 | T0 | H1 | H0 |

**Tabelle 2.1:** Mehrwertige Logik. – Wahrheitstabelle eines NAND-Gatters mit zwei Eingängen für sechswertige Logik.

Für einen fehlerhaften Test wird eine Gutsimulation in **mehrwertiger Logik** durchgeführt, um die Signalpropagierung und die möglichen Transienten für den Test im Schaltkreis sichtbar zu machen. Häufig wird dabei auf eine sechswertige Logik nach [Hay86] zurückgegriffen, die sich zur Analyse von Transienten eignet.

Die Logik verwendet dabei die folgenden Symbole zur Repräsentation von Signalzuständen:

- C0: repräsentiert ein Signal, das über die Zeit konstant auf '0' bleibt. (*stabile '0'*)

- C1: repräsentiert ein Signal, das über die Zeit konstant auf '1' bleibt. (*stabile '1'*)

- T0: repräsentiert ein Signal, das ausgehend von einem initialen Wert '1' nach Stabilisierung den Wert '0' annimmt. (*steigende Transition*)

- T1: repräsentiert ein Signal, das ausgehend von einem initialen Wert '0' nach Stabilisierung den Wert '1' annimmt. (*fallende Transition*)

- H0: repräsentiert ein Signal, das ausgehend von einem initialen Wert '0' mögliche Transitionen haben kann, aber nach Stabilisierung wieder '0' ist. (*statischer 0-Hazard*)

- H1: repräsentiert ein Signal, das ausgehend von einem initialen Wert '1' mögliche Transitionen haben kann, aber nach Stabilisierung wieder '1' ist. (*statischer 1-Hazard*)

In Tabelle 2.1 ist die Wahrheitstabelle des NAND-Gatters aus der  $\mathbb{H}_6$ -Logik illustriert.

Nach der Gutsimulation werden die Signalleitungen und Gatter im Eingangskegel eines jeden fehlerhaften Ausgang im DUD anhand der Netzliste und den Transienten an den Knoten zurückverfolgt. Dabei werden an Gattern nur die Eingänge weiterverfolgt, die *Ereignisse* (z.B. Transitionen oder Hazards) bzw. Signalwechsel für das aktuelle Testmuster aufweisen [GLP92], da Leitungen und Gatter ohne Signalwechsel für den Test keine Verzögerungsfehler propagieren können und diese dadurch nicht zur Erzeugung des Syndroms beitragen. Alle Leitungen und Gatter, die von dem fehlerhaften Ausgang zurückverfolgt werden können, werden dann mit der Liste der verbliebenen Kandidaten *geschnitten*.

Diese Prozedur wird für jeden der zu untersuchenden Tests ausgeführt, um so die Kandidaten stetig reduzieren zu können. Mit der Einzelfehlerannahme befindet sich der gesuchte Kandidat dabei immer unter den verbleibenden Kandidaten, da dieser bei jedem fehlerhaften Test von allen fehlerhaften Ausgängen zurückverfolgt werden können muss. Erweiterungen und Optimierungen für die Rückverfolgung sehen vor, das Backtracing bei *kontrollierten* Gattern auf Gattereingänge mit *kontrollierenden* Ereignissen zu beschränken [GLP95]. Kontrollierende bzw. **dominante Ereignisse** sind Signalverläufe mit kontrollierendem *Finalwert*. Ein Gatter wird als **kontrolliert** bezeichnet, wenn ein oder mehrere Eingänge kontrollierende Ereignisse haben, d.h. sodass Signalwechsel an nicht kontrollierenden Eingängen zu keiner Änderung des Finalwerts am Gatterausgang führen. Die Idee ist hierbei, dass die Fehlerpropagierung von Eingängen mit nicht-dominierenden Ereignissen durch dominierende fehlerfreie Ereignisse maskiert wird, da letztere das Gatter in einen kontrollierten und fehlerfreien Zustand bringen.

### 2.2.2 Weitere Verfahren

Im Folgenden werden weitere Methoden zur Diagnose von Verzögerungsfehlern vorgestellt:

In [TBT98] werden zunächst fehlerhafte Ausgänge im Schaltkreis mit einer Backtracing-Prozedur zurückverfolgt, um eine Menge initialer Fehlerkandidaten zu berechnen. Die Kandidaten werden anschließend mit Hilfe expliziter Simulation von Gatterverzögerungsfehlern in mehrwertiger Logik reduziert. Dabei werden Fehler ausgeschlossen, wenn die Antworten nicht mit dem DUD übereinstimmen. Zusätzlich wird versucht über die Simulation von fehlerfreien Tests weitere verbleibende Kandidaten zu eliminieren.

[WHH02] verwendet sogenannte *Symbolische Fehlerpropagierung* mit mehrwertiger Logik zur Diagnose von Gatterverzögerungsfehlern. Hierbei wird die mögliche Propagierung eines Fehlers ausgehend von einer Fehlerstelle für alle fehlerhaften Testmuster des DUDs beobachtet. Eine Bewertungsfunktion wird dann dazu verwendet, um die Übereinstimmung mit dem DUD zu messen.

Das Verfahren aus [ATH<sup>+</sup>07] wird zur Diagnose kleinster Verzögerungsfehler vorgeschlagen und verwendet neben mehrwertiger Logiksimulation mit Backtracing zusätzlich die Zeit der letzten Transition an einem jeden Knoten. Hierbei werden Fehler mit der kleinsten detektierbaren Defektgröße an den einzelnen Kandidatenstellen für *fehlerhafte* und *fehlerfreie* Tests beobachtet und bewertet.

In [MMSTR08] wird eine initiale Kandidatenmenge durch Backtracing der fehlerhaften Ausgänge berechnet und die möglichen Defektgrößen der Knoten mit Hilfe einer *Zeitsimulation* durch eine Unter- und Oberschranke eingegrenzt. Die Information über die Slacks an *fehlerhaften* und *fehlerfreien* Ausgängen wird dann dazu verwendet die Kandidatenmenge systematisch zu reduzieren.

Die Verfahren aus [RBG<sup>+</sup>07, BGPV10] verwenden mehrwehrtige Logiksimulation und Critical Path Tracing, um die möglichen Fehlerstellen eines DUDs einzuschränken. In einem zweiten Schritt wird für jede Kandidatenstelle eine Menge an möglichen Fehlerarten bestimmt, die anhand der Symbole der Logiksimulation berechnet werden.

[PB07] verwendet sogenannte *Segment Netzwerk Fehler (SNF)* zur Darstellung von Verzögerungsfehlern. Bei der Diagnose werden nach einem konservativen Backconing alle verbleibende Kandidatenstellen mit einer ‚X‘-Propagierung simuliert, um die Fehlerpropagierung ausgehend von den Stellen zu beobachten und eine Fehlersignatur zu bestimmen. Die Signaturen dieser Fehler werden dann zu einem  *Fehler-Cluster-Graphen* zusammengesetzt und analysiert, um passende SNFs zu extrahieren.

In [YB08, YB10] wurde ein Verfahren zur Diagnose von Mehrfachfehlern vorgestellt. Hierbei wird nach einem Backtracing an den verbliebenen Kandidaten ‚X‘-Markierungen injiziert, die zu den Ausgängen propagiert werden. Anschließend werden durch eine konservative Rückwärtsimulation ausgehend von fehlerfreien Ausgängen weitere Fehlerkandidaten ausgeschlossen.

Ein statistischer Ansatz zur Diagnose von Verzögerungsfehlern wurde in [KWCL03] präsentiert. Hierbei werden *statistische statische Zeit-Analyse (SSTA)* und *dynamische Zeitsimulation* verwendet, um über die Fehlerwahrscheinlichkeiten der Ausgänge die statistische Übereinstimmung von Kandidaten zu berechnen und zu vergleichen.

Die meisten der vorgestellten Methoden verwenden ein mehrstufiges Diagnoseverfahren und nutzen dabei das Backtracing von fehlerhafter Ausgänge, um die initiale Kandidatenmenge einzuschränken. Insbesondere bei den simulationsbasierten Ansätzen kann der Aufwand durch die Vorarbeit stark verringert werden, da Fehlersimulation je nach Modell sehr teuer werden kann. Nur wenige der Diagnoseverfahren verwenden dabei jedoch die Zeitdaten der Schaltungen. Zudem wird oftmals die Information über fehlerhafte *und* fehlerfreie Ausgänge verwendet, um Kandidaten auszuschließen. Hierbei werden leider keine dynamischen Hazards in den Signalverläufen berücksichtigt, was z.B. bei nicht-robuster Fehlerpropagierung in die Irre führen kann. Simulationsbasierte Ansätze mit Auswertung der Signalverläufe durch explizite Zeitsimulation sind dem Autor nicht bekannt.

## 2.3 POINTER Diagnose mit Resimulation

Um das POINTER-Verfahren für SMALLDELAY-Fehler zu beobachten und auszuwerten, wurde der parallele Fehlersimulator in [Sch11] zunächst dazu genutzt, um fehlerhafte Testantworten von DUDs zu generieren. Mit Hilfe von einer Fehlermaschine zur Simulation von einzelnen Haftfehlern wurde das Syndrom eines DUDs ausgewertet. Da SMALLDELAY-Fehler an einem Gatter zwar unabhängig von der Polarität der Transitionen aktiviert werden können, aber die Aktivierung der Haftfehler vom aktuellen Signalwert abhängig ist, hatten sich die Evidenzen des Fehlers auf die jeweiligen Haftfehler-Repräsentanten (*StuckAt-0*, *StuckAt-1*) am Knoten

**Abbildung 2.2:** Beispiel eines Verzögerungsfehlers, der aufgrund von nicht robuster Signalpropagation für das Testmuster nicht durch den Haftfehler-Repräsentanten am Gatter ersetzt werden kann.

aufgeteilt. In Abhängigkeit der Häufigkeit der Polarität bei fehleraktivierenden Transitionen, hatte sich hierbei gezeigt, dass die Evidenzen *einzelner* Haftfehler nicht zur Diagnose geeignet sind. Deswegen wurden die Evidenzen der Haftfehler-Repräsentanten eines Gatters durch komponentenweises addieren in sogenannte **Lokationsevidenzen** zusammengefasst [Sch11].

Da Haftfehler unabhängig von einer Defektgröße sind und ohne Transitionen aktiviert werden, haben die Lokationsevidenzen sehr viele Fehlvorhersagen produziert. Solche Haftfehler, die näher an den Ausgängen waren und kleinere Ausgangskegel hatten, wurden typischerweise besser bewertet als jene, die im Eingangsbereich lagen, wodurch diese bei kleineren Verzögerungsfehlern irreführende Ergebnisse lieferten. Weil SMALLDELAY-Fehler an einem Knoten in Abhängigkeit der Defektgröße oftmals nur einen bestimmten Anteil aller sensibilisierten Pfade durch diesen verletzen, ist häufig der Fall aufgetreten, dass  $\sigma_{f,\pi} > 0$  und  $\iota_{f,\pi} > 0$ , wodurch  $\gamma_{f,\pi} > 0$ . Aus diesem Grund musste die **Bewertungsfunktion** der Evidenzen auf **Sigma-Iota-Gamma** geändert werden, da sehr viele falsche bzw. unlogische Fehler (z.B.  $\sigma_f = 0 \Rightarrow \gamma_f = 0$ ) besser gewichtet worden sind und die eigentlichen Kandidaten sehr weit von den ersten Rängen verdrängt hatten [Sch11].

Bei der sogenannten **Resimulation** wurden die Fehlerstellen der sortierten und bewerteten Lokationsevidenzen mit Hilfe des Zeitsimulators nachsimuliert, um das Verhalten von Verzögerungsfehlern an den Kandidatenstellen zum Abtastzeitpunkt zu beobachten. Aus Gründen der Performance wurde dabei für eine beschränkte Anzahl an Knoten (die besten 25 berichteten Fehlerstellen) jeweils der Transitionsfehler und die mittlere Defektgröße des Defektgrößen-Intervalls simuliert. Dabei konnte mit der Resimulation eine Verbesserung der Diagnoseergebnisse erzielt werden [Sch11].

## 2.4 Neuer Ansatz

Das in dieser Arbeit präsentierte Verfahren setzt gänzlich auf SMALLDELAY-Referenzfehler und wendet sich damit von der Haftfehlersimulation ab, da Haftfehler die Verzögerungsfehler

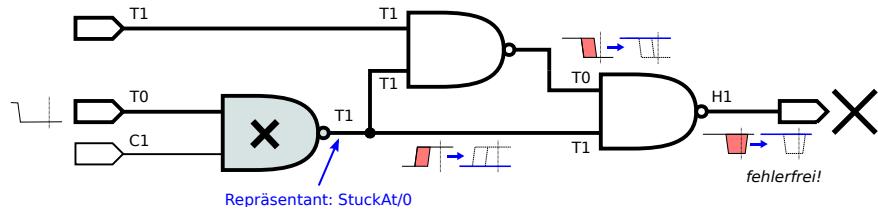

Abbildung 2.3: Übersicht des zweistufigen Diagnoseansatzes.

nicht in einem ausreichenden Maß repräsentieren können. Dies ist an einem Beispiel in Abbildung 2.2 illustriert. Hier produziert ein Verzögerungsfehler für eine steigende Transition einen fehlerhaften Ausgang. Da sich die Fehlerpropagierung am folgenden Verzweigungsstamm auf zwei Pfade verteilt und diese später (mit umgekehrter Polarität) rekonvergieren, ist das Ausgangssignal nur für einen kurzen Moment als Hazard sichtbar. Der zugehörige Haftfehler-Repräsentant (*StuckAt-0*) kann dieses Symptom jedoch nicht reproduzieren, da dieser das Ausgangsgatter konstant auf einem kontrollierten Wert hält. Für das Ausgangsgatter findet sich hier jedoch ein Haftfehler (*StuckAt-1*) um das Symptom zu reproduzieren, wodurch dieser nun besser bewertet wird als der eigentliche Kandidat.

Um die Simulation der SMALLDELAYS effizient zu gestalten, soll dabei zunächst die Menge der logischen Kandidaten eingeschränkt werden. Als nächsten Schritt sollen in **selektiven Verfahren** die zu simulierenden Kandidaten *adaptiv* anhand des Evidenzverhaltens bestimmt werden, um die Zahl der Simulationen gering zu halten.

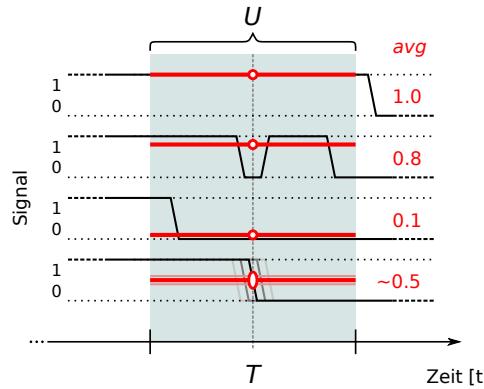

Ein weiteres Problem beim Vergleichen von Referenzfehler-Antworten mit dem Syndrom eines DUDs entsteht, wenn eine hohe **Dynamik** in den Ausgangssignalen vorliegt. So können dann bereits kleinste Abweichungen im Abtastzeitpunkt zwischen *fehlerhaft* und *fehlerfrei* unterscheiden. Insbesondere führen Variationen der Gatterverzögerungen dazu, dass das Fehlermodell das Verhalten des Defekts im DUD nicht mehr akkurat nachahmen kann, wodurch ein direkter Vergleich zusätzlich erschwert wird. Da der verwendete Zeitsimulator die Signalverläufe im Schaltkreis präzise modellieren kann, sollen diese genauer untersucht werden, um Aufschluss über die Stabilität von Ausgangssignalen zu geben und diese in die Bewertung von Kandidaten mit einfließen zu lassen.

# 3 Adaptive simulationsbasierte Diagnose

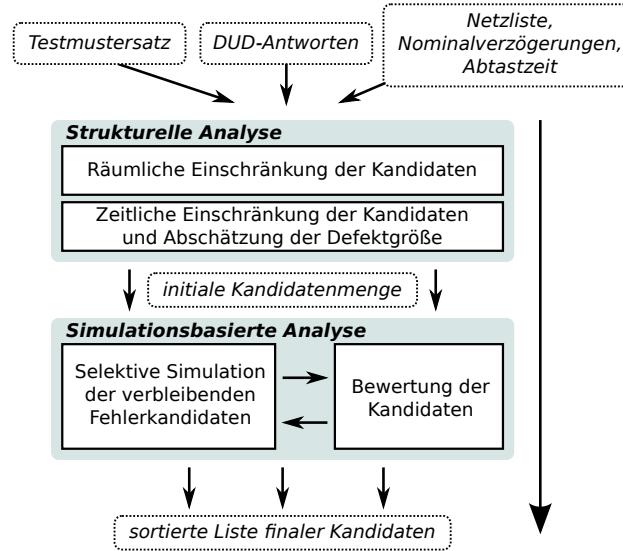

Dieses Kapitel beschreibt ein Verfahren zur Diagnose von Verzögerungsfehlern, das anhand der Testantworten des zu diagnostizierenden Chips (DUDs) sowohl die Defektstelle einzelner SMALLDELAY-Fehler lokalisieren als auch die Defektgröße bestimmen kann. Aufgrund der Komplexität des Verzögerungsfehlermodells, wurde das Verfahren aus zwei Teilen zusammengesetzt: Einer *strukturellen* und einer *simulationsbasierten* Analyse.

Der erste Abschnitt dieses Kapitels befasst sich mit der **strukturellen Analyse**. Hierbei werden fehlermodellunabhängige *Effect-Cause*-Methoden zur *räumlichen*, sowie *zeitlichen* Einschränkung der möglichen initialen Fehlerkandidaten eingesetzt und eine erste Abschätzung der Defektgröße durchgeführt.

Der zweite Teil beschreibt die **simulationsbasierte Analyse**. Dabei wird eine neuartige *Cause-Effect*-Methode vorgestellt, die mit Hilfe expliziter Simulation von SMALLDELAY-Fehlern die verbleibenden Kandidaten genauer untersucht. Die zu simulierenden Fehler werden dabei *adaptiv* bestimmt, um die Gesamtzahl der Simulationen zu begrenzen.

Im dritten Teil wird ein Verfahren zur **Bewertung** der Fehlerkandidaten eingeführt, welches die Stabilität in den Ausgangssignalen mit berücksichtigt und die Diagnoseresultate im Falle von Variationen im Schaltkreis verbessert.

## 3.1 Strukturelle Analyse

Die Anzahl der möglichen SMALLDELAY-Fehler in einem Schaltkreis hängt von der Zahl der Pfade ab [Sch11] und kann im schlimmsten Fall *exponentiell* mit der Gatterzahl  $N$  steigen, weshalb eine erschöpfende Fehler-Simulation zur Diagnose mit allen Kandidaten praktisch nicht durchsetzbar ist [WWW06]. Da industrielle Schaltkreise — insbesondere *Full-Scan*-Designs — typischerweise kurze Pfade und kleine Kegel besitzen, haben Verzögerungsfehler an einem Gatter meist jedoch nur auf einen relativ kleinen Bereich der Schaltung Einfluss. Dadurch sind Fehler häufig nur an einer kleinen Anzahl von Ausgängen sichtbar. Umgekehrt lässt sich die Fehlerquelle anhand der fehlerhaften Ausgänge ebenso auf einen Bereich der Schaltung *räumlich* eingrenzen. Fehlerkandidaten, die sich außerhalb dieser Bereiche befinden, können ohne explizites Überprüfen durch Fehlerimulation von den Untersuchungen ausgeschlossen werden. Die strukturellen Analyse hat nun als Aufgabe diese Bereiche zu identifizieren. Als Ausgangspunkt dienen dabei die jeweiligen Testantworten der zu diagnostizierenden Chips.

### 3.1.1 Räumliche Einschränkung der Kandidaten

Damit eine Fehlerstelle zur Menge der potentiellen Kandidaten angehören kann, müssen bei dem Knoten die folgenden beiden Punkte für *jeden* fehlerhaften Ausgang der Testmuster erfüllt sein:

**Fehler-Aktivierung** Es kommen nur solche Knoten als Kandidaten in Frage, die bei *allen* fehlerhaften Verzögerungstests mindestens eine Transition im Signalverlauf aufweisen.

**Fehler-Propagierung** Ausgehend von der Defektstelle der Kandidaten, müssen bei aktiviertem Fehler die Transitionen an der Fehlerstelle zu *jedem* betroffenen Ausgang des fehlerhaften Tests propagieren können.

Alle Knoten, die mindestens einmal gegen diese Bedingungen verstößen, können von den Kandidaten logisch ausgeschlossen werden. Um die Bedingungen zu überprüfen, wurde das in Abschnitt 2.2.1 vorgestellte *Critical Path Tracing* für Verzögerungsfehler [GLP95] gewählt.

#### Critical Path Tracing

Das implementierte Critical Path Tracing (CPT) beruht auf Grundversion von [GLP95]. Ausgehend von einer Logiksimulation der fehlerhaften Verzögerungstests in sechswertiger Logik [Hay86], werden die fehlerhaften Ausgänge des DUDs über die sensibilisierten Leitungen in der Schaltung bis zu den Eingängen verfolgt und markiert. Von jeden fehlerhaften Ausgang eines jeden Testmusters werden die Gatter mit möglichen Transienten (T0, T1, H0, H1) in einer Backtracing-Iteration traversiert. Im Rahmen einer Optimierung aus [GLP95] werden dabei Signale mit **dominierenden** Ereignissen bevorzugt, d.h. wenn ein Gatter an den Eingängen sowohl dominierende als auch nicht-dominierende Ereignisse aufweist, dann wird das Backtracing nur an den jeweiligen *dominierenden* Eingängen fortgesetzt.

Nach der Rückverfolgung eines fehlerhaften Ausgangs werden die markierten Gatter in einer Liste  $S_i$  zusammengefasst und mit den verbleibenden Kandidaten *geschnitten*, um eine initiale Kandidaten-Liste  $S$  ( $= \cap S_i$ ) zu erhalten. Jeder dieser Kandidaten  $s \in S$  erfüllt dabei die Aktivierungs- und Propagierungsbedingungen für das Syndrom des DUDs, während die Gatter aus  $V \setminus S$  gegen mindestens eine dieser Bedingungen verstößen haben.

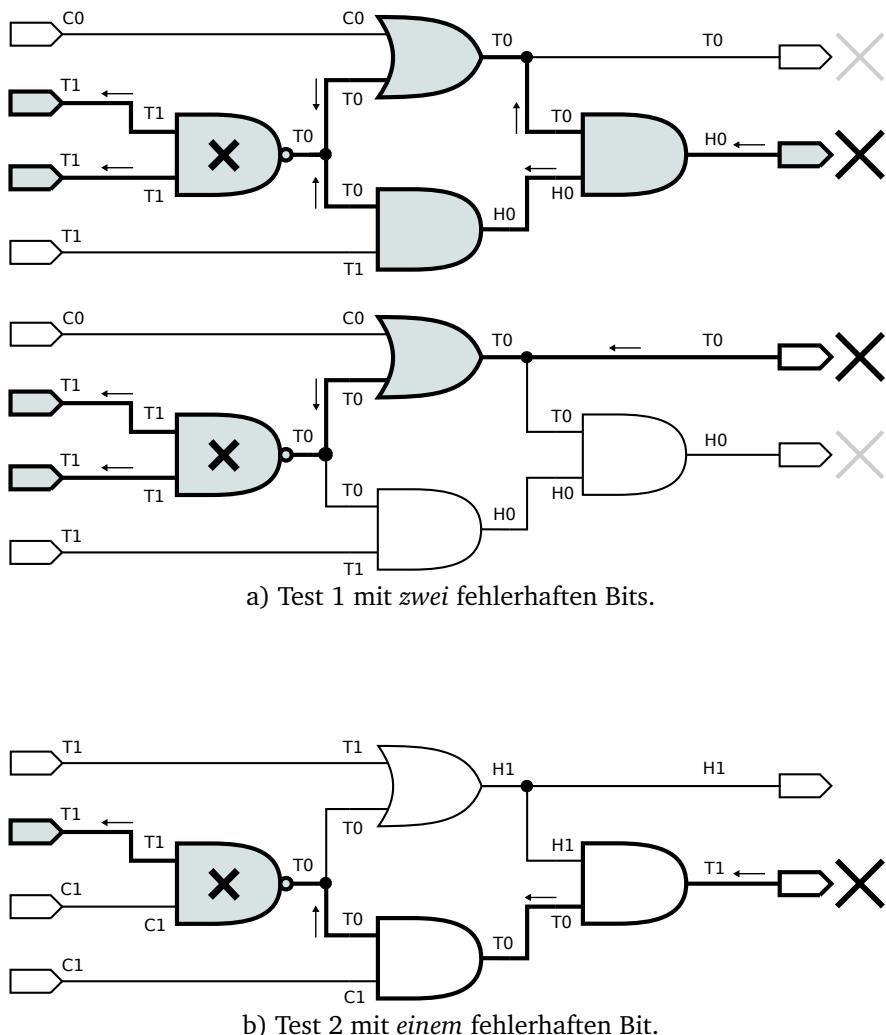

In Abbildung 3.1 ist das Critical Path Tracing an einem Beispiel illustriert. Hier wurde das CPT auf zwei Verzögerungstests angewendet. Dicken Linien markieren die Teile der Schaltung, die beim Backtracing zurückverfolgt werden konnten. Beim ersten Verzögerungstest (1-2) muss die Prozedur für jeden der beiden fehlerhaften Ausgänge separat aufgerufen werden. Nach Rückverfolgung des zweiten Tests (3) reduziert sich die logische Kandidatenmenge auf zwei Stellen. Alle verbleibenden Kandidaten nach einem Schritt sind schattiert dargestellt.

**Abbildung 3.1:** Einfaches *Critical Path Tracing* am Beispiel mit zwei fehlerhaften Verzögerungstests. – Das defekte Gatter ist mit einem ‚X‘ markiert. Die Symbole der Logiksimulation vom untersuchten Test sind an den Leitungen dargestellt.

## Kollabierung struktureller Äquivalenzen

Verzögerungsfehler an unterschiedlichen Gattern in einem Schaltkreis können für einen Test oder einen ganzen Testmustersatz ein identisches Syndrom verursachen und sich dadurch *äquivalent* verhalten. Dies kann dabei mehrere Ursachen haben:

- Der Testmustersatz kann die Fehler nicht weiter unterscheiden, weil der Fehlereffekt z.B. aufgrund blockierender Seitenpfade nicht an alle Ausgänge propagiert werden kann.

- Die Gatter und deren assoziierte Fehler sind *strukturell äquivalent* und produzieren für **alle** Testmuster ein identisches Syndrom.

Im ersten Fall können die Äquivalenzen aufgelöst werden, indem man versucht die Fehlerinformation, die von einer möglichen Fehler-Stelle aus propagiert wird, zu maximieren. Hierbei könnte man mit Hilfe von **ATPG-Tools (Automatic Test Pattern Generation)** einen geeigneten Testmustersatz erzeugen, der Transitionen über alle möglichen Pfade durch die Gatter verschickt und so ein vollständiges Bild des Fehlerausmaßes erzeugt. In der Praxis ist dies aber aufgrund der hohen Anzahl an möglichen Pfaden im Schaltkreis nicht durchführbar.

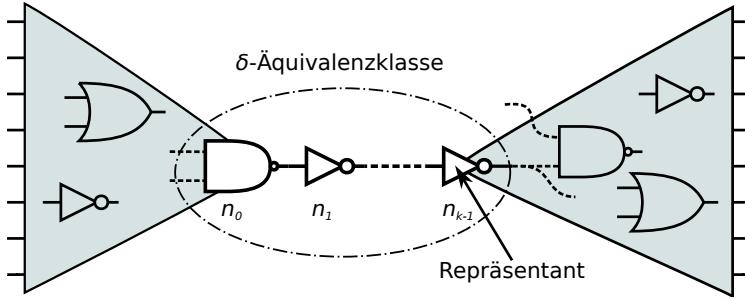

Im Fall einer **strukturellen Äquivalenz** lässt sich die Fehlerinformation dagegen nicht durch die Wahl eines anderen Testmustersatzes verbessern. Fehler mit fester Defektgröße können an diesen Gattern aufgrund des äquivalenten Verhaltens nicht unterschieden werden, wodurch die diagnostische Auflösung *beschränkt* wird. Deshalb werden die im Anschluss an das Critical Path Tracing verbleibenden Fehlerkandidaten von strukturell äquivalenten Knoten in *Äquivalenzklassen* eingeteilt, sodass der Diagnosealgorithmus die Symptome eines DUDs nun zu bestimmten Fehlerklassen zuordnen kann. Die Gatter der *Äquivalenzklassen* werden für **SMALLDELAYS** dabei gemäß einem Vorschlag aus [Sch11] zusammengefasst, der auf einer Methode aus [WLRI87] zur Bestimmung der strukturellen Äquivalenzen bei Transitionenfehlern basiert. Hierfür werden die folgenden Regeln verwendet:

- (R1) Sei  $n$  ein Gatter mit einem einzigen Fanout  $g$ . Dann sind  $n$  und  $g$  *strukturell äquivalent*, wenn  $g$  einen einzigen Eingang hat.

- (R2) Seien  $n$  und  $g$  bzw.  $g$  und  $h$  strukturell äquivalent, dann sind  $n$  und  $h$  ebenfalls strukturell äquivalent (*Transitivität*).

Mit  $g$  als einzigm Nachfolger von  $n$  sind die beiden Gatter Teil eines Fanout-freien Bereichs. Da  $g$  keine zusätzlichen *Nebenpfade* (Off-Path Signale) hat, ist die Menge an Paden durch den Knoten  $n$  identisch mit denen durch  $g$ , wodurch alle injizierten **SMALLDELAY**-Fehler dieselben Aktivierungs- und Propagierungsbedingungen haben. Dabei bleibt auch die Puls-Filterung der Signale entlang der Kette konsistent, sodass das Verhalten von Fehlern gleicher Größe an  $n$  und  $g$  identisch ist. Die Gatter können somit durch keinen Verzögerungstest unterschieden werden und sind deshalb *strukturell äquivalent* (R1). Mit Hilfe der *transitiven* Eigenschaft (R2) werden die strukturell äquivalenten Gatter nun folgendermaßen in Äquivalenzklassen eingeteilt:

**Abbildung 3.2:** Strukturelle Äquivalenz. – Kollabierung einer  $\delta$ -Äquivalenzklasse zu einem Repräsentanten.

**Definition 3.1 ( $\delta$ -Äquivalenzklasse).** Sei  $H \subseteq G$  ein verbundener Graph bestehend aus einer Kette von  $k$  strukturell äquivalenten Gattern  $n_0, n_1, \dots, n_{k-1}$ . Ist  $H$  maximal und gemäß den vorigen Regeln, dann bilden die Knoten von  $H$  eine  $\delta$ -Äquivalenzklasse.

Die Gatter der Äquivalenzklassen und deren assoziierte Fehler werden nun zu einzelnen **Repräsentanten** reduziert (*Fault-Collapsing*), die das Verhalten der Fehler in ihrer Klasse wider-spiegeln. Als **Repräsentant** wurde das vorderste Glied der Kette einer jeden Äquivalenzklasse gewählt. Einzelne Gatter, die nicht nach Definition 3.1 in Gruppen zusammengefasst werden konnten, bilden jeweils eigenständige Klassen. Die Beschränkung der CPT Kandidaten auf die Repräsentanten von Äquivalenzklassen verringert dabei den *Aufwand* weiterer logischer Diagnose-Verfahren. Falls die logische Diagnose zur Steuerung einer physischen Untersuchung (z.B. mit dem Elektronenraster-Mikroskop) verwendet werden soll, so müssen die einzelnen Fehlerstellen der Äquivalenzklassen dennoch explizit untersucht werden, um die defekte Stelle auszumachen. Abbildung 3.2 illustriert das Schema einer Kollabierung von strukturell äquivalenten Gattern und zeigt die Äquivalenzklasse mit dem dazugehörigen Repräsentanten.

### 3.1.2 Zeitliche Einschränkung der Kandidaten

Mit dem Critical Path Tracing und der Kollabierung von strukturellen Äquivalenzen können die initialen Fehler-Kandidaten eines Schaltkreises *räumlich* reduziert werden. Da SMALLDELAYS mit ihrer individuellen Verzögerung auch eine Zeitkomponente besitzen, kann es vorkommen, dass manche Symptome aufgrund bestimmter Pfadlängen bei der Signalpropagierung nur für bestimmte Defektgrößen an den verbleibenden Knoten sichtbar sind. Dadurch kann zusätzlich eine globale **zeitliche** Abschätzung der Defekte *aller* Knoten durch Eingrenzung der DUD-Fehlergröße  $\delta_f$  mit Hilfe einer Unter- ( $LB$ ) und einer Obergrenze ( $UB$ ) durchgeführt werden, sodass  $\delta_f \in [LB, UB]$ . Des Weiteren kann die Fehlerinformation dazu verwendet werden, um eine erste Abschätzung der Defektgröße zu gewinnen.

### Bestimmung einer Untergrenze

Zur Bestimmung einer **Defekt-Untergrenze** wird die *minimale* ( $EA$ ) und *maximale* ( $LS$ ) kumulative Signal-Propagierungszeit von den Eingängen bis zu den Knoten durch den Schaltkreis propagiert [Sch11]. Die Zeiten errechnen sich über die Nominalschaltzeiten der jeweiligen Gatter: Sei  $n \in V$  ein Gatter mit einer Nominalverzögerung von  $\delta$ , dann gilt

$$EA(n) = \min_{i \in \text{FanIn}(n)} (EA(i)) + \delta \quad \text{und} \quad LS(n) = \max_{i \in \text{FanIn}(n)} (LS(i)) + \delta.$$

Die Eingänge  $i \in I \subseteq V$  des Schaltkreises werden mit  $EA(i) = 0$  und  $LS(i) = 0$  initialisiert. An einem Schaltungsausgang  $o \in O \subseteq V$  kann man aus den Zeiten  $EA(o)$  und  $LS(o)$  die kumulative Verzögerung des längsten bzw. kürzesten Pfades von den Schaltungseingängen bis Ausgang  $o$  ableiten. Mit Hilfe der **Slacks**  $\Delta_{\min}^T = T - LS(o)$  bzw.  $\Delta_{\max}^T = T - EA(o)$  dieser Pfade lässt sich dabei ein Defektgrößen-Intervall für den Ausgang  $o$  bestimmen [Sch11]:

$$D_o = [\Delta_{\min}^T, \Delta_{\max}^T].$$

Das **Defekt-Intervall**  $D_o$  vereint alle *relevanten* Defektgrößen eines Ausgangs  $o$ . So gibt  $\min(D_o)$  die untere Schranke der detektierbaren Defektgrößen an. Defekte mit einer Verzögerung  $\delta_f < \min(D_o)$  werden am Ausgang nicht erkannt, und müssen deswegen nicht weiter betrachtet werden. Die obere Schranke  $\max(D_o)$  repräsentiert dagegen die kleinstmögliche Transitionsfehler-Größe an diesem Ausgang. Da jeder Transitionsfehler bereits den schlimmsten Fall eines Verzögerungsfehlers an einem Gatter modelliert, brauchen die Defekte  $\delta_f > \max(D_o)$  im variationsfreien Fall ebenfalls nicht weiter betrachtet zu werden. Die Berechnung der Propagierungszeiten wird einmalig und mit einem Aufwand von  $\mathcal{O}(N)$  durchgeführt.

**Lemma 3.1.1.** *Um die effektive Defekt-Untergrenze  $LB$  eines Fehlers anhand der fehlerhaften Ausgänge  $O_f$  zu bestimmen, wird im Folgenden die größte untere Schranke der Defekt-Intervalle  $D_o$  aller Ausgänge  $o \in O_f$  berechnet:*

$$LB = \min(\cap_{o \in O_f} \{D_o\}) = \max(\{\min(D_o) : o \in O_f\}).$$

*Dadurch ist sichergestellt, dass die Zeitbedingung von **mindestens** einem Pfad durch einen jeden Ausgang verletzt ist.*

*Beweis.* Sei  $LB = \max(\{\min(D_o) : o \in O_f\})$ . Dann gibt es einen Ausgang  $o \in O_f$ , an dem ein längster Pfad  $p$  mit einem Slack  $\Delta_{\min}^T = LB$  endet. Nimmt man nun an, es existiere eine kleinere Schranke  $LB' = LB - \epsilon$  für ein  $\epsilon > 0$ , dann ist die Slack-Differenz des längsten Pfades durch  $o$  und der neuen Schranke  $LB'$  gegeben mit  $\Delta_{\min}^T - \Delta_{LB'}^T = LB - LB' = \epsilon > 0$ . Daraus folgt  $o \notin O_f$  und ein Widerspruch.  $\square$

**Beispiel 3.1.** Seien  $D_{o_1} = [3, 5]$  und  $D_{o_2} = [1, 6]$  die Defekt-Intervalle zweier fehlerhafter Ausgänge  $o_1, o_2 \in O_f$ . Dann ist  $LB = \max(\{\min([3, 5]), \min([1, 6])\}) = \max(\{3, 1\}) = 3$  die Mindestdefektgröße, die benötigt wird, um das Zeitverhalten von  $o_1$  und  $o_2$  zu verletzen.

Für den variationsfreien Fall repräsentiert die hergeleitete Schranke  $LB$  immer eine **gültige** Untergrenze, mit der die Fehlermenge an den verbleibenden Gatter-Kandidaten zeitlich eingegrenzt werden kann.

### Bestimmung einer Obergrenze

In [MMSTR08] werden die fehlerfreien Antworten dazu genutzt, um Aussagen über eine mögliche **Obergrenze** zu machen. Hierbei wird angenommen, dass Defekte, die einen Fehler über einen Pfad zu einem Ausgang  $o \in O$  propagieren können, nicht groß genug sind, wenn  $o$  bei der Abtastung einen fehlerfreien Wert aufweist. Bei genauerer Betrachtung können **Glitches** und **Hazards** an den Schaltungsausgängen dabei jedoch einen *falschen Eindruck* verbreiten, wenn die Signale zum Zeitpunkt  $T$  der Abtastung einen gutartigen Wert besitzen. Als Konsequenz würde die Defekt-Obergrenze somit *unterschätzt* werden, wodurch der eigentliche Fehlerkandidat aus der Kandidatenmenge entfällt. Aus diesem Grund wurde in dieser Arbeit auf eine obere Beschränkung der Defektgröße durch fehlerfreie Antworten verzichtet.

Die Obergrenze  $UB$  wird deshalb mit der größten aller *kleinsten* Transitionsfehlergrößen  $UB = \max(\cup_{o \in O_f} D_o)$  abgeschätzt, wodurch sichergestellt ist, dass alle betroffenen Ausgänge verletzt werden können und größere Defekte keine Änderungen am Syndrom verursachen.

### Erste Abschätzung der Defektgröße

Um die Defektgröße in einer ersten Instanz *genauer* zu approximieren, wird mit dem Zeitsimulator zunächst eine **Gutsimulation** der Testmustermenge  $\Pi$  durchgeführt. Anschließend extrahiert man für jeden fehlerhaften Ausgang  $o \in O_f$  eines fehlerhaften Verzögerungstests  $\pi \in \Pi$  die **Stabilisierungszeit**  $LS(o, \pi)$  im fehlerfreien Fall. Die **Stabilisierungszeit** eines Ausgangs gibt dabei den Zeitpunkt der letzten Transition im Signalverlauf an.

Mit Hilfe der Abtastzeit  $T$  kann man den **Slack**  $\Delta^T(o) = T - LS(o, \pi)$  am Schaltungsausgang  $o \in O_f$  eines fehlerhaften Verzögerungstests  $\pi$  berechnen und erhält somit eine mögliche Defektgröße, die zur Verletzung der Zeitbedingungen an  $o$  verwendet werden kann. Hierbei wird angenommen, dass die Zeitbedingungen an einem Knoten verletzt sind, sobald der Slack  $\Delta^T(o) \leq 0$  ist. Da die Zeitbedingung eines jeden fehlerhaften Ausgangs  $o \in O_f$  notwendigerweise verletzt sein **muss**, wird das **Maximum** der berechneten Slacks zur Abschätzung der möglichen Defektgröße  $\delta_{est}$  genommen:

$$\delta_{est} = \max(\{\Delta^T(o) : o \in O_f\}).$$

Je nachdem, über welche Pfade die Verzögerungstests die Transitionen durch den Schaltkreis propagieren, können die Stabilisierungszeiten der Signale und die daraus resultierenden Slacks *variieren*.

Aufgrund der Berücksichtigung der Signalpropagierung in der Zeitsimulation kann die abgeschätzte Defektgröße  $\delta_{est}$  die echte Defektgröße  $\delta_f$  insbesondere bei *robusten* Verzögerungstests relativ gut approximieren.

Falls die Stabilisierungszeiten an einem Ausgang durch einen Pfad bestimmt ist, der nicht durch die Fehlerstelle führt, ist es möglich, dass  $\delta_f$  **unterschätzt** wird. Das tritt hauptsächlich dann auf, wenn der Seiten-Pfad eine größere Propagierungszeit hat, als der Pfad durch die Fehlerstelle. Das Unterschätzen ist aber nicht weiter schlimm, da  $\delta_{est}$  in diesem Fall immer noch eine gültige Untergrenze ist.

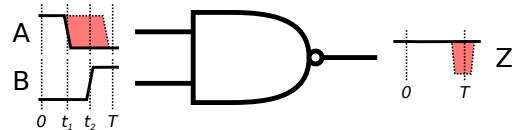

**Abbildung 3.3:** Überschätzung der Defektgröße durch blockierte Transitionen in der Zeitsimulation. Das Ausgangssignal ist hier konstant, wodurch  $\delta_{est} = T$ .

Bei *nicht-robuster* Signalpropagierung kann die Defektgröße durch Zeitsimulation allerdings auch **überschätzt** werden. Dies ist in Abbildung 3.3 am Beispiel eines NAND-Gatters zu sehen. Während der Gutsimulation erreicht das Eingangssignal A einen kontrollierenden Zustand zur Zeit  $t_1 > 0$ , noch bevor B diesen bei  $t_2 > t_1$  verlässt. Die Propagierung der Transitionen wird *maskiert*, wodurch der Gatterausgang auf einem konstant kontrollierten Wert bleibt. Die Stabilisierungszeit von Z ist aufgrund der fehlender Transitionen gleich null und es ergibt sich eine Untergrenze von  $\delta_{est} = T$ . Da jedoch  $t_1 > 0$  und der tatsächliche Defekt  $\delta_f$  somit auch eine Größe von  $\delta_f = T - t_1$  haben kann, würde dieser Defekt bei der Begrenzung der Kandidaten ausgeschlossen werden, da  $\delta_f < \delta_{est}$ . Aus diesem Grund ist  $\delta_{est}$  **keine** gültige Untergrenze und eignet sich deshalb nicht zur Einschränkung der Kandidatenmenge.

## 3.2 Simulationsbasierte Analyse

Nachdem die initialen Fehler-Kandidaten durch die strukturelle Analyse räumlich und zeitlich reduziert worden sind, werden nun die verbleibenden Fehlerstellen durch explizite Fehlersimulation genauer untersucht, um so den eigentlichen Defekt lokalisieren zu können.

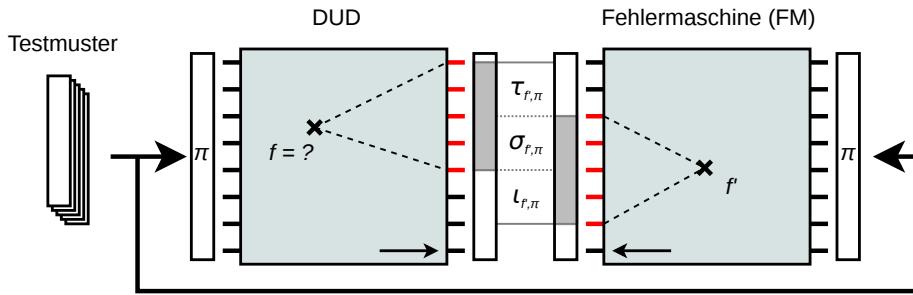

**Abbildung 3.4:** Berechnung der Evidenz-Komponenten ( $\sigma_{f',\pi}$ ,  $\tau_{f',\pi}$  und  $\mathcal{I}_{f',\pi}$ ) eines Referenzfehlers  $f'$  für ein Testmuster  $\pi$  durch Vergleich der fehlerhaften Ausgänge.

### 3.2.1 Aufbau

Abbildung 3.4 zeigt den allgemeinen Aufbau der simulationsbasierten Analyse. Hierbei wird ein Antwortmuster des zu diagnostizierenden Chips (DUD) mit denen der von einer **Fehlermaschine (FM)** simulierten Referenzfehler verglichen. Die FM ist hier ein Zeitsimulator, der einzelne SMALLDELAY-Fehler in die Schaltung injizieren und diese mit Hilfe der Signalverläufe (Waveforms) präzise an beliebigen Zeitpunkten evaluieren kann.

Für jeden Verzögerungstest  $\pi$  werden beim Vergleichen der Antworten eines Referenzfehlers  $f$  aus der Kandidatenmenge anhand die fehlerhaften Bits von DUD und FM sogenannte *Evidenzen*  $e(f, \pi)$  berechnet. Evidenzen sind Tupel, die sich aus den Komponenten  $\sigma_{f,\pi}$ ,  $\tau_{f,\pi}$ , sowie  $\mathcal{I}_{f,\pi}$  zusammensetzen (vgl. [HW07]). Durch komponentenweises Addieren der  $e(f, \pi)$  eines jeden Testmusters  $\pi \in \Pi$ , erhält man die *globale* Evidenz  $e(f, \Pi)$  des Referenzfehlers  $f$  für den gesamten Testmustersatz. Nach Simulation aller Referenzfehler werden die globalen Evidenzen mit Hilfe einer Funktion bewertet, um so eine sortierte Liste von Kandidaten zu erhalten, die den Defekt im DUD am besten erklären können.

### 3.2.2 Adaptive Simulation

Nach der strukturellen Analyse kann die Zahl der möglichen Fehlerkandidaten immer noch sehr groß sein. Diese hängt dabei sowohl von der Menge der verbleibenden Fehlerstellen  $S$  nach dem Critical Path Tracing, als auch von der Zahl der verschiedenen zu untersuchenden Defektgrößen an jedem Knoten ab. Bei der Fehlergenierierung im SMALLDELAY-Fehlermodell sind die einzelnen Defektgrößen eines Knoten durch die Menge der unterschiedlich langen Pfade durch diesen bestimmt [Sch11]. Jeder im Fehlermodell generierte Defekt eines Knotens verletzt dabei in Abhängigkeit der assoziierten Defektgröße  $\delta$  die Zeitbedingungen aller Pfade mit der Länge größer oder gleich  $T - \delta$ .

Sei nun  $k$  die gemittelte Anzahl an verschiedenen langen Pfaden durch die Knoten in  $G$ , dann existieren durchschnittlich  $k$  verschiedene SMALLDELAY-Fehler für einen jeden Knoten im Modell, womit die Gesamtzahl der zu simulierenden Fehler mit  $\mathcal{O}(k \cdot |S|)$  abgeschätzt werden kann. Da Fehlersimulation mit dem Zeitsimulator ein sehr aufwändiger Prozess ist und  $k$  in der Regel sehr groß ist, wäre ein simulationsbasierter Ansatz mit der vollständigen verbliebenen Kandidatenmenge  $S$  aus den  $\mathcal{O}(k \cdot |S|)$  Fehlern somit immer noch sehr kostspielig. Aus diesem Grund muss die Zahl der Simulationen noch weiter gesenkt werden.

### Untersuchung des Evidenz-Verhaltens

Um den Simulationsaufwand weiter reduzieren zu können, werden in dieser Arbeit Annahmen über das *qualitative* Verhalten der Evidenzen von Fehlern an den einzelnen Kandidatenstellen gemacht.

Hierbei wurde zunächst das Verhalten von Fehlern an der eigentlichen Defektstelle

in Abhängigkeit der Defektgröße beobachtet. Die Zahl der übereinstimmenden fehlerhaften Bits  $\sigma_{f'}$  eines Referenzfehlers  $f'$  wies dabei für eine Defektgröße  $\delta_{f'} \approx \delta_f$  ein globales Maximum auf. Für  $\delta_{f'} < \delta_f$  fielen diese typischerweise geringer aus, da sich die Zahl der fehlerhaften Antwortbits für kleinere Defekte verringert. Ebenso wurde bei  $\delta_{f'} > \delta_f$  ein Verlust an  $\sigma_{f'}$  festgestellt, was sich durch die Präsenz von Hazards erklären ließ, die über den Zeitpunkt der Abtastung hinausgeschoben worden sind. Bei den Fehlvorhersagen  $\iota_{f'}$  konnte man des Weiteren beobachten, dass sich die Anzahl bei Erhöhung der Defektgröße im qualitativen Verlauf bis zur Sättigung stetig vergrößert hat. Lediglich bei  $\delta_{f'} \approx \delta_f$  wurde ein vorübergehender Einbruch im Verlauf festgestellt. Hier hat  $\iota_{f'}$  ein lokales Minimum aufgewiesen, da die Defektgrößen  $\delta_{f'}$  und  $\delta_f$  übereingestimmt hatten.

Zudem wurde angenommen, dass Defekte *einer* Größe an den unterschiedlichen Gattern aufgrund von strukturellen Korrelationen ein *gleichartiges* Fehlverhalten aufweisen. Erste Beobachtungen hatten dabei ergeben, dass sich die qualitativen Verläufe der Evidenzkomponenten  $\sigma_{f'}$  und  $\iota_{f'}$  für unterschiedlichen Kandidatenstellen gleich verhalten, da die Gatter ähnliche Aktivierungs- und Propagierungsbedingungen haben. In Abhängigkeit von der Struktur des Schaltkreises (z.B. durch Rekonvergenzen), können sich die Verläufe einzelner Gatter dennoch von anderen unterscheiden. Allerdings wurde unter den *Ausreißern* ebenso ein Gruppen-Verhalten festgestellt, sodass auch hier von Ähnlichkeiten im qualitativen Verlauf gesprochen werden kann.

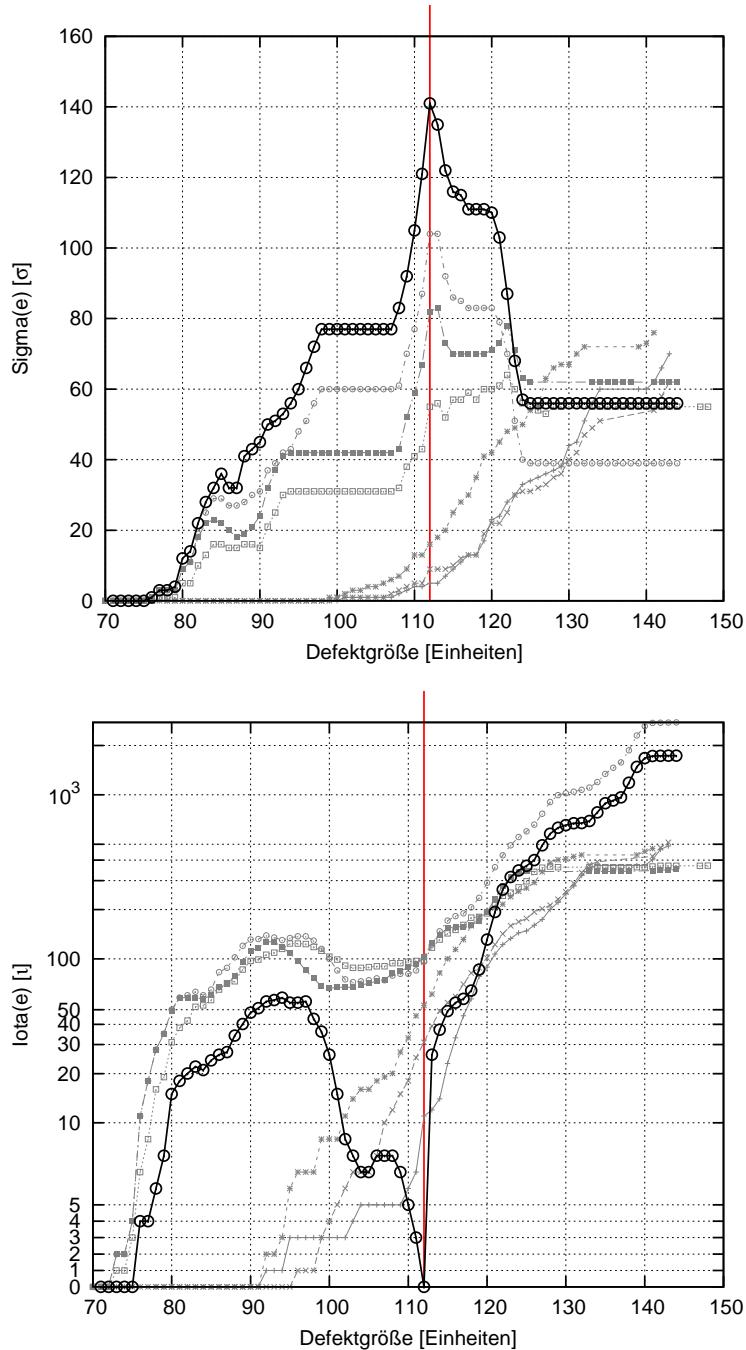

Abbildung 3.5 illustriert die Ähnlichkeiten der Evidenzen am Beispiel der Kandidaten  $S$  nach der strukturellen Analyse mit 2560 Testantworten eines DUDs. Jede Kurve entspricht dem Verlauf der übereinstimmenden (Sigma) bzw. falsch vorhergesagten (Iota) fehlerhaften Bits aller simulierten Defekte an den Kandidatenstellen.

**Abbildung 3.5:** Sigma- und Iota-Werte von CPT-Kandidaten für einen Testsatz aus Pseudozufallsmustern. Die simulierten Defekte der eigentlichen Fehlerstelle sind mit schwarzen Kreisen eingezeichnet. Der senkrechte Strich markiert die eigentliche Größe des Defekts (112) im DUD.

## Selektive Simulation der Kandidaten

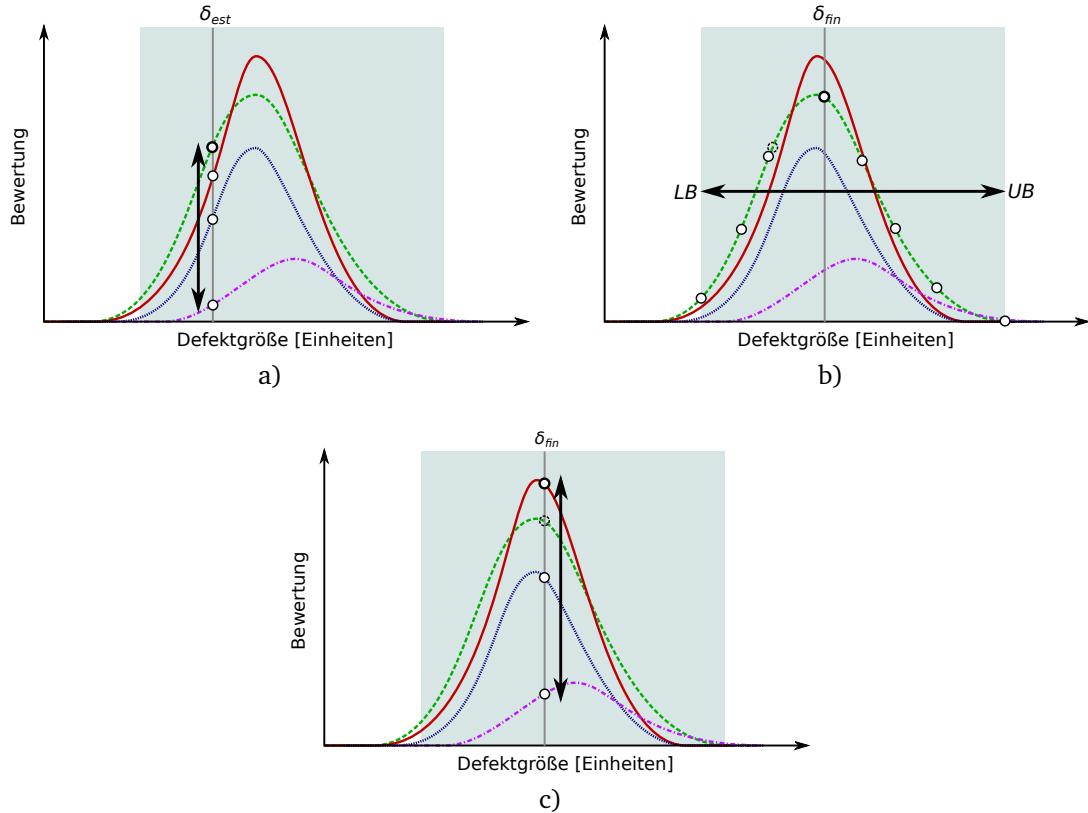

Die Ähnlichkeiten in den Evidenzen werden nun ausgenutzt, um **selektiv** Kandidaten zu simulieren. Dabei werden die folgenden drei Schritte ausgeführt:

- Simuliere die in der ersten Instanz abgeschätzte Defektgröße  $\delta_{est}$  an allen CPT-Kandidaten und bewerte die Evidenzen.

- Simuliere eine Menge verschiedener Defektgrößen an der Stelle des besten Kandidaten aus Schritt 1 und bewerte die Evidenzen.

- Simuliere die Defektgröße  $\delta_{fin}$  des besten Kandidaten aus Schritt 2 an allen anderen CPT-Fehlerstellen und bewerte die Evidenzen.

Zunächst wird an allen Kandidaten  $S$  des Critical Path Tracing die in Abschnitt 3.1.2 abgeschätzte Defektgröße mit der Fehlermaschine simuliert. Die dabei berechneten Evidenzen werden anschließend mit Hilfe einer *Bewertungsfunktion* evaluiert (siehe nächster Abschnitt), um einen **Einstiegspunkt**  $s \in S$  zu finden. Wenn die strukturelle Analyse bereits eine gute Approximation der Defektgröße liefert, sodass  $\delta_{est} \approx \delta_f$ , dann befindet sich der Eingangspunkt mit hoher Wahrscheinlichkeit an der eigentlichen Defektstelle.

Im zweiten Schritt wird anschließend die abgeschätzte Defektgröße  $\delta_{est}$  **korrigiert**, indem das Verhalten einer Menge von Defekten *verschiedener* Größen am Einstiegspunkt  $s$  simuliert und beobachtet wird. Hinsichtlich der vielen Pfade im Schaltkreis ist die Berechnung einer vollständigen Liste mit allen Fehler eines Knotens nach dem Modell sehr aufwändig. Die zu simulierenden Fehler werden deshalb durch eine Quantisierung des Defekt-Intervalls am Einstiegspunkt gewonnen, welches folgendermaßen nach [Sch11] bestimmt wird: Sei  $\delta_{min}(s)$  der kleinste detektierbare Defekt und  $\delta_{max}(s)$  der Transitionsfehler des Knoten  $s$ , dann repräsentiert  $D_s = [\delta_{min}(s), \delta_{max}(s)]$  das Defektgrößen-Intervall von  $s$ . Aus diesem lassen sich nun durch *Quantisieren* des Intervalls mit einem festen Faktor  $q$  insgesamt  $q$  verschiedene Defektgrößen in gleichen Abständen extrahieren. Diese können nun mit Hilfe der berechneten Ober- und Untergrenzen auf die Menge  $D'_s = \text{QUANTISIERE}(D_s, q) \cap [LB, UB]$  reduziert werden.

**Anmerkung:** Durch die Quantisierung des Defekt-Intervalls  $D_s$  in diskrete Werte kann es passieren, dass sich der eigentliche zu diagnostizierende Defekt nicht mehr unter den extrahierten Größen befindet, wodurch ein Fehler bei der Abschätzung eingeführt wird. Die Abweichung ist dabei abhängig vom gewählten Quantisierungsfaktor  $q$ , der die Abstände zwischen zwei aufeinanderfolgenden Defektgrößen in  $D'_s$  bestimmt. Der lokale Fehler der Abschätzung beträgt bei einer erfolgreichen Diagnose somit im Mittel  $\Delta_{err} = |\delta_{fin} - \delta_f| \approx \frac{1}{2} \cdot \frac{1}{q}$  Prozent. Zeitgleich reduziert die Quantisierung jedoch die Komplexität des Fehlermodells in der Zeit-Komponente auf einen konstanten Quantisierungsfaktor  $q < k$  und bietet einen Kompromiss zwischen Präzision und Aufwand.

**Abbildung 3.6:** Illustration aller Schritte der selektiven Simulation. – a) Bestimmung des Einstiegspunktes. b) Korrektur der abgeschätzten Defektgröße. c) Finale Evaluierung der Kandidaten.

Die verbleibenden Defektgrößen in  $D'_s$  werden dann in der Fehlermaschine simuliert. Nach Bewertung der Evidenzen extrahiert man die Defektgröße  $\delta_{fin}$  des besten Kandidaten, welche im Weiteren als neue Abschätzung von  $\delta_f$  dient.

Im dritten und letzten Schritt werden die einzelnen CPT-Fehlerstellen unter der korrigierten Defektgröße  $\delta_{fin}$  evaluiert und die Evidenzen berechnet. Da die korrigierte Defektgröße am Einstiegspunkt bereits im vorigen Schritt simuliert worden ist, muss diese hier nicht mehr zusätzlich ausgewertet werden. Nach einer letzten Bewertung der resultierenden Evidenzen erhält man dann die finale Rangliste mit den wahrscheinlichsten Kandidaten für den Defekt im DUD.

Zur Veranschaulichung der selektiven Simulationsmethode wurden die drei Schritte in Abbildung 3.6 illustriert. Im Vergleich zum vollen Simulationsansatz, müssen mit dieser Methode nur  $q + 2 \cdot |S| - 1 \in \mathcal{O}(k + |S|)$  anstatt  $\mathcal{O}(k \cdot |S|)$  Simulationen durchgeführt werden.

### 3.3 Bewertung der Kandidaten