Institut für Technische Informatik

Universität Stuttgart

Pfaffenwaldring 47

D–70569 Stuttgart

Diplomarbeit Nr. 3380

## **Test Rekonfigurierbarer Scan-Netzwerke**

Marcel Schaal

**Studiengang:** Informatik

**Prüfer:** Prof. Dr. rer. nat.

Hans-Joachim Wunderlich

**Betreuer:** M. Sc. Rafał Baranowski

Dipl. Inf. Michael Kochte

**begonnen am:** 8. August 2012

**beendet am:** 7. Februar 2013

**CR-Klassifikation:** B.7.1, B.8.1, D.2.5, J.6, K.1

# Inhaltsverzeichnis

|                                                                  |           |

|------------------------------------------------------------------|-----------|

| <b>1. Einleitung und Motivation</b>                              | <b>7</b>  |

| <b>2. Grundlagen des Hardware-Tests</b>                          | <b>9</b>  |

| 2.1. Test und Diagnose . . . . .                                 | 9         |

| 2.2. Testbarer Entwurf . . . . .                                 | 11        |

| 2.3. Abstraktionsebenen in der Modellierung . . . . .            | 16        |

| 2.4. Strukturelle Fehlermodelle . . . . .                        | 17        |

| 2.5. Fehlersimulation . . . . .                                  | 19        |

| 2.6. Automatische Testmustererzeugung . . . . .                  | 21        |

| 2.7. Erfüllbarkeitsproblem der Aussagenlogik . . . . .           | 21        |

| <b>3. Grundlagen Rekonfigurierbarer Scan-Netzwerke</b>           | <b>25</b> |

| 3.1. Aufbau und Struktur . . . . .                               | 25        |

| 3.2. Modellierung auf Transaktionsebene . . . . .                | 29        |

| 3.3. Klassifizierung der Fehlerwirkung und Testbarkeit . . . . . | 31        |

| 3.4. Funktionale Fehlermodelle auf Transaktionsebene . . . . .   | 34        |

| <b>4. Testalgorithmen für Rekonfigurierbare Scan-Netzwerke</b>   | <b>37</b> |

| 4.1. Pseudo-zufällige Testmustererzeugung . . . . .              | 37        |

| 4.2. Funktionale Testheuristiken . . . . .                       | 39        |

| 4.3. Testmustererzeugung auf Transaktionsebene . . . . .         | 40        |

| 4.4. Vergleich der Testalgorithmen . . . . .                     | 45        |

| <b>5. Implementierung</b>                                        | <b>47</b> |

| 5.1. Übersicht des Testverfahrens . . . . .                      | 47        |

| 5.2. Zugriffsmustererzeugung – eda1687 . . . . .                 | 48        |

| 5.3. Einlesen und Verarbeiten von Netzlisten . . . . .           | 49        |

| 5.4. Extraktion des Scan-Pfads aus der Netzliste . . . . .       | 51        |

| 5.5. Aktivierung von Scan-Pfad-Segmenten . . . . .               | 53        |

| 5.6. Fehlerinjektion und -detektion . . . . .                    | 55        |

| 5.7. Fehlersimulation . . . . .                                  | 58        |

| <b>6. Ergebnisse und Bewertung</b>                               | <b>61</b> |

| 6.1. Übersicht der verwendeten Testschaltungen . . . . .         | 61        |

| 6.2. Auswertung der Testalgorithmen . . . . .                    | 66        |

| 6.3. Klassifizierung nicht detekter Fehler . . . . .             | 71        |

| <b>7. Zusammenfassung und Ausblick</b>                           | <b>77</b> |

|                             |           |

|-----------------------------|-----------|

| <b>A. Anhang</b>            | <b>81</b> |

| <b>Literaturverzeichnis</b> | <b>83</b> |

# Abbildungsverzeichnis

---

|      |                                                                                                |    |

|------|------------------------------------------------------------------------------------------------|----|

| 2.1. | Beispiel eines untestbaren Haftfehlers . . . . .                                               | 11 |

| 2.2. | Beispiel einer flankengesteuerten Scan-Zelle . . . . .                                         | 13 |

| 2.3. | Beispiel einer Scan-Kette . . . . .                                                            | 13 |

| 2.4. | Beispiel eines Haftfehlers . . . . .                                                           | 18 |

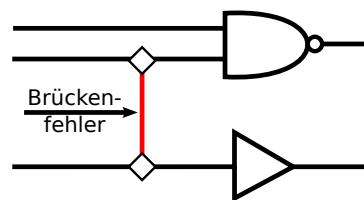

| 2.5. | Beispiel eines Brückenfehlers . . . . .                                                        | 18 |

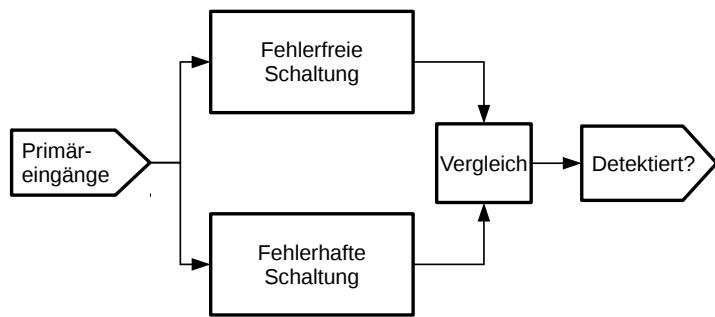

| 2.6. | Skizzierter Aufbau einer seriellen Fehlersimulation . . . . .                                  | 20 |

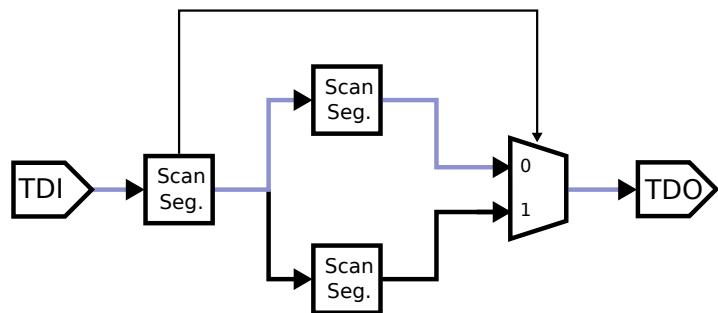

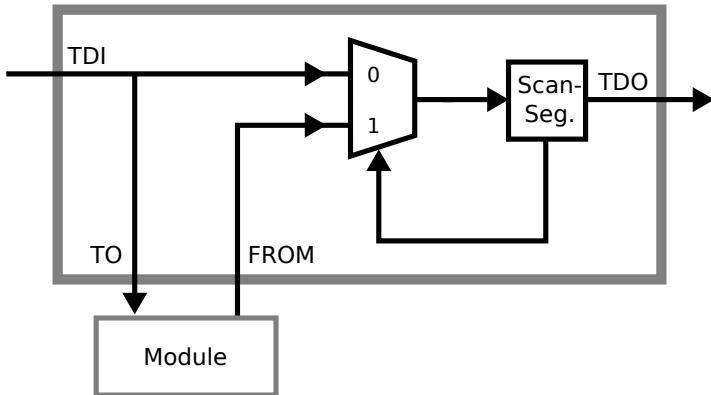

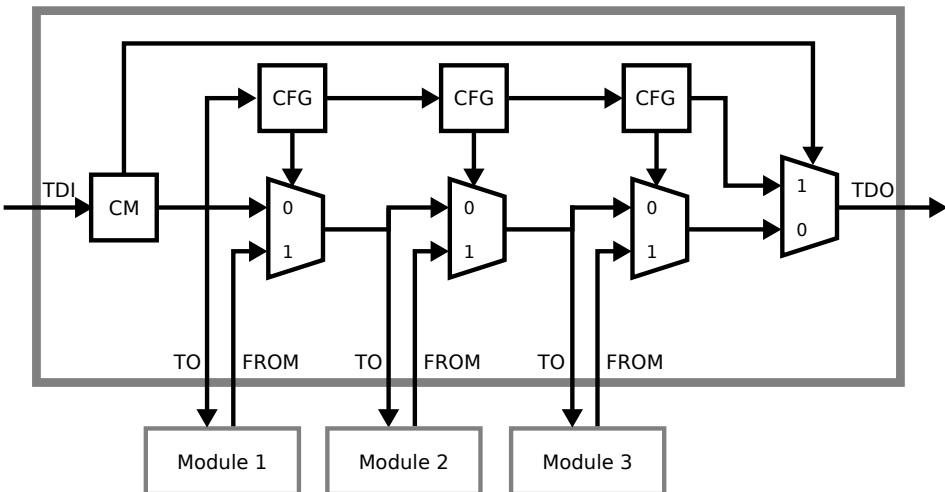

| 3.1. | Beispiel eines Rekonfigurierbaren Scan-Netzwerks . . . . .                                     | 26 |

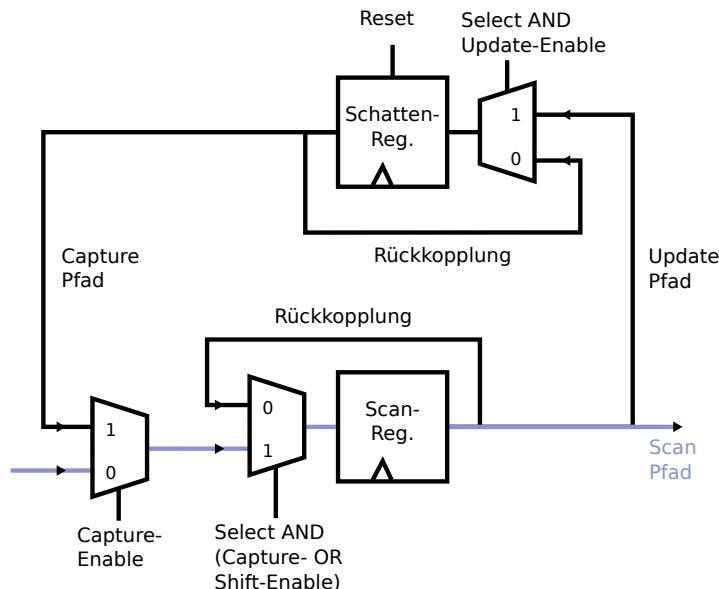

| 3.2. | Beispiel eines Scan-Segments . . . . .                                                         | 27 |

| 3.3. | Beispiel der aktiven Pfade in einem Scan-Segment während der Update-Phase                      | 28 |

| 3.4. | Beispiel der aktiven Pfade in einem Scan-Segment während der Capture-Phase                     | 29 |

| 3.5. | Beispiel der aktiven Pfade in einem Scan-Segment während der Scan-Phase .                      | 29 |

| 3.6. | Beispiel der Aktivierungsvariablen an Scan-Pfad-Segmenten auf Transaktions-<br>ebene . . . . . | 31 |

| 3.7. | Beispiel eines gebrochenen Scan-Pfads . . . . .                                                | 35 |

| 3.8. | Beispiel eines fälschlich aktiven Scan-Pfads . . . . .                                         | 35 |

| 3.9. | Beispiel eines instabilen aktiven Scan-Pfads . . . . .                                         | 36 |

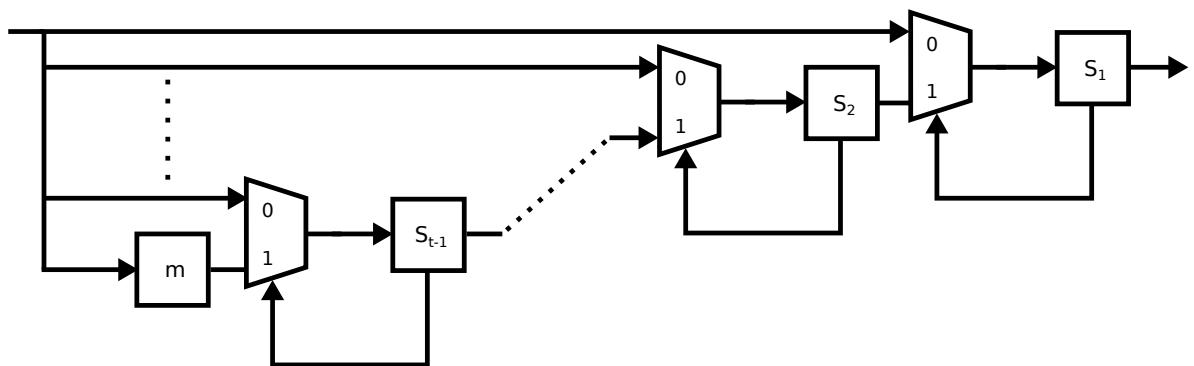

| 4.1. | Beispiel einer hierarchisch bedingten Zugriffsstruktur . . . . .                               | 38 |

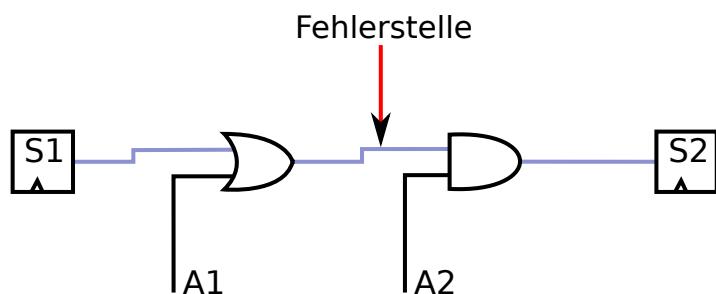

| 4.2. | Beispiel eines direkt gebrochenen Scan-Pfads . . . . .                                         | 41 |

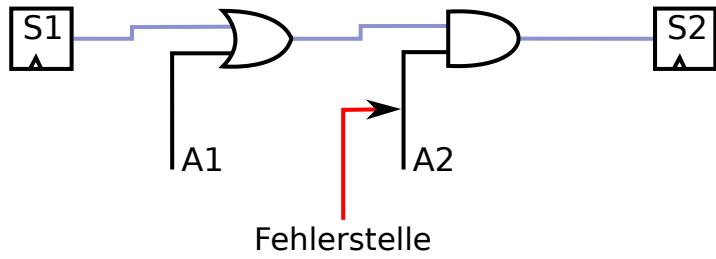

| 4.3. | Beispiel eines durch fehlerhafte Kontrolllogik gebrochenen Scan-Pfads . . . . .                | 42 |

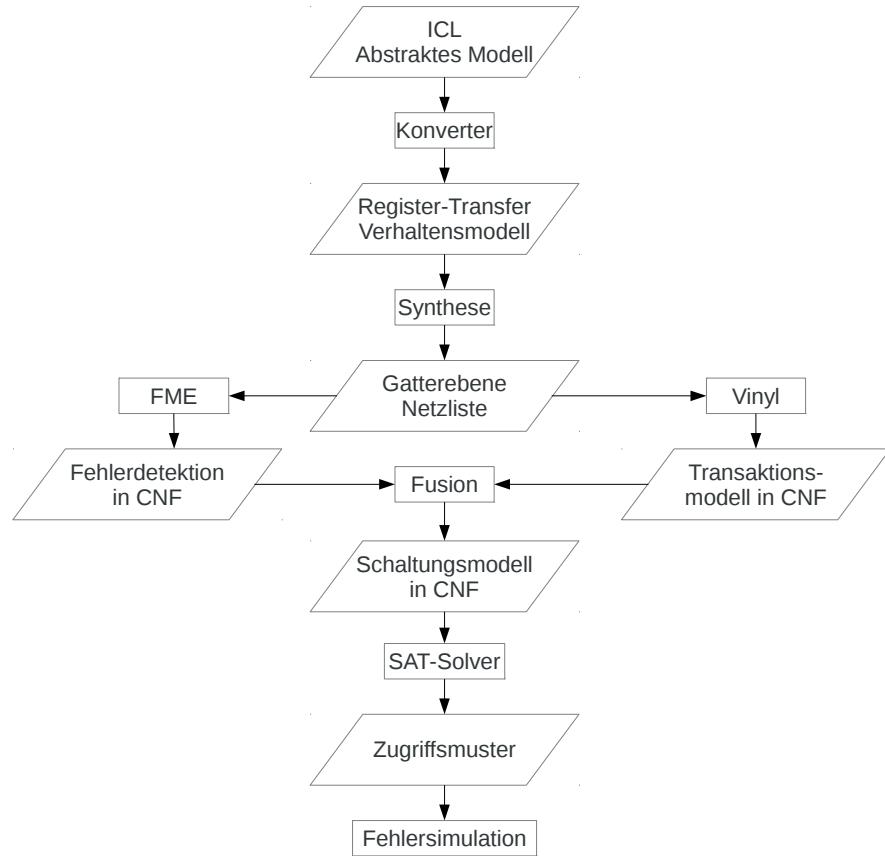

| 5.1. | Flowchart des Testverfahrens . . . . .                                                         | 48 |

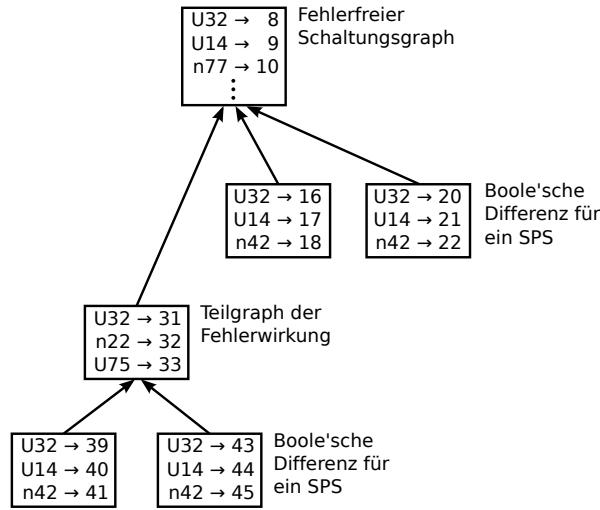

| 5.2. | Beispielinstanz zur hierarchischen Variablenabbildung . . . . .                                | 51 |

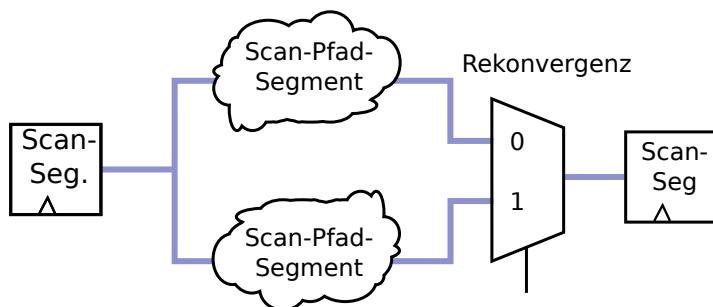

| 5.3. | Beispiel einer Scan-Pfad-Rekonvergenz . . . . .                                                | 52 |

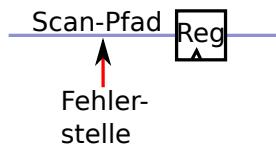

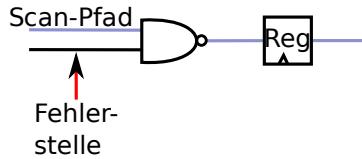

| 5.4. | Beispiel eines Fehlers auf dem Scan-Pfad . . . . .                                             | 56 |

| 5.5. | Beispiel eines Eingangsfehlers des Scan-Pfads . . . . .                                        | 57 |

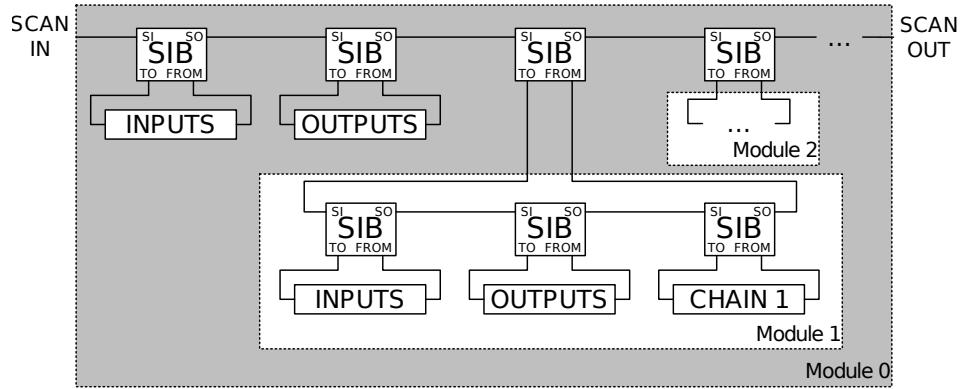

| 6.1. | Beispiel einer SIB-basierten Testschaltung . . . . .                                           | 62 |

| 6.2. | Struktureller Aufbau eines SIBs . . . . .                                                      | 62 |

| 6.3. | Struktureller Aufbau einer MUX-Zelle . . . . .                                                 | 63 |

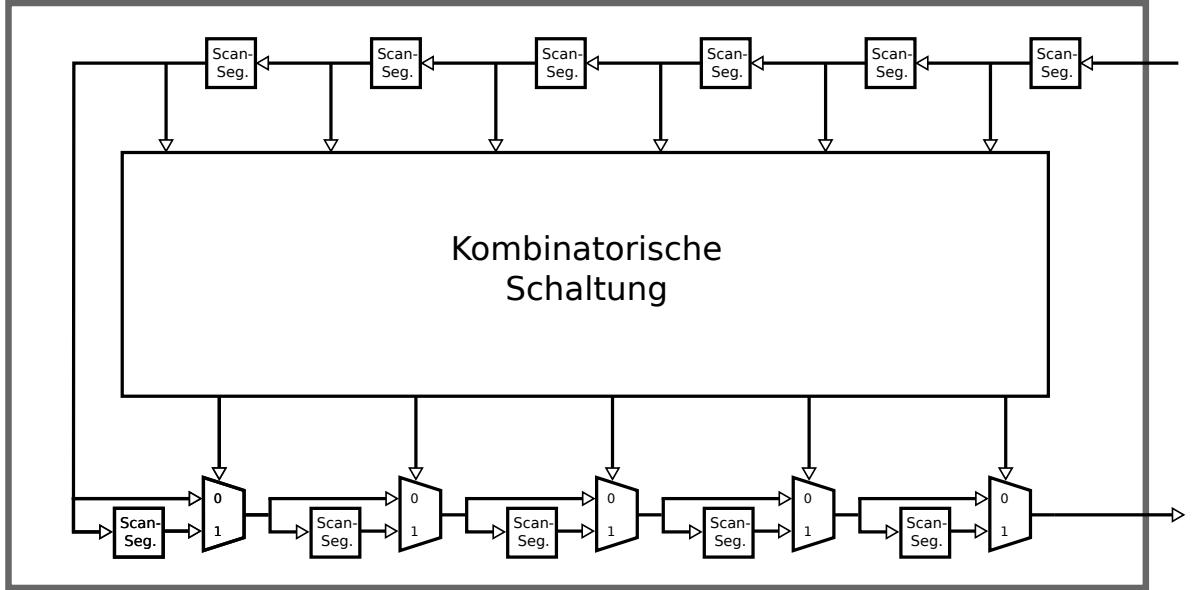

| 6.4. | Struktureller Aufbau einer Chain-Testschaltung . . . . .                                       | 64 |

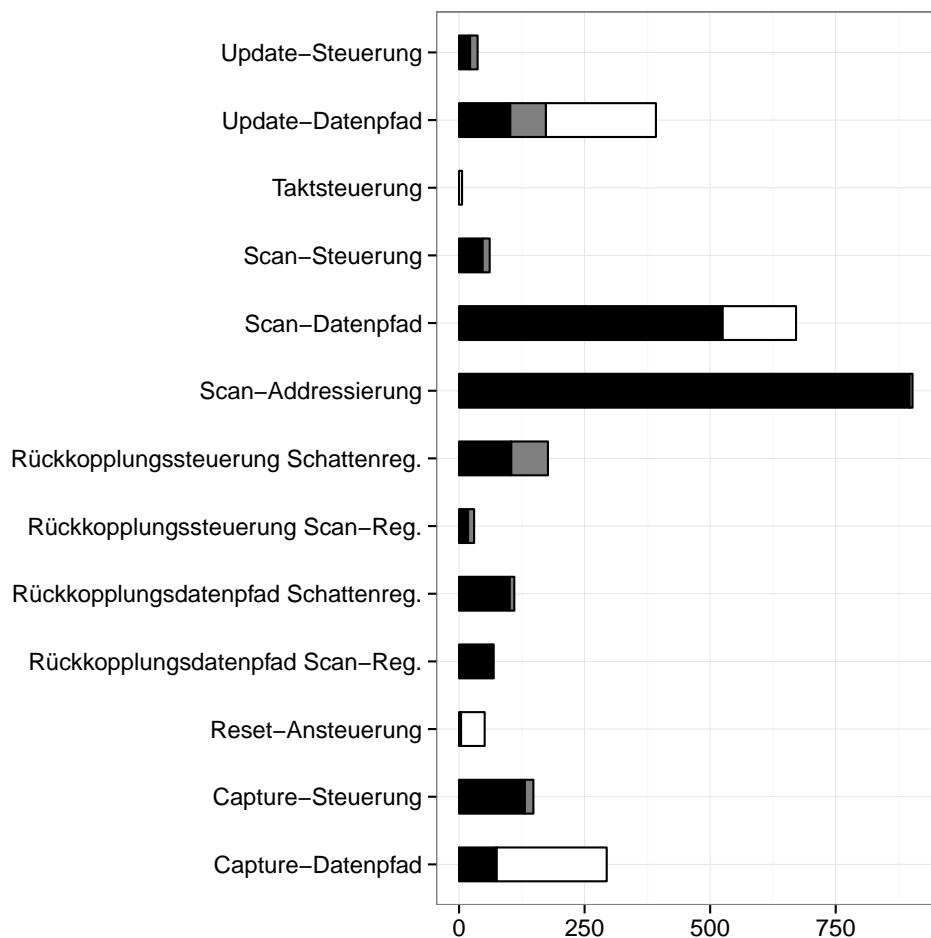

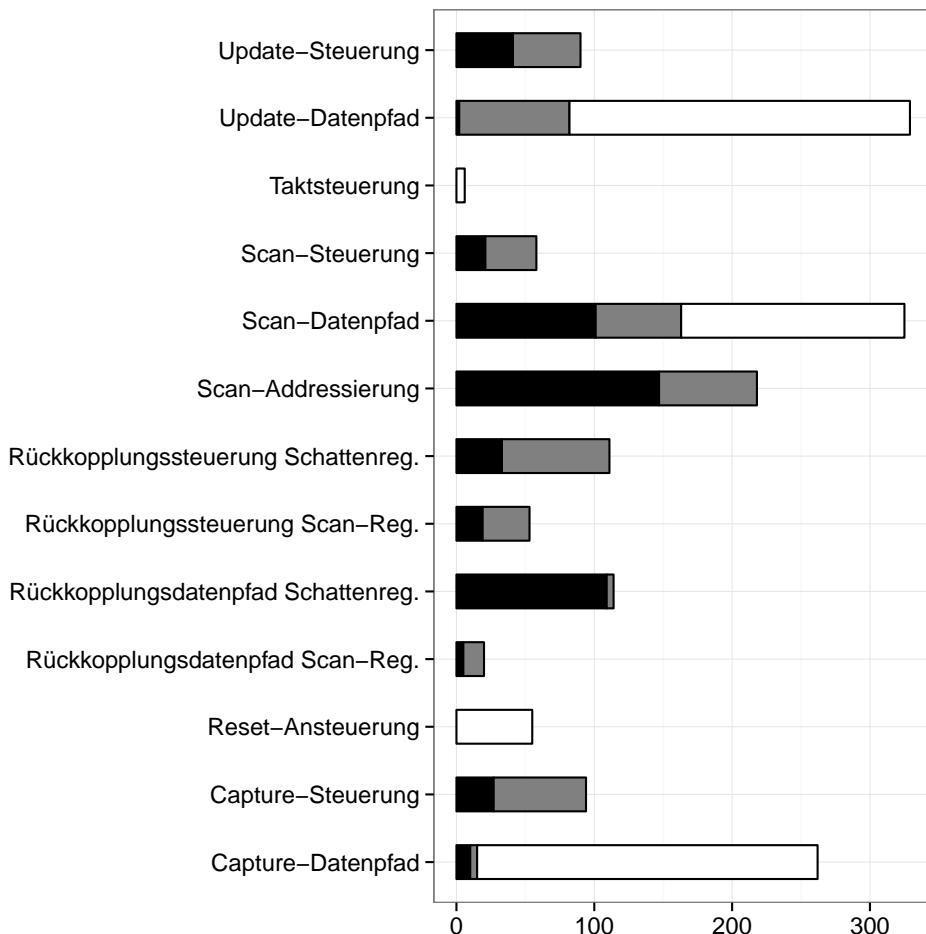

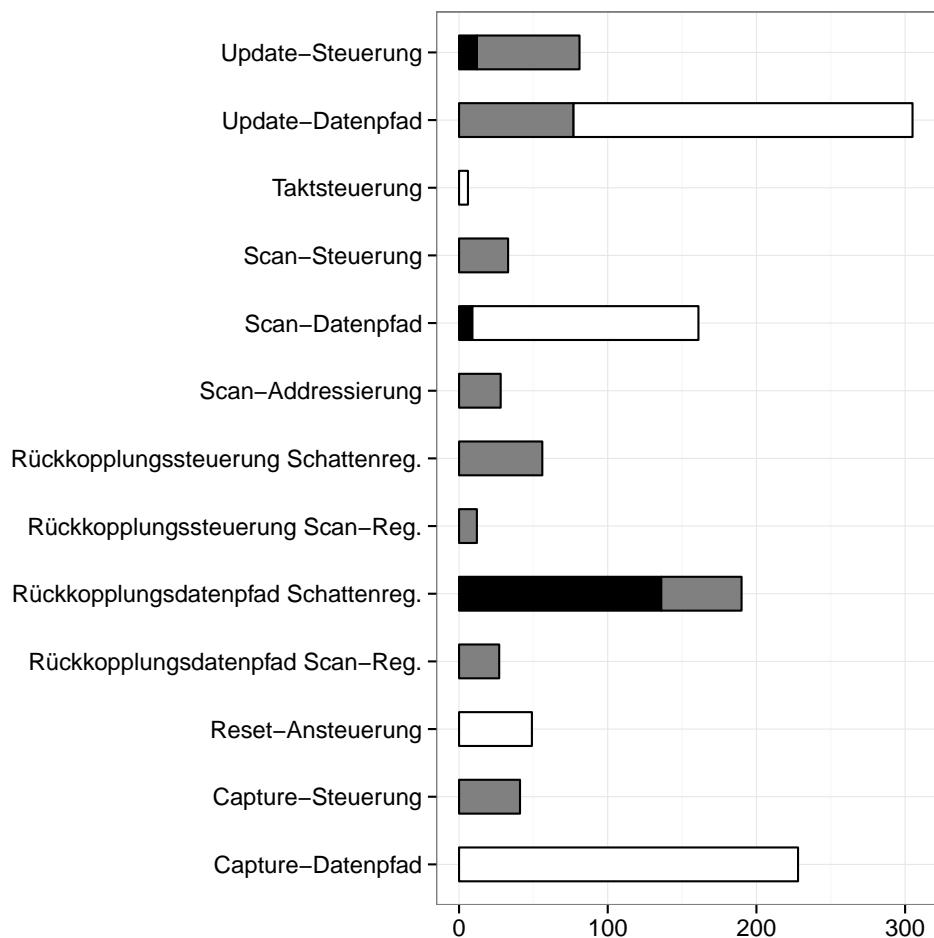

| 6.5. | Verbleibende Fehler in c499_chain . . . . .                                                    | 72 |

| 6.6. | Verbleibende Fehler in f2126_mux . . . . .                                                     | 73 |

| 6.7. | Verbleibende Fehler in f2126_sib . . . . .                                                     | 74 |

# Tabellenverzeichnis

---

|      |                                                                           |    |

|------|---------------------------------------------------------------------------|----|

| 2.1. | CNF-Äquivalente-Darstellung von Logikprimtiven . . . . .                  | 24 |

| 4.1. | Wahrscheinlichkeitstabelle für pseudo-zufälligen Test . . . . .           | 39 |

| 4.2. | Zusammenfassung der Testbarkeit verschiedener Fehlerklassen . . . . .     | 45 |

| 5.1. | Nicht-kontrollierende Werte von Logikgattern . . . . .                    | 54 |

| 5.2. | Äquivalente Fehlerklassen . . . . .                                       | 58 |

| 6.1. | Übersicht über ISCAS'85 Testschaltungen . . . . .                         | 64 |

| 6.2. | Statistik der Testschaltungen . . . . .                                   | 65 |

| 6.3. | Ergebnisse für Fehlerabdeckung und Laufzeit verwendeter Testalgorithmen . | 68 |

| 6.4. | Ergebnisse für die Anzahl und Länge der erzeugten Testmuster . . . . .    | 69 |

# Verzeichnis der Algorithmen

---

|      |                                                               |    |

|------|---------------------------------------------------------------|----|

| 4.1. | Schreibende funktionale Testheuristik . . . . .               | 40 |

| 5.1. | Datenstruktur eines Graphknotens . . . . .                    | 50 |

| 5.2. | Datenstruktur der hierarchischen Variablenabbildung . . . . . | 51 |

| 5.3. | Scan-Pfad-Extraktion . . . . .                                | 52 |

| 5.4. | Modellierung der Boole'schen Differenz . . . . .              | 53 |

| 5.5. | Pfadaktivierung . . . . .                                     | 55 |

| 5.6. | Pessimistische Fehlerdetektion . . . . .                      | 57 |

| A.1. | ICL-Beispiel . . . . .                                        | 81 |

# 1. Einleitung und Motivation

Moderne Mikrochips enthalten zahlreiche Instrumente, die zur Auswertung der Betriebsparameter, zum Test oder zur Validierung der Funktionalität genutzt werden. Rekonfigurierbare Scan-Netzwerke (RSN) bieten die Möglichkeit eines effizienteren, flexibleren und skalierbareren Zugriffs auf eingebettete Instrumente gegenüber üblichen statischen Scan-Ketten.

Durch den Einsatz von Rekonfigurierbaren Scan-Netzwerken nimmt jedoch die Komplexität der Zugriffsinfrastruktur zu. Während Scan-Ketten im Wesentlichen aus Schieberegistern bestehen, wodurch ein Defekt im Scan-Pfad relativ einfach festgestellt werden kann, finden sich in Rekonfigurierbaren Scan-Netzwerken, neben einfachen Logikelementen, auch Multiplexer und möglicherweise komplexere Schaltungen. Somit können unterschiedliche Scan-Pfade und -Hierarchien gebildet werden. Allerdings können bestehende Tests für Scan-Ketten die komplexere Steuerlogik bei Rekonfigurierbaren Scan-Netzwerken nicht ausreichend testen. Deshalb ist es notwendig, neuartige Teststrategien zu entwickeln, welche speziell an die Merkmale von Rekonfigurierbaren Scan-Netzwerken angepasst sind.

In dieser Arbeit werden Strategien für den Test Rekonfigurierbarer Scan-Netzwerke analysiert und ausgewertet. Es werden mehrere neue Verfahren zur Erzeugung von Testmustern vorgestellt, welche effizient bezüglich Laufzeit als auch des Speicherplatzbedarfs arbeiten.

Einen Überblick über die notwendigen Grundlagen des Hardware-Tests für den Verlauf dieser Arbeit wird in Kapitel 2 gegeben werden. Dort wird auf die Notwendigkeit des Tests bei der Herstellung von Mikrochips eingegangen. Zum besseren Verständnis folgt darauf ein Überblick über Fehlermodelle und Fehlersimulation als auch über die automatische Testmustererzeugung.

Aufbau und Arbeitsweise Rekonfigurierbarer Scan-Netzwerke werden im dritten Kapitel erklärt. Ebenfalls findet sich darin eine Klassifizierung der Fehlerwirkung des Haftfehlermodells in Rekonfigurierbaren Scan-Netzwerken. Darüber hinaus wird auf die effiziente Modellierung auf Transaktionsebene eingegangen, da sich eine taktgenaue Modellierung als zu komplex gestaltet.

Die verwendeten Testalgorithmen für Rekonfigurierbare Scan-Netzwerke werden in Kapitel 4 vorgestellt. Es wird deren Methodik erklärt und eine erste Analyse der Testbarkeit beschrieben.

Im fünften Kapitel wird die erarbeitete Implementierung näher erläutert. Dabei wird auf die Modellierung zur Erzeugung von Testmustern auf Transaktionsebene eingegangen. Hierzu ist es notwendig, eine entsprechende Verhaltensbeschreibung des Rekonfigurierbaren Scan-Netzwerks mit den notwendigen Erweiterungen zur Testmustererzeugung in ein Modell auf-

## *1. Einleitung und Motivation*

---

Transaktionsebene zu überführen, welches ebenfalls Teil des Implementierungskapitels ist. Abschließend wird die Modellierung von Fehlern und deren Wirkung, als auch Detektion, auf Transaktionsebene beschrieben, da diese eine Voraussetzung für die Testmustererzeugung ist.

Die Ergebnisse und Bewertung der Testalgorithmen finden sich in Kapitel 6. Hierbei wird zuerst der Aufbau der Experimente beschrieben, welche zur Analyse der betrachteten Algorithmen zur Testmustererzeugung herangezogen wurden. Im restlichen Verlauf des Kapitels werden die Ergebnisse der Experimente erläutert.

Das abschließende Kapitel 7 fasst die Arbeit und deren Ergebnisse kurz zusammen und gibt einen Ausblick, welche weiteren Verbesserungen aus Sicht des Autors sinnvoll sind.

## 2. Grundlagen des Hardware-Tests

In diesem Kapitel werden die notwendigen Grundlagen zum Verständnis der weiteren Arbeit vermittelt. Dabei wird Grundwissen aus der Technischen Informatik, wie sie im Grundstudium des Studiengangs Diplom Informatik gelehrt werden, vorausgesetzt. Nachgelesen werden können diese Grundlagen zum Beispiel in [WWW06] oder [PHo4]. Da die Implementierung der Arbeit auf der Gatterebene realisiert ist, werden keine elektrotechnischen Kenntnisse benötigt. Ein Grundwissen in Theoretischer Informatik, wie es zum Beispiel in [Scho8] vermittelt wird, ist vorteilhaft, denn die Modellierung des Problems findet in Form der Aussagenlogik statt.

Der erste Abschnitt erläutert das Problem des Hardware-Tests und der Diagnose, welches sich bei der Fertigung von integrierten Schaltungen ergibt. Daraufhin werden Verfahren vorgestellt, um dieses Problem einfacher zu gestalten. Anschließend wird eine Übersicht über verschiedene Abstraktionsebenen integrierter Schaltungen gegeben. Defekte werden im Hardware-Test als abstrakte Fehler in Form von Fehlermodellen beschrieben, welche näher in 2.4 erläutert werden. Zur Überprüfung der Auswirkung eines Fehlers in einer integrierten Schaltung kann Fehlersimulation genutzt werden, die in Kapitel 2.5 beschrieben wird. Folgend wird die Erzeugung von Testmustern für den Hardware-Test beschrieben und auf dessen Komplexität eingegangen. Abschließend wird die Umwandlung einer auf Gatterebene modellierten Schaltung in eine Instanz des Erfüllbarkeitsproblem der Aussagenlogik dargelegt.

### 2.1. Test und Diagnose

Eine fehlerfreie Herstellung integrierter Schaltkreise ist mit moderner Fertigungstechnik nicht möglich. Die immer höhere Integrationsdichte, und damit verbundene geringere Strukturgrößen, führen zu einem stärkeren Einfluss der Prozessschwankung auf die Schaltungseigenschaften und damit zu geringerer Ausbeute (engl. yield) [Sta86]. Die Ausbeute gibt das Verhältnis von funktionsfähigen Chips  $n_{funktional}$  zur Gesamtzahl produzierter Chips  $n_{produziert}$  an, daher:

$$(2.1) \quad yield = \frac{n_{funktional}}{n_{produziert}}$$

Die Ausbeute hängt von vielen Faktoren ab, wie etwa der Ausgereiftheit des Herstellungsverfahrens, der geforderten Produktqualität, der Größe der Chips und der Qualität des Tests. Je früher ein fehlerhafter Chip entdeckt wird, desto geringer sind die Kosten, da unnötige

## *2. Grundlagen des Hardware-Tests*

---

Schritte, wie Verpacken in ein Gehäuse oder im schlimmsten Fall Rückholung des Systems von einem Kunden, vermieden werden. Deshalb werden Chips in jeder Phase der Fertigung getestet. Zur Überprüfung, ob ein Mikrochip bestimmte Anforderungen in Form seiner Spezifikation erfüllt, das heißt funktional ist, existierten unterschiedliche Teststrategien.

Werden Testmuster außerhalb des Chips erzeugt und durch Testsysteme zugeführt, so wird von externem Test gesprochen. Testverfahren, welche dedizierte Testlogik auf einem Chip zur Erzeugung von Testmustern voraussetzen, werden als eingebauter Selbsttest (engl. Built-in self-test, BIST) bezeichnet.

Während es beim Hardware-Test im Wesentlichen lediglich um eine binäre Entscheidung geht, nämlich ob ein Mikrochip korrekt arbeitet oder nicht, steht bei der Diagnose die Frage im Vordergrund, warum ein Mikrochip oder Modul nicht richtig funktioniert. Dies kann unter anderem mit der Fehlerstelle und der Art des Fehlers beantwortet werden.

Die Diagnoseergebnisse können genutzt werden, um den Fertigungsprozess zu optimieren und damit die Ausbeute erhöhen und die Produktionskosten senken. Bestimmte physikalische Strukturen können zum Beispiel sehr empfindlich auf Schwankungen des Fertigungsprozesses sein und zu einer Häufung von Defekten führen. Diese Strukturen sollten dann mit dem fortschreitendem Prozess des Herstellungsverfahrens angepasst werden, um eine höhere Schwankungstoleranz zu gewährleisten, so dass die Defekte reduziert und die Produktqualität verbessert werden kann.

### **2.1.1. Fehlerabdeckung**

Um eine Aussage über die Güte einer gegebenen Testmustermenge  $T$  zu treffen, wird ein Gütekriterium benötigt. Dazu kann die Fehlerabdeckung  $C_T$  (engl. fault coverage) genutzt werden, welche sich aus der Zahl der von  $T$  entdeckten Fehler  $D$ , geteilt durch die Gesamtzahl der modellierten Fehler  $F$  ergibt:

$$(2.2) \quad C_T = \frac{D}{F}$$

Die Fehlerabdeckung gibt daher die relative Zahl der detektierten Fehler an und wird als Prozentzahl ausgedrückt. Da weder die Anzahl der Testmuster, noch die benötigte Testzeit in die Aussage der Fehlerabdeckung eingehen, stellt die Fehlerabdeckung nur ein Effektivitätsmaß und kein Effizienzmaß dar.

Je nach Anwendungsbereich werden unterschiedliche Fehlerabdeckungen gefordert. In der Automobilindustrie wird von den Herstellern in der Regel eine Fehlerabdeckung von mindestens 99,999% nach ISO 26262-5 vorgeschrieben [iso12].

### **2.1.2. Testbarkeit von Fehlern**

Ein Fehler ist detektierbar genau dann, wenn eine Folge von Testmustern  $M$  existiert, welche den Fehler aktiviert und zu einer von der fehlerfreien abweichenden Ausgabe an

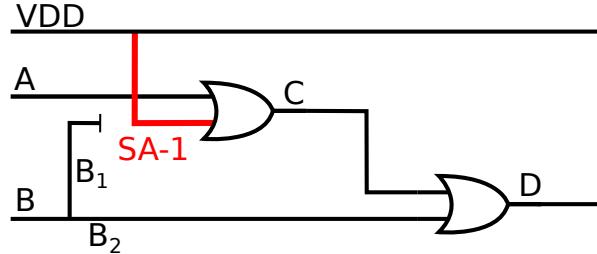

den Primärausgängen führt. Ein Fehler ist nicht detektierbar, falls keine solche Folge von Testmustern existiert. Abbildung 2.1 zeigt einen untestbaren Fehler. Diese können unter anderem in fehlertoleranten Strukturen auftreten, da in diesen ein Fehler keine Auswirkung auf das Ergebnis nehmen soll, sofern keine weiteren Maßnahmen des testbaren Entwurfs eingesetzt wurden.

Abbildung 2.1.: Beispiel eines untestbaren Haftfehlers an Signal  $B_1$

Wird ein Fehler  $F1$  ausschließlich durch eine Teilmenge der Testmustermenge eines weiteren Fehlers  $F2$  detektiert, so dominiert der Fehler  $F2$  den Fehler  $F1$ .

Die Fehlerwirkung verschiedener Fehler kann identisch sein, so dass diese nicht voneinander unterscheidbar sind. In diesem Fall können die Fehler in Äquivalenzklassen zusammengefasst werden und müssen nicht separat behandelt werden. Dadurch kann Rechenzeit bei der Erzeugung von Testmustern eingespart werden [HKB94].

## 2.2. Testbarer Entwurf

Die Implementierung einer integrierten Schaltung beeinflusst ihre Testbarkeit und die entstehenden Testkosten. Testbarer Entwurf umfasst Verfahren und Strategien zum gezielten Entwurf integrierter Schaltungen mit hoher Testbarkeit.

Je schlechter eine integrierte Schaltung testbar ist, desto aufwendiger ist der benötigte Test und damit zum Beispiel die Anzahl der benötigten Testmuster. Auf der einen Seite müssen dann mehr Testmuster erzeugt werden, wodurch die benötigte Vorbereitungszeit für den Test steigt, um diese zusätzlichen Muster zu berechnen und zu validieren. Dies kann dann zu einer verlängerten Produkteinführungszeit führen und somit den Gewinn schmälern. Auf der anderen Seite müssen mehr Testmuster mittels automatischer Testsysteme (engl. automatic test equipment, ATE) in der gleichen Zeit geprüft werden, so dass entweder weniger Chips gefertigt werden können, oder weitere automatische Testsysteme benötigt werden, wodurch die Testkosten steigen.

Ein klassisches Beispiel für schlechte Testbarkeit stellt ein  $n$ -Bit-Zähler dar, welcher nur über zwei Eingänge zum Inkrementieren und Zurücksetzen verfügt und keine Optimierungen für einen effizienten Test besitzt. Um diesen Zähler vollständig funktional zu testen, müssen dazu alle  $2^n$  Zustände iteriert werden. Unter Annahme, dass der Zähler 64 Bit besitzt, das heißt

## 2. Grundlagen des Hardware-Tests

---

$n = 64$  und 25 Millionen Iterationen pro Sekunde durchgeführt und getestet werden können, so beträgt die Testdauer fast 24.000 Jahre. Eine Möglichkeit des testbaren Entwurfs wäre die Aufspaltung in kleinere Zähler mit beispielsweise 8-Bit und separaten Reset-Eingängen.

Um den Test integrierter Schaltungen wirtschaftlich zu gestalten, wurden Methoden entwickelt, um die Testbarkeit stark zu verbessern. Eine davon besteht in der Integration einer zusätzlichen Testinfrastruktur in die Schaltung. Scan-Design, welches im Abschnitt 2.2.1 näher erklärt wird, stellt so eine Testinfrastruktur dar.

Weitere Verfahren des testbaren Entwurf umfassen Prüfpunkte, das heißt das Hinzufügen von zusätzlichen Dateneingängen, um die Kontrollierbarkeit oder das Hinzufügen von Datenausgängen, um die Observierbarkeit zu erhöhen, sowie BIST und Testdatenkompression.

### 2.2.1. Scan-Ketten

Mit Scan-Ketten (engl. scan chain) wurde eine Entwurfstechnik eingeführt, welche die Erzeugung von Testmustern wesentlich vereinfacht. Dies wird erreicht, indem sequentielle Speicherelemente von außen kontrollier- und observierbar gemacht werden. Dadurch wird eine wirtschaftliche deterministische Testmustererzeugung auch für große integrierte Schaltungen ermöglicht. Scan-Ketten werden seit der Einführung durch [WA73] nahezu überall im testbaren Entwurf eingesetzt.

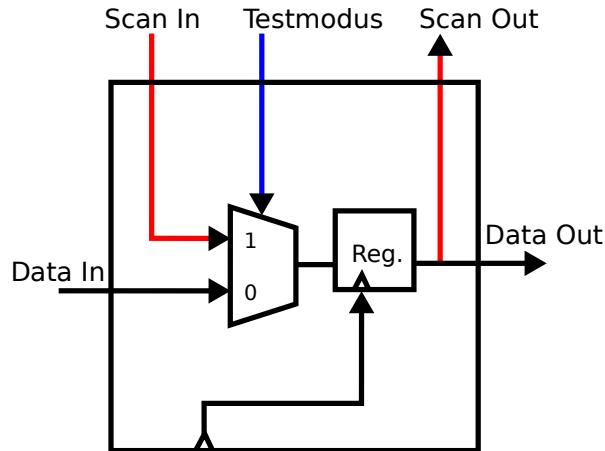

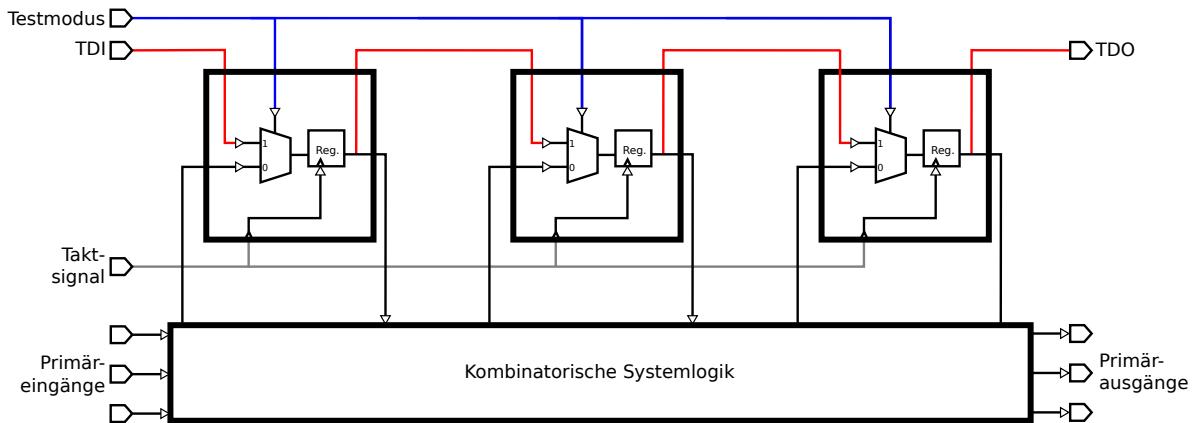

Die grundlegende Idee der Scan-Ketten besteht darin, dass sequentielle Speicherelemente durch Scan-Zellen ersetzt werden. Diese Scan-Zellen bestehen, neben dem ursprünglichen Daten- und Kontrollpfad des Speicherelements, aus einem weiteren Datenpfad mit zugehöriger Kontrolllogik, wie es in der Abbildung 2.2 skizziert ist. Alle Scan-Zellen werden dann über diesen zusätzlichen Datenpfad in einer langen Kette verbunden, wie es in Abbildung 2.3 dargestellt wird. Die offenen Enden der Kette werden als zusätzliche Primärein- und -ausgänge, sowie deren Kontrollsignale, zur integrierten Schaltung hinzugefügt. Die zusätzlichen Signale sollen kurz erläutert werden:

**Testdatenein- und -ausgänge** Die eigentlichen Ein- und Ausgänge zum Transport von Daten vom automatischen Testsystem zum Chip, und vom Chip zum automatischen Testsystem. Diese bilden den Anfang (TDI) und das Ende (TDO) der Scan-Kette.

**Testtakt** Ein separates Taktsignal für die Testinfrastruktur kann notwendig sein, falls das Zeitverhalten im Testbetrieb anders ist, als im funktionalen Betrieb.

**Testmodus** Spezielles Signal, welches den Modus des Chips zwischen funktionalem Systembetrieb und Testbetrieb umschaltet.

**Test-Reset** Die Testinfrastruktur kann optional ein eigenes Signal zum Zurücksetzen aller Scan-Register besitzen.

Somit können Daten unabhängig von der eigentlichen Systemlogik von außerhalb der integrierten Schaltung in die Register geschrieben oder ausgelesen werden. Dies führt zur vollen Observier- und Kontrollierbarkeit der Speicherelemente.

**Abbildung 2.2.:** Beispiel einer flankengesteuerten Scan-Zelle

Die Verbindungen des Scan-Pfads (blau) und der Aktivierung des Testmodus (rot) wurden hervorgehoben.

**Abbildung 2.3.:** Beispiel einer Scan-Kette

Alle speichernden Elemente der Schaltung wurden durch Scan-Zellen ersetzt. Die zusätzlichen Verbindungen des Scan-Pfads (rot) und der Aktivierung des Testmodus (blau) wurden hervorgehoben.

Ein Nachteil der Scan-Ketten besteht darin, dass durch das Hinzufügen der Multiplexer an den Registereingängen und der zusätzlichen Steuerlogik, der Logik- beziehungsweise Flächenbedarf für die Schaltung um bis zu 30 Prozent erhöht wird [Kun93]. Ein weiterer Nachteil betrifft das Zeitverhalten, da die Multiplexer unweigerlich auf dem kritischen Pfad liegen und die Pfadlänge erhöhen beziehungsweise die maximale Betriebsfrequenz reduzieren können.

## *2. Grundlagen des Hardware-Tests*

---

Beim Entwurf der Testinfrastruktur gibt es hierbei verschiedene Varianten, die im Folgenden kurz erläutert werden:

**Full-Scan-Design** Bei einem Full-Scan-Design sind alle Register über die Scan-Ketten les- und schreibbar, so dass alle sequentiellen Elemente der Schaltung vollständig kontrollier- und observierbar sind.

**Partial-Scan-Design** Sofern nur eine Teilmenge der Register direkt durch die Scan-Ketten zugreifbar ist, handelt es sich um ein Partial-Scan-Design nach [Tri84]. Dies reduziert die zusätzlich benötigte Logik für die Testinfrastruktur gegenüber einem Full-Scan-Design und kann bei geeignetem Schaltungsentwurf zu ähnlich hoher Testbarkeit führen. Insbesondere bei Registern mit ungünstigem kritischem Pfad kann ein Partial-Scan-Design genutzt werden, um die geforderte Geschwindigkeit einzuhalten.

**Parallele Scan-Ketten** Durch die Verwendung von mehreren Scan-Ketten kann die Testzeit entsprechend reduziert werden und damit die Testkosten gesenkt werden [NGB92]. Soll die Zunahme an Primärein- und -ausgängen reduziert werden, so kann die Illinois Scan-Architektur eingesetzt werden, bei der lediglich ein einzelner Scan-Dateneingang genutzt wird [HP99].

**Test-Kompression** Häufig ist die Bandbreite zwischen externem Tester und zu testender Schaltung auf dem Wafer begrenzt. Deshalb werden die Testdaten vor der Übertragung komprimiert und auf dem Chip wieder dekomprimiert [VMo3]. Dadurch können Kompressionsraten von 30-500 erreicht werden, was eine entsprechende Reduktion der Testzeit zur Folge hat [RTKMo4].

### **2.2.2. Boundary Scan/JTAG**

Zur Interoperabilität zwischen verschiedenen Herstellern beziehungsweise Anwendern im Verlauf der Fertigung und damit auch im Herstellungstest, wurde ein Standard zum Zugriff auf die Testinfrastruktur durch Scan-Ketten geschaffen. Diese Initiative wurde durch die Firma Philips initiiert und von verschiedenen großen Halbleiter-Herstellern in der Joint Test Action Group (JTAG) mitgetragen. Das Ziel war es eine standardisierte Schnittstelle zum Zugriff auf die Testinfrastruktur eines Mikrochips, welche ohne weitere Absprachen interoperabel ist, zu schaffen. Eine entsprechende Normierung fand im Rahmen des weltweiten Berufsverbands der Ingenieure aus Elektro- und Informationstechnik (Institute oft Electrical and Electronics Engineers, IEEE) unter der Bezeichnung IEEE 1149.1 statt [IEE01].

Verschiedene Erweiterungen wurden seit der ursprünglichen Normierung geschaffen, um den Einsatzzweck von JTAG zu erweitern. So wurde unter anderem IEEE 1149.6 zum Test von gemischten differentiellen Hochgeschwindigkeitssignalen oder 1149.4 für analoge Schaltungsteile erarbeitet.

Bei IEEE 1149/JTAG handelt es sich um eine Standardisierung für den Zugriff auf der Platinenebene. Ursprünglich entwickelt zum Test der Verbindungen auf der Platine (engl. boundary test), wird es heute ebenfalls genutzt, um die integrierte Schaltung selbst zu testen.

Dafür wurde bei der Entwicklung die Testinfrastruktur als Ganzes betrachtet und entworfen. Jedoch bestehen heutige Mikrochips nicht mehr nur aus einer einzelnen integrierten Schaltung, sondern setzen sich oft aus mehreren Modulen zu einem ganzen System auf einem Chip (engl. System-on-a-Chip, SOC) zusammen. Dies ist ohne Weiteres mit JTAG möglich, dennoch ist der Zugriff auf ein einzelnes Modul, ohne dass der gesamte Chip in den Testmodus versetzt werden muss, oft wünschenswert.

Um die Entwurfskosten niedrig zu halten, wurde ein Standard zur Wiederverwendung von Modultests gewünscht, um z.B. die Integration und Test von IP-Cores in SOCs zu vereinfachen. Ein solcher Standard fand Normierung als IEEE 1500 „Embedded Core Test“. Des weiteren ermöglicht IEEE 1500 ein Modul auf dem Scan-Pfad zu umgehen und so einen Bypass zu erzeugen, so dass ein separater Modultest möglich ist. Dabei handelt es sich allerdings nicht mehr um eine Scan-Kette mit statischer Struktur, sondern um ein Rekonfigurierbares Scan-Netzwerk, welche in Kapitel 3.1 beschrieben werden.

### **2.2.3. Test und Diagnose von Scan-Ketten**

Eine Scan-Kette kann von einem Defekt betroffen sein und muss getestet werden. Insbesondere für die Diagnose ist es wichtig zu wissen, ob und wo eine Scan-Kette defekt ist. Für den Produkttest ist die Scan-Kette aufgrund ihrer Test- und Diagnoseeigenschaften essentiell.

Sind Scan-Ketten fehlerbehaftet, dann können diese keine Testantwort liefern. Dadurch können nur statische Werte am Ende des Scan-Ausgangs gelesen werden. In einem solchen Fehlerfall ist die Observier- und Kontrollierbarkeit extrem eingeschränkt.

Ein Testverfahren für Scan-Ketten ist der sogenannte Flush-Test. Dieses Testverfahren schreibt vordefinierte Werte in die Scan-Kette und überprüft, ob diese nach einer berechneten Zeitspanne an den Ausgängen wieder gelesen werden können.

Charakteristische Sequenzen für verschiedene Fehlermodelle auf Transistorebene wurden untersucht [MM95]. Das untersuchte Fehlermodell beschränkt sich dabei nicht nur auf einfache Haftfehler, sondern es werden zum Beispiel auch Setup-/Hold-Zeitfehler getestet, bei denen ein Datum bei bestimmten Sequenzen einen Takt zu früh beziehungsweise zu spät übernommen wird. Der so ausgelesene Testvektor weist dann den Verlust oder die Wiederholung eines Bits auf.

Ein weiteres Verfahren zum Test und zur Diagnose besteht in der Nutzung der Systemlogik. Dazu werden Testmuster in die Scan-Kette eingeschoben und ein oder mehrere Takte lang der Systemtakt aktiviert, so dass die Muster auf der Scan-Kette durch das System verarbeitet werden. Anschließend wird die Scan-Kette ausgelesen und die Testdaten untersucht [SPM92].

Die Scan-Kette kann um entsprechende Teststrukturen erweitert werden, um die Diagnoseauflösung zu erhöhen. Ein solches Verfahren basiert auf dem Hinzufügen von XOR-Gattern auf dem Scan-Pfad [EE95]. Durch einen zusätzlichen Primäreingang gesteuert können diese bei Aktivierung alle auf dem Scan-Pfad propagierten Werte invertieren. Werden diese für einen Takt aktiviert, so sind alle Werte nach der Fehlerstelle invertiert, während alle nachfolgenden

## *2. Grundlagen des Hardware-Tests*

---

Werte weiter von der Fehlerwirkung beeinflusst sind. Aus der Länge der ausgelesenen und invertierten Werte lässt sich die Fehlerstelle präzise lokalisieren.

### **2.3. Abstraktionsebenen in der Modellierung**

Abstraktion ermöglicht ein einfacheres Verständnis eines Systems durch eine Reduktion der Komplexität unter Verlust an Genauigkeit. In dieser Arbeit werden verschiedene Abstraktionsebenen integrierter Schaltungen genutzt. Die Zusammenhänge zwischen diesen Ebenen, sollen im Folgenden kurz erläutert werden.

Es finden zwei Arten der Abstraktion statt. Zum einen die Räumliche, anhand derer die weitere Modellierung betrachtet werden soll. Bei dieser werden verschiedene einzelne Teile zu einem größeren Block abstrahiert und dann im weiteren Verlauf gemeinsam behandelt. Die andere ist die oft mit der räumlichen einhergehende zeitliche Abstraktion. Wurde durch die räumliche Abstraktion ein System soweit vereinfacht, wie etwa beim Übergang von kontinuierlichen zu diskreten Modellen, dass eine weitere Betrachtung einer kontinuierlichen Zeit unnötig erscheint, so sollte diese auch entsprechend abstrahiert werden.

Das Verhalten von Modulen wird häufig in Verilog oder VHDL definiert. Scan-Ketten können in ihren domänen-spezifischen Sprachen (engl. domain specific language, DSL) beschrieben werden, wie zum Beispiel BSDL [PO90].

#### **2.3.1. Gatterebene**

Die erste für diese Arbeit wichtige Abstraktionsebene, die Gatterebene, betrachtet einzelne kombinatorische Logikelemente und sequentielle Speicherelemente, sowie deren Interkonnektivität. Häufig besteht die Beschreibung eines solchen Netzwerks aus einer Gatternetzliste. Diese benennt neben jedem Gatter auch die Ein- und Ausgangs- sowie die Verbindungsleitungen und enthält zusätzlich die Angabe, wie jedes Element mit den anderen verbunden ist.

Der Vorteil auf dieser Ebene ist die Observierbarkeit einzelner Signale. Der Aufwand ist jedoch für die Simulation und Modellierung deutlich höher als in einem abstrakteren Modell.

#### **2.3.2. Register-Transfer-Ebene**

Auf der höher liegenden Register-Transfer-Ebene werden Gatter zu einzelnen Teilmodulen, beispielsweise eine ALU, zusammengefasst. Die Zeit ist taktgenau modelliert, d.h. die Kommunikation findet in Form von einzelnen Datenwerten statt.

### 2.3.3. Transaktionsebene

Auf der Transaktionsebene werden Kommunikationsabläufe in atomare Operationen zusammengefasst. Das bedeutet, dass die Kommunikation in Form von Lese- und Schreibzugriffen, sowie eventuelle Verarbeitungsschritte, als unteilbare Transaktion stattfindet. Dies abstrahiert die taktgenaue Kommunikation durch Signale der Register-Transfer- oder Gatterebene und reduziert so die nötigen Simulationsschritte.

## 2.4. Strukturelle Fehlermodelle

Fehlermodelle dienen der Abstraktion von Defekten, welche bei der Fertigung von Mikrochips auftreten. Es existiert eine Vielzahl verschiedener Fehlermodelle für unterschiedliche Verwendungszwecke. Diese decken jeweils eine spezifische Untermenge von physikalischen Defekten ab und sind nicht zwangsläufig disjunkt.

Ein Fehlermodell betrachtet eine Untermenge der spezifischen Fehlerausprägungen von Defekten, denn ohne diese Einschränkungen wären alle möglichen auftretenden Fehler denkbar. Dabei können unter Umständen nicht alle Ausprägungen von Defekten abgedeckt werden.

Wird ein strukturelles und deterministisches Fehlermodell für eine spezifische integrierte Schaltung betrachtet, so können alle möglichen Fehler in dieser aufgezählt werden. All diese Fehler in einer Menge zusammengefasst, ergeben die Fehlermenge für die entsprechende Schaltung.

Basierend auf einem Fehlermodell können entsprechende Testmuster erzeugt werden, die Fehler aktivieren und propagieren können. Mit den Testmustern kann geprüft werden, ob ein produzierter Mikrochip einen Fehler enthält oder fehlerfrei bezüglich des Fehlermodells ist.

### 2.4.1. Haftfehler

Ein sehr einfaches und sehr häufig eingesetztes Fehlermodell ist das Haftfehlermodell (engl. stuck-at fault model), welches auch die Grundlage für diese Arbeit bildet. Hier wird das Einfach-Haftfehlermodell betrachtet, welches ein Einfach-Fehlermodell ist, das heißt, es wird angenommen, dass immer nur genau ein einziger Fehler in der gesamten Schaltung beziehungsweise dem System auftritt.

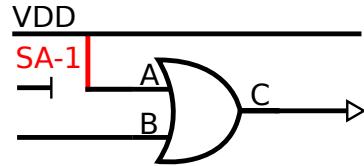

Im Haftfehlermodell sind die Defekte als Verbindungsfehler zwischen den Gattern modelliert. Eine Verbindungsleitung ist im Fehlerfall unterbrochen und propagiert statisch entweder eine logische Null (stuck-at-0, SA-0) oder eine logische Eins (stuck-at-1, SA-1). Physikalisch lässt sich dies als direkte Verbindung der Fehlerinjektionsstelle zu Masse oder der Versorgungsspannung erklären. Die Gatter selbst sind nicht von Fehlern betroffen, das heißt die Logikfunktionen bleiben erhalten.

## 2. Grundlagen des Hardware-Tests

---

Ein entsprechendes Beispiel ist in Abbildung 2.4 dargestellt. Die Verbindungsleitung am Eingang A des ODER-Gatters ist unterbrochen und propagiert nun statisch eine logische Eins.

**Abbildung 2.4.:** Beispiel eines Haftfehlers

Eingang A weist Haftfehler an 1 auf.

Aufgrund seiner Einfachheit lässt sich dieses Fehlermodell auf Gatterebene taktgenau sehr effizient simulieren. Ein weiterer Vorteil besteht in der relativ simplen Erzeugung von Testmustern. Da dieses Fehlermodell am häufigsten eingesetzt wird, stehen entsprechend viele und ausgereifte Werkzeuge bereit.

Trotz der Einfachheit deckt es dennoch ein großes Spektrum an physikalischen Fehlerklassen aus anderen Fehlermodellen ab [BARVT82]. Zu großen Teilen trifft dies auch auf Verzögerungsfehler zu, welche ein anderes Zeitverhaltens besitzen und eine dynamischere Fehlerwirkung aufweisen.

### 2.4.2. Brückenfehler

Beim Brückenfehlermodell werden zwei oder mehr Verbindungsleitungen miteinander verbunden und damit kurzgeschlossen, so dass Daten zwischen unabhängigen Einheiten sich gegenseitig beeinflussen können. Dies hat zur Folge, dass der Fehler selbst zwar statisch vorhanden ist, wie beim Haftfehlermodell, aber die Fehlerwirkung abhängig von der Aktivität an den Verbindungen ist. So können beispielsweise verschiedene Taktdomänen verbunden werden. Welcher Wert bei Kurzschluss unterschiedlicher Werte resultiert, hängt von der verwendeten Technologie, Treiberstärke, den Ohmschen Widerstand, etc. ab. Ein Beispiel ist in Abbildung 2.5 gezeigt.

**Abbildung 2.5.:** Beispiel eines Brückenfehlers

Zwei unabhängige Verbindungsleitungen wurden durch einen Brückenfehler verbunden

Brückenfehler zur Versorgungsspannung  $V_{DD}$  oder zur Masse  $V_{SS}$  entsprechen den einfachen Haftfehlern. Welcher Wert als Ergebnis des Kurzschlusses entsteht, wird in weiteren Unterklassen des Brückenfehlermodells definiert. Zum Beispiel ergibt sich beim Wired-AND-Modell eine Null, sobald eines der beiden Signale eine Null führt, während es beim Wired-OR zu einer Eins kommt, sobald eines der Signale eine Eins führt. Weitere Brückenfehler-Klassifikationen für CMOS finden sich in [ESBo].

#### **2.4.3. Weitere Fehlermodelle**

Die bisher aufgezählten Fehlermodelle gehen von einer statischen Änderung der Logikfunktion aus. Jedoch müssen in einer korrekten synchronen Schaltung die Datenworte auch rechtzeitig zur Abtastung an den Registereingängen zu den Taktflanken anliegen. Ist dies nicht der Fall, so werden falsche Werte gespeichert. Solche Fehler werden unter anderem in unterschiedlichen Verzögerungsfehlermodellen betrachtet [MA98]. Jedoch können auch solche Fehler teilweise durch das einfache Haftfehlermodell beschrieben werden [MBAB99].

Das Byzantinische Fehlermodell ist ein allgemeines Fehlermodell und nimmt eine höchstmögliche Störung des Systems an. Byzantinische Fehler werden in vielen Bereichen der Informatik betrachtet und haben ihren eigentlichen Ursprung im Zwei-Generäle-Problem der Verteilten Systeme [PSL80].

### **2.5. Fehlersimulation**

Zur Berechnung des Verhaltens einer integrierten Schaltung, kommen Simulationsmodelle zum Einsatz. Während des Entwurfs wird beispielsweise Logiksimulation zur funktionalen Validierung der Implementierung genutzt. Dahingegen wird bei der Testmustererzeugung die Fehlersimulation verwendet, welche dazu dient, einen Fehler in das Simulationsmodell einer Schaltung zu injizieren und dessen Auswirkung zu propagieren, um das Verhalten der fehlerhaften Schaltung zu untersuchen.

Die Eingabe für eine Fehlersimulation besteht aus einem Schaltungsmodell, Fehler- und einer Testmustermenge. Die Fehlersimulation untersucht dann für jeden Fehler, ob dieser von der Testmustermenge detektiert wird.

Fehlersimulation ist eine essentielle Aufgabe im Entwurf von Mikrochips und stellt aus diesem Grund einen wichtigen Forschungsbereich in der Technischen Informatik dar. Entsprechend ergiebig wurde dieser bereits untersucht und effiziente Verfahren entwickelt. Von diesen sollen nun ausgewählte Verfahren kurz vorgestellt werden.

### 2.5.1. Serielle Fehlersimulation

Bei der seriellen Fehlersimulation handelt es sich um ein sehr simples Verfahren: Zuerst wird die fehlerfreie Schaltung mit den Testmustern als Eingabe simuliert und die erzeugte Ausgabe gespeichert. Anschließend wird die fehlerbehaftete Schaltung mit den gleichen Eingaben simuliert und die Ausgabe mit der Gut-Simulation verglichen. Weichen die Ausgaben voneinander ab, so ist der Fehler durch die Testmuster detektierbar. Abbildung 2.6 zeigt einen möglichen Aufbau, bei dem Gut- und Fehlersimulation parallel ablaufen.

**Abbildung 2.6.:** Skizzierter Aufbau einer seriellen Fehlersimulation

Ein Vorteil dieser Methode ist die einfache Implementierung als doppelte Instantiierung, welche von einem Logiksimulator simuliert werden kann. Dadurch können je nach Fähigkeiten des Logiksimulators viele Fehlermodelle abgedeckt werden. Jedoch ist die Simulationszeit sehr hoch im Vergleich zu effizienten Fehlersimulationsalgorithmen, welche unter anderem ereignisgesteuert oder bitparallel rechnen.

### 2.5.2. Parallel Pattern Single Fault Propagation

Die Idee des PPSFP-Algorithmus besteht in der parallelen Simulation mehrere Werte der Schaltung in einem Datenwort, während gleichzeitig nur ein Fehler betrachtet wird. Darüber hinaus werden Fehler bei der Gebietsanalyse durch logisches Schließen effizient detektiert [Sch88].

Der PPSFP-Algorithmus lässt sich effizient auf Many-Core-Architekturen wie GPGPUs (General Purpose Graphical Processing Units), aufgrund seiner guten Parallelisierbarkeit, abbilden. Dadurch lässt sich die Simulationszeit bis zu einem Faktor 16 beschleunigen [KSWZ10].

### 2.5.3. Sequentielle Fehlersimulation

Bei der nebenläufigen Fehlersimulation (engl. concurrent fault simulation) werden die fehlerfreie, sowie alle fehlerbehafteten Schaltungen gleichzeitig ereignisgesteuert simuliert [UB73]. Dazu werden alle Gut- und Fehlerereignisse, das heißt eine Signaländerung an einem Gatter, an den Gattern selbst gespeichert. Die nebenläufige Fehlersimulation kann für verschiedene Schaltungsmodelle, unter anderem für sequentielle Schaltungen, Fehlermodelle und Zeitabstraktionen verwendet werden.

Die Differentielle Fehlersimulation bearbeitet ereignisgesteuert für ein Testmuster alle möglichen Fehler. Zunächst wird eine Gut-Simulation durchgeführt und anschließend Fehler nacheinander injiziert und simuliert. Bei abweichender Ausgabe wird ein Fehler als detektiert markiert und aus der Fehlerliste entfernt [LH92].

## 2.6. Automatische Testmustererzeugung

Automatische Testmustererzeugung (engl. automatic test pattern generation, ATPG) ist ein Sammelbegriff für Verfahren, welche der Erzeugung von Testmustern für Fehler in einer integrierten Schaltung dienen. Ein so erzeugtes Testmuster soll bei Anwendung den Fehler aktivieren, dessen Wirkung propagieren und so zu einem beobachtbaren, abweichenden Verhalten der fehlerbehafteten Schaltung im Gegensatz zur fehlerfreien Schaltung führen. Durch das abweichende Verhalten kann eine fehlerbehaftete Schaltung von einer fehlerfreien unterschieden werden. ATPG für kombinatorische Schaltungen und dem Haftfehlermodell gehört zur Klasse der NP-vollständigen Probleme, welche in Abschnitt 2.7.1 beschrieben werden und nach gegenwärtigem Stand der Forschung nicht effizient berechenbar sind.

Ein Beispiel für ATPG stellt der D-Algorithmus dar [Rot66]. Dieser beschreibt ein Verfahren zur Erzeugung von Testmustern für einfache Haftfehler. Der Ansatz basiert auf der Propagierung des Fehlers durch die Schaltung und Ableitung der daraus entstehenden Belegungen für die Primäreingänge durch logisches Schließen. Da unterschiedliche Belegungen möglich sind und Konflikte auftreten können, wird Backtracking genutzt, um diese durch zu probieren. Weitere Verbesserungen des D-Algorithmus stellen PODEM (path oriented decision making) als auch FAN (fanout-oriented test generation) dar, welche die Laufzeit reduzieren [GR81], [FS83].

Andere Verfahren reduzieren das Problem des ATPGs auf das Erfüllbarkeitsproblem der Aussagenlogik, welches in Kapitel 2.7 vorgestellt wird [Lar92], [TED10].

## 2.7. Erfüllbarkeitsproblem der Aussagenlogik

Das Erfüllbarkeitsproblem der Aussagenlogik (engl.: Boolean satisfiability-problem, SAT) stellt ein Entscheidungsproblem dar. Es überprüft, ob für die Variablen einer gegebenen

Boole'schen Funktion  $f(v_1, \dots, v_n) : \mathcal{B}^n \mapsto \mathcal{B}$  eine Belegung existiert, so dass  $f$  eine wahre Aussage ist [MMZ<sup>+</sup>01], [GN02].

Das Erfüllbarkeitsproblem, das klassische Beispiele für NP-Vollständigkeit, diente Stephen Cook zum Herleiten jener. Nachfolgend soll auf die NP-Vollständigkeit eingegangen werden, um die Komplexität der beschriebenen Probleme besser zu verstehen.

### 2.7.1. NP-Vollständigkeit

In der Komplexitätstheorie bezeichnet die Klasse  $NP$  alle Entscheidungsprobleme, welche von einer nichtdeterministischen Turingmaschine in polynomieller Zeit bezüglich der Eingabellänge  $n$  entschieden werden können. Eine besondere Teilmenge in  $NP$  bildet die NP-Vollständigkeit, welche von Stephen A. Cook 1971 beziehungsweise Levin postuliert wurde [Coo71], [Lev73]. NP-vollständige Entscheidungsprobleme lassen sich untereinander, mittels sogenannter Polynomialzeitreduktion  $\preceq_p$ , aufeinander abbilden. Eine Polynomialzeitreduktion  $r$  ist eine Abbildung, welche eine Instanz eines Entscheidungsproblems  $P$  in eine andere Instanz des Problems  $Q$  transformiert. Die Lösung für die Instanz des Problems in  $Q$  ist dann auch die Lösung für das Problem in  $P$ .

Ein Problem  $L$  ist NP-schwer (engl. NP-hard), wenn es mindestens so „schwer“ wie alle anderen Probleme in  $NP$  ist. Formal muss dafür jedes Problem  $K \in NP$  mittels einer Polynomialzeitreduktion durch  $L$  lösbar sein, das heißt:

$$(2.3) \quad L \in NP \Leftrightarrow \forall K \in NP : L \preceq_p K$$

Ist  $L$  zusätzlich in  $NP$  selbst, dann gehört  $L$  zur Klasse der NP-vollständigen Probleme.

### 2.7.2. Aussagenlogische Normalformen

Für eine gegebene Boole'sche Funktion kann es mehrere Repräsentationen geben. Im Laufe der Zeit wurden verschiedene Repräsentationformen, so genannte Normalformen, mit vorgegebenen Eigenschaften geschaffen. Eine Sonderform der Normalformen bilden kanonische Normalformen, welche strenger Kriterien genügen, so dass es eine eindeutige Repräsentation für jede Funktion gibt.

Eine wesentliche Normalform stellt hierbei die sogenannte konjunktive Normalform (engl. conjunctive normal form, CNF) dar. Bei dieser setzen sich Formeln aus Konjunktionstermen zusammen, welche wiederum aus Disjunktionstermen bestehen. Ein Disjunktionsterm wird aus Literalen, das heißt positive oder negierte Variablen, gebildet. Als Beispiel ist in Gleichung 2.4 das Übertragsbit eines Volladdierers in CNF angegeben.

$$(2.4) \quad \begin{aligned} c_{out} &= (\bar{a} \wedge b \wedge c_{in}) \vee (a \wedge \bar{b} \wedge c_{in}) \vee (a \wedge b \wedge \bar{c}_{in}) \vee (a \wedge b \wedge c_{in}) \\ &= (b \wedge c_{in}) \vee (a \wedge c_{in}) \vee (a \wedge b) \end{aligned}$$

Als Standard für die Eingabe benutzen die Werkzeuge zum Lösen aussagenlogischer Erfüllbarkeitsprobleme die konjunktive Normalform, da für diese effiziente Lösungsverfahren existieren [GZA<sup>+</sup>02].

Die Darstellung in konjunktiver Normalform alleine führt nicht zu einer eindeutigen Repräsentation, sie ist daher nicht kanonisch. Zur Bildung der kanonischen konjunktiven Normalform werden die Produktterme aus paarweise verschiedenen Maxtermen gebildet. Ein Maxterm oder Volldisjunktion ist ein Disjunktionsterm, welcher alle Variablen der Funktion enthält und entsprechend als Literale einbettet.

Jede aussagenlogische Formel kann in eine entsprechende konjunktive Normalform umgewandelt werden. Eine händische Möglichkeit besteht in der Aufstellung der Wahrheitstabelle und das Auslesen der entsprechenden Disjunktionsterme, für welche die Wahrheitstabelle einen wahren Wert in der Ergebnisspalte enthält. Allerdings benötigt die Aufstellung der Wahrheitstabelle für  $n$  Variablen bereits  $2^n$  Einträge und ist damit nicht effizient.

Zur Umwandlung in konjunktive Normalform können Logikäquivalenzumformungen, wie das Distributiv- oder De Morgan's-Gesetz genutzt werden. Shannons Aufzählungstheorem besagt, dass in der Regel kanonische Normalformen exponentiell länger sind als eine entsprechende freie Form der aussagenlogischen Formel [Sha49]. Es kann also vorkommen, dass zur Erzeugung der entsprechenden kanonischen Normalform exponentieller Aufwand benötigt wird und somit nicht effizient berechenbar ist.

Dies soll an folgendem Beispiel verdeutlicht werden. Gegeben sei die Formel f:

$$(2.5) \quad F \equiv \bigvee_{i=0}^n (X_i \wedge Y_i) \equiv (X_0 \wedge Y_0) \vee \dots \vee (X_{n-1} \wedge Y_{n-1})$$

Aus  $F$  lässt sich die äquivalente Gleichung  $G$  mittels Distributivgesetz in konjunktiver Normalform herleiten:

$$\begin{aligned} G &\equiv F \\ (2.6) \quad &\equiv \bigwedge_{i=0}^n \left( \bigvee_{k=0}^{n-i} (X_k) \bigvee_{k=n-i}^n (Y_k) \right) \\ &\equiv (X_0 \vee X_1 \vee \dots \vee X_{n-1}) \wedge (X_0 \vee X_1 \vee \dots \vee Y_{n-1}) \wedge \dots \wedge (Y_0 \vee Y_1 \vee \dots \vee Y_{n-1}) \end{aligned}$$

Während  $F$  lediglich  $2n$  Literale besitzt, gibt es nach Umformung in konjunktive Normalform nach 2.6 in  $G$   $2^n$  Literale. Um diesen Aufwand zu vermeiden, wird die Methode der Erfüllbarkeitsäquivalenzumformung genutzt. Die Gleichung ist nach einer solchen Umformung nicht mehr exakt äquivalent, sondern lediglich erfüllbarkeitsäquivalent, das heißt bei gleichen Eingabewerten für korrespondierende Variablen ergibt die Gleichung dieselbe Lösung. Eine solche Umformung ist die Tseitin-Umformung [Tse68]. Die Größe einer Formel bei den Tseitin-Umformungen wächst lediglich linear im Verhältnis zur Ausgangsgleichung.

### 2.7.3. Schaltungstransformation in konjunktive Normalform

Die Erzeugung von Zugriffsmustern für Rekonfigurierbare Scan-Netzwerke kann mittels des Erfüllbarkeitsproblems für aussagenlogische Gleichungen gelöst werden. Dazu wird die Schaltungsbeschreibung in Form einer Gatternetzliste in eine aussagenlogische Formel umgeformt.

Die Modellierung kombinatorischer Logik in konjunktiver Normalform lässt sich einfach durch statische Umformung durchführen. In Tabelle 2.1 sind für die gebräuchlichen Gatter die entsprechenden Terme in konjunktiver Normalform angegeben. Mit diesen kann der Schaltungsgraph traversiert und die einzelnen Knoten in einem CNF-Modell aufgebaut werden. Jeder Primärein- und -ausgang der Schaltung sowie das Ausgangssignal eines Gatters werden separate Variablen zugeteilt.

| Name           | Operation                   | CNF-Äquivalente Darstellung                                                                                                        |

|----------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Identität      | $C = A$                     | $(\bar{A} \vee C) \wedge (A \vee \bar{C})$                                                                                         |

| Negation       | $C = \bar{A}$               | $(\bar{A} \vee \bar{C}) \wedge (A \vee C)$                                                                                         |

| Konjunktion    | $C = A \wedge B$            | $(\bar{A} \vee \bar{B} \vee C) \wedge (A \vee \bar{C}) \wedge (B \vee \bar{C})$                                                    |

| Disjunktion    | $C = A \vee B$              | $(A \vee B \vee \bar{C}) \wedge (\bar{A} \vee C) \wedge (\bar{B} \vee C)$                                                          |

| Kontravalenz   | $C = A \oplus B$            | $(\bar{A} \vee \bar{B} \vee \bar{C}) \wedge (A \vee B \vee \bar{C}) \wedge (A \vee \bar{B} \vee C) \wedge (\bar{A} \vee B \vee C)$ |

| Äquivalenz     | $C = A \Leftrightarrow B$   | $(\bar{A} \vee \bar{B} \vee C) \wedge (A \vee B \vee C) \wedge (A \vee \bar{B} \vee \bar{C}) \wedge (\bar{A} \vee B \vee \bar{C})$ |

| Sheffer (NAND) | $C = \overline{A \wedge B}$ | $(\bar{A} \vee \bar{B} \vee \bar{C}) \wedge (A \vee C) \wedge (B \vee C)$                                                          |

| Peirce (NOR)   | $C = \overline{A \vee B}$   | $(\bar{A} \vee \bar{C}) \wedge (\bar{B} \vee \bar{C})$                                                                             |

| Implikation    | $C = A \rightarrow B$       | $(\bar{A} \vee B \vee \bar{C}) \wedge (A \vee C) \wedge (\bar{B} \vee C)$                                                          |

Tabelle 2.1.: Logikprimitive umgeformt nach konjunktiver Normalform

Für sequentielle Schaltungen müssen die einzelnen Zeitabschnitte, wie zum Beispiel Takte, modelliert werden. Dies kann durch Ausrollen, das heißt mehrfaches Instantiieren und durch Erweitern mit zusätzlichen Transitionsklauseln, geschehen. Diese Transitionsklauseln modellieren dabei den Übergang der Daten einzelner Speicherelemente zwischen zwei Zeitabschnitten. Die Primäreingänge werden dabei ebenfalls ausgerollt, so dass in jedem Zeitabschnitt neue Daten an die Schaltung angelegt werden können. Das fiktive Anlegen im Erfüllbarkeitsproblem geschieht durch Festlegung als positives oder negatives Literal für die jeweilige Variable des Zeitabschnitts. Ebenso werden Variablen für die Primärausgänge ausgerollt und sind so in der berechneten Lösung zu finden.

## **3. Grundlagen Rekonfigurierbarer Scan-Netzwerke**

Ohne weitere Optimierungen wächst die Zugriffszeit von Scan-Ketten linear mit der Länge des Scan-Pfads. Dies ist besonders ineffizient im Zusammenhang mit der stetigen Verbesserung der Fertigungstechnologie, insbesondere der Integrationsdichte für moderne Mikrochips. Gordon E. Moore beobachtete die Gesetzmäßigkeit, welche als Moore's Gesetz bekannt ist, dass sich seit 1970 die Zahl der Transistoren ungefähr alle zwei Jahre verdoppelt [Moo98]. Da es sich dabei um ein exponentielles Wachstum handelt und die Zahl der Register ebenfalls entsprechend wächst, ist es offensichtlich, dass sich eine reine lineare Skalierung der Scan-Ketten als nicht effizient erweist. Der Vorteil von Rekonfigurierbaren Scan-Netzwerken besteht in einer effizienteren Zugriffszeit, welche sich aus der Möglichkeit des unabhängigen Zugriffs auf Instrumente, wie zum Beispiel Temperatursensoren, ohne das andere Teilmodule in den Testmodus versetzt oder anderweitig beeinflusst werden, ergibt.

Dieses Kapitel führt die Grundlagen Rekonfigurierbarer Scan-Netzwerke ein. Zu Beginn wird deren Aufbau und Struktur erläutert und die entsprechende Terminologie erklärt. Das anschließende Kapitel befasst sich mit der Modellierung eines Rekonfigurierbaren Scan-Netzwerks auf Transaktionsebene. Abschließend wird die Fehlerwirkung des Haftfehlermodells für Rekonfigurierbare Scan-Netzwerke diskutiert und spezielle Fehlermodelle auf Transaktionsebene betrachtet.

### **3.1. Aufbau und Struktur**

Rekonfigurierbare Scan-Netzwerke bilden einen generischen und skalierbaren Ansatz für den Zugriff auf Teilmodule und Instrumente integrierter Schaltungen. Wie bei Scan-Ketten werden sequentielle Speicherelemente durch Scan-Zellen ersetzt und von außen zugänglich gemacht, um so Kontrollier- und Observierbarkeit zu erreichen. Diese Scan-Zellen beziehungsweise Scan-Segmente befinden sich auf einer Zugriffsinfrastruktur, welche als ein gerichteter, azyklischer Graph (engl. directed, acyclic Graph, DAG) dargestellt werden kann. Durch die flexible Infrastruktur kann der Zugriff auf einzelne Teilmodule effizienter gestaltet werden als mit einer simplen linearen Verkettung.

In diesem Graphen werden die Scan-Zellen als Knoten dargestellt und Kanten bilden einfache Scan-Pfade ab. Ein Scan-Pfad stellt einen Pfad durch den Graphen vom Eingangsknoten bis zum Ausgangsknoten dar.

### 3. Grundlagen Rekonfigurierbarer Scan-Netzwerke

Zu jedem Zeitpunkt kann es nur einen einzigen Pfad durch den Graphen geben, welcher dann ähnliche Eigenschaften, wie eine Scan-Kette, aufweist. Um dies zu erreichen, besitzen Knoten beziehungsweise Scan-Zellen mit mehreren Vorgängern Multiplexer zur Auswahl eines Vorgängers. Der sich so ergebende Pfad wird als aktiver Scan-Pfad bezeichnet.

Welcher Scan-Pfad aktiv ist, ergibt sich aus der Konfiguration des Rekonfigurierbaren Scan-Netzwerkes. Abbildung 3.1 zeigt ein Beispiel eines Rekonfigurierbaren Scan-Netzwerks mit hervorgehobenen aktivem Scan-Pfad. Als Konfiguration wird der Zustand der Register bezeichnet, welche zur Steuerung der Multiplexer dienen. Diese Konfigurationsregister liegen auf der Zugriffsinfrastruktur selbst und werden, genau wie der Zugriff auf Module, durch den Schiebevorgang des Scan-Pfads kontrolliert. Dadurch können sowohl Schreib- als auch Lesevorgänge ausgeführt werden. Die Ansteuerung der Zugriffsinfrastruktur kann dabei die gleichen Anschlüsse wie Scan-Ketten nutzen. Bei JTAG wird dies als TAP (test access port) bezeichnet, womit bestehende Testwerkzeuge weiter genutzt werden können.

**Abbildung 3.1.:** Beispiel eines Rekonfigurierbaren Scan-Netzwerks

Der aktive Scan-Pfad (blau) wurde hervorgehoben. Das erste Scan-Segment entspricht einem Konfigurationsregister, da dessen Wert die Einstellung des Multiplexers steuert.

Als Scan-Pfad-Segment wird ein Pfad zwischen zwei Scan-Segmenten bezeichnet. Dieses entspricht einer Kante des DAG.

Ein Scan-Pfad ist symmetrisch zu einem anderen Scan-Pfad genau dann, wenn beide Scan-Pfade die gleiche Anzahl von Scan-Segmenten aufweisen. Die Scan-Pfade des in Abbildung 3.1 skizzierten Rekonfigurierbaren Scan-Netzwerks sind alle symmetrisch.

Die Berechnung der Stimuli für die Zugriffsinfrastruktur, um die Modulauswahl von einer Konfiguration in eine vorgegebene Konfiguration zu überführen, wird als Retargeting bezeichnet. Ein solches Muster zur Rekonfiguration heißt Zugriffsmuster.

Teilmodule können beliebig gewählt werden, allerdings scheint eine Auswahl nach einzelnen Komponenten, wie beispielsweise die ALU eines Prozessors, die BIST-Steuerung eines Speichers oder eine Gruppe von Instrumenten, als sinnvoll. IP-Cores von SOCs besitzen häufig bereits eine eigene Testschnittstelle, welche daher als Teilmodule sehr gut geeignet sind. Tatsächlich findet dies Anwendung in dem in Kapitel 2.2.2 beschriebenen Standard IEEE 1500

„Embedded Core Test“. Schaltungen nach diesem Standard können als Rekonfigurierbares Scan-Netzwerk betrachtet werden. Die Testschnittstelle der einzelnen Module ermöglicht es, diese durch den Scan-Pfad zugreifbar zu machen oder vom Scan-Pfad abzukoppeln. Dadurch ist der Scan-Pfad nicht mehr rein statisch, sondern veränderbar und bildet damit ein Rekonfigurierbares Scan-Netzwerk.

Eine Normierung zum Zugriff auf die Instrumente einer integrierten Schaltung ist derzeit in der Entstehung als IEEE P1687 „Instrument JTAG“ (IJTAG) [EBo6]. In dieser Normierung wird unter anderem die Nutzung von Rekonfigurierbaren Scan-Netzwerken zum Zugriff auf die Instrumente vorgeschlagen.

### 3.1.1. Struktur von Scan-Segmenten

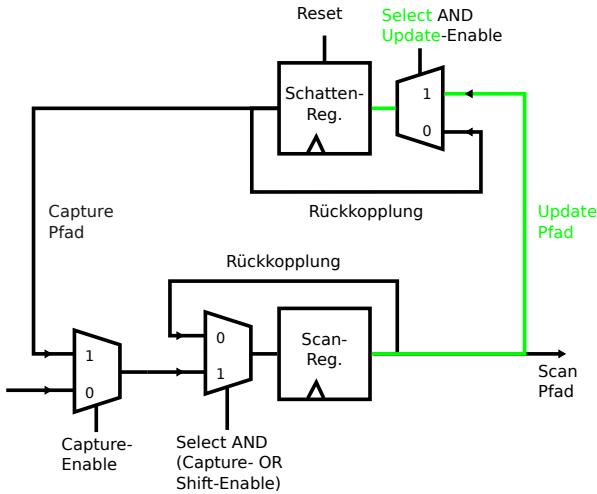

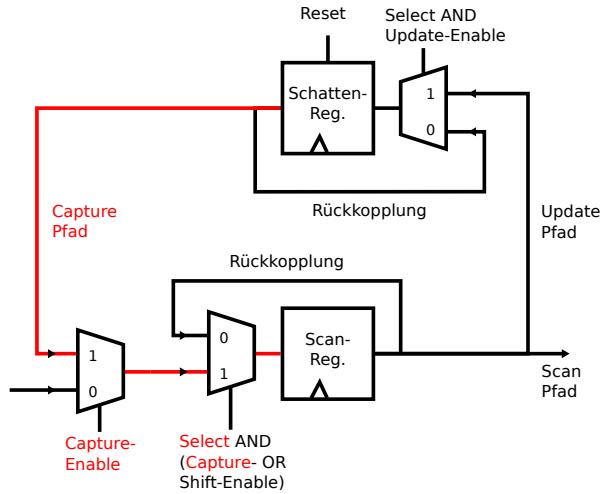

Scan-Segmente, welche als Konfigurationsregister dienen, benötigen ein zusätzliches Schattenregister, welches den gespeicherten Inhalt während des Schiebebetrags erhält. Ansonsten würden sich die Steuersignale der Kontrolllogik während des Schiebebetrags verändern und dadurch auch der aktive Scan-Pfad anders ausprägen. Eine solche Struktur wird bei Scan-Ketten als „Enhanced Scan“ bezeichnet. Eine Beispielinstanz ist in Abbildung 3.2 skizziert.

**Abbildung 3.2.:** Beispiel eines Scan-Segments und zugehöriger Daten- und Kontrollpfade

Der Scan-Pfad (blau) wurde hervorgehoben.

Jedes Scan-Segment besitzt eine Aktivierungsbedingung in Form des Select-Signals. Dieses muss aktiv sein, sofern sich das Scan-Segment auf dem aktiven Scan-Pfad befindet und das

### 3. Grundlagen Rekonfigurierbarer Scan-Netzwerke

---

Rekonfigurierbare Scan-Netzwerk eine Operation ausführen soll. Das Select-Signal wird kombinatorisch aus den Konfigurationsregistern erzeugt.

Die Daten aus einem Scan-Register werden in das Schattenregister übernommen, genau dann, wenn die Signale Update-Enable und Select aktiv sind. Diese werden in Abbildung 3.3 entsprechend dargestellt. Dazu werden die Multiplexer so getrieben, dass der Update-Pfad aktiviert wird.

**Abbildung 3.3.:** Beispiel der aktiven Pfade und Signale (grün) in einem Scan-Segment während der Update-Phase. Der aktive Rückkopplungsdatenpfad des Scan-Registers wurde nicht explizit hervorgehoben.

Bei einer Capture-Operation wird das Datum des Schattenregisters in das Scan-Register übertragen und dient damit dem Auslesen des Zustands des Rekonfigurierbaren Scan-Netzwerks. Die Capture-Operation wird durch setzen des Capture-Enable- sowie Select-Signals erreicht, wie es in Abbildung 3.4 gezeigt ist.

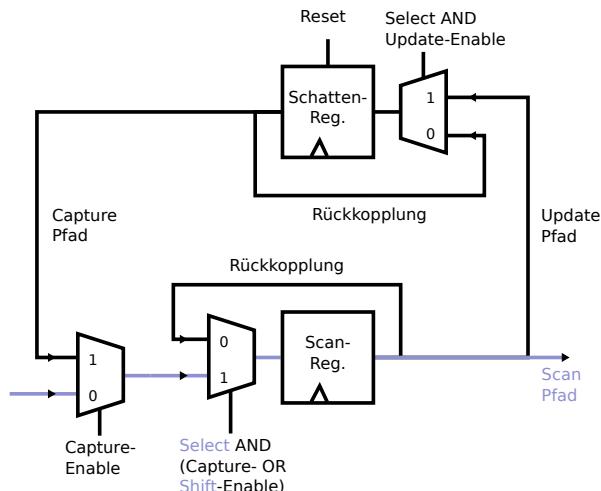

Der Schiebemodus wird durch das Aktivieren des Shift-Enable- und des Select-Signals erreicht, welches in Abbildung 3.5 skizziert wird. Hierbei übernimmt das Scan-Register die Daten von seinem Vorgänger auf dem aktiven Scan-Pfad.

#### 3.1.2. Scan-Pfadzugriff (CSU-Zyklus)

Ein Zugriff auf ein Rekonfigurierbares Scan-Netzwerk läuft, wie bei Scan-Ketten nach JTAG, in CSU-Zyklen ab. Ein CSU-Zyklus umfasst dabei das Übertragen der Werte aus dem Schattenregister zu den Scan-Registern (Capture) sowie das Herausschieben der Konfigurationsdaten und Hineinschieben von Daten in Form einer neuen Konfiguration (Shift). Wenn die neuen Daten beziehungsweise Konfiguration in die Scan-Register geschoben wurden, werden die Daten durch die Update-Operation in die Schattenregister übernommen (Update).

**Abbildung 3.4.:** Beispiel der aktiven Pfade und Signale (rot) in einem Scan-Segment während der Capture-Phase. Der aktive Rückkopplungsdatenpfad des Schattenregisters wurde nicht explizit hervorgehoben.

**Abbildung 3.5.:** Beispiel der aktiven Pfade und Signale (blau) in einem Scan-Segment während der Scan-Phase. Der aktive Rückkopplungsdatenpfad des Schattenregisters wurde nicht explizit hervorgehoben.

## 3.2. Modellierung auf Transaktionsebene

Die taktgenaue Modellierung eines Rekonfigurierbaren Scan-Netzwerks führt zu einem hohen Aufwand aufgrund der sequentiellen Tiefe dieser Schaltungen. Deshalb werden Rekonfigurierbare Scan-Netzwerk hier auf Transaktionsebene modelliert, so dass einzelne

### *3. Grundlagen Rekonfigurierbarer Scan-Netzwerke*

---

getaktete Schiebeoperationen nicht notwendig sind und eine Effizienzsteigerung bei der Rechenzeit erreicht wird.

In dieser Modellierung entspricht eine Transaktion einem vollständigen CSU-Zyklus, wie er in Kapitel 3.1.2 beschrieben wurde. In einer Transaktion wird der zugreifbare Zustand eines Rekonfigurierbaren Scan-Netzwerkes, das heißt alle Scan-Elemente auf dem aktiven Scan-Pfad, neu geschrieben. Damit überführt eine Transaktion die Konfiguration eines Rekonfigurierbaren Scan-Netzwerks in eine neue Konfiguration, welche sich nur auf dem aktiven Scan-Pfad unterscheidet. Dabei ändert sich die Ausprägung des aktiven Scan-Pfads entsprechend der neuen Konfiguration.

Eine CSU-Operation entspricht dabei nur einem Simulationsschritt im Modell auf Transaktionsebene, da sowohl die Capture-, Shift- sowie die Update-Operationen nicht explizit modelliert werden. Hingegen hängt die Anzahl der Schritte im taktgenauen Modell von der Länge des aktiven Scan-Pfads ab und ist damit variabel, was die Modellierung als Instanz des Erfüllbarkeitsproblems erschwert. Die Zahl der Zyklen zur Rekonfiguration beträgt  $n + 2$  Schritte, wenn der aktive Scan-Pfad  $n$  Scan-Segmente aufweist. Die mögliche Zustandsmenge kann daher auf Transaktionsebene wesentlich kleiner und damit effizienter in Rechenzeit und Speicherplatzbedarf simuliert werden.

#### **3.2.1. Modellierung von Scan-Segmenten**

Auf Transaktionsebene werden Scan- und Schattenregister als ein speicherndes Element in Form eines Scan-Segments betrachtet. Es wird angenommen, dass in einer Transaktion aktive Scan-Segmente gelesen und beschrieben werden können. Hierdurch kann der Zugriff auf den aktiven Scan-Pfad als ein einzelner Lese- und Schreibzugriff betrachtet werden.

#### **3.2.2. Modellierung der Scan-Pfadaktivierung**

Zur Erzeugung von Zugriffsmustern in Rekonfigurierbaren Scan-Netzwerken ist es notwendig zu gewährleisten, dass ein vollständig konsistenter und aktiver Scan-Pfad existiert. Dies ergibt sich aus der Konfiguration und der Kontrolllogik, welche auch auf Transaktions-ebene als Boole'sche Funktion modelliert ist.

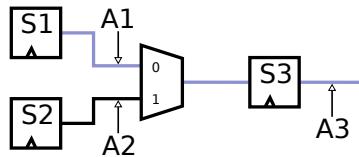

Wie auf der Register-Transfer-Ebene, besitzen die Scan-Segmente auf Transaktionsebene eine Aktivierungsbedingung, welche das Speichern neuer Werte ermöglicht. Diese ist aktiv oder wahr, sofern sich das Scan-Segment auf dem aktiven Scan-Pfad befindet. Zusätzlich gilt, dass wenn ein Scan-Segment aktiv ist, dann müssen auch genau ein eingehendes Scan-Pfad-Segment und genau ein ausgehendes Scan-Pfad-Segment aktiviert sein. Andernfalls würde kein oder mehr als ein aktiver Scan-Pfad ausgeprägt werden, was verboten ist. Abbildung 3.6 zeigt die entsprechenden Aktivierungsvariablen an Scan-Pfad-Segmenten in einem Rekonfigurierbaren Scan-Netzwerk.

**Abbildung 3.6.:** Beispiel der Aktivierungsvariablen auf Transaktionsebene

Die Aktivierungsbedingungen  $A_1$  und  $A_3$  der Scan-Pfad-Segmente auf dem aktiven Scan-Pfad (blau) müssen erfüllt sein. Die Aktivierungsbedingung  $A_2$  des Scan-Segments auf einem inaktiven Scan-Pfad-Segment muss hingegen inaktiv sein.

Die in Kapitel 3.1.1 beschriebenen Aktivierungssignale werden daher als Boole'sche Formel modelliert. Gleichung 3.1 beschreibt die Aktivierung eines Scan-Segments. Ein Scan-Segment  $S$  ist aktiv, wenn die Boole'sche Aktivierungsbedingung  $A$  erfüllt ist und ein Vorgänger  $V$  als auch ein Nachfolger  $N$  aktiv sind.

$$\begin{aligned}

\text{Aktiv}(S) \Leftrightarrow & A \text{ ist erfüllt} \wedge \\

(3.1) \quad & \exists V \in \text{Vorgänger}(S) : \text{Aktiv}(V) \wedge \\

& \exists N \in \text{Nachfolger}(S) : \text{Aktiv}(N)

\end{aligned}$$

### 3.3. Klassifizierung der Fehlerwirkung und Testbarkeit

In diesem Abschnitt werden Fehlerstellen für das einfache Haftfehlermodell klassifiziert und diese Fehlerklassen mit deren Fehlerwirkung beschrieben.

**Scan-Datenpfad** Liegt ein Fehler auf dem Datenpfad eines Scan-Pfads, so ist der Fehler unmittelbar aktiviert, sobald der Scan-Pfad in einer Konfiguration aktiv ist. Mittels eines Flush-Tests ist die Fehlerwirkung observierbar, da der Scan-Pfad ab einer bestimmten Stelle nur noch konstante Werte propagiert.

Diese Fehlerklasse kann dazu führen, dass die Schaltung nicht mehr kontrolliert werden kann, nachdem ein Fehler aktiviert wurde. Dies ist aber von geringer Bedeutung für den Test, da der Fehler erfolgreich nachgewiesen wurde. Jedoch wird die Diagnose in solch einem Fall aufgrund der geringen Sichtbarkeit erschwert.

**Scan-Steuerung** Befindet sich ein Fehler unmittelbar im Eingangskegel eines Scan-Datenpfads, hat nur Auswirkungen auf diesen und beeinflusst dessen Aktivierung, dann führt dies zu zwei unterschiedliche Auswirkungen.

Der Fehler kann einen eigentlich inaktiven Pfad sensibilisieren und so die Werte in einem Scan-Register verändern, was zu Datenverlust führen kann. Um dies zu detektieren müsste im Scan-Register am Ausgangspunkt des fälschlich aktiven Scan-Pfads der komplementäre Wert geschrieben werden. Das Scan-Pfad-Segment müsste daraufhin deaktiviert werden und später wieder ausgelesen werden.

Andernfalls kann ein aktiver Scan-Pfad deaktiviert werden, falls der Fehler einen kontrollierenden Wert an einem Gatter propagiert, so dass der Pfad gebrochen wird. Dieser Fall ist äquivalent zum gebrochenen Scan-Datenpfad.

**Scan-Adressierung** Wirkt sich ein Fehler auf mehrere unterschiedliche Scan-Pfade aus und beeinflusst deren gemeinsame, wenn auch komplementäre Aktivierung, so kann dies zur Vertauschung zweier Scan-Pfade führen. Bei unterschiedlichen Scan-Pfad-Längen kann dies durch den Flush-Test erkannt werden, bereitet aber bei gleicher Scan-Pfad-Länge Probleme.

In diesem Fall kann es sein, dass beide Scan-Pfade die gleichen Datenwerte enthalten und so nicht direkt voneinander unterschieden werden. Befinden sich Konfigurationsregister auf den betroffenen Scan-Segmenten, welche asymmetrische Scan-Pfade treiben, dann können diese genutzt werden um den eigentlich Fehler in der Adressierung festzustellen. Dazu müssten entsprechende Testmuster für die kontrollierten Scan-Pfad-Segmente erzeugt werden. Sind jedoch nur Scan-Pfade betroffen, die keine Kontrollregister ansteuern, so können eventuell angeschlossene Instrumente oder Systemlogik dazu genutzt werden, um die Scan-Pfad-Segmente voneinander zu unterscheiden.

**Capture-Datenpfad** Liegt die Fehlerstelle auf dem Capture-Datenpfad, so können keine Datenwerte vom Schattenregister zum Scan-Register übertragen werden, sondern nur ein statischer Wert. Dies lässt sich einfach testen, indem der komplementäre Wert in einer CSU-Operation  $O_1$  in das Scan-Register geschrieben wird und dieser vom fehlerhaften Wert in der nächsten CSU-Operation  $O_2$  überschrieben wird. Die Scan-Phase von  $O_2$  macht den Fehler anschließend an den Primärausgängen sichtbar.

**Capture-Steuerung** Ein Fehler in der Kontrolllogik des Capture-Pfads führt dazu, dass entweder der Pfad statisch desensibilisiert oder statisch aktiviert ist. Der erste Fall entspricht einem Fehler auf dem Capture-Datenpfad selbst. Beim statisch aktivierten Fall propagiert der Wert aus dem Schattenregister immer auf den Scan-Pfad zum Scan-Register. Dieser Fall ist testbar, wenn der kontrollierende Wert der Konvergenz der beiden Datenpfade im Schattenregister gespeichert ist und der nicht-kontrollierende Wert auf dem Scan-Pfad propagiert.

**Update-Datenpfad** Liegt der Fehler auf dem Update-Pfad selbst, so wird ein Schreiben eines abweichenden Wertes verhindert und somit das Erreichen einer bestimmten gewünschten Konfiguration verhindert. Dies lässt sich testen, indem der komplementäre Wert geschrieben und in einer folgenden CSU-Operation ausgelesen wird.

Die sequentielle Fehlerwirkung wird dadurch sichtbar, dass zum Beispiel ein Scan-Pfad nicht aktiviert wird, weil der entsprechende Wert der Konfiguration nicht gesetzt werden kann. Der Fehler kann daher durch einen abweichend von dem geforderten gewählten Scan-Pfad erkannt werden.

**Update-Steuerung** Ein Fehler in der Ansteuerung eines Update-Pfads kann, wie bei den bisher betrachteten Kontrolllogiken auch, den entsprechenden Datenpfad statisch aktivieren oder deaktivieren. Bei Deaktivierung lässt sich der fehlerhaft gespeicherte Wert

durch eine Update-Operation, welche den komplementären Wert schreibt, aktivieren. Eine Capture-Operation überführt den Wert in das Scan-Register, von wo aus der Schieberegister den Fehler ausliest.

Die Fehlerwirkung eines statisch aktiven Update-Pfads ist sehr interessant, da diese von der Aktivität des Scan-Pfads abhängt. Dabei kann sich der aktive Scan-Pfad ständig verändern und neu ausprägen.

**Rückkopplungsdatenpfad** Befindet sich der Fehler auf dem Rückkopplungspfad eines Registers, so ist die Speicherfähigkeit des Registers reduziert und beschränkt sich auf einen einzelnen Wert, falls es sich um den nicht-kontrollierenden Wert der Konvergenz der Datenpfade handelt. Das Register kann, wenn es beschrieben wird, den Wert nur für einen Takt halten, sofern es nicht erneut beschrieben wird.

Scan-Register können nur getestet werden, indem das Select-Signal während des Schieberegisters deaktiviert wird. Andernfalls wird in der Capture-Phase der fehlerhafte Wert überschrieben und während dem Schieberegister werden ständig neue Daten gespeichert, so dass kein Wert aufgrund des Fehlers verloren gehen würde.

Fehlerhaften Daten können bei Schattenregistern nach einer Capture-Operation ausgelesen werden. Jedoch kann dies auch zu einer Veränderung des aktiven Scan-Pfads führen, wodurch eventuell ein falscher Pfad ausgelesen würde.

Besteht der Fehler aus dem kontrollierenden Wert der Konvergenz, so propagiert kein anderer Wert zum Register. Daher ist das Register nicht funktional und kann durch Lese- und Schreibzugriffe einfach getestet werden.

**Rückkopplungssteuerung** Beeinflusst der Fehler die Kontrolllogik des Rückkopplungspfads eines Scan- als auch Schattenregisters, so dass der Datenpfad statisch desensibilisiert ist, dann propagiert über den Rückkopplungsdatenpfad nur noch ein konstanter Wert, und es handelt sich um die entsprechende statische Fehlerklasse eines Rückkopplungsdatenpfads.

Wird hingegen ein Rückkopplungsdatenpfad statisch sensibilisiert, so tritt an der Konvergenz der Datenpfade immer der kontrollierende Wert auf, sobald er einmal propagierte. Das Register speichert den kontrollierenden Wert und propagiert über den Rückkopplungsdatenpfad wieder an die Konvergenz. Da es sich um den kontrollierenden Wert handelt, wird er wieder im Register gespeichert. Da die Fehlerwirkung statisch auftritt, sobald sie einmal aktiviert ist, ist diese Fehlerklasse einfach zu testen. Die Fehlerwirkung lässt sich durch einfachen Zugriff auf das Scan-Segment sichtbar machen.

**Taktverteilung** Fehler, welche die Taktverteilung beeinflussen, führen dazu, dass ein oder mehrere Register nicht funktional sind und keine Daten speichern oder weiterleiten können. Diese Fehlerklasse lässt sich sehr gut testen. Für Scan-Register ist die Fehlerwirkung äquivalent zu einem Fehler direkt auf dem Scan-Datenpfad und für Schattenregister äquivalent zum Capture-Datenpfad.

**Reset-Steuerung** Betrifft ein Fehler die Reset-Steuerung in der Art, dass ein oder mehrere Register nicht in ihren Initialzustand zurückgesetzt werden können, dann enthalten diese möglicherweise einen abweichenden Wert. Dieser Fehler wird nur aktiviert, falls vor dem Reset in den betroffenen Registern der komplementäre Wert gespeichert ist.

Eine Folge der fehlerhaften Konfiguration kann darin bestehen, dass ein inkorrekt Pfad nach dem Reset als aktiver Scan-Pfad ausgeprägt wird. Befindet sich ein zugehöriges Scan-Segment auf dem aktiven Scan-Pfad, so wird der Fehler unmittelbar nach der ersten CSU-Operation als abweichender Wert sichtbar.

Ebenfalls ist es möglich, dass eine ungültige Konfiguration durch den fehlerhaften Reset erreicht werden kann. Dies führt zu einem nicht funktionsfähigen oder mehreren aktiven Scan-Pfaden, welche einfach testbar sein sollten. Jedoch ist es dafür notwendig, dass das betroffene Modul aktiviert wird.

Scan-Register besitzen keine Steuerung für den Reset, denn durch die erste Capture-Operation werden gültige Daten aus den Schattenregistern in die Scan-Register geschrieben. Würden diese zurücksetzbar sein, so wären die Fehler aus diesem Grund an Scan-Registern nicht detektierbar.

Eine weitere Möglichkeit der Fehlerwirkung besteht im ständig aktiven Reset, wodurch die betroffenen Register nicht mehr funktional sind. Dies ist ein äquivalenter Fall zu einem Fehler in der Taktverteilung.

### 3.4. Funktionale Fehlermodelle auf Transaktionsebene

Das Einfache-Haftfehler-Modell eignet sich gut für Fehler auf Gatterebene, ist jedoch auf der Transaktionsebene, wie sie bei der CSU-Zyklen-Abstraktion betrachtet wird, schwierig anwendbar, da einige strukturelle beziehungsweise funktionale Teile der Schaltung nicht betrachtet werden. Dies umfasst im Wesentlichen die explizite Modellierung der Capture- und Update-Pfade, als auch die Rückkopplungsdatenpfade der speichernden Elemente. Daher sollen in diesem Kapitel drei mögliche funktionale Fehlermodelle beschrieben werden.

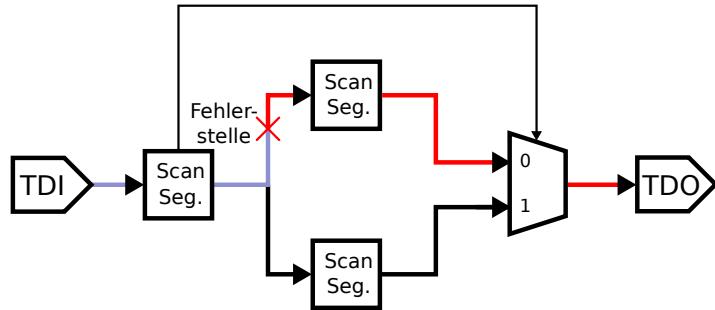

**Gebrochener Scan-Pfad** Besteht die Fehlerwirkung in der Deaktivierung eines Scan-Pfad-Segments des aktiven Scan-Pfads, so kann ab der Fehlerstelle nur noch der konstante Wert der Fehlerwirkung ausgelesen beziehungsweise in nachfolgende Segmente geschrieben werden. Ein solcher Fehler kann Zugriffe auf ein Rekonfigurierbares Scan-Netzwerk so beeinflussen, dass dieses bis zu einem Reset unbrauchbar ist, falls der Fehler nur noch Konfigurationen zulässt, welche aufgrund der Fehlerwirkung keinen Scan-Pfad aktivieren. Dies kann relevant für eine spätere Diagnose sein.

**Abbildung 3.7.:** Beispiel eines gebrochenen Scan-Pfads (rot)

Der Scan-Pfad ist an der Fehlerstelle unterbrochen und Werte propagieren nicht mehr weiter. Stattdessen wird nur noch ein konstanter Wert propagiert.

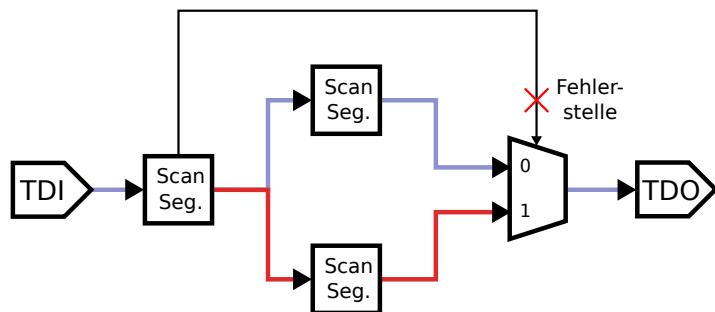

**Falscher Scan-Pfad** Beeinflusst die Fehlerwirkung die Ansteuerung eines Scan-Multiplexers, so besteht die Möglichkeit, dass statt dem eigentlich konfigurierten Scan-Pfad ein anderer Scan-Pfad aktiviert wird. Auf Transaktionsebene wirkt sich dies als Auswahl eines anderen Pfads durch den Graphen aus. Dabei sind die Gültigkeitsbedingungen immer noch erfüllt, das heißt es wird nur ein aktiver Scan-Pfad ausgeprägt.

**Abbildung 3.8.:** Beispiel eines fälschlich aktiven Scan-Pfads (rot)

Der eigentlich ausgewählte blaue Scan-Pfad ist aufgrund des Fehlers nicht aktiv. Durch die Fehlerwirkung wurde stattdessen der rote Scan-Pfad aktiviert.

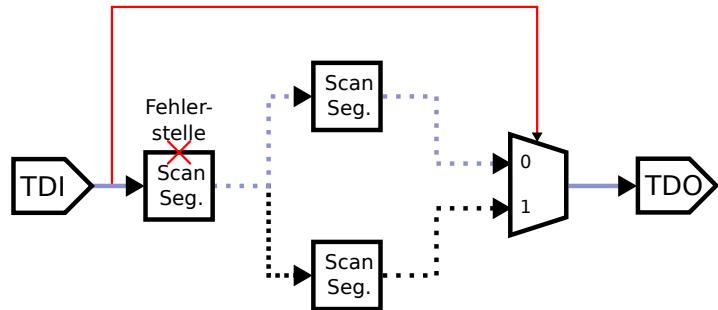

**Instabiler Scan-Pfad** Angenommen die Kontrolllogik eines Update-Pfads auf Gatterebene sei so betroffen, dass ein Schattenregister in jedem Takt den Wert aus dem Scan-Register übernehme. Dann basiert die Ausprägung eines aktiven Scan-Pfads auf den propagierenden Datenwerten auf dem Scan-Pfad und nicht mehr auf den durch CSU kontrollierten Datenwerten eines Konfigurationsregisters. Dadurch verändert sich der aktive Scan-Pfad entsprechend der Aktivität auf dem entsprechenden Scan-Pfad-Segment. Diese Fehlerannahme führt zu einem pseudo-dynamischen Verhalten auf Transaktionsebene, so dass ab der Fehlerstelle lediglich pseudo-zufällige Daten gelesen und geschrieben werden können.

**Abbildung 3.9.:** Beispiel eines instabilen aktiven Scan-Pfads (schraffiert)

Die Kontrolllogik des Scan-Multiplexers wird nicht mehr aus einem stabilen Konfigurationsregister gesteuert, daher prägt sich der aktive Scan-Pfad basierend auf der Aktivität des Scan-Pfads aus.

## 4. Testalgorithmen für Rekonfigurierbare Scan-Netzwerke

In diesem Kapitel wird ein Überblick über unterschiedliche Testalgorithmen für Rekonfigurierbare Scan-Netzwerke geben. Zuerst wird die Möglichkeit eines pseudo-zufälligen Tests diskutiert. Darauf folgen zwei funktionale Testheuristiken, welche zum einen aus einem einmaligen Zugriff auf alle Scan-Segmente besteht und zum anderen die Funktionalität der Scan-Segmente betrachtet. Abschließend werden weitere Testalgorithmen vorgeschlagen, welche insbesondere in Hinblick auf die Bedürfnisse einer schnellen Testmustererzeugung für Rekonfigurierbare Scan-Netzwerke entwickelt worden sind.

### Flush-Test

Ziel des Flush-Tests ist festzustellen, ob der Scan-Pfad Daten unverfälscht schiebt. Dieser findet in den folgenden Testalgorithmen Anwendung.

Bei einfachen Haftfehlern ist es ausreichend, dass beide Logikwerte 0 und 1 durch den Scan-Pfad propagieren. Dabei können kombinatorische Fehler aktiviert und deren Fehlerwirkung propagiert werden, welche auf dem aktiven Scan-Pfad liegen oder dessen Kontrolllogik beeinflussen.