Institut für Parallele und Verteilte Systeme

Universität Stuttgart

Universitätsstraße 38

D–70569 Stuttgart

Diplomarbeit Nr. 3070

## **Hardware Implementierung eines parallelen Entropie Koders**

Maximiliano Keller

**Studiengang:** Informatik

**Prüfer:** Prof. Dr.-Ing. Sven Simon

**Betreuer:** Dipl.-Inf. Simeon Wahl

**begonnen am:** 26. Juli 2010

**beendet am:** 25. Januar 2011

**CR-Klassifikation:** E4, B.2.1, F.2.0

# Inhaltsverzeichnis

|                                                                                                     |           |

|-----------------------------------------------------------------------------------------------------|-----------|

| <b>Abstract</b>                                                                                     | <b>7</b>  |

| <b>1 Einleitung</b>                                                                                 | <b>9</b>  |

| <b>2 Arithmetisches Kodieren</b>                                                                    | <b>11</b> |

| 2.1 Grundlagen . . . . .                                                                            | 11        |

| 2.1.1 Motivation . . . . .                                                                          | 11        |

| 2.1.2 Prinzip . . . . .                                                                             | 13        |

| 2.2 Kodierung als reelle Zahl . . . . .                                                             | 19        |

| 2.3 Dekodierung als reelle Zahl . . . . .                                                           | 20        |

| 2.4 Beweis der Eindeutigkeit . . . . .                                                              | 21        |

| 2.5 Effizienz . . . . .                                                                             | 23        |

| 2.6 Kodierung als begrenzte Festkommazahl . . . . .                                                 | 24        |

| 2.6.1 Abbildung auf Ganze Zahlen . . . . .                                                          | 24        |

| 2.6.2 Skalierung bei Überlauf . . . . .                                                             | 26        |

| 2.6.3 Skalierung bei Unterlauf . . . . .                                                            | 28        |

| 2.7 Dekodierung als begrenzte Festkommazahl . . . . .                                               | 34        |

| <b>3 Parallelisierung</b>                                                                           | <b>37</b> |

| 3.1 Parallelisierung nach J. Jiang und S. Jones . . . . .                                           | 38        |

| 3.1.1 Einleitung . . . . .                                                                          | 38        |

| 3.1.2 Prinzip . . . . .                                                                             | 39        |

| 3.1.3 Normalisierung . . . . .                                                                      | 42        |

| 3.1.4 Stark unterschiedliche Häufigkeiten . . . . .                                                 | 43        |

| 3.2 Parallelisierung nach J. Šupol und B. Melichar . . . . .                                        | 43        |

| 3.2.1 Einleitung . . . . .                                                                          | 43        |

| 3.2.2 Prinzip . . . . .                                                                             | 44        |

| 3.2.3 Beispiel . . . . .                                                                            | 46        |

| 3.2.4 Parallelisierung . . . . .                                                                    | 47        |

| 3.3 Parallelisierung nach Horg-Yeong Lee, Leu-Shing Lan, Ming-Hwa Sheu und Chien-Hsing Wu . . . . . | 49        |

| 3.3.1 Einleitung . . . . .                                                                          | 49        |

| 3.3.2 Prinzip . . . . .                                                                             | 49        |

| 3.4 Konklusion . . . . .                                                                            | 50        |

| 3.4.1 Gleichungen für Parallelisierung . . . . .                                                    | 50        |

| 3.4.2 Präzision . . . . .                                                                           | 52        |

| 3.4.3 Algorithmus für Skalierung . . . . .                                                          | 54        |

|                             |                                               |            |

|-----------------------------|-----------------------------------------------|------------|

| 3.5                         | Parallelisierung in Hardware . . . . .        | 57         |

| 3.5.1                       | CUDA . . . . .                                | 58         |

|                             | Architektur . . . . .                         | 58         |

|                             | Implementierung . . . . .                     | 58         |

| 3.5.2                       | VHDL . . . . .                                | 59         |

|                             | Algorithmus . . . . .                         | 60         |

| <b>4</b>                    | <b>Implementierung</b>                        | <b>61</b>  |

| 4.1                         | Referenz Beispiel . . . . .                   | 61         |

| 4.2                         | Struktur . . . . .                            | 65         |

| 4.3                         | Incrementer . . . . .                         | 66         |

| 4.4                         | RAM . . . . .                                 | 67         |

| 4.5                         | Parallel Loader . . . . .                     | 67         |

| 4.6                         | Parallel Koder . . . . .                      | 69         |

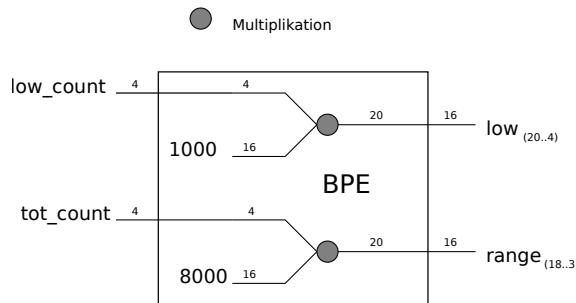

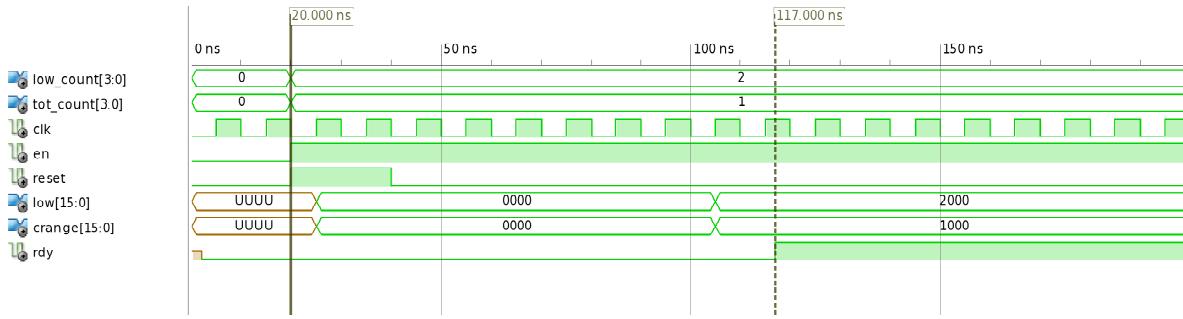

| 4.6.1                       | BPE . . . . .                                 | 69         |

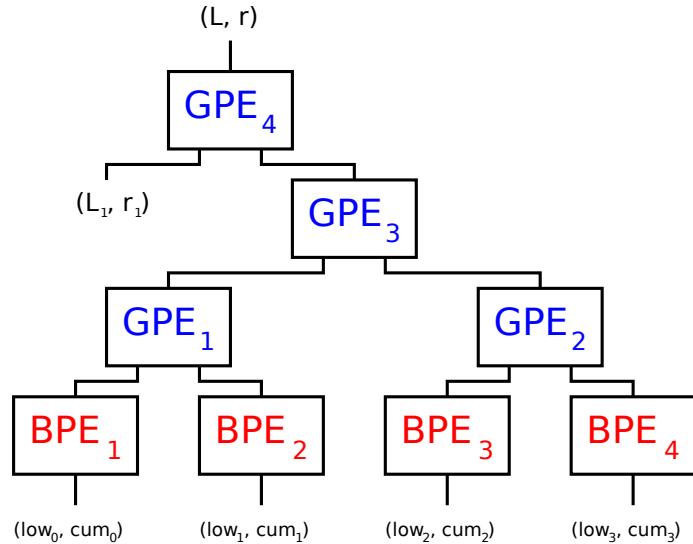

| 4.6.2                       | GPE . . . . .                                 | 71         |

| 4.6.3                       | Der Koder . . . . .                           | 72         |

| 4.7                         | Normalizer . . . . .                          | 74         |

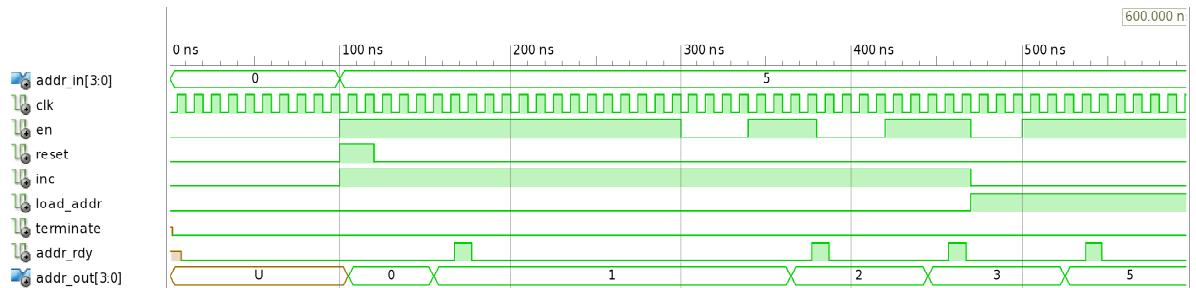

| 4.8                         | Control Unit . . . . .                        | 76         |

| 4.9                         | Validierung und Synthese Ergebnisse . . . . . | 78         |

| <b>5</b>                    | <b>Zusammenfassung und Ausblick</b>           | <b>81</b>  |

| 5.1                         | Ausblick . . . . .                            | 81         |

| <b>Appendix</b>             |                                               | <b>83</b>  |

| <b>Literaturverzeichnis</b> |                                               | <b>97</b>  |

| <b>Zeichenliste</b>         |                                               | <b>99</b>  |

| <b>Stichwortverzeichnis</b> |                                               | <b>101</b> |

# Abbildungsverzeichnis

---

|      |                                                                      |    |

|------|----------------------------------------------------------------------|----|

| 2.1  | Intervalleinteilung (obere Grenzen = $F_x(i)$ ) . . . . .            | 14 |

| 2.2  | Teilintervalleinteilung (obere Grenzen = $F_x(i)$ ) . . . . .        | 15 |

| 2.3  | Intervalleinteilung in Quadranten . . . . .                          | 29 |

| 3.1  | Basisformeln für Parallelisierung . . . . .                          | 41 |

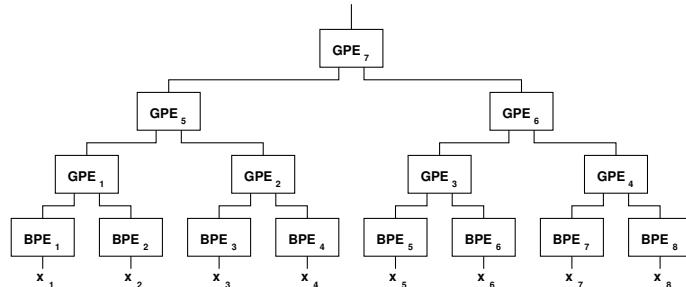

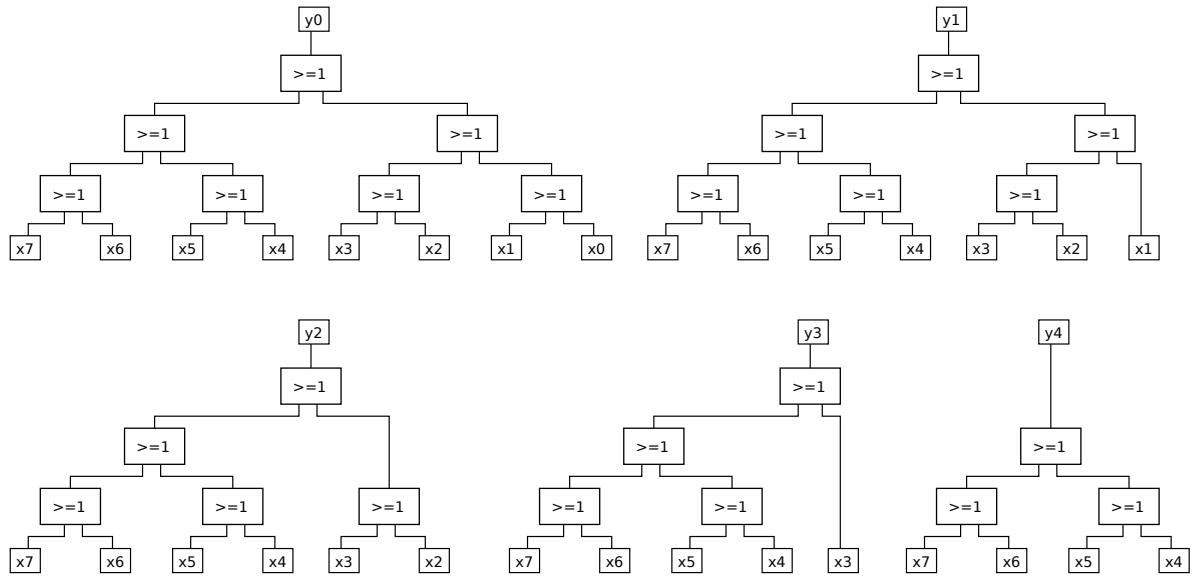

| 3.2  | Berechnungs-Baum für 8 Symbole . . . . .                             | 41 |

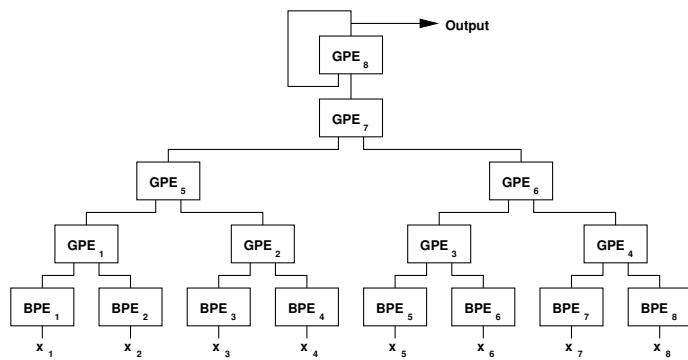

| 3.3  | Berechnungs-Baum für 8 Symbole + Konkatenation . . . . .             | 42 |

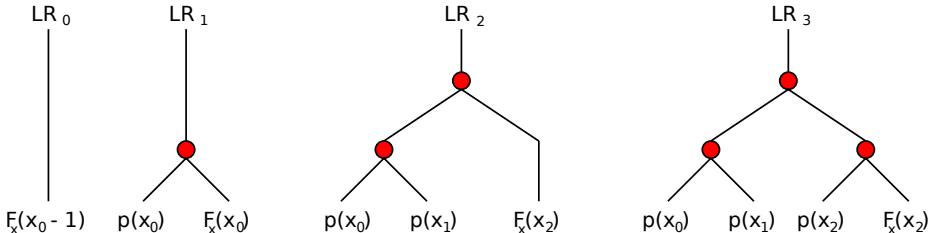

| 3.4  | Berechnungs-Baum <i>LR</i> für die ersten 4 Symbole . . . . .        | 47 |

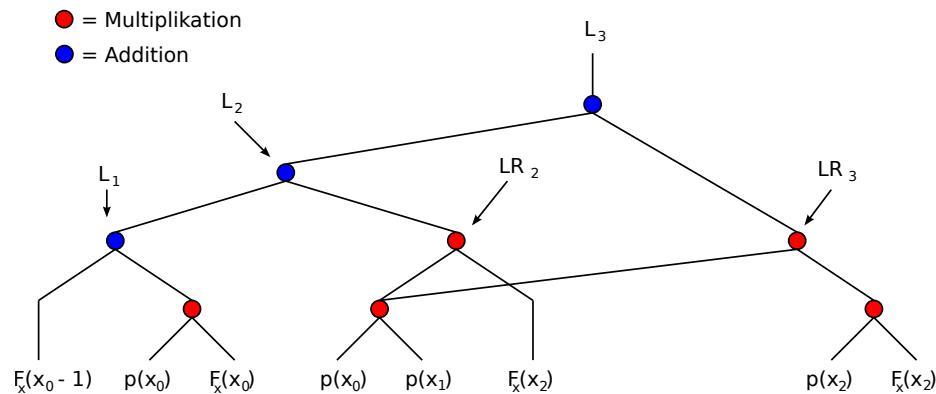

| 3.5  | Berechnungs-Baum <i>L</i> für die ersten 4 Symbole . . . . .         | 48 |

| 3.6  | Berechnungs-Baum . . . . .                                           | 49 |

| 3.7  | Berechnungs-Baum für 32 Symbole . . . . .                            | 51 |

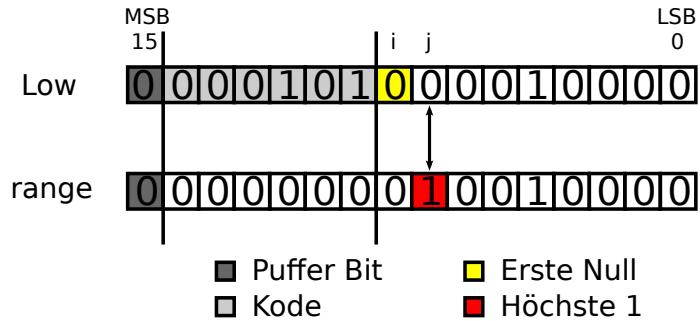

| 3.8  | direkte Bestimmung des Kodes für $L = 0A10$ und $r = 0090$ . . . . . | 56 |

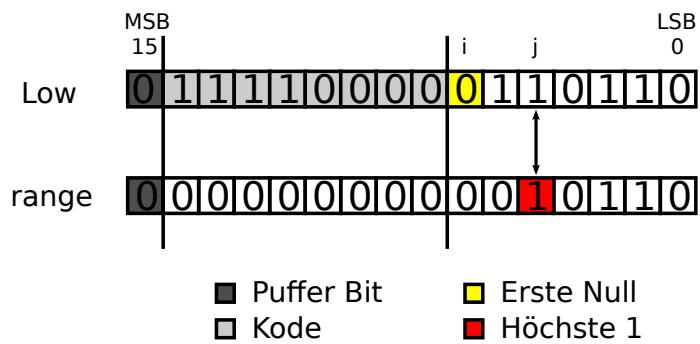

| 3.9  | direkte Bestimmung des Kodes für $L = 7836$ und $r = 0016$ . . . . . | 56 |

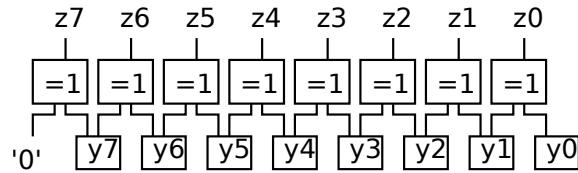

| 3.10 | Prioritätsenkoder <i>OR</i> -Baum . . . . .                          | 57 |

| 3.11 | Bitbestimmung mit <i>XOR</i> Gattern . . . . .                       | 57 |

| 4.1  | Berechnungs-Baum für 4 Symbole + Konkatenation . . . . .             | 62 |

| 4.3  | Incrementer Test Bench . . . . .                                     | 66 |

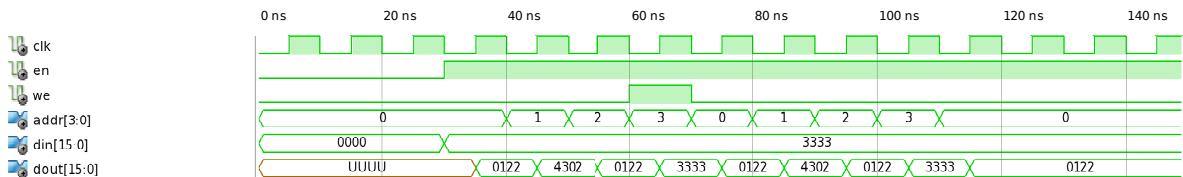

| 4.4  | RAM Testbench . . . . .                                              | 67 |

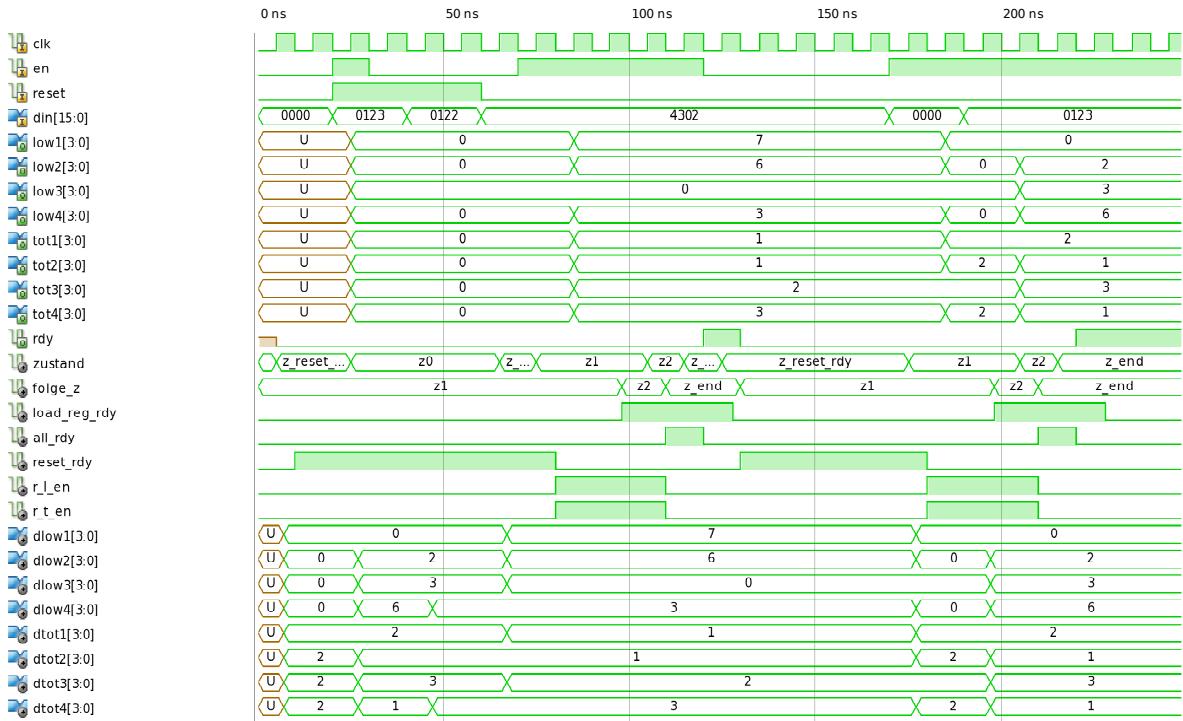

| 4.5  | Parallel Loader Testbench . . . . .                                  | 69 |

| 4.6  | Schematische BPE . . . . .                                           | 70 |

| 4.7  | Testbench für BPE . . . . .                                          | 71 |

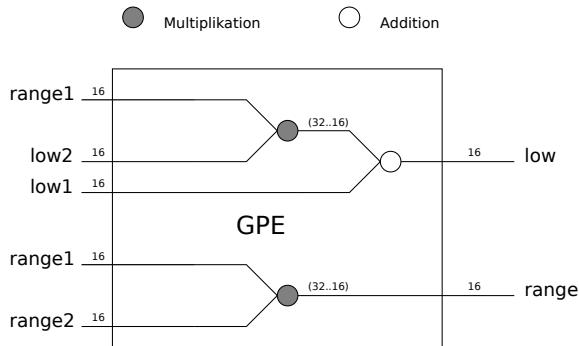

| 4.8  | Schematische GPE . . . . .                                           | 72 |

| 4.9  | Testbench für GPE . . . . .                                          | 72 |

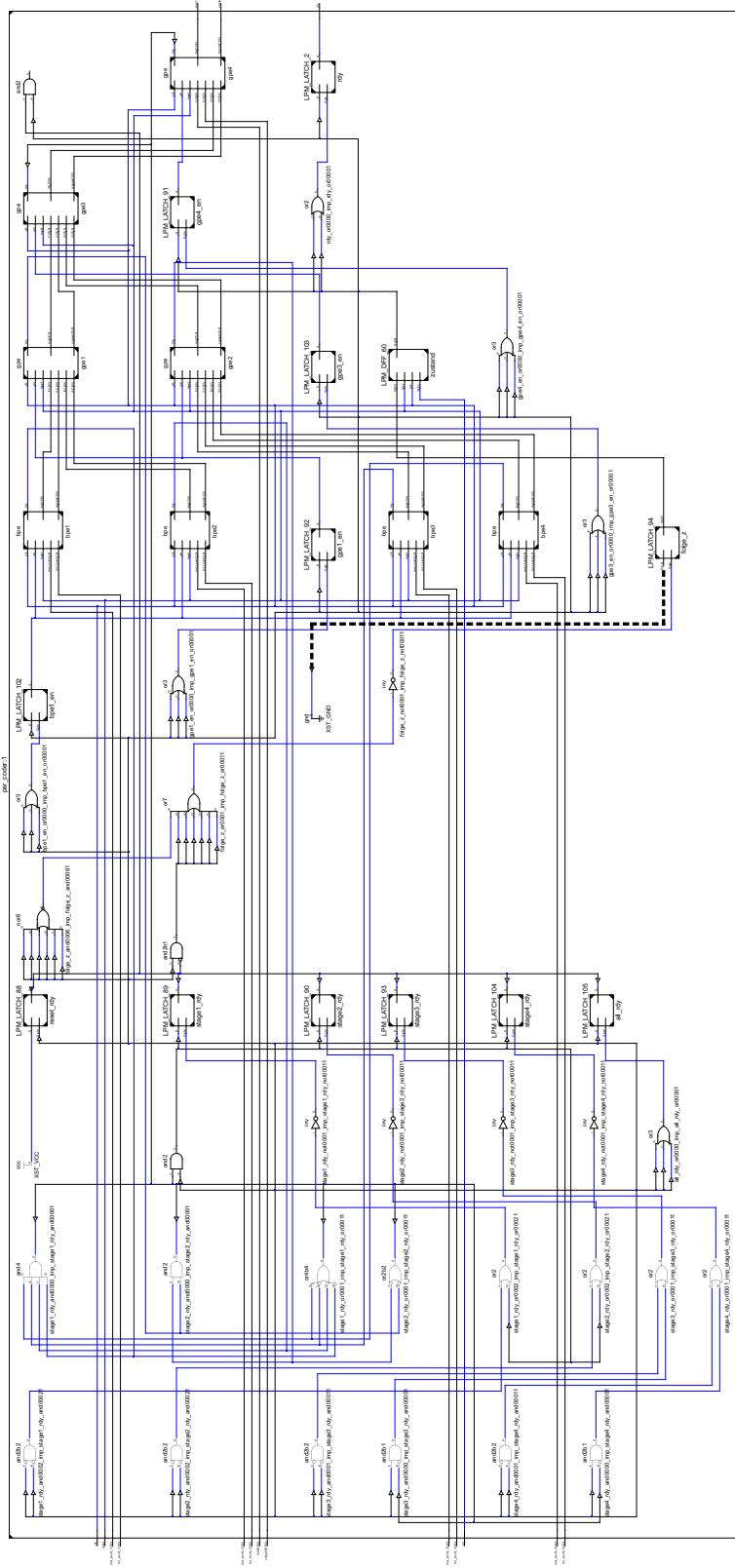

| 4.10 | Technologie Block Parallel Koder . . . . .                           | 73 |

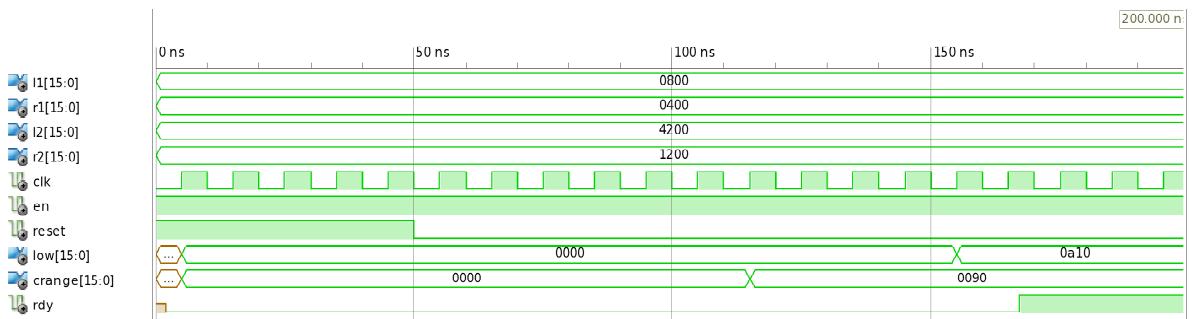

| 4.11 | Testbench für Parallel Koder . . . . .                               | 74 |

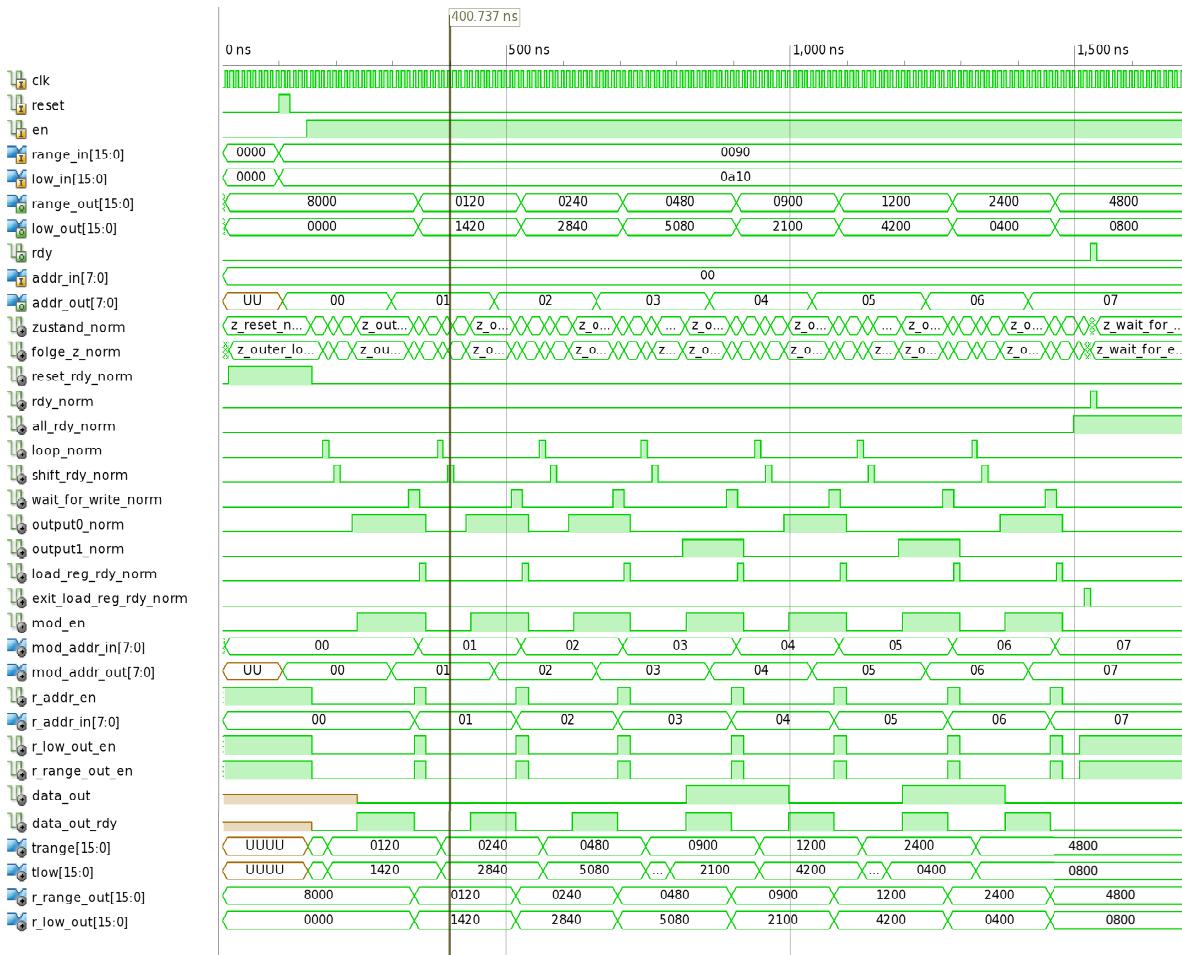

| 4.12 | Testbench für Normalizer mit $L = 0A10$ und $r = 0090$ . . . . .     | 75 |

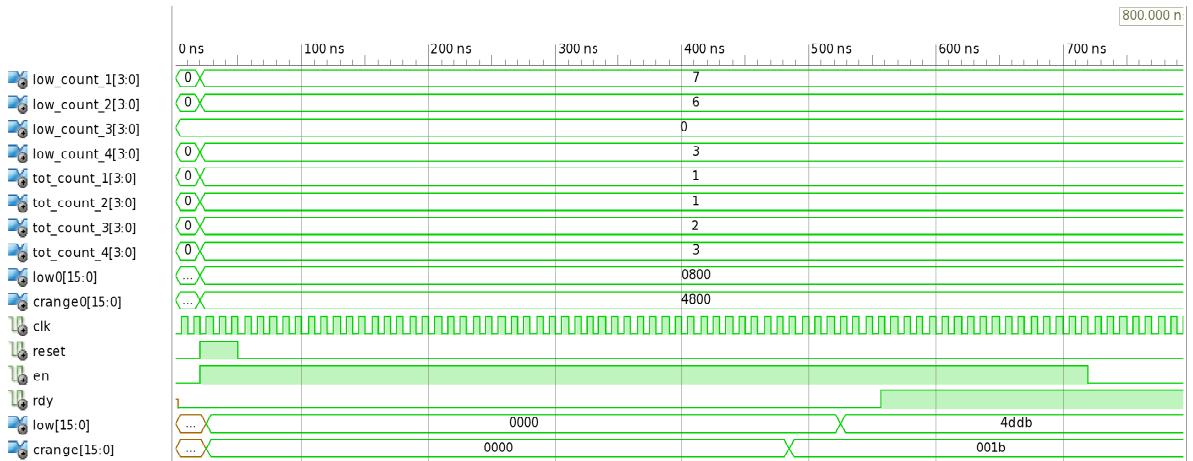

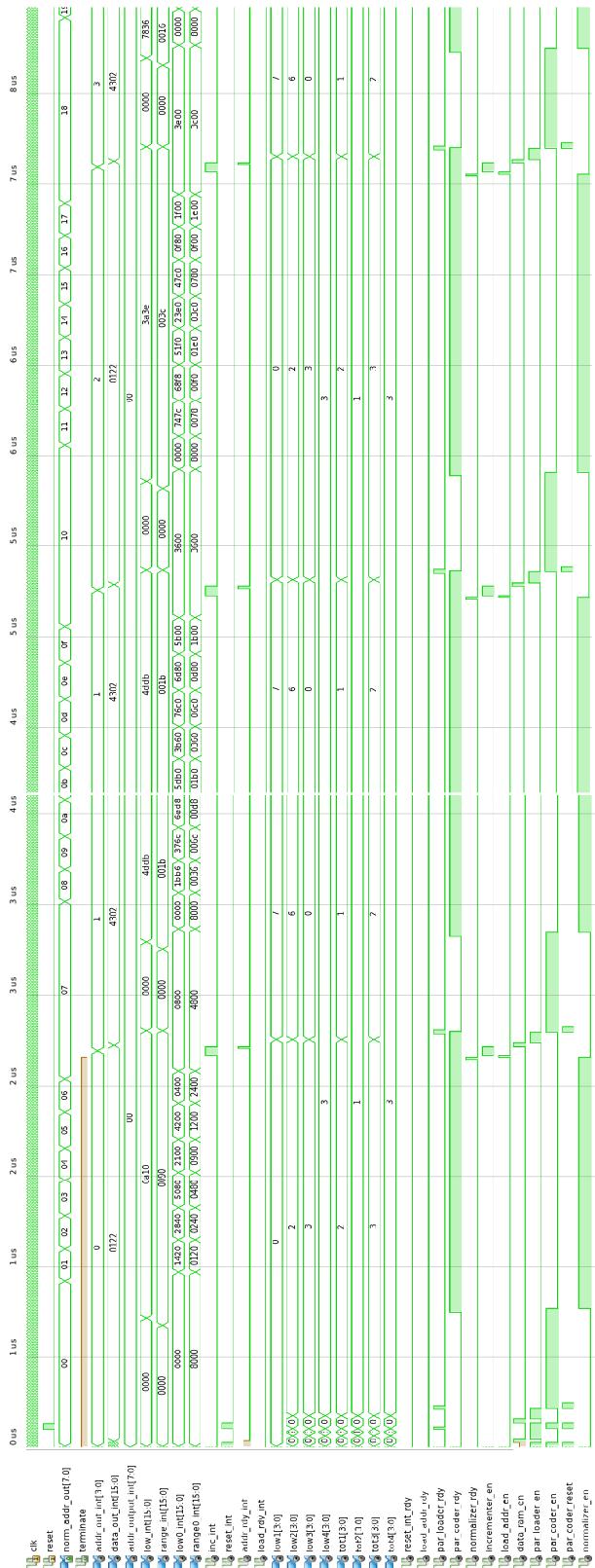

| 4.13 | Gesamtentwurf Testbench . . . . .                                    | 77 |

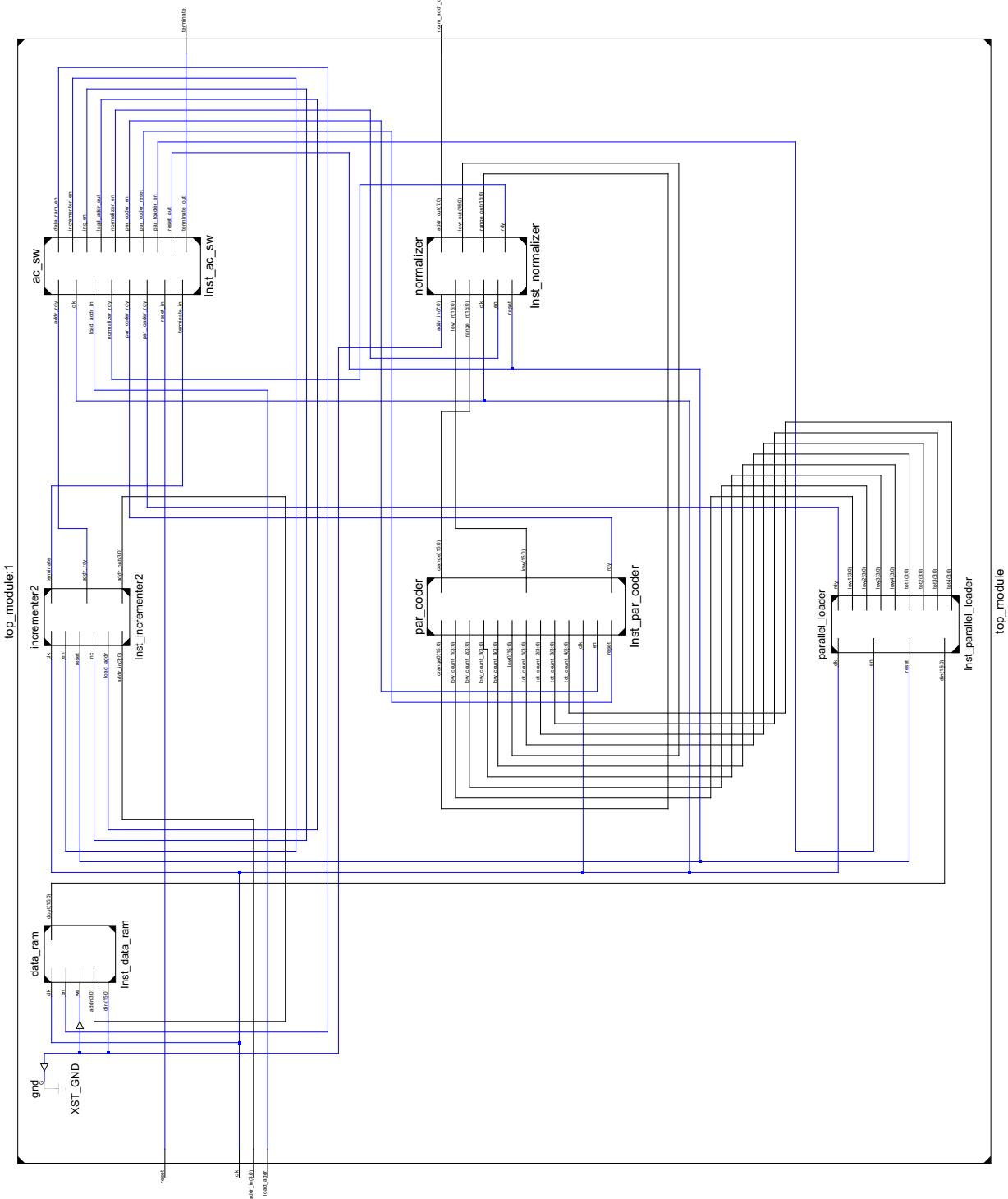

| 4.2  | Gesamtentwurf . . . . .                                              | 79 |

# **Verzeichnis der Listings**

---

|     |                                                      |    |

|-----|------------------------------------------------------|----|

| 2.1 | Algorithmus für Kodierung (Bit Breite 8) . . . . .   | 32 |

| 2.2 | Algorithmus für Dekodierung (Bit Breite 8) . . . . . | 35 |

# **Abstract**

Das Arithmetische Kodieren hat den Vorteil, nahe der Entropie komprimieren zu können. Das Verfahren besteht aus zwei Differenzengleichungen, deren Berechnung sequenziell ist. Teilrechnungen können jedoch zusammengefasst und parallel berechnet werden.

In dieser Diplomarbeit wurde die Parallelisierung des Arithmetischen Kodierens in Hinblick auf eine Hardware-Implementierung untersucht. Lösungsvorschläge wurden analysiert und gegenübergestellt sowie ihre Gemeinsamkeiten herausgearbeitet.

Ein wesentlich einfacherer Algorithmus für die Skalierung wurde entwickelt und eine Formel für die mindestens zu wählende Bit Breite erarbeitet. Abschließend wurde eine VHDL Lösung implementiert.

## **Abstract**

The advantage of Arithmetic Coding is a compression rate close to the Entropy. The method consists of two difference equations. Their calculation is of a sequential nature. Parts of them can be combined and calculated in parallel.

In this diploma theses the parallelization of Arithmetic Coding has been examined with focus on a hardware implementation. Different approaches for such parallelization were analyzed and compared. The similarities have been worked out.

A simpler scaling algorithm has been presented and a formula for the minimum bit width was developed. A VHDL solution has been implemented.

# 1 Einleitung

In der Informationsverarbeitung müssen große Datenmengen gespeichert und verwaltet werden. Suchmaschinenhersteller wie beispielsweise Google<sup>TM</sup>, die Inhalte aus Internet-Seiten für ihre Suchanfragen speichern müssen, erreichen Index-Größen von einer Trillion URLs (1.000.000.000.000)<sup>1</sup>. Soziale Netzwerke wie Facebook<sup>TM</sup> zählen inzwischen 500 Millionen registrierte Nutzer mit über 50 Billionen<sup>2</sup> Uploads, deren Daten bewältigt und verwaltet werden müssen. Es ist klar, dass man bei diesen Mengen nach möglichst effizienten Speichermethoden sucht. Hier spielt die Komprimierung eine große Rolle. Nicht nur der Platzbedarf würde sinken und damit Kosten sparen, sondern selbst geringe Komprimierungsraten würden ausreichen, um erhebliche Geschwindigkeitssteigerungen zu erreichen.

Wann immer Daten übertragen werden, kann man den Durchsatz steigern, indem man für den selben Informationsgehalt weniger Bytes überträgt. Das gilt nicht nur für Datenübertragung von der Festplatte zum Computer, sondern ist allgemein gültig. Es findet unter anderem Anwendung in der Telekommunikationsbranche. Hier werden große Anstrengungen unternommen, die Gespräche möglichst stark zu komprimieren, um die Bandbreite besser zu nutzen.

Bei Anwendungen wie beispielsweise einer Hochgeschwindigkeitskamera, die sehr große Mengen an Daten produziert, ist man zusätzlich mit dem Problem konfrontiert, ob die Daten in der geforderten Zeit überhaupt komprimiert werden können. Man kann davon ausgehen, dass eine stärkere Komprimierung mehr Rechenzeit in Anspruch nehmen wird als eine geringe.

Das Arithmetische Kodieren verspricht Komprimierungsraten nahe der Entropie. Die streng sequenzielle Abarbeitung der Daten macht den Algorithmus jedoch sehr langsam. In diesem Zusammenhang wäre es interessant zu wissen, ob man dieses Verfahren durch eine Parallelisierung in Hardware beschleunigen kann, um es zum Beispiel in Mobiltelefonen oder Hochgeschwindigkeitskameras einsetzen zu können. Dieser Frage werden wir in dieser Arbeit nachgehen.

## Gliederung

Es erschien mir sinnvoll, erst das Prinzip des Arithmetischen Kodierens zu erklären und dann dieses mit der Parallelisierung zu vertiefen. Zuerst wird die allgemeine Idee erklärt.

<sup>1</sup><http://googleblog.blogspot.com/2008/07/we-knew-web-was-big.html>

<sup>2</sup>[http://www.usatoday.com/tech/news/2010-07-21-facebook-hits-500-million-users\\_N.htm](http://www.usatoday.com/tech/news/2010-07-21-facebook-hits-500-million-users_N.htm)

## 1 Einleitung

---

Sind diese Grundlagen geschafft, kann man sich weiter Gedanken über die Parallelisierung machen. Schließlich fließen die gewonnenen Erkenntnisse dann in die konkrete Umsetzung ein.

**Kapitel 2 – Arithmetisches Kodieren:** Hier wird das Prinzip des sequenziellen Arithmetischen Kodierens beschrieben und ein Algorithmus entwickelt.

**Kapitel 3 – Parallelisierung:** Ansätze zur Parallelisierung des Algorithmus werden hier vorgestellt. Diese werden im Hinblick auf eine konkrete Hardware Implementierung hin analysiert und gegenübergestellt. Die daraus gewonnenen Erkenntnisse bilden den Kern dieser Diplomarbeit.

**Kapitel 4 – Implementierung:** Das Ergebnis der Analyse endet mit einer konkreten Implementierung in VHDL. In diesem Kapitel werden die einzelnen Module des Kodes im Detail erklärt.

## 2 Arithmetisches Kodieren

### 2.1 Grundlagen

#### 2.1.1 Motivation

Die Geschichte des Arithmetischen Kodierens ist eigentlich ziemlich interessant. Shannon hat schon 1948 [Sha48] in einem Paper ein Verfahren erwähnt, das die Verteilungsfunktion für eine Kodierung vorschlägt. Später wurde es unter dem Namen Shannon-Fano Kode bekannt. Peter Elias, der auch Fanos Vorlesung über Informationstheorie hörte, entwickelte eine rekursive Implementierung des Problems. Diese wurde jedoch nie veröffentlicht. Jelinek entwickelte diese Idee in einem Anhang in seinem Buch, das 1968 erschien, weiter.

Der wirkliche Durchbruch gelang aber erst 1976 durch unabhängige Erkenntnisse von Pasco [Pas76] und Rissanen [Ris76]. Hier wurde erstmalig das Problem der endlichen Genauigkeit gelöst. Schließlich erschienen aufgrund dieser Erkenntnisse Paper mit praktischen Implementierungen. Eine der bekanntesten davon ist die Referenzimplementierung von Witten, Neal und Cleary [WNC87]. Wie wir sehen werden, vergingen wieder einige Jahre bis eine parallele Implementierung erstmals von Jiang und Jones [JJ94] 1994 in einem Paper vorgeschlagen wurde.

Was diese Geschichte so interessant macht, ist die Tatsache, dass das Prinzip zwar relativ früh bekannt wurde, es jedoch sehr lange gedauert hat, bis man die Probleme, die dieses Verfahren mit sich bringt, in den Griff bekommen hat. Eine andere Betrachtungsweise wäre, dass dieses Verfahren eher uninteressant ist und von keiner praktischen Bedeutung. Dann würden sich auch weniger Menschen damit befassen und sich so die lange Geschichte erklären. Das ist nicht der Fall. Ganz im Gegenteil! Das Arithmetische Kodieren hat einige Vorteile gegenüber dem sehr umfassend behandelten Huffman Coding.

Welche Vorteile hat das Arithmetische Kodieren gegenüber dem Huffman Coding?

Dazu benötigen wir erstmal ein paar Definitionen. Ich halte mich dabei an die Nomenklatur und die Beispiele von K. Sayood [Say96].

Sei  $P(A)$  die Wahrscheinlichkeit, dass ein Ereignis  $A$  eintritt, dann ist die SELBSTINFORMATION des Ereignisses  $A$

$$i(A) = \log_b \frac{1}{P(A)} = -\log_b P(A)$$

Diese Definition kann man sich so vorstellen, dass ein Ereignis welches selten auftritt mehr Informationsgehalt hat als eines welches häufig vorkommt. Das entspricht auch der intuitiven Auffassung von Informationsgehalt.

**Beispiel 1.** Seien  $K$  und  $Z$  die möglichen Ergebnisse eines Münzwurfs. Dann gilt

$$P(K) = P(Z) = \frac{1}{2}$$

und damit auch

$$i(K) = i(Z) = -\log_b(\frac{1}{2}) = 1 \text{ bit}$$

Würde man die Münze unfair gestalten, so dass

$$P(K) = \frac{1}{8} \text{ und } P(Z) = \frac{7}{8}$$

dann ergibt sich daraus

$$i(K) = 3 \text{ bits, und } i(Z) = 0.193 \text{ bits}$$

◊

Den Informationsgehalt eines Textes nennt man die ENTROPIE. Sie ist die Summe der einzelnen Informationsgehalte multipliziert mit der Wahrscheinlichkeit, mit der sie auftreten:

$$E = \sum P(A_i)i(A_i) = -\sum P(A_i)\log_b P(A_i)$$

Die Entropie stellt die untere Grenze einer Kompaktierung dar. In der Regel wird man diese Grenze nur in Ausnahmefällen erreichen.

Das genügt an dieser Stelle, um in einem Beispiel die Probleme des Huffman Codings zu zeigen.

**Beispiel 2.** Gegeben sei ein Alphabet  $A = \{a_1, a_2, a_3\}$  mit den Wahrscheinlichkeiten  $P(a_1) = 0.95$ ,  $P(a_2) = 0.02$  und  $P(a_3) = 0.03$ . Die Entropie ist also

$$-(0.95\log_b(0.95) + 0.03\log_b(0.03) + 0.02\log_b(0.02)) = 0.3349$$

Einen Huffman Code für diese Quelle zeigt Tabelle 2.1

Die durchschnittliche Kodelänge für diesen Kode ist  $1 \cdot 0.95 + 2 \cdot 0.02 + 2 \cdot 0.03 = 1.05$  Bits/Symbol und damit 213% der Länge der Entropie. Das bedeutet, dass es mehr als doppelt soviel Bits braucht wie die Entropie. Selbst wenn man die Symbole in Zweiergruppen aufteilen würde, erhält man noch eine durchschnittliche Kodelänge, die 72% über der Entropie liegt.

Um noch bessere Kompaktierung zu erreichen, kann man noch größere Gruppen zusammenfassen. Bei einer Gruppe von 8 Symbolen erreicht man akzeptable Werte. Das dazugehörige Alphabet steigt aber zu einer Anzahl von  $3^8 = 6561$  Symbolen an. Hier sieht man, dass in diesem Fall das Huffman Coding nicht mehr effizient ist.

◊

| Symbol | Kodewort |

|--------|----------|

| $a_1$  | 0        |

| $a_2$  | 11       |

| $a_3$  | 10       |

**Tabelle 2.1:** Huffman Code für einstellige Symbole

| Symbol   | Wahrscheinlichkeit | Kodewort |

|----------|--------------------|----------|

| $a_1a_1$ | 0.9025             | 0        |

| $a_1a_2$ | 0.0190             | 111      |

| $a_1a_3$ | 0.0285             | 100      |

| $a_2a_1$ | 0.0190             | 1101     |

| $a_2a_2$ | 0.0004             | 110011   |

| $a_2a_3$ | 0.0006             | 110001   |

| $a_3a_1$ | 0.0285             | 101      |

| $a_3a_2$ | 0.0006             | 110010   |

| $a_3a_3$ | 0.0009             | 110000   |

**Tabelle 2.2:** Huffman Code für zweistellige Symbole

An diesem Beispiel wird klar, wo die Probleme beim Huffman Code liegen: Man erreicht bessere Kompaktierung, wenn man Kodewörter für Gruppen von Symbolen generiert. Doch für lange Symbolgruppen muss man dann sehr viele Kodes erzeugen. Die zu erzeugenden Kodes steigen exponentiell an.

Man kann das umgehen, indem man ein Kodewort für eine bestimmte Symbolsequenz generiert. Genau das ist die Idee hinter dem Arithmetischen Kodieren.

Beim Arithmetischen Kodieren wird einer Symbolsequenz  $S = x_1x_2x_3\dots$  genau eine Zahl (oder Kode) zugewiesen. Die Länge der Sequenz ist  $|S| = n$ .

### 2.1.2 Prinzip

Um einer Symbolsequenz oder auch einer Buchstabensequenz eine eindeutige Zahl zuzuweisen bedienen wir uns der Verteilungsfunktion einer diskreten Zufallsvariablen. Sei also ein Ereignis  $a_i \in A$  einer Zufallsvariablen

$$X(a_i) = i$$

zugewiesen, wobei  $A = a_1, a_2, a_3 \dots a_m$  ein Alphabet ist. Damit gilt die Wahrscheinlichkeit, dass  $X$  den Wert  $i$  annimmt:

$$P(X = i) = p(a_i)$$

Das Zuweisen einer Wahrscheinlichkeit ist das zugrundeliegende Modell  $P$  für die Quelle. Wir werden später sehen, dass diese Zuweisung großen Einfluss auf die Kompressionsrate haben wird.

Die Verteilungsfunktion ist dann als

$$F_x(i) = \sum_{k=1}^i P(X = k) = \sum_{k=1}^i p(a_i) \quad (2.1)$$

definiert. Es gelte außerdem, dass sämtliche Ereignisse  $a_i$  disjunkt sind und

$$\cap a_i = A$$

Nun aber endlich zu der grundlegenden Idee: Wir wollen erreichen, einer Sequenz einen eindeutigen Wert zuzuweisen. Dafür geht man folgendermaßen vor:

Mit  $|A| = m$  ist  $F_x(m) = 1$ . Deshalb betrachten wir ein Intervall von  $[0, 1)$ . Wir nutzen die Tatsache, dass in diesem Intervall unendlich viele irrationale Zahlen existieren und teilen dieses Intervall in Teilintervalle aus der diskreten Verteilungsfunktion  $F_x(i)$ . Wir weisen jedem  $a_i$  das Teilintervall:

$$[F_x(i-1), F_x(i)) \quad \text{für } i = 1 \dots m \quad (2.2)$$

zu.

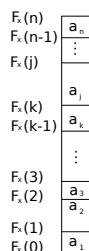

**Abbildung 2.1:** Intervalleinteilung (obere Grenzen =  $F_x(i)$ )

Wird jetzt zum Beispiel als erstes das Symbol  $a_k$  gelesen, weisen wir das Intervall  $[F_x(k-1), F_x(k))$  unserem Kode zu. Wir merken uns hierzu die untere Grenze  $F_x(k-1)$  und die obere, offene Grenze  $F_x(k)$ . Dann teilen wir dieses Intervall wieder in  $m$  Teilintervalle ein.

Damit das Verhältnis erhalten bleibt, müssen die neuen Grenzen durch die Länge des neuen Intervalls geteilt werden. Lesen wir beispielsweise als nächstes das Symbol  $a_j$  ein, wird dem Kode das Intervall

$$\left[ \frac{F_x(k-1) + F_x(j-1)}{F_x(k) - F_x(k-1)}, \frac{F_x(k) + F_x(j)}{F_x(k) - F_x(k-1)} \right] \quad (2.3)$$

zugewiesen.

**Abbildung 2.2:** Teilintervalleinteilung (obere Grenzen =  $F_x(i)$ )

**Beispiel 3.** Gegeben sei ein Alphabet  $A = \{a_1, a_2, a_3\}$  mit  $P(a_1) = 0.7$ ,  $P(a_2) = 0.1$  und  $P(a_3) = 0.2$ . Die Gleichung (2.1) liefert  $F_x(1) = 0.7$ ,  $F_x(2) = 0.8$  und  $F_x(3) = 1.0$ . Falls nun das Symbol  $a_1$  kodiert werden soll, liegt das Intervall zwischen  $[0.0, 0.7]$ , für  $a_2$  zwischen  $[0.7, 0.8]$  und entsprechend für  $a_3$  zwischen  $[0.8, 1.0]$ .

Angenommen wir lesen erst das Symbol  $a_1$ . Dann liegt unser Kode zwischen den Werten  $[0.0, 0.7]$ . Dieses Intervall wird gemäß der Gleichung (2.3) in die Teilintervalle  $[0.0, 0.49]$ ,  $[0.49, 0.56]$  und  $[0.56, 0.7]$  zerlegt. Würde als nächstes wieder das Symbol  $a_1$  gelesen, dann läge der Kode im Intervall  $[0.0, 0.49]$ , oder bei  $a_2$  im Intervall  $[0.49, 0.56]$  und bei  $a_3$   $[0.56, 0.7]$ .

Und wieder würde man das Intervall aufteilen und für das nächste Symbol das entsprechende Teilintervall wählen. ◇

Das Zerlegen in Teilintervalle und Auswählen des Teilintervalls wiederholt man so lange, bis die Quelle gelesen ist. Das letzte (Teil-)Intervall<sup>1</sup> bildet das Ergebnis der Kodierung. Man muss sich aber nicht die untere und obere Grenze merken. Es reicht, eine beliebige Zahl aus dem Intervall zu nehmen. Das ergibt sich aus der Tatsache, dass die Teilintervalle voneinander disjunkt sind und sobald man irgendeine Zahl aus dem Intervall gewählt hat, es kein anderes Intervall gibt, welches diese Zahl beinhaltet. Damit ist eindeutig festgelegt, um welches Intervall es sich handelt. Aus praktischen Gründen wählt man gerne die untere Grenze, wie wir später sehen werden.

<sup>1</sup>Das erste Intervall wird in Teilintervalle zerlegt. Das dann ausgesuchte Teilintervall wird nun zum Intervall

Um den mathematischen Weg der Kodegenerierung zu erläutern, wählen wir hier die Mitte des Intervalls und definieren dafür folgende Rechenregel

$$\begin{aligned}\bar{T}_x(a_i) &= \sum_{k=1}^{i-1} P(X = k) + \frac{1}{2}P(x = i) \\ \bar{T}_x(a_i) &= F_x(i - 1) + \frac{1}{2}P(x = i)\end{aligned}\tag{2.4}$$

Das  $\bar{T}$  steht hier für das englische Wort «tag». Jetzt können wir jedem Symbol  $a_i$  einen Kode zuweisen.

**Beispiel 4.** Sei die Augenzahl eines sechsseitigen, fairen Würfels den Ereignissen  $\{1, 2, 3, 4, 5, 6\}$  zugewiesen. Dann gilt

$$P(X = i) = \frac{1}{6} \quad \text{für } i = 1, 2, \dots, 6$$

Mit der Gleichung (2.4) erhält man

$$\begin{aligned}\bar{T}_x(1) &= P(X = 0) + \frac{1}{2}P(X = 1) = 0 + \frac{1}{2} \cdot \frac{1}{6} = \frac{1}{12} = 0.08\overline{33} \\ \bar{T}_x(2) &= P(X = 1) + \frac{1}{2}P(X = 2) = \frac{1}{6} + \frac{1}{2} \cdot \frac{1}{6} = 0.25 \\ \bar{T}_x(3) &= \sum_{k=1}^2 P(X = k) + \frac{1}{2}P(X = 3) = 0.41\overline{66} \\ &\vdots\end{aligned}$$

Und so kann man auf einfache Weise für alle Ereignisse einen Kode zuweisen.  $\diamond$

Das Prinzip des Kodezuweisens kann man auf eine Sequenz von Ereignissen erweitern. Hierzu wird zunächst eine feste Ordnung der Symbole oder Ereignisse definiert:

$$\bar{T}_x^{(m)}(x_i) = \sum_{y < x_i} P(y) + \frac{1}{2}P(x_i) \tag{2.5}$$

Dabei bedeutet  $y < x$ , dass das Ereignis  $y$  dem Symbol  $x$  vorangeht und das hochgestellte  $m$  ist die Länge des Alphabets.

**Beispiel 5.** Wir benutzen wieder einen fairen Würfel und berechnen den Kode, der sich für das Ereignis  $13$ , also dass man zuerst eine  $1$ , und im Anschluss eine  $3$  würfelt, ergibt.

$$\begin{aligned}\bar{T}_x(13) &= P(X = 11) + P(X = 12) + \frac{1}{2}P(X = 13) \\ &= 1/36 + 1/36 + 1/2(1/36) \\ &= 5/72\end{aligned}$$

In diesem Beispiel ist zu sehen, dass zur Berechnung der Sequenz der Länge  $n$  die Kodes aller vorangehenden Sequenzen der Länge  $n - 1$  benötigt werden. Das wäre aber genauso aufwendig als wenn man für das Huffman Coding die Wahrscheinlichkeiten aller möglichen Symbole der Länge  $n$  berechnen würde. Im nächsten Beispiel werden wir aber sehen, dass dieses nicht notwendig ist.

Im Folgenden werden wir die mathematische Vorgehensweise zum Erstellen eines Kodes für eine Sequenz kennenlernen.

**Beispiel 6.** Wir benutzen weiterhin den fairen, sechsseitigen Würfel und wollen jetzt eine obere und untere Grenze des Intervalls für einen Kode für das Ereignis 3 2 2 berechnen. Sind die Grenzen bekannt, kann man wie schon beschrieben eine beliebige Zahl aus diesem Intervall benutzen, um daraus einen Kode zu generieren.

Das Ereigniss besteht darin, dass zuerst eine 3 dann eine 2 und schließlich wieder eine 2 gewürfelt wird. Wir bezeichnen die obere Grenze mit der Sequenzlänge  $n$  mit  $H_n$  und die untere Grenze mit  $L_n$ .

Wir betrachten das Ereignis 3, gehen gemäß Gleichung (2.2) vor und setzen  $i = 3$ . Die Länge der Sequenz ist  $n = 1$ . Die Ereignisse sind laut Gleichung (2.5) in der Reihenfolge  $\{1, 2, 3, 4, 5, 6\}$  geordnet. Damit ist das Ereignis  $i - 1 = 2$ . Wir setzen ein:

$$H_1 = F_x(3), \quad L_1 = F_x(2)$$

Als nächstes lesen wir die 2. Die Sequenz ist  $x = 32$ . Die neuen Grenzen sind

$$H_2 = F_x(32), \quad L_2 = F_x(31)$$

Die Berechnung dieser Werte geht folgendermaßen:

$$\begin{aligned} F_x(32) &= P(X = 11) + P(X = 12) + P(X = 13) \dots P(X = 16) + \\ &\quad P(X = 21) + P(X = 22) + P(X = 23) \dots P(X = 26) + \\ &\quad P(X = 31) + P(X = 32) \end{aligned}$$

Wenn  $i$  sämtliche Ereignisse  $m$  beinhaltet — also in unserem Beispiel 1 bis 6 — dann gilt

$$\sum_{i=1}^m P(X = ki) = \sum_{i=1}^m P(X_1 = k, X_2 = i) = P(X_1 = k)$$

wobei  $X = X_1 X_2$ . Wir können also schreiben

$$\begin{aligned} F_x(32) &= P(X_1 = 1) + P(X_2 = 2) + P(X = 31) + P(X = 32) \\ &= F_x(2) + P(X = 31) + P(X = 32) \end{aligned}$$

Weil die einzelnen Würfe unabhängige Ereignisse sind, gilt

$$P(X = 31) = P(X = 3)P(X = 1)$$

und

$$P(X = 32) = P(X = 3)P(X = 2)$$

Damit ergibt sich

$$\begin{aligned} P(X = 31) + P(X = 32) &= P(X_1 = 3)(P(X_2 = 1) + P(X_2 = 2)) \\ &= P(X_1 = 3)F_x(2) \end{aligned}$$

Weil

$$P(X_1 = i) = F_x(i) - F_x(i-1)$$

also in unserem Beispiel

$$P(X_1 = 3) = F_x(3) - F_x(2)$$

können wir schreiben

$$P(X = 31) + P(X = 32) = (F_x(3) - F_x(2)) \cdot F_x(2)$$

oder

$$F_x(32) = F_x(2) + (F_x(3) - F_x(2)) \cdot F_x(2)$$

oder auch

$$H_2 = L_1 + (H_1 - L_1) \cdot F_x(2)$$

Auf gleiche Weise können wir zeigen, dass für die untere Grenze  $L_2$  gilt

$$F_x(31) = F_x(2) + (F_x(3) - F_x(2)) \cdot F_x(1)$$

oder

$$L_2 = L_1 + (H_1 - L_1)F_x(1)$$

Das dritte Symbol in diesem Beispiel ist wieder eine 2 und damit

$$H_3 = F_x(322), \quad L_3 = F_x(321)$$

Die gleiche Rechnung ergibt damit

$$\begin{aligned} F_x(321) &= F_x(31) + (F_x(32) - F_x(31)) \cdot F_x(1) \\ F_x(322) &= F_x(31) + (F_x(32) - F_x(31)) \cdot F_x(2) \end{aligned}$$

oder

$$\begin{aligned} L_3 &= L_2 + (H_2 - L_2) \cdot F_x(1) \\ H_3 &= L_2 + (H_2 - L_2) \cdot F_x(2) \end{aligned}$$

◊

Die allgemeine Vorschrift für die Intervallbildung der Sequenz  $X = x_1x_2x_3 \dots x_n$  sind die Differenzengleichungen

$$L_i = L_{i-1} + (H_{i-1} - L_{i-1}) \cdot F_x(i-1) \quad (2.6)$$

$$H_i = L_{i-1} + (H_{i-1} - L_{i-1}) \cdot F_x(i) \quad (2.7)$$

Für die Berechnung der Grenzen mussten keine vereinigten Wahrscheinlichkeiten berechnet werden. Es reicht also, die Verteilungsfunktion über das Alphabet zu kennen. Diese wird wie schon erwähnt durch das Modell gegeben. Für den Kode nimmt man nun eine Zahl aus dem Intervall. Wir wählen wieder die Hälfte

$$\bar{T}_x(X) = \frac{H_n - L_n}{2}$$

falls  $X = x_1x_2x_3 \dots x_n$  ist.

## 2.2 Kodierung als reelle Zahl

Wir gehen jetzt etwas konkreter vor und wollen die Zeichenfolge SWISS $\sqcup$ MISS kodieren. Dieses Beispiel ist aus [Salo8] entnommen. Die fünf vorkommenden Symbole können in einer beliebigen Reihenfolge in eine Tabelle für die Wahrscheinlichkeiten gespeichert werden. Die Funktion `cum_count` stehend für «cummulative count» wird mit

$$\text{cum\_count}_{a_i} = \sum_{k=1}^i |a_i|$$

definiert.

Wie schon eingangs erwähnt, entspricht diese Zuweisung dem Modell des Koders. Das Modell für unser Beispiel ist in Tabelle 2.3 zusammengefasst.

| Symbol             | Häufigkeit | Wahrscheinlichkeit $p_i$ | $F_x(i-1)$ | $F_x(i)$ | Intervall    | <code>cum_count</code> |

|--------------------|------------|--------------------------|------------|----------|--------------|------------------------|

| $a_1 = \sqcup$     | 1          | $1/10=0.1$               | 0.0        | 0.1      | $[0.0, 0.1)$ | 1                      |

| $a_2 = \mathbb{M}$ | 1          | $1/10=0.1$               | 0.1        | 0.2      | $[0.1, 0.2)$ | 2                      |

| $a_3 = \mathbb{I}$ | 2          | $2/10=0.2$               | 0.2        | 0.4      | $[0.2, 0.4)$ | 4                      |

| $a_4 = \mathbb{W}$ | 1          | $1/10=0.1$               | 0.4        | 0.5      | $[0.4, 0.5)$ | 5                      |

| $a_5 = \mathbb{S}$ | 5          | $5/10=0.5$               | 0.5        | 1.0      | $[0.5, 1.0)$ | 10                     |

**Tabelle 2.3:** Modell für Zeichenfolge SWISS $\sqcup$ MISS

Wir benutzen die Gleichungen (2.6) und (2.7), um sequentiell  $H$  und  $L$  zu errechnen. Am Anfang muss  $H$  mit 1 und  $L$  mit 0 initialisiert werden. Das bedeutet, am Anfang geht das

Intervall über die volle Breite. Erst nach Einlesen des ersten Symbols wird dieses Intervall eingeschränkt.

Als nächstes haben wir das Symbol  $x_1 = S$  gelesen. Die neuen Grenzen errechnen sich mit

$$L_1 = 0 + (1 - 0) \cdot F_x(4) = 0 + 0.5 = 0.5$$

$$H_1 = 0 + (1 - 0) \cdot F_x(5) = 0 + 1.0 = 1.0$$

Das neue Intervall nach Einlesen von  $S$  ist  $[0.5, 1.0]$ . Wir fahren fort und lesen  $x_2 = W$

$$L_2 = 0.5 + (1.0 - 0.5) \cdot F_x(3) = 0.5 + 0.5 \cdot 0.4 = 0.70$$

$$H_2 = 0.5 + (1.0 - 0.5) \cdot F_x(4) = 0.5 + 0.5 \cdot 0.5 = 0.75$$

Das Intervall verkleinert sich weiter auf  $[0.70, 0.75]$ . Wir lesen  $x_3 = I$

$$L_3 = 0.70 + (0.75 - 0.70) \cdot F_x(2) = 0.70 + 0.05 \cdot 0.2 = 0.71$$

$$H_3 = 0.70 + (0.75 - 0.70) \cdot F_x(3) = 0.70 + 0.05 \cdot 0.4 = 0.72$$

und so weiter bis das letzte Symbol  $x_n$  gelesen ist. Wir können gemäß Gleichung (2.4) für den Kode die Mitte des Intervalls nehmen, oder einfach die untere Grenze. Der Kode ist in dem Fall 0.71753375.

## 2.3 Dekodierung als reelle Zahl

Die Dekodierung läuft analog zur Kodierung. Wir starten damit, dass wir  $L$  den Wert 0 und  $H$  den Wert 1 zuweisen. Nach der Dekodierung des ersten Symbols erhalten wir

$$L_1 = 0 + (1 - 0) \cdot F_x(x_1 - 1) = F_x(x_1 - 1)$$

$$H_1 = 0 + (1 - 0) \cdot F_x(x_1) = F_x(x_1)$$

Mit anderen Worten heißt das, dass wir dasjenige  $x_1$  suchen, welches im Intervall  $[F_x(x_1 - 1), F_x(x_1)]$  liegt. Der Kode von 0.71753375 liegt im Intervall von  $S = [0.5, 1.0]$ . Also ist das gesuchte  $x_1 = S$ .

Wir wiederholen die Vorgehensweise und suchen  $x_2$ .

$$L_2 = 0.5 + (1 - 0.5) \cdot F_x(x_2 - 1) = 0.5 + 0.5 \cdot F_x(x_2 - 1)$$

$$H_2 = 0.5 + (1 - 0.5) \cdot F_x(x_2) = 0.5 + 0.5 \cdot F_x(x_2)$$

Jetzt wählen wir  $x_2 = W$ , denn

$$L_2 = 0.5 + 0.5 \cdot F_x(3) = 0.7 \quad \text{und} \quad H_2 = 0.5 + 0.5 \cdot F_x(4) = 0.75$$

Und das Intervall beinhaltet als einziges 0.71753375. Doch die Rechenregel lässt sich vereinfachen. Wir haben beim Kodieren zu  $L$  immer ein Teilintervall hinzugefügt. Beim Dekodieren können wir entsprechend dieses wieder abziehen, die Werte anpassen und erhalten so etwas direkter das gesuchte  $x_i$ . Wir ziehen  $L_1$  vom Kode ab  $0.71753375 - 0.5 = 0.21753375$ . Jetzt wird dieser Kode durch die Intervalllänge von  $S$  geteilt, um es auf den ursprünglichen Wert zu bringen  $0.21753375 / 0.5 = 0.4350675$ . Jetzt sieht man direkt, dass dieser Wert im Intervall  $W = [0.4, 0.5]$  liegt. Diesen errechneten Wert (0.4350675) bezeichnen wir mit `RANGE`. Die weitere Dekodierung ist in Tabelle 2.5 zusammengefasst.

| Symbol   |     | Berechnung von $H$ und $L$                                  |

|----------|-----|-------------------------------------------------------------|

| S        | $L$ | $0.0 + (1.0 - 0.0) \cdot 0.5 = 0.5$                         |

|          | $H$ | $0.0 + (1.0 - 0.0) \cdot 1.0 = 1.0$                         |

| W        | $L$ | $0.5 + (1.0 - 0.5) \cdot 0.4 = 0.70$                        |

|          | $H$ | $0.5 + (1.0 - 0.5) \cdot 0.5 = 0.75$                        |

| I        | $L$ | $0.7 + (0.75 - 0.7) \cdot 0.2 = 0.71$                       |

|          | $H$ | $0.7 + (0.75 - 0.7) \cdot 0.4 = 0.72$                       |

| S        | $L$ | $0.71 + (0.72 - 0.71) \cdot 0.5 = 0.715$                    |

|          | $H$ | $0.71 + (0.72 - 0.71) \cdot 1.0 = 0.72$                     |

| S        | $L$ | $0.715 + (0.72 - 0.715) \cdot 0.5 = 0.7175$                 |

|          | $H$ | $0.715 + (0.72 - 0.715) \cdot 1.0 = 0.72$                   |

| $\sqcup$ | $L$ | $0.7175 + (0.72 - 0.7175) \cdot 0.0 = 0.7175$               |

|          | $H$ | $0.7175 + (0.72 - 0.7175) \cdot 0.1 = 0.71775$              |

| M        | $L$ | $0.7175 + (0.71775 - 0.7175) \cdot 0.1 = 0.717525$          |

|          | $H$ | $0.7175 + (0.71775 - 0.7175) \cdot 0.2 = 0.717550$          |

| I        | $L$ | $0.717525 + (0.71755 - 0.717525) \cdot 0.2 = 0.717530$      |

|          | $H$ | $0.717525 + (0.71755 - 0.717525) \cdot 0.4 = 0.717535$      |

| S        | $L$ | $0.71753 + (0.717535 - 0.71753) \cdot 0.5 = 0.7175325$      |

|          | $H$ | $0.71753 + (0.717535 - 0.71753) \cdot 1.0 = 0.717535$       |

| S        | $L$ | $0.7175325 + (0.717535 - 0.7175325) \cdot 0.5 = 0.71753375$ |

|          | $H$ | $0.7175325 + (0.717535 - 0.7175325) \cdot 1.0 = 0.717535$   |

Tabelle 2.4: Kodierung von SWISS $\sqcup$ MISS

## 2.4 Beweis der Eindeutigkeit

Sei  $\bar{T}_x(x)$  eine Nummer im Intervall  $[0, 1]$ . Einen binären Kode für diese Nummer können wir erhalten, indem wir die binäre Darstellung nehmen und auf  $l(x) = \lceil \log_b(\frac{1}{p(x)}) \rceil + 1$  Bits beschränken.

Wir erinnern uns, dass  $\bar{T}_x(x)$  ein Kode für die Sequenz  $S$  ist. Um zu beweisen, dass  $\lfloor \bar{T}_x(x) \rfloor_{l(x)}$  eindeutig ist, müssen wir lediglich zeigen, dass es im Intervall  $[F_x(x-1), F_x(x))$  liegt.

Durch das Runden von  $\lfloor \bar{T}_x(x) \rfloor_{l(x)}$  gilt  $\lfloor \bar{T}_x(x) \rfloor_{l(x)} \leq \bar{T}_x(x)$ . Damit ist

$$0 \leq \bar{T}_x(x) - \lfloor \bar{T}_x(x) \rfloor_{l(x)} < \frac{1}{2^{l(x)}} \quad (2.8)$$

| $i$ | Symbol | Kode - $L_i = / (H_i - L_i)$    | = range            |

|-----|--------|---------------------------------|--------------------|

| 1   | S      | $0.71753375 - 0.5 = 0.21753375$ | $/0.5 = 0.4350675$ |

| 2   | W      | $0.4350675 - 0.4 = 0.0350675$   | $/0.4 = 0.350675$  |

| 3   | I      | $0.350675 - 0.2 = 0.150675$     | $/0.2 = 0.753375$  |

| 4   | S      | $0.753375 - 0.5 = 0.253375$     | $/0.5 = 0.50675$   |

| 5   | S      | $0.50675 - 0.5 = 0.00675$       | $/0.5 = 0.0135$    |

| 6   | U      | $0.0135 - 0.0 = 0.0135$         | $/0.1 = 0.135$     |

| 7   | M      | $0.135 - 0.1 = 0.035$           | $/0.1 = 0.35$      |

| 8   | I      | $0.35 - 0.2 = 0.15$             | $/0.2 = 0.75$      |

| 9   | S      | $0.75 - 0.5 = 0.25$             | $/0.5 = 0.5$       |

| 10  | S      | $0.5 - 0.5 = 0.0$               | $/0.5 = 0.0$       |

**Tabelle 2.5:** Dekodierung von SWISSLUMISS

Weil  $\bar{T}_x(x)$  die Hälfte vom Intervall  $[F_x(x-1), F_x(x))$  ist, gilt

$$\begin{aligned} \bar{T}_x(x) &< F_x(x) \\ \lfloor \bar{T}_x(x) \rfloor_{l(x)} &< \bar{T}_x(x) < F_x(x) \\ \lfloor \bar{T}_x(x) \rfloor_{l(x)} &< F_x(x) \end{aligned}$$

Jetzt müssen wir noch zeigen, dass  $\lfloor \bar{T}_x(x) \rfloor_{l(x)} \geq F_x(x-1)$ . Mit

$$\begin{aligned} \frac{1}{2^{l(x)}} &= \frac{1}{2^{\lceil \log_b(\frac{1}{p(x)}) \rceil + 1}} \\ &< \frac{1}{2^{\log_b(\frac{1}{p(x)}) + 1}} \\ &= \frac{1}{2^{\frac{1}{p(x)}}} \\ &= \frac{p(x)}{2} \end{aligned}$$

Aus Gleichung (2.4) wissen wir

$$\frac{p(x)}{2} = \bar{T}_x(x) - F_x(x-1)$$

und damit auch

$$\bar{T}_x(x) - F_x(x-1) > \frac{1}{2^{l(x)}} \tag{2.9}$$

Kombinieren wir Gleichung (2.8) und (2.9) erhalten wir

$$\lfloor \bar{T}_x(x) \rfloor_{l(x)} > F_x(x-1)$$

Damit ist  $\lfloor \bar{T}_x(x) \rfloor_{l(x)}$  eine eindeutige Repräsentierung von  $\bar{T}_x(x)$ .

Um jetzt zu zeigen, dass dieser Kode auch eindeutig dekodierbar ist, zeigen wir dass es ein Präfix Kode ist. Das heisst, kein Kode ist Präfix eines anderen Kodes. Weil ein Präfix Kode immer eindeutig dekodierbar ist, reicht es zu zeigen, dass  $\lfloor \bar{T}_x(x) \rfloor_{l(x)}$  ein Präfix Kode ist.

Falls  $x$  und  $y$  zwei verschiedene Sequenzen sind, wissen wir, dass  $\lfloor \bar{T}_x(x) \rfloor_{l(x)}$  und  $\lfloor \bar{T}_x(y) \rfloor_{l(y)}$  in zwei unterschiedlichen Intervallen  $[F_x(x-1), F_x(x))$  und  $[F_x(y-1), F_x(y))$  liegen. Falls wir also zeigen können, dass für jede Sequenz  $x$  das Intervall  $[\lfloor \bar{T}_x(x) \rfloor_{l(x)}, \lfloor \bar{T}_x(x) \rfloor_{l(x)} + 2^{l(x)}]$  ganz in  $[F_x(x-1), F_x(x))$  liegt, kann  $x$  kein Präfix für einen anderen Kode sein.

Wir wissen bereits, dass  $\lfloor \bar{T}_x(x) \rfloor_{l(x)} > F_x(x-1)$ . Was wir noch zeigen müssen ist

$$F_x(x) - \lfloor \bar{T}_x(x) \rfloor_{l(x)} > 2^{l(x)}$$

und das gilt, weil:

$$\begin{aligned} F_x(x) - \lfloor \bar{T}_x(x) \rfloor_{l(x)} &> F_x(x) - \bar{T}_x(x)_{l(x)} \\ &= \frac{p(x)}{2} \\ &> \frac{1}{2^{l(x)}} \end{aligned}$$

## 2.5 Effizienz

Wir haben gezeigt, dass die Anzahl  $l(x)$  der benötigten Bits um  $F_x(x)$  eindeutig zu dekodieren

$$l(x) = \lceil \log_b \left( \frac{1}{p(x)} \right) \rceil + 1$$

ist.  $l(x)$  ist die Zahl der benötigten Bits für die gesamte Sequenz  $x$ . Für die Sequenz der Länge  $|x| = m$  gilt demnach

$$\begin{aligned} l_{A^m} &= \sum p(x) l(x) \\ &= \sum p(x) \left[ \lceil \log_b \left( \frac{1}{p(x)} \right) \rceil + 1 \right] \\ &< \sum p(x) \left[ \log_b \left( \frac{1}{p(x)} \right) + 1 + 1 \right] \\ &= - \sum p(x) \log_b p(x) + 2 \sum p(x) \\ &= E(x^m) + 2 \end{aligned}$$

Weil die durchschnittliche Länge immer größer als die Entropie ist, können wir für  $l(x)$  die Grenzen

$$E(x^m) \leq l_{A^m} < E(x^m) + 2$$

festlegen. Die durchschnittliche Länge pro Symbol  $l_A$  ist  $\frac{l_A m}{m}$ . Durch Einsetzen gilt damit

$$\frac{E(x^m)}{m} \leq l_A < \frac{E(x^m)}{m} + \frac{2}{m}$$

und mit  $E(x^m) = mE(x)$  erhalten wir

$$E(x) \leq l_A < E(x) + \frac{2}{m}$$

Desto länger also die Länge  $m$  der Sequenz, desto näher kommen wir an die Entropie.

## 2.6 Kodierung als begrenzte Festkommazahl

Je länger die Quelle, desto länger der Kode und damit umso höher die Präzision. Die derzeitigen Rechner sind sehr ineffizient, wenn es um Rechnungen beliebiger Genauigkeit geht. Je länger die Quelle, desto länger der Kode und damit umso höher die Präzision. Man stelle sich eine Quelle von 1 MByte vor. Selbst bei einer Komprimierung auf die Hälfte wäre das Teilen einer 500 kByte großen Zahl sehr komplex und aufwendig. Das war Jahrzehnte lang das Hindernis für eine praktische Verwendung des Arithmetischen Kodierens. Pasco und Rissanen haben unabhängig voneinander das Problem gelöst, indem sie einen Algorithmus entwarfen, mit dem man mit einer begrenzten Festkommazahl dennoch einen Kode generieren kann. Die Vorgehensweise, die hier vorgestellt wird, lehnt sich an die von Witten [WNC87] an.

### 2.6.1 Abbildung auf Ganze Zahlen

Für das Arithmetische Kodieren verwendet man am besten Ganzzahl-Variablen (integer Variable) statt Fließkomma-Variablen (floating point Variable), weil in der Fließkommaarithmetik Genauigkeit verloren geht<sup>2</sup>. Um möglichst den ganzen Bereich der Ganzzahl-Variablen zu nutzen, bilden wir die 0 auf die 0 ab und die 1 auf die 0.9, denn  $0.9 = 1$ . Diesen Bereich kann man so erweitern, dass keine Dezimalstelle mehr notwendig wird. Das ergibt für eine Ganzzahl-Variable die höchstmögliche darstellbare Zahl.

**Beispiel 7.** Eine integer Variable der Länge 4 kann im Dezimalsystem die Werte 0000 . . . 9999 annehmen. 9999 ist der höchste Wert. In diesem Fall würde man also  $L = 0000$  und  $H = 9999$  setzen, um alle Möglichkeiten dieser Variablen zu nutzen.

Eine Variable mit der Bitbreite 4 kann im Dualsystem die Werte 0000<sub>b</sub> . . . 1111<sub>b</sub> annehmen. Wobei hier 1111<sub>b</sub> der höchste Wert ist. Analog wäre hier  $L = 0000_b$  und  $H = 1111_b$ . ◇

<sup>2</sup>Eine Ganzzahl-Variable kann mehr Werte annehmen als eine Fließkomma-Variable derselben Bit Breite

Das tiefgestellte «b» bedeutet, dass die Zahl im Dualsystem geschrieben ist. In den Fällen, an denen es nicht eindeutig ist in welchem System wir uns befinden, benutzen wir «d» für dezimal oder «h» für hexadezimal.

Daraus ergibt sich die interessante Frage nach der Auswirkung, die das Abbilden von unendlich vielen Zahlen auf eine endlich viele Menge auf den Algorithmus hat.

Wir definieren

$$r_i = H_i - L_i \quad (2.10)$$

als die Intervalllänge `range`.

Wenn wir wie im Beispiel 7  $H_0 = 1111$  setzen und damit das Intervall  $[L_0, H_0)$  berechnen, kommt als Ergebnis

$$r_0 = H_0 - L_0 = 1111 - 0000 = 1111$$

heraus. Das entspricht aber nicht dem vollen Intervall. Dieser ist nämlich  $1.0_d$  und  $H_0$  wurde auf  $0.\bar{9}_d$  abgebildet. Um dieser Tatsache nachzukommen, muss, falls mittels  $H$  die `range` berechnet wird, noch  $1_b$  hinzugaddiert werden.

Das hat aber eine Auswirkung auf die zu wählende Bit Breite. Für dasselbe Beispiel würde bei einer Bit Breite von 4 Bits  $H_0 = 1111$  bei Addition von 1 ein Überlauf stattfinden. Deshalb muss man bei der Wahl der Bit Breite 1 Bit Puffer hinzufügen.

Für die Berechnung von `range` schreiben wir

$$\text{range}_i = H_i - L_i + 1$$

Wir wissen, dass  $F_x(i)$  die kumulative Verteilungsfunktion für  $a_i$  ist. Also folgt daraus

$$F_x(i) = \frac{\text{high\_count}_i}{\text{total}} \quad (2.11)$$

Weiter gilt

$$F_x(i-1) = \frac{\text{high\_count}_{i-1}}{\text{total}} = \frac{\text{low\_count}_i}{\text{total}}$$

Wir setzen

$$\text{high\_count}_i = \text{cum\_count}_i \quad (2.12)$$

und

$$\text{step}_i = \text{range}_i / \text{total}$$

Setzen wir die Gleichungen (2.10), (2.11), und (2.12) in Gleichung (2.7) ein, ergibt das

$$\begin{aligned}

L_i &= L_{i-1} + \text{range}_{i-1} \cdot \frac{\text{low\_count}_i}{\text{total}} \\

&= L_{i-1} + \frac{\text{range}_{i-1} \cdot \text{low\_count}_i}{\text{total}} \\

&= L_{i-1} + \frac{\text{range}_{i-1} \cdot \text{cum\_count}_{i-1}}{\text{total}} \\

&= L_{i-1} + \text{step}_{i-1} \cdot \text{cum\_count}_{i-1}

\end{aligned} \tag{2.13}$$

Und für  $H_i$

$$H_i = L_{i-1} + \text{step}_{i-1} \cdot \text{cum\_count}_i - 1 \tag{2.14}$$

Man beachte hier die  $-1$  bei  $H_i$ . Wie schon erwähnt wird  $H$  um 1 verringert, um die nach oben offene Intervallgrenze darzustellen.

Weiterhin werden wir später sehen, dass es eine wichtige Rolle spielt, wann man durch  $\text{total}$  teilt. Nun können wir uns dem Problem der endlichen Präzision widmen.

### 2.6.2 Skalierung bei Überlauf

Wenn man sich die Tabelle 2.4 anschaut, dann fällt auf, dass sobald eine der höherwertigen Ziffern bei  $L$  und  $H$  gleich sind, sich diese nicht mehr ändern. Die Erklärung ist, dass sich ein Intervall, sobald er einen Wertebereich eingenommen hat, diesen nicht mehr verlassen kann. Bei jedem Schritt wird ein Intervall in Teilintervalle geteilt, die alle innerhalb des (Ursprungs-)Intervalls liegen. Wenn also eine Stelle von links bei  $H$  und  $L$  gleich sind, braucht man diese für die weitere Berechnung nicht und kann diese Ziffer als Kode herausziehen. Wir nennen das hier – eher willkürlich – den ÜBERLAUF<sup>3</sup>. Im Dezimalsystem ist das dann der Fall, wenn das Intervall um eine Zehnerpotenz kleiner geworden ist als der ursprüngliche Intervall; hier also ein Zehntel so groß wie vorher ( $10^{-1} = 0.1$ ). Sei  $B$  die Basis des verwendeten Systems, dann ist die Skalierung bei Erreichen von  $sc$  durchführbar. Die Gleichung dafür ist

$$sc = B^{-1}$$

Im Dualen System entspricht eine Stelle einer Zweierpotenz. Hier findet der Überlauf bei der Hälfte ( $2^{-1} = 0.5$ ) des Ursprungs-Intervalls statt. Ist das höchstwertigste Bit von  $L$  und  $H$  gleich, dann ist das Intervall nur noch halb so groß wie ursprünglich. Das höchstwertigste Bit kann als Kode nach links heraus geschoben werden. Für  $L$  wird von rechts eine 0 und für  $H$  eine 1 nach geschoben. Das höchstwertige Bit ist dann bei  $L$  und  $H$  gleich, wenn beide Grenzen entweder in der unteren Hälfte oder beide in der oberen Hälfte des Intervalls liegen.

<sup>3</sup>vielleicht angelehnt an die Tatsache, dass der Wert nach links, also höherwertig, überläuft

Jetzt können wir konkreter werden und zu einem Beispiel übergehen, welches später auch in Hardware realisiert werden wird. Dieses Beispiel soll den Anspruch haben, möglichst klein zu sein und dennoch sämtliche Fälle abzudecken. Dieses Beispiel ist aus [BCKo2] entnommen.

**Beispiel 8.** Ein Alphabet mit  $A = \{a, b, c, d, e\}$  sei gegeben. Wir wollen die Sequenz  $S = abccedac$  kodieren. Dann ist  $|S| = \text{total} = 8$ .

Das Modell ergibt dann Tabelle 2.6

| Symbol    | tot_count | low_count | high_count |

|-----------|-----------|-----------|------------|

| $a_1 = a$ | 2         | 0         | 2          |

| $a_2 = b$ | 1         | 2         | 3          |

| $a_3 = c$ | 3         | 3         | 6          |

| $a_4 = d$ | 1         | 6         | 7          |

| $a_5 = e$ | 1         | 7         | 8          |

**Tabelle 2.6:** Modell für Zeichenfolge «abccedac»

Als Bit Breite wählen wir 8 Bits und können somit die unteren 7 Bits für die Kodierung nutzen. Das achte Bit ist nur für den Überlauf. Für uns gilt also das siebte Bit als das oberste. Zur besseren Lesbarkeit verwenden wir das Hexadezimalsystem und geben es andernfalls explizit an.  $L$  und  $H$  werden nun mit

$$L_0 = 00_h = 00000000_b$$

$$H_0 = 7F_h = 01111111_b$$

initialisiert. Wir lesen das erste Symbol  $a$  ein und erhalten mit den Formeln (2.13) und (2.14)

$$\begin{aligned} \text{range}_0 &= 7F - 00 + 1 = 80 \\ \text{step}_0 &= 80/8 = 10 \\ L_1 &= 00 + \text{step}_0 \cdot \text{cum\_count}_0 = 00 + 10 \cdot 0 = 00 \\ H_1 &= 00 + \text{step}_0 \cdot \text{cum\_count}_1 - 1 = 00 + 10 \cdot 2 - 1 = 20 - 1 = 1F \end{aligned}$$

Wir sehen, dass die oberen zwei Bits von  $H$  und  $L$  gleich sind ( $00$ )<sub>b</sub>. Das sind also die ersten zwei Kode Bits. Wir schieben diese raus und erhalten für  $L$  und  $H$

$$\begin{aligned} L_1 &= 00 \\ H_1 &= 3F \end{aligned}$$

Wir nennen diesen Vorgang die SKALIERUNG oder auch NORMALISIERUNG von  $L$  und  $H$ . Der Algorithmus in C dafür ist in Listing 2.1 präsentiert. Wir schieben  $L$  und  $H$  und zwei bits nach links und fügen jeweils 0 bzw. 1 nach.

$$L_1 = 00$$

$$H_1 = 7F$$

Jetzt lesen wir b ein und erhalten mit den Formeln (2.13) und (2.14)

$$\text{range}_1 = 7F - 00 + 1 = 80$$

$$\text{step}_1 = 80/8 = 10$$

$$L_2 = 00 + \text{step}_1 \cdot \text{cum\_count}_1 = 00 + 10 \cdot 2 = 20$$

$$H_2 = 00 + \text{step}_1 \cdot \text{cum\_count}_2 - 1 = 00 + 10 \cdot 3 - 1 = 30 - 1 = 2F$$

Wir sehen, dass die oberen drei Bits von  $H$  und  $L$  gleich sind  $(010)_b$ . Wir schieben diese raus und erhalten für  $L$  und  $H$

$$L_2 = 00$$

$$H_2 = 7F$$

Und so fahren wir fort. Der Kode für diese zwei Buchstaben ist 00010.  $\diamond$

### 2.6.3 Skalierung bei Unterlauf

Es kann passieren, dass sich das Intervall immer um die Mitte des Intervalls (range) verkleinert. Dann bleibt  $L$  in der unteren und  $H$  in der oberen Hälfte des Intervalls. In diesem Fall bleiben die oberen Bits gleich und eine Skalierung ist nicht möglich. Das führt irgend wann dazu, dass die Präzision für das Kodieren nicht mehr reicht. Wir benennen das — auch wieder willkürlich — UNTERLAUF.<sup>4</sup> Dieses Problem des Unterlaufs löst man folgendermaßen:

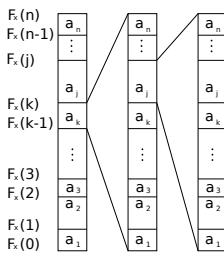

Der Unterlauf entsteht nur, wenn  $L$  in der unteren Hälfte und  $H$  in der oberen Hälfte des Intervalls ist. Dann ist das höchste Bit von  $L$  gleich 0 und von  $H$  gleich 1. Sobald das zweithöchste Bit von  $L$  Eins ist, und von  $H$  Null, ist das Intervall innerhalb der Grenzen des zweiten und dritten Quadranten. Das heißt es könnte wieder skaliert werden, denn dann ist es kleiner als die Hälfte des ursprünglichen Intervalls. Wir erweitern das Intervall, indem von  $L$  und  $H$  ein Viertel des Gesamt-Intervalls abziehen und dann verdoppeln. Allerdings wissen wir noch nicht, in welche Hälfte des Intervalls das Teil-Intervall fallen wird.

<sup>4</sup>im Gegensatz zum Überlauf, läuft der Wert hier nach rechts runter

**Abbildung 2.3:** Intervalleinteilung in Quadranten

Deshalb wird skaliert, und gleichzeitig ein Zähler inkrementiert, der solange zählt, bis wieder eine Skalierung wegen eines Überlaufs stattfindet. Erst hier wird dann wieder Kode generiert. Falls die höchsten Bits Null waren wird hier eine Eins kodiert und dann werden so viele Nullen wie der Zähler gezählt hat hinzugefügt. Falls die höchsten Bits beide Eins waren, wird eine Null und entsprechend dem Zähler so viele Einsen kodiert. Einen Beweis dafür, dass das in der Folge geht liefert E. Bodden M. Clasen und J. Kneiss in [BCKo2]. Wir wollen diesen Vorgang zum besseren Verständnis hier erklären.

Wir benennen die einzelnen Skalierungen wie folgt

$E1$  = Überlauf Skalierung in der unteren Hälfte des Intervalls

$E2$  = Überlauf Skalierung in der oberen Hälfte des Intervalls

$E3$  = Skalierung bei Unterlauf

Weiter soll  $g \circ f$  die hintereinander Ausführung von  $f$  und danach  $g$  bedeuten.

Im Falle, dass sich das Intervall um die Mitte des Ursprungs Intervalls verkleinert entsteht die Folge  $(E1)^n \circ (E2)$  oder  $(E2)^n \circ (E1)$  von Skalierungen. Aus der oben genannten Problematik würden wir aber nicht Skalieren können, weil sich die oberen Bits nie gleichen. Mit der  $E3$  Skalierung erreichen wir folgende Gleichheiten:

$$E1 \circ (E3)^n = (E2)^n \circ (E1)$$

$$E2 \circ (E3)^n = (E1)^n \circ (E2)$$

und können  $n$  mal  $E3$  skalieren, bis eine Überlauf Skalierung eintritt, bei der dann der Kode ausgegeben wird.

**Beweis für den Algorithmus der Unterlauf Skalierung 1.** Die Skalierungsfunktionen sehen wie folgt aus

$$\begin{aligned} E1 \begin{pmatrix} L \\ H \end{pmatrix} &= \begin{pmatrix} 2L \\ 2H \end{pmatrix} \\ E2 \begin{pmatrix} L \\ H \end{pmatrix} &= \begin{pmatrix} 2L - 1 \\ 2H - 1 \end{pmatrix} \\ E3 \begin{pmatrix} L \\ H \end{pmatrix} &= \begin{pmatrix} 2L - (1/2) \\ 2H - (1/2) \end{pmatrix} \end{aligned}$$

Die erste Iteration ergibt

$$\begin{aligned} (E1 \circ E1) \begin{pmatrix} L \\ H \end{pmatrix} &= \begin{pmatrix} 2 \cdot 2L \\ 2 \cdot 2H \end{pmatrix} = \begin{pmatrix} 2^2 L \\ 2^2 H \end{pmatrix} \\ (E2 \circ E2) \begin{pmatrix} L \\ H \end{pmatrix} &= \begin{pmatrix} 2 \cdot (2L - 1) - 1 \\ 2 \cdot (2H - 1) - 1 \end{pmatrix} = \begin{pmatrix} 2^2 L - 3 \\ 2^2 H - 3 \end{pmatrix} = \begin{pmatrix} 2^2 L - 2^2 - 1 \\ 2^2 H - 2^2 - 1 \end{pmatrix} \\ (E3 \circ E3) \begin{pmatrix} L \\ H \end{pmatrix} &= \begin{pmatrix} 2 \cdot (2L - 0.5) - 0.5 \\ 2 \cdot (2H - 0.5) - 0.5 \end{pmatrix} = \begin{pmatrix} 2^2 L - 1.5 \\ 2^2 H - 1.5 \end{pmatrix} = \begin{pmatrix} 2^2 L - 2^1 + 0.5 \\ 2^2 H - 2^1 + 0.5 \end{pmatrix} \end{aligned}$$

und die  $n$ -te

$$\begin{aligned} E1^n \begin{pmatrix} L \\ H \end{pmatrix} &= \begin{pmatrix} 2^n L \\ 2^n H \end{pmatrix} \\ E2^n \begin{pmatrix} L \\ H \end{pmatrix} &= \begin{pmatrix} 2^n L - 2^n + 1 \\ 2^n H - 2^n + 1 \end{pmatrix} \\ E3^n \begin{pmatrix} L \\ H \end{pmatrix} &= \begin{pmatrix} 2^n L - 2^{n-1} + 0.5 \\ 2^n H - 2^{n-1} + 0.5 \end{pmatrix} \end{aligned}$$

Einen Beweis für diese Folgerung liefert eine vollständige Induktion. Mit

$$(E1 \circ (E3)^n) \begin{pmatrix} L \\ H \end{pmatrix} = E1 \begin{pmatrix} 2^n L - 2^{n-1} + 0.5 \\ 2^n H - 2^{n-1} + 0.5 \end{pmatrix} = \begin{pmatrix} 2^{n+1} L - 2^n + 1 \\ 2^{n+1} H - 2^n + 1 \end{pmatrix} \quad (2.15)$$

$$((E2)^n \circ E1) \begin{pmatrix} L \\ H \end{pmatrix} = (E2)^n \begin{pmatrix} 2L \\ 2H \end{pmatrix} = \begin{pmatrix} 2^{n+1} L - 2^n + 1 \\ 2^{n+1} H - 2^n + 1 \end{pmatrix} \quad (2.16)$$

Damit gilt mit den Gleichungen (2.15) und (2.16)

$$E1 \circ (E3)^n = (E2)^n \circ E1$$

□

**Beispiel 9.** Wir nehmen Beispiel 8 wieder auf und lesen als nächstes den Buchstaben c ein.

$$\text{range}_2 = 7F - 00 + 1 = 80$$

$$\text{step}_2 = 80/8 = 10$$

$$L_3 = 00 + \text{step}_2 \cdot \text{cum\_count}_2 = 00 + 10 \cdot 3 = 30 = 0011\_0000_b$$

$$H_3 = 00 + \text{step}_2 \cdot \text{cum\_count}_3 - 1 = 00 + 10 \cdot 6 - 1 = 60 - 1 = 5F = 0101\_1111_b$$

Die Bits 7 sind ungleich, aber Bit 6 ist bei  $L$  Eins und bei  $H$  Null. Das Intervall liegt im zweiten und dritten Quadranten und kann skaliert werden. Wir merken uns, dass einmal für den Unterlauf skaliert wurde.

$$L_3 = 30 - 20 = 10 = 0001\_0000_b$$

$$H_3 = (5F - 20) \cdot 2 = 7E = 1101\_1110_b$$

Bit 8 wird maskiert, und zu  $H$  noch 1 addiert:

$$L_3 = 20 = 0010\_0000_b$$

$$H_3 = 7F = 0101\_1111_b$$

Erst wenn eine Skalierung aufgrund eines Überlaufs entsteht, wird der Kode generiert und ausgegeben. ◇

Die Details kann man aus dem Algorithmus in C vom Listing 2.1 entnehmen.

Die vollständige Kodierung ist in Tabelle 2.7 zusammengefasst. Der so erhaltene Kode ist  $00010101001101111_b$ .

**Listing 2.1** Algorithmus für Kodierung (Bit Breite 8)

---

```

...

for (;;)

{

t1 = *low & 0x40; t2 = *high & 0x40;

if ( t1 == t2 ) // check high bit

{ // overflow

if ( t1 >= 1 ) // high bit is 1

{

setbit (output, output_counter, 1);

while ( *udcount > 0 )

{

setbit (output, output_counter, 0);

(*udcount)--;

}

}

else

{

setbit (output, output_counter, 0);

while ( *udcount > 0 )

{

setbit (output, output_counter, 1);

(*udcount)--;

}

}

shift ( low, high );

}

else

{ // check for underflow

t1 = *low & 0x20; t2 = *high & 0x20;// second highest bit

if ( t1 > t2 )

{

do { // shift low and high but no output

(*udcount)++;

*low = *low & 0x1f; // same as subtracting 20 as bit must be 1

*high = *high | 0x20; // same as adding 20 as bit must be 0

shift ( low, high );

t1 = *low & 0x20;

t2 = *high & 0x20;

} while ( t1 > t2 );

}

else

{ // no more shifting

break;

}

}

}

...

void shift ( unsigned short *low, unsigned short *high )

{

*low <= 1;

*high <= 1;

*high = *high | 0x01; // same as adding one

/* mask high bit as it's not used for calculation */

*low = *low & 0x7f;

*high = *high & 0x7f;

}

```

---

| Sym  | lc | hc | rng | $L_i$        | $H_i$        | KdBts | ÜL-Low       | ÜL-High      | cnt | UNL-Low      | UNL-High     |

|------|----|----|-----|--------------|--------------|-------|--------------|--------------|-----|--------------|--------------|

| a    | 0  | 2  | 10  | 0000000 [0]  | 0011111 [1F] | 00    | 0000000 [0]  | 1111111 [7F] | 0   |              |              |

| b    | 2  | 3  | 10  | 0100000 [20] | 0101111 [2F] | 010   | 0000000 [0]  | 1111111 [7F] | 0   |              |              |

| c    | 3  | 6  | C   | 0110000 [30] | 1011111 [57] |       |              |              | 1   | 0100000 [20] | 1111111 [7F] |

| c    | 3  | 6  | 9   | 1000100 [44] | 1100111 [67] | 10    |              |              | 0   | 0001000 [8]  | 1001111 [4F] |

| e    | 7  | 8  | 9   | 1000111 [47] | 1001111 [4F] | 100   | 0111000 [38] | 1111111 [7F] | 0   |              |              |

| d    | 6  | 7  | 9   | 1101111 [6E] | 1110110 [76] | 11    | 0111000 [38] | 1011011 [5B] | 1   | 0110000 [30] | 1110111 [77] |

| a    | 0  | 2  | 9   | 0110000 [30] | 1000001 [41] |       |              |              | 3   | 0000000 [00] | 1000111 [47] |

| c    | 2  | 3  | 9   | 0011011 [1B] | 0110101 [35] | 0111  | 0110110 [36] | 1101011 [3B] | 0   |              |              |

| rest |    |    |     |              |              | 1     |              |              |     |              |              |

Tabelle 2.7: Kodierung von «abccedac»

Sym Symbol

lc low\_count

hc high\_count

$L_i$  untere Grenze des Intervalls beim Buchstaben  $i$

$H_i$  obere Grenze des Intervalls beim Buchstaben  $i$

KdBts Kode Bits

ÜL-Low untere Grenze des Intervalls nach einer Überlauf Skalierung

ÜL-High obere Grenze des Intervalls nach einer Überlauf Skalierung

cnt Zähler für Unterlauf Skalierung

UNL-Low untere Grenze des Intervalls nach einer Unterlauf Skalierung

UNL-High obere Grenze des Intervalls nach einer Unterlauf Skalierung

## 2.7 Dekodierung als begrenzte Festkommazahl

Das Dekodieren als begrenzte Festkommazahl unterscheidet sich nicht wesentlich vom dem im Kapitel 2.3 vorgestellten Verfahren. Hinzu kommt nur, dass man hier die Überlauf- und Unterlauf-Skalierungen berücksichtigen muss.

Beim Puffer  $\text{buf}$ , der den Kode enthält, muss man beim links Schieben die nächsten Bits des Kodes nachschieben. Also anders als die festen Werte die Bei  $L$  und  $H$  nachgeschoben werden.

Die Subtraktion von einem Quadranten bei der Unterlauf Skalierung kann man durch einfache Bit Manipulation sowohl für  $L$ ,  $H$  als auch  $\text{buf}$  ersetzen. Nur die oberen Bits sind von Bedeutung. Wir lassen die unteren Bits weg und schreiben dafür  $XXX\cdots$ . Betrachten wir als ersten den Fall  $L$ . Das Puffer-Bit ist eingeklammert, weil es für die Rechnung nicht relevant ist.

$$(0)010\cdots_b \leq L \leq (0)011\cdots_b$$

oder mit anderen Worten:  $L$  liegt im zweiten Quadranten. (siehe auch Bild 2.3 Damit ist das zweithöchste Bit immer gesetzt. Das entspricht einem Viertel des Intervalls. Setzt man dieses Bit auf 0, entspricht es dem Abzug von einem Viertel.

Für  $H$  gilt

$$(0)100\cdots_b \leq H \leq (0)101\cdots_b$$

oder mit anderen Worten:  $H$  liegt im dritten Quadranten. Zwar manipuliert eine Subtraktion in der zweithöchsten Stelle auch die höchste Stelle, diese wird aber bei der anschließenden Multiplikation mit 2 raus geschoben und hat damit keine Relevanz. Wir können also einfach das zweithöchste Bit von 0 auf 1 setzen.

Für  $\text{buf}$  ist die Betrachtung ähnlich. Der Wertebereich ist jedoch größer:

$$(0)010\cdots_b \leq \text{buf}_b \leq (0)101\cdots_b$$

Wir haben aber gesehen, dass sowohl für  $L$  als auch für  $H$  das zweithöchste Bit einfach negiert wird. Diese Regel gilt also für den gesamten Bereich von  $\text{buf}$ . Wir können damit die Subtraktion von einem Viertel so formulieren:

$$\text{buf}_b = \text{buf}_b \text{ xor } (0)010\cdots_b$$

Wir verzichten an dieser Stelle auf ein Beispiel und zeigen den Algorithmus in Listing 2.2. Das Ergebnis der Dekodierung ist in Tabelle 2.8 dargestellt.

---

**Listing 2.2** Algorithmus für Dekodierung (Bit Breite 8)

---

```

...

for (;;)

{

t1 = *low & 0x4000;

t2 = *high & 0x4000;

if ( t1 == t2 )

{

// overflow

while ( *udcount > 0 )

{

(*udcount)--;

}

shift_d ( low, high, buf, output, output_counter );

}

else

{

// check for underflow

t1 = *low & 0x20;

t2 = *high & 0x20;

if ( t1 > t2 )

{

*low = *low & 0x1f;

*high = *high | 0x20;

*buf = *buf ^ 0x20;

shift_d ( low, high, buf, output, output_counter );

(*udcount)++;

}

else

{

// no more shifting

break;

}

}

}

...

void shift_d ( unsigned short *low, unsigned short *high,

unsigned short *buf, int *output, int *output_counter )

{

*low <= 1;

*high <= 1;

*high = *high | 0x01;

*buf <= 1;

*buf = *buf | output[ *output_counter ];

(*output_counter)++;

*low = *low & 0x7f;

*high = *high & 0x7f;

*buf = *buf & 0x7f;

}

```

---

| S | lc | hc | buf          | rg | $L_i$         | $H_i$         | KB   | ÜL-Low        | ÜL-High       | cn | UNL-Low       | UNL-High      |

|---|----|----|--------------|----|---------------|---------------|------|---------------|---------------|----|---------------|---------------|

| a | 0  | 2  | 0001010 [0A] | 10 | 00000000 [0]  | 00111111 [1F] | 00   | 0000000 [0]   | 00111111 [1F] | 0  |               |               |

| b | 2  | 3  | 0101010 [2A] | 10 | 01000000 [20] | 01011111 [2F] | 010  | 01000000 [20] | 01011111 [2F] | 0  |               |               |

| c | 3  | 6  | 1010011 [53] | 10 | 01100000 [30] | 10111111 [57] |      |               |               | 1  | 01100000 [30] | 10111111 [5F] |

| c | 3  | 6  | 1100110 [66] | C  | 1000100 [44]  | 11001111 [67] | 10   | 0001000 [8]   | 10011111 [AF] | 0  |               |               |

| e | 7  | 8  | 1001101 [4D] | E  | 1000111 [47]  | 10011111 [4F] | 100  | 0111000 [38]  | 11111111 [FB] | 0  |               |               |

| d | 6  | 7  | 1101111 [6F] | D  | 11011111 [6E] | 1110110 [76]  | 11   | 0111000 [38]  | 1011011 [EB]  | 1  | 01100000 [30] | 11101111 [77] |

| a | 0  | 2  | 0111000 [38] | A  | 01100000 [30] | 1000001 [41]  |      |               |               | 3  | 00000000 [00] | 1000111 [47]  |

| c | 2  | 3  | 0100000 [20] | C  | 0011011 [1B]  | 0110101 [35]  | 0111 |               |               | 0  |               |               |

Tabelle 2.8: Dekodierung von «abccedac»

S Symbol

lc low\_count

hc high\_count

buf Buffer mit dem Kode

$L_i$  untere Grenze des Intervalls beim Buchstaben  $i$

$H_i$  obere Grenze des Intervalls beim Buchstaben  $i$

KB Kode Bits

ÜL-Low untere Grenze des Intervalls nach einer Überlauf Skalierung

ÜL-High obere Grenze des Intervalls nach einer Überlauf Skalierung

cn Zähler für Unterlauf Skalierung

UNL-Low untere Grenze des Intervalls nach einer Unterlauf Skalierung

UNL-High obere Grenze des Intervalls nach einer Unterlauf Skalierung

## 3 Parallelisierung

Es wird zunehmend schwieriger, die Taktraten der Integrierten Schaltungen zu steigern. Die immer dichter werdenden Schaltungen erreichen die theoretisch machbaren Grenzen. Leckströme werden zunehmend zum Problem. Die Rechenleistung der heutigen Rechner lässt sich nicht mehr allein durch höhere Taktraten steigern.

Eine Möglichkeit, dennoch die Leistung zu steigern, ist das Parallelisieren. In Großrechenanlagen hat dieses Vorgehen schon längst Einzug gehalten. Inzwischen findet dieser Trend verstärkt Anwendung auch im PC. Moderne CPUs haben inzwischen acht Kerne und Intel hat kürzlich ein «cloud on chip» Prozessor mit 48 Kernen vorgestellt<sup>1</sup>. Grafikkarten werden mittlerweile nicht nur zur Darstellung und Berechnung von Polygonen benutzt, sondern vermehrt für allgemeine Berechnungen. Diese sogenannten GPGPU GENERAL-PURPOSE COMPUTING ON GRAPHICS PROCESSING UNIT mit hunderten von Kernen erreichen beeindruckende Geschwindigkeitssteigerungen. Diese GPGPUs verarbeiten die Daten doppelt bis dreißig Mal schneller als eine herkömmliche CPU<sup>2</sup>.

Doch der wesentliche Punkt ist, dass diese Geschwindigkeitssteigerungen nur erreicht werden können, wenn der zugrundeliegende Algorithmus auf die gegebene Architektur parallelisierbar ist. Es ist also entscheidend, ob der Algorithmus parallelisierbar ist und wenn ja, wie stark.

Dieser Frage wollen wir für das Arithmetische Kodieren nachgehen. Wie schon in Kapitel 2 (Arithmetisches Kodieren) erwähnt, hat es sehr lange gedauert, bis hierzu etwas veröffentlicht wurde. J. Jiang und S. Jones haben 1994 erstmals einen parallelen Algorithmus vorgeschlagen [JJ94]. Nur wenige Papers sind danach zu diesem Thema veröffentlicht worden. Wir wollen diese im Einzelnen vorstellen und hinsichtlich einer konkreten Umsetzung in Hardware analysieren.

<sup>1</sup><http://www.pcper.com/article.php?aid=825>

<sup>2</sup><http://code.google.com/p/pyrit/>

### 3.1 Parallelisierung nach J. Jiang und S. Jones

#### 3.1.1 Einleitung

Dieses Paper ist das erste, das zum Thema Parallelisierung des Arithmetischen Kodierens geschrieben wurde. In diesem Paper verwenden Jiang und Jones eine Vorwärtskonvention im Gegensatz zu einer Rückwärtskonvention. Damit ist die Bezeichnung des Teilintervalls gemeint. Bei unserer bisherigen Rückwärtskonvention gilt

$$p(x_i) = F_x(i) - F_x(i-1)$$

und bei einer Vorwärtskonvention

$$p(x_i) = F_x(i+1) - F_x(i)$$

Der Konsistenz wegen bleiben wir bei der Rückwärtskonvention.

Wir nehmen die Differenzengleichungen 2.6 und 2.7

$$\begin{aligned} L_i &= L_{i-1} + (H_{i-1} - L_{i-1}) \cdot F_x(i-1) \\ H_i &= L_{i-1} + (H_{i-1} - L_{i-1}) \cdot F_x(i) \end{aligned}$$

Weil

$$\begin{aligned} r_i &= H_i - L_i \\ &= [L_{i-1} + (H_{i-1} - L_{i-1}) \cdot F_x(i)] - [L_{i-1} + (H_{i-1} - L_{i-1}) \cdot F_x(i-1)] \\ &= (H_{i-1} - L_{i-1}) \cdot (F_x(i) - F_x(i-1)) \\ &= r_{i-1} \cdot (F_x(i) - F_x(i-1)) \\ &= r_{i-1} \cdot p(x_i) \end{aligned} \tag{3.1}$$

und

$$\begin{aligned} L_i &= L_{i-1} + (H_{i-1} - L_{i-1}) \cdot F_x(i-1) \\ &= L_{i-1} + r_{i-1} \cdot F_x(i-1) \end{aligned}$$

kann man die Gleichungen (2.6) und (2.7) etwas anders schreiben. Wir rechnen  $H$  nicht mehr explizit aus, sondern nur noch  $L$  und die dazugehörige Länge des Teilintervalls  $r_i$ .

$$\begin{aligned} L_i &= L_{i-1} + r_{i-1} \cdot F_x(i-1) \\ r_i &= r_{i-1} \cdot p(x_i) \end{aligned}$$

### 3.1.2 Prinzip

Wir nehmen zur Vereinfachung an, dass die Sequenz aus einer geraden Anzahl von Symbolen besteht  $|S| = 2n$ . Eine ungerade Länge kann man leicht auf eine gerade erweitern.

Um den Algorithmus zu parallelisieren, verfolgen wir, die Ergebnisse der Berechnungen, wenn man diese ausschreibt.

$$\begin{aligned}

r_1 &= r_0 \cdot p(x_0) \\

r_2 &= r_1 \cdot p(x_1) = (r_0 \cdot p(x_0)) \cdot p(x_1) \\

r_3 &= r_2 \cdot p(x_2) = ((r_0 \cdot p(x_0)) \cdot p(x_1)) \cdot p(x_2) \\

r_4 &= r_3 \cdot p(x_3) = (((r_0 \cdot p(x_0)) \cdot p(x_1)) \cdot p(x_2)) \cdot p(x_3) \\

&\vdots \\

r_{2n} &= r_0 \cdot p(x_0) \cdot p(x_1) \cdot p(x_2) \cdot p(x_3) \dots p(x_{2n-1})

\end{aligned} \tag{3.2}$$

Und für  $L$

$$\begin{aligned}

L_1 &= L_0 + r_0 \cdot F_x(0) \\

L_2 &= L_1 + r_1 \cdot F_x(1) \\

&= (L_0 + r_0 \cdot F_x(0)) + r_1 \cdot F_x(1) \\

&= (L_0 + r_0 \cdot F_x(0)) + r_0 \cdot p(x_0) \cdot F_x(1) \\

&= L_0 + r_0 \cdot F_x(0) + r_0 \cdot p(x_0) \cdot F_x(1) \\

L_3 &= L_2 + r_2 \cdot F_x(2) \\

&= (L_0 + r_0 \cdot F_x(0) + r_0 \cdot p(x_0) \cdot F_x(1)) + r_2 \cdot F_x(2) \\

&= (L_0 + r_0 \cdot F_x(0) + r_0 \cdot p(x_0) \cdot F_x(1)) + (r_0 \cdot p(x_0)) \cdot p(x_1) \cdot F_x(2) \\

&= L_0 + r_0 \cdot F_x(0) + r_0 \cdot p(x_0) \cdot F_x(1) + r_0 \cdot p(x_0) \cdot p(x_1) \cdot F_x(2) \\

&\vdots \\

L_{2n} &= L_0 + r_0 \cdot F_x(0) + r_0 \cdot p(x_0) \cdot F_x(1) + r_0 \cdot p(x_0) \cdot p(x_1) \cdot F_x(2) + \\

&\quad \dots + r_0 \cdot p(x_0) \cdot p(x_1) \dots p(x_{2n-2}) \cdot F_x(2n-1)

\end{aligned} \tag{3.3}$$

Wir teilen jetzt die Berechnungen (3.2) und (3.3) in zwei gleich große Abschnitte und erhalten

$$\begin{aligned}

r_{1..n} &= r_0 \cdot p(x_0) \cdot p(x_1) \cdot p(x_2) \cdot p(x_3) \dots p(x_{n-1}) \\

L_{1..n} &= L_0 + r_0 \cdot F_x(0) + r_0 \cdot p(x_0) \cdot F_x(1) + r_0 \cdot p(x_0) \cdot p(x_1) \cdot F_x(2) + \\

&\quad \dots + r_0 \cdot p(x_0) \cdot p(x_1) \dots p(x_{n-1}) \cdot F_x(n-1)

\end{aligned}$$

und

$$\begin{aligned}

r_{(n+1)..2n} &= r_0 \cdot p(x_{n+1}) \cdot p(x_{n+2}) \cdot p(x_{n+3}) \cdot p(x_{n+4}) \dots p(x_{2n-1}) \\

L_{(n+1)..2n} &= L_0 + r_0 \cdot F_x(n+1) + \\

&\quad r_0 \cdot p(x_{n+1}) \cdot F_x(n+2) + \\

&\quad r_0 \cdot p(x_{n+1}) \cdot p(x_{n+2}) \cdot F_x(n+3) + \dots \\

&\quad + r_0 \cdot p(x_{n+1}) \cdot p(x_{n+2}) \dots p(x_{2n-2}) \cdot F_x(2n-1)

\end{aligned}$$

### 3 Parallelisierung

---

Somit ist  $r_{2n}$  nichts anderes als

$$r_{2n} = \frac{r_{1..n} \cdot r_{(n+1)..2n}}{r_0} \quad (3.4)$$

Wir schreiben  $L_{2n}$  nochmal komplett aus und fügen zusammen

$$\begin{aligned} L_{2n} &= L_0 + r_0 \cdot F_x(0) + r_0 \cdot p(x_0) \cdot F_x(1) + r_0 \cdot p(x_0) \cdot p(x_1) \cdot F_x(2) + \dots \\ &\quad + r_0 \cdot p(x_0) \cdot p(x_1) \dots p(x_{n-1}) \cdot F_x(n) + \dots \\ &\quad + r_0 \cdot p(x_0) \cdot p(x_1) \dots p(x_n) \cdot F_x(n+1) + \dots \\ &\quad + r_0 \cdot p(x_0) \cdot p(x_1) \dots p(x_{2n-2}) \cdot F_x(2n-1) \\ &= L_{1..n} + r_{1..n} \cdot \\ &\quad (F_x(n+1) + \dots + r_0 \cdot p(x_0) \cdot p(x_1) \dots p(x_{2n-2}) \cdot F_x(2n-1)) \end{aligned}$$

Wir erweitern die abgesetzte Zeile mit  $r_0$

$$L_{2n} = L_{1..n} + r_{1..n} \left( \frac{r_0 \cdot [F_x(n+1) + \dots + r_0 \cdot p(x_0) \cdot p(x_1) \dots p(x_{2n-2}) \cdot F_x(2n-1)]}{r_0} \right)$$

und erweitern noch mit  $L_0$

$$L_{2n} = L_{1..n} + r_{1..n} \left( \frac{L_0 + [r_0 \cdot F_x(n+1) + \dots + r_0 \cdot p(x_0) \cdot p(x_1) \dots p(x_{2n-2}) \cdot F_x(2n-1)] - L_0}{r_0} \right)$$

und erhalten

$$\begin{aligned} L_{2n} &= L_{1..n} + r_{1..n} \left( \frac{L_{(n+1)..2n} - L_0}{r_0} \right) \\ &= L_{1..n} + \frac{r_{1..n} (L_{(n+1)..2n} - L_0)}{r_0} \end{aligned} \quad (3.5)$$

Die Differenzengleichungen (3.5) und (3.4) ergeben die neue Rechenvorschrift für das Kodieren. Setzen wir  $L_0 = 0$ , erhalten wir

$$L_{2n} = L_{1..n} + \frac{r_{1..n} \cdot L_{(n+1)..2n}}{r_0} \quad (3.6)$$

$$r_{2n} = \frac{r_{1..n} \cdot r_{(n+1)..2n}}{r_0} \quad (3.7)$$

Wir können Gleichung (3.2) und (3.3) immer weiter nach dieser Regel aufteilen, bis zum Schluss nur noch ein Symbol kodiert werden muss. Die Formel für diese Kodierung ist dann

$$\begin{aligned} L_1 &= L_0 + r_0 \cdot F_x(0) \\ r_1 &= r_0 \cdot p(x_0) \end{aligned}$$

Weil  $L_0 = 0$  gilt

$$L_1 = r_0 \cdot F_x(0) \quad (3.8)$$

$$r_1 = r_0 \cdot p(x_0) \quad (3.9)$$

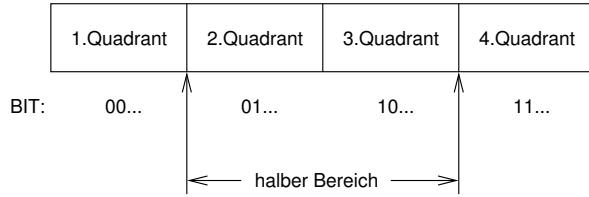

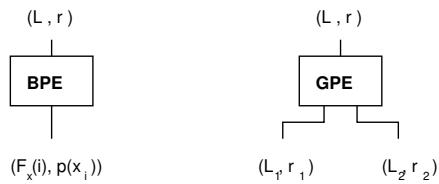

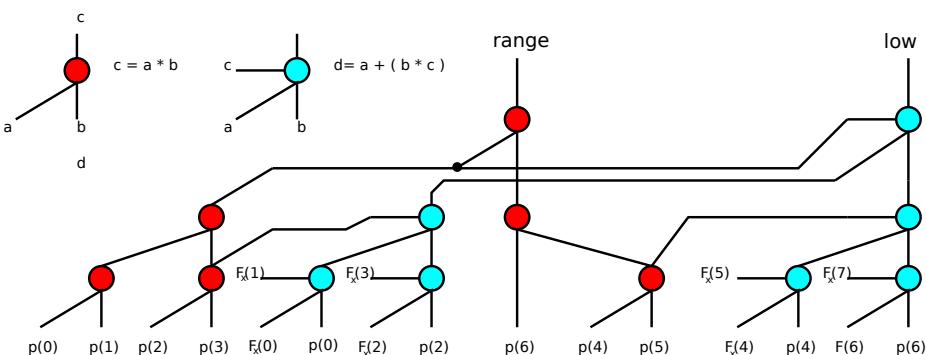

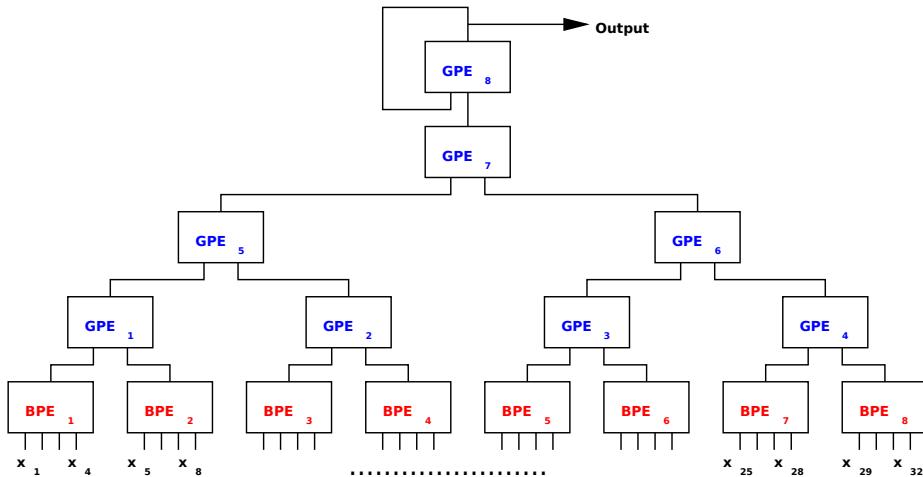

Wir können also zwei verschiedene Rechenvorschriften definieren. Eine zum Berechnen von  $L$  und  $r$ , und eine um zwei  $Ls$  und  $rs$  zusammenzufügen. In diesem Paper sprechen die Autoren von einer BPE und einer GPE. Die BPEs berechnen ein  $L_{x_i}$  und  $r_{x_i}$  zum Symbol  $x_i$  und die GPE konkateniert die Berechnungen zu den Symbolen  $x_i$  und  $x_{i+1}$ . Das Ergebnis dieser Zusammenführung wird mit der nächsten Berechnung in einer weiteren Stufe zusammengefügt. Auf diese Weise kann man beliebig viele Symbole durch BPEs einlesen und in

**Abbildung 3.1:** Basisformeln für Parallelisierung

einer baumartigen Struktur von GPEs zusammenfügen. Abbildung 3.2 zeigt ein Beispiel mit 8 Symbolen. In der obersten GPE erhält man dann das neue  $L$  und  $r$ . Es stellt sich nun die

**Abbildung 3.2:** Berechnungs-Baum für 8 Symbole

Frage, wie die Berechnung fortgeführt werden kann. Eine Möglichkeit wäre, so viele BPEs und GPEs zur Verfügung zu stellen, wie es Symbole gibt. Dann wäre die Länge des Textes begrenzt und außerdem würde die dafür benötigte Präzision zu groß werden, wie wir später erfahren werden.

Ein anderer Ansatz ist, für die Berechnungen die Differenzengleichungen (3.4) und (3.5) statt (3.6) und (3.7) für die GPEs zu nehmen. Dann setzt man für  $L_0$  das zuvor errechnete  $L$  ein und erhält bei GPE7 das neue  $L$  und  $r$ , welches dann für den nächsten Schritt verwendet wird. So kann man immer 8 Symbole gleichzeitig einlesen und den Vorgang durch eine parallele Implementierung der Bausteine in

$$m = (\log_b k) + 1$$

### 3 Parallelisierung

---

Schritten berechnen. Dabei ist  $k$  die Anzahl der gleichzeitig eingelesenen Symbole. In unserem Beispiel ist  $k = 8$  und damit  $m = 4$ .

Eine weitere Möglichkeit ist, die vorhergehende Berechnung und die aktuelle aus der höchsten BPE mit einer weiteren GPE zu konkatenieren. Wir würden also für die GPEs weiterhin die Differenzengleichungen (3.6) und (3.7) verwenden, aber nach der höchsten GPE eine weitere Stufe anbringen, die das vorangehende  $L$  und  $r$  mit dem der höchsten GPE zusammenfügt. Das ist nichts anderes als das vorhergehende Ergebnis in einem weiteren Durchlauf in einer nächsten GPE wieder einzufügen. Bild 3.3 zeigt das in unserem Beispiel.

Für den ersten Durchlauf muss dann für diese — nun höchste GPE —  $L = 0$  und  $r = \text{max\_val}$  gesetzt werden. In unserem Beispiel GPE8. Die Berechnung von  $L$  und  $r$  stünden somit nach

**Abbildung 3.3:** Berechnungs-Baum für 8 Symbole + Konkatenation

$$m = (\log_b k) + 2$$

Schritten fest.

#### 3.1.3 Normalisierung

Nachdem nun die Berechnung schrittweise parallel durchgeführt werden kann, stellt sich die Frage nach der erforderlichen Präzision. Im sequenziellen Fall wurde nach jedem Berechnungsschritt die Normalisierung durchgeführt. Durch diese Maßnahme wurde effektiv ein Über- und Unterlauf verhindert.

J. Jiang und S. Jones schlagen dieses auch in ihrem Paper vor. Hiernach soll bei jeder GPE eine lokale Skalierung stattfinden. Die auf der linken Seite anliegenden Werte bei einer GPE entsprechen dem alten  $L$  und  $r$ . Von der rechten Seite wird mit  $L_2$  und  $r_2$  die Berechnung fortgeführt. Das heißt, dass für die Werte an der rechten Seite die volle Präzision vorhanden sein muss. Die Autoren schlagen hierfür einen Puffer vor, der mitgeführt wird und die Bits puffert, die bei einer Skalierung herausgeschoben werden. Dieser Puffer wird der darüber liegenden GPE weitergegeben und für die Berechnung von  $L$  und  $r$  herangezogen. Somit muss an der obersten GPE alle herausgeschobenen Bits berücksichtigt werden. Man hat hier

also innerhalb der Baumstruktur — oder des parallelen Blocks — keine reale Skalierung durchgeführt.

Wir könnten also, anstatt nach jedem Schritt zu skalieren, die Berechnungen bis zur obersten GPE durchrechnen und erst dann skalieren. Bei genügender Präzision ist es egal, wann man skaliert, solange Koder und Dekoder nach der gleichen Rechenregel vorgehen. Es ist klar, dass eine höhere Präzision erforderlich sein wird, wenn man länger rechnet bis man skaliert.

Diese Erkenntnis ermöglicht somit eine vollständige Berechnung des parallelen Blocks und im Anschluss die Normalisierung. Wir müssen hierfür lediglich die Präzision erhöhen und können somit, ohne nach jedem Schritt auf die Normalisierung zu warten und ohne zusätzliche Maßnahmen, zu Ende rechnen. Um wieviel die Präzision erhöht werden muss, ist Gegenstand von Kapitel 3.4.2.