Institut für Parallelle und Verteilte Systeme

Universität Stuttgart

Universitätsstraße 38

D-70569 Stuttgart

Studienarbeit Nr. 2320

## **PCIe Treiber für ein Linux-System**

Alexander Henning

**Studiengang:** Elektrotechnik und Informationstechnik

**Prüfer:** Prof. Dr. Sven Simon

Prof. Dr. P. Levi

**Betreuer:** Dipl.-Ing. Jürgen Hillebrand

**begonnen am:** 05. Oktober 2010

**beendet am:** 06. April 2011

**CR-Klassifikation:** B.4.1, B.4.3, D.4.0, D.4.9

# PCIe Treiber für ein Linux-System

Author: Alexander Henning

Supervisor: Dipl.-Ing. Jürgen Hillebrand

Abteilung Parallele Systeme

Institut für Parallele und Verteilte Systeme

Universität Stuttgart

# Inhaltsverzeichnis

|                                                  |           |

|--------------------------------------------------|-----------|

| <b>1 Einführung</b>                              | <b>1</b>  |

| <b>2 Aufbau von Linux</b>                        | <b>5</b>  |

| 2.1 Geschichte . . . . .                         | 5         |

| 2.2 Kernel . . . . .                             | 7         |

| 2.2.1 Mikrokern . . . . .                        | 8         |

| 2.2.2 Hybridkern . . . . .                       | 9         |

| 2.2.3 Monolithischer Kern . . . . .              | 10        |

| 2.3 Linux-Kern . . . . .                         | 11        |

| 2.3.1 Interface für die System-Aufrufe . . . . . | 12        |

| 2.3.2 Prozessverwaltung . . . . .                | 12        |

| 2.3.3 Speicherverwaltung . . . . .               | 15        |

| 2.3.4 I/O-Subsystem . . . . .                    | 16        |

| 2.3.5 Geräte-Treiber . . . . .                   | 17        |

| <b>3 PCIe - Schnittstelle</b>                    | <b>21</b> |

| 3.1 Einführung . . . . .                         | 21        |

| 3.2 PCIe . . . . .                               | 23        |

| 3.3 PCIe Transaktionen . . . . .                 | 25        |

| 3.3.1 Memory Transactions . . . . .              | 25        |

| 3.3.2 I/O Transactions . . . . .                 | 25        |

| 3.3.3 Configuration Transactions . . . . .       | 26        |

| 3.3.4 Message Transactions . . . . .             | 26        |

| 3.4 PCIe Übertragungsschichten . . . . .         | 26        |

| 3.4.1 PCIe Transaktionsschicht . . . . .         | 28        |

| 3.4.2 PCIe Data Link Schicht . . . . .           | 29        |

| 3.4.3 PCIe Bitübertragungsschicht . . . . .      | 32        |

| <b>4 Treiber und Anwendung</b>                   | <b>37</b> |

| 4.1 Registerbeschreibung . . . . .               | 38        |

| 4.2 Treiber . . . . .                            | 39        |

| 4.2.1 Funktion <code>probe</code> . . . . .      | 42        |

| 4.2.2 Funktion <code>remove</code> . . . . .     | 46        |

| 4.2.3 Funktion <code>open</code> . . . . .       | 46        |

| 4.2.4 Funktion <code>release</code> . . . . .    | 47        |

| 4.2.5 Funktion <code>mmap</code> . . . . .       | 47        |

| 4.2.6 Funktion <code>read</code> . . . . .       | 48        |

|                              |                                             |           |

|------------------------------|---------------------------------------------|-----------|

| 4.2.7                        | Funktion <code>write</code>                 | 49        |

| 4.2.8                        | Funktion <code>ioctl</code>                 | 49        |

| 4.2.9                        | Funktion <code>ML_do_full_duplex_dma</code> | 53        |

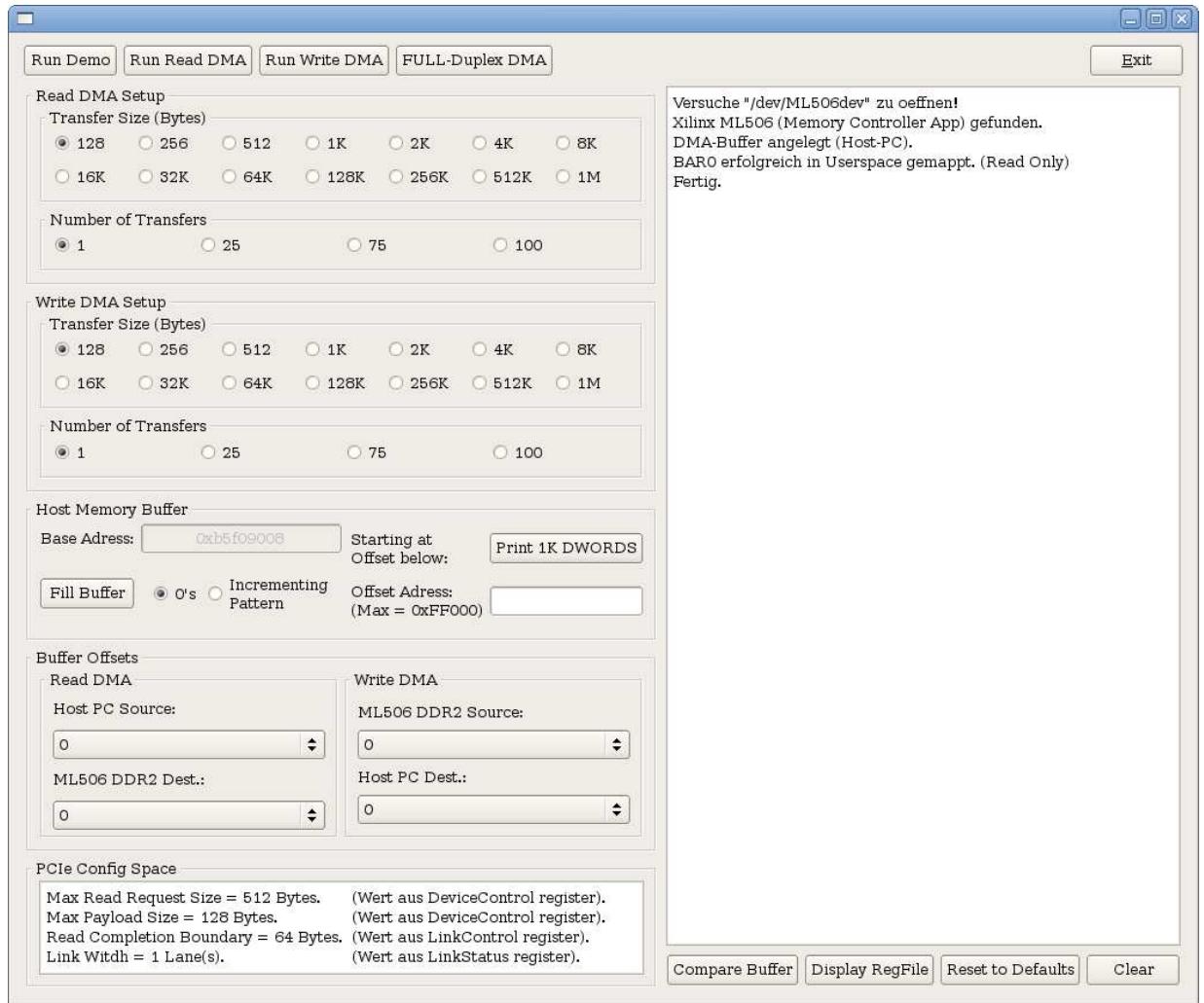

| 4.3                          | Anwendung, grafische Benutzeroberfläche     | 53        |

| 4.3.1                        | Aufbau des Programms                        | 54        |

| 4.3.2                        | Bestimmung des Datendurchsatzes             | 57        |

| <b>5</b>                     | <b>Zusammenfassung und Ausblick</b>         | <b>59</b> |

| 5.1                          | Zusammenfassung                             | 59        |

| 5.2                          | Ausblick                                    | 59        |

| <b>Literaturverzeichnis</b>  |                                             | <b>61</b> |

| <b>Abbildungsverzeichnis</b> |                                             | <b>62</b> |

| <b>Tabellenverzeichnis</b>   |                                             | <b>64</b> |

| <b>Akronyme</b>              |                                             | <b>67</b> |

# Kurzfassung

Am Institut für Parallele und Verteilte Systeme - Abteilung Parallele Systeme wird in mehreren Projekten ein Prototyp zur parallelen Berechnung elektrischer Feldgrößen mit Hilfe der Finite-Differenzen-Methode im Zeitbereich erstellt. Die zur Berechnung benötigten Algorithmen werden dazu in anderen Teilprojekten für die FPGA-Entwicklungsplattform in VHDL entwickelt. Um die zur Berechnung erforderliche große Menge an Daten und Ergebnisse möglichst schnell und effizient zwischen der FPGA-Entwicklungsplattform und dem PC austauschen zu können, soll dazu die PCIe-Schnittstelle verwendet werden.

Im Rahmen dieser Arbeit wurde ein Linux Treiber für eine Virtex 5 FPGA-Entwicklungsplattform mit PCIe-Schnittstelle und eine Anwendung implementiert. Der Treiber soll die Steuerung, die Konfiguration und den Datenaustausch zwischen der FPGA-Entwicklungsplattform und dem PC über die PCIe-Schnittstelle ermöglichen. Da das System eine schnelle Übertragung großer Datenmengen zwischen PC und FPGA-Entwicklungsplattform erfordert, soll weiterhin der Datenaustausch mittels Speicherdirektzugriff (DMA) realisiert werden. Die zu implementierende Anwendung soll zudem die Datenübertragung und Verifikation des Treibers und der Vermessung der erzielten Übertragungsbandbreiten ermöglichen.

# 1 Einführung

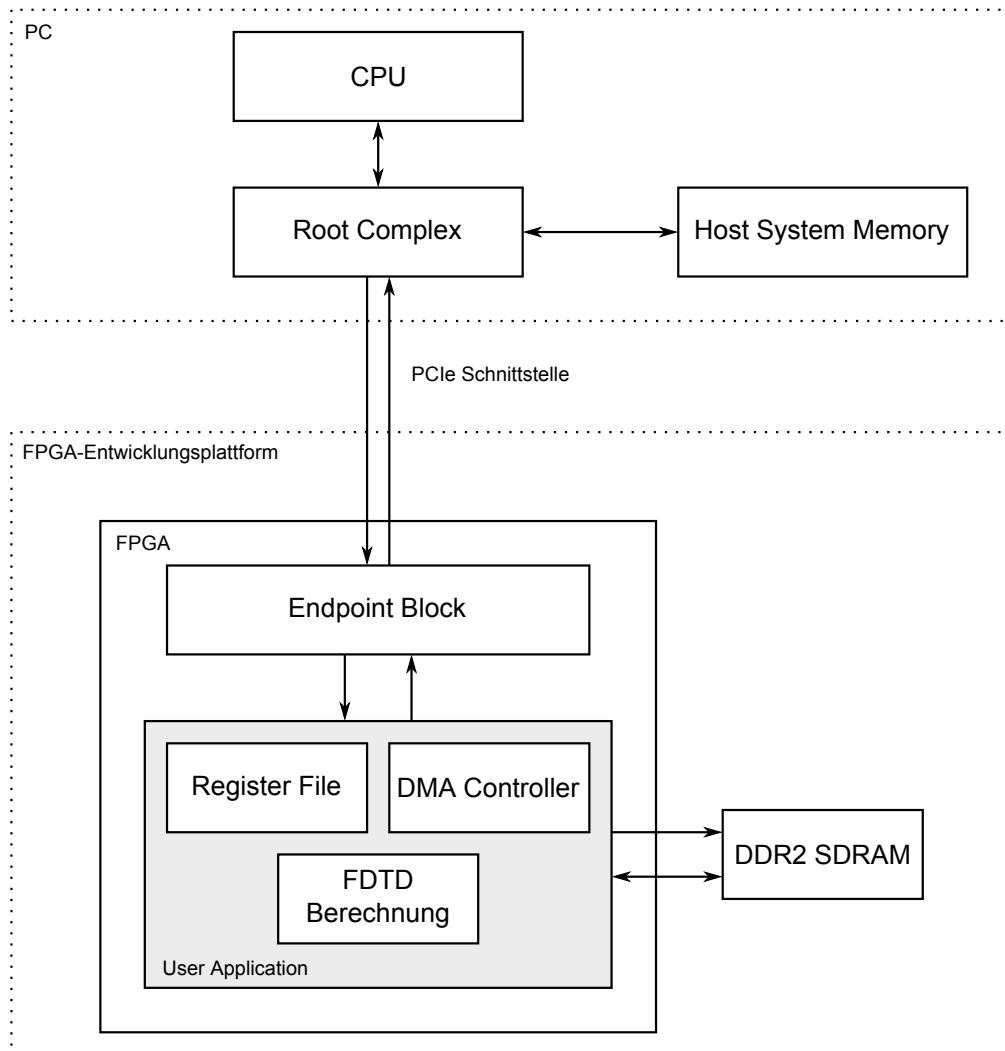

In dieser Studienarbeit soll ein Linux Treiber für die FPGA-Entwicklungsplattform ML506 der Firma Xilinx mit einem Virtex-5 FPGA zwecks Datenaustausch über die PCIe (Peripheral Component Interconnect Express)-Schnittstelle [7] mit dem PC (Personal Computer) entwickelt werden. Das gegebene System, für das der Treiber entwickelt werden soll, zeigt die Abbildung 1.1. Aus der Abbildung kann entnommen werden, dass

Abbildung 1.1: Blockdiagramm des Systems

die FPGA-Entwicklungsplattform mit dem PC über die PCIe-Schnittstelle verbunden ist. Der Datenaustausch erfolgt dabei unmittelbar zwischen dem Root Complex des PCs und dem Endpointblock [8] des FPGAs über einen x1 Link. Am Endpointblock sind zwei weitere logische Blöcke angeschlossen, der Register-File-Block und der DMA Controller Block, die gemäß der Anwendungsbeschreibung XAPP859 [9] implementiert sind. Der Register-File-Block dient der Einstellung des DMA (Speicherdirektzugriff, engl. Direct Memory Access) Controllers, der die Datenübertragung mittels Speicherdirektzugriffs [4, S. 440ff.] zwischen dem DDR2 Speicher und dem Host System Memory durchführt. Der in der Abbildung vorhandene FDTD [1] -Berechnungsblock wird im Rahmen eines anderen Projektes implementiert, weshalb in dieser Arbeit nicht näher auf diesen Block eingegangen wird. Die Durchführung der parallelen Berechnungen durch den FDTD-Berechnungsblock setzt einen breitbandigen Übertragungsweg zwischen dem PC und FPGA-Entwicklungsplattform voraus, da dabei große Mengen von Modell- und Ergebnisdaten ausgetauscht werden müssen.

Die große Menge an Daten erfordert eine besonders effektive Methode der Datenübertragung, weshalb in dieser Arbeit die Methode eines Speicherdirektzugriffs verwendet wird. Der Vorteil der Verwendung des Speicherdirektzugriffes liegt in der bestmöglichen Ausnutzung der Übertragungsbandbreite der PCIe-Schnittstelle, da die Daten nicht von der CPU (Central Processing Unit) übertragen werden müssen.

Der in dieser Studienarbeit implementierte Treiber soll weiterhin die

- Allokation und Initialisierung von Speicherbereichen im Kernel,

- Einstellung der Datenübertragung,

- Einbindung des Treibers in den Kernel des Betriebssystems zur Laufzeit,

- Kontrolle der Datenübertragung ermöglichen und

- eine definierte Schnittstelle für die Benutzeranwendungen auf dem PC bieten.

Zusätzlich zu den bereits aufgelisteten Anforderungen soll der Treiber den Anwendungen alle Funktionalitäten der Hardware zur Verfügung stellen und dabei sparsam mit den Systemressourcen umgehen.

Die erstellte Benutzeranwendung für den PC soll dem Benutzer die Steuerung und die Kontrolle der Datenübertragung ermöglichen. Dabei greift sie auf alle Funktionen des Treibers und damit auch auf alle bereits implementierten Funktionen der Hardware zurück, wodurch die Funktionalität der Hardware und des Treibers demonstriert werden kann. Eine weitere Anforderung an die Anwendung ist, dass sie die Übertragungsbandbreite zur Überprüfung der Effizienz des Treibers messen kann.

Die fünf Kapitel umfassende Arbeit gibt eine ausführliche Beschreibung über die erfolgte Implementierung des Treibers an. Im nachfolgenden Kapitel 2 werden zunächst wichtige Details des Linux Betriebssystems erläutert, die zur Implementierung des Treibers beachtet werden müssen. Zusätzlich erfolgt auch ein kurzer geschichtlicher Exkurs in das Linux Betriebssystem. Das Kapitel 3 beschreibt die PCIe-Schnittstelle. Im Kapitel 4 wird der entwickelte Treiber beschrieben und die Benutzeranwendung vorgestellt.

Abschließend werden im Kapitel 5 die Ergebnisse von Durchsatzmessungen vorgestellt, sowie eine Zusammenfassung und ein Ausblick gegeben.

## 2 Aufbau von Linux

### 2.1 Geschichte

Mit dem Begriff Linux sind meistens Mehrbenutzer-Betriebssysteme gemeint, die auf dem Linux-Kernel basieren. Dieser Begriff bezeichnet aber nur die Kernkomponente des Betriebssystems, den sog. „Kernel“. Zu dem Linux-Betriebssystem gehören neben dem Kernel selbst noch die System- und Anwendersoftware. Diese zusätzliche Software, vereint mit dem Kernel und der entsprechenden Installationsroutine, wird zu einer sogenannten Distribution zusammengefasst. Zumindest bei einigen kommerziellen Distributionen gehören die Handbücher und andere Dokumentation zum Lieferumfang. Zu den bekanntesten Distributionen zählen unter anderen Debian, mit seinen Abkömlingen Knoppix und Ubuntu, Red Hat, Fedora, OpenSUSE, Mandriva und Gentoo.

Linux ist ein Unix-ähnliches Betriebssystem. Im Gegensatz zu den proprietären Unix-Systemen ist der vollständige Quellcode verfügbar und darf frei verändert und kopiert werden. Die Unix-Entwicklung startete 1965 und wurde von MIT, BELL und General Electric vorangetrieben. Das neue Betriebssystem war für ein Einsatz an damaligem Grossrechner MULTICS vorgesehen. Die ursprünglichen Unix-Programme wurden alle in Assembler geschrieben. Im Laufe der Zeit spalteten sich mehrere Gruppen ab und verfolgten eigene Ziele, meistens bedingt durch den Wechsel auf andere Zielplattformen. Die Programmierung in Assembler war sehr aufwendig und somit wurden eigens für die Entwicklung des Betriebssystems neue Programmiersprachen entwickelt. Die erste neue Programmiersprache war „B“, die stark durch die BCPL (Basic Combined Programming Language) beeinflusst wurde. Der Plattformwechsel im Jahre 1971 erforderte eine neue, diesmal eine byteorientierte Programmiersprache. Dennis Ritchie entwickelte die „C“-Programmiersprache. Diese Sprache zeichnet sich durch die Systemnähe aus und sie wird auch noch heute verwendet.

Das Jahr 1973 markiert die Geburt eines Multiuser-Multitasking-Betriebssystems, das vollständig in C geschrieben wurde. Im weiteren Verlauf wurde Unix weiterentwickelt und wegen der großen Anzahl von unterschiedlichen Entwicklerfirmen auf unterschiedliche Plattformen portiert. Durch die Vergabe von Quellcode-Lizenzen an Universitäten konnte zudem das Unix-Derivat BSD (Berkeley Software Distribution) entwickelt werden. BSD zeichnet sich durch die Implementierung und Integration des TCP/IP Stacks und der Berkeley Socket API (Application Programming Interface) aus. Dadurch wurden Standards geschaffen und umgesetzt, die bis heute ihre Gültigkeit besitzen und angewendet werden.

Die Entstehungsgeschichte des Linux Betriebssystemkerns ist eng mit dem Namen Linus Torvalds verbunden. Im Frühjahr 1991 begann er mit der Entwicklung seines eigenen

Betriebssystems. Er veröffentlichte seine erste Entwicklerversion am 17.09.1991 und lud interessierte Entwickler zur Mitarbeit ein. Zuerst wollte Linus Torvalds die kommerzielle Benutzung verbieten, aber erst die Lizenzierung des Linux-Kernels unter der GNU (GNU's Not Unix) GPL (General Public License) ermöglichte weite Verbreitung, auch im kommerziellen Bereich.

Die GNU General Public License wurde 1982 von Richard Stallman erarbeitet. Ebenfalls in diesem Jahr gründete er ein GNU-Projekt mit dem Ziel ein komplett freies Betriebssystem zu entwickeln. Dadurch wollte er der Weitergabe der Software in binärer Form entgegenwirken. Sein Projekt ergab eine große Fülle an Programmen, die für ein komplettes Betriebssystem notwendig sind. Die Entwicklung des dazugehörigen Betriebssystemkerns, des Kernel war aber noch nicht ausreichend voran geschritten. Das Betriebssystem basiert heute auf dem Linux-Kernel. Die Linux-Systeme wiederum benutzen für die wichtigsten Systemkomponenten und die Userspace-Software die GNU lizenzierte Programme.

Mit der 1998 erschienenen Kernel-Version 2.2 unterstützte das Betriebssystem mehrere Prozessoren. Mit den neuen Versionen 2.4 und 2.6 wurden immer mehr neue Features eingebaut.

- Unterstützung großer Arbeitsspeicher (bis zu 64 GByte)

- Unterstützung für Plug-and-Play-Geräte

- SATA-Unterstützung

- Bluetooth-Unterstützung

- Zahlreiche neue Dateisysteme (ReiserFS, Ext4, JFS)

- bessere Scheduler

Nachteilig ist, dass mit den größeren Versionssprüngen die Schnittstellen des Kernels sich zum Teil erheblich verändern. Viele Treiber müssen daraufhin angepasst werden und manchmal ist es sogar einfacher sie stattdessen neu zu entwickeln.

Auch noch heute leitet und überwacht Linus Torvalds die Entwicklung des Kernels. Die gemachten Veränderungen, meistens Verbesserungen, am Kernel werden an die verantwortlichen Kernel-Entwickler weitergereicht. Die hochqualitativen Anpassungen und von solchen nur die, die Linus Torvalds zusagen, werden dann von ihm in den offiziellen Kernel übernommen.

Für jeden Einsatzbereich gibt es entsprechende Linux-Varianten. Die Palette reicht von Desktop PC über die Mobiltelefone und Router bis hin zu den Supercomputern. Die Verbreitung in den einzelnen Einsatzbereichen ist jedoch unterschiedlich. Die Linux-Systeme im Servereinsatz sind weit verbreitet, in Heimanwender-Bereich spielen sie nur eine geringe Rolle. Der gute Ruf, kostenfreie Verfügbarkeit und immer einfachere Handhabung tragen dazu bei, dass dieser Heimanwender-Bereich stetig wächst.

Auf dem freien Betriebssystem setzen weitere Großprojekte an, wie z.B. KDE, Gnome und X-Server von X.Org-Projekt. Diese Projekte haben erheblich dazu beigetragen, dass dieses Betriebssystem für die Benutzer einfacher und zugänglicher wurde.

## 2.2 Kernel

Der Kernel oder Systemkern ist ein zentraler Bestandteil des Betriebssystems und ist die unterste Softwareschicht. Der Kernel bildet die hardwareabstrahierende Schicht zwischen der Hardware und übrigen Softwarekomponenten. Da die Hardwarebasis sehr unterschiedlich sein kann, muss der Kernel alle Variationen abdecken. Da dies nicht möglich bzw. sinnvoll ist, muss der Kernel über Mechanismen verfügen, die eine Einbindung externer Module erlaubt. Der Systemkern bietet definierte Schnittstellen sowohl für die Treiber als auch für die Software des Benutzers, die unabhängig von der Rechnerarchitektur ist. Die grundlegenden Aufgaben des Kernels sind:

- Kontrolle über die vorhandenen Ressourcen wie CPU, Speicher, Geräte.

- Zuteilung der Ressourcen an die Anwenderprogrammen, z.B. die Rechenzeit.

- Bereitstellung einer Softwareschnittstelle für die Anwenderprogramme.

- Hierarchische Strukturierung der Ressourcen, z.B. Dateisysteme, Netzwerkprotokolle.

- Arbitrierung von Zugriffskonflikten und Bereitstellung von Warteschlangen bei knappen Ressourcen.

- Überwachung von Zugriffsrechten auf Dateien und Geräte bei Mehrbenutzersystemen.

- Speicher- und Prozessverwaltung.

- Virtualisierung: Verbergen der Komplexität der Maschine vor dem Anwender.

Der Kernel selber ist in Schichten aufgebaut. Das Schichtenmodell sieht vor, dass es eine unterste Schicht gibt, hier z.B. die Hardwareabstraktionsschicht. Die höher liegenden Schichten bauen auf den Funktionalitäten der jeweils unter ihnen liegenden Schichten auf. Die Unterteilung in Schichten erfolgt z.B. nach den Funktionalitäten oder Aufgaben.

Nach dem Umfang der im Kernel enthaltenen Schichten unterscheidet man zwischen drei verschiedenen Kerneltypen:

1. Monolithischer Kernel, alle Funktionen sind in dem Systemkern implementiert.

2. Mikrokern, nur die grundlegenden Funktionen sind im Systemkern integriert. Die restlichen Funktionen werden in getrennten Prozessen ausgeführt.

3. Hybridkernel, ist eine Mischung von monolithischem Kernel und dem Mikrokern.

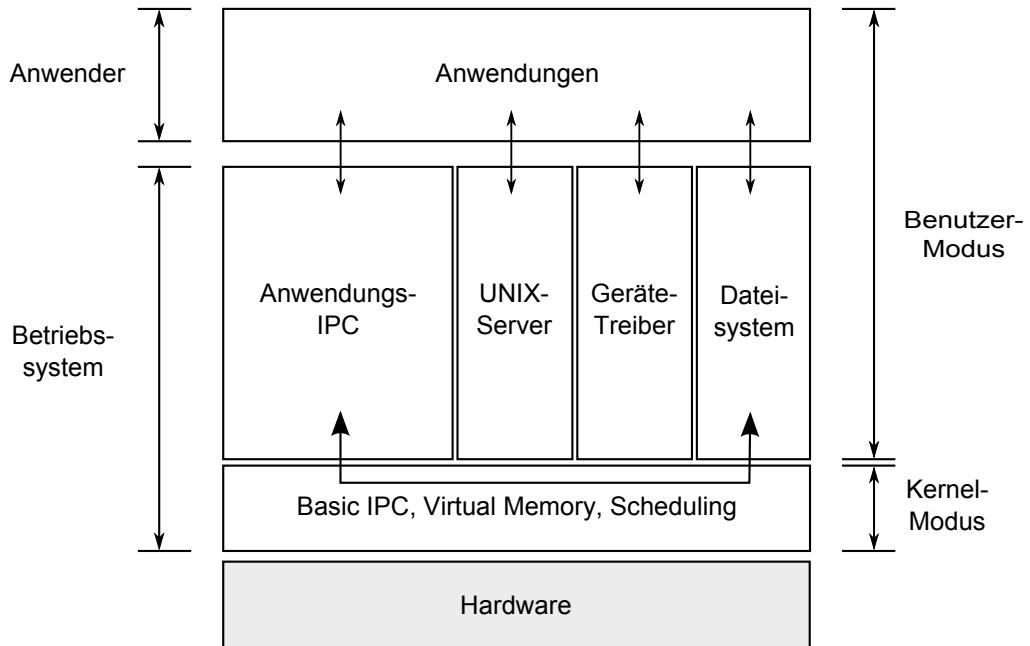

Abbildung 2.1: Mikrokernell Betriebssysteme

### 2.2.1 Mikrokernell

Bei einem Betriebssystem mit einem Mikrokernell werden nur die grundlegendsten Funktionen im Kernel implementiert. Alle anderen Teile des Betriebssystems laufen als getrennte Prozesse im Benutzer-Modus und sie stehen somit den Benutzerprogrammen zur Verfügung, oder sie werden als Programmbibliothek in die Benutzerprogramme mit eingebunden. Die Eigenschaft des Mikrokernels, die Teile des Betriebssystems auslagern zu können, begünstigt die Entwicklung von verteilten Betriebssystemen. Ein Nachteil der auf dem Mikrokernell basierten Betriebssystemen ist, dass ein Kontextwechsel öfter als bei anderen Betriebssystemen erfolgt, da die Teile des Betriebssystems als eigenständige Prozesse laufen. Die verschiedenen Teile des Betriebssystems können zur Laufzeit, z.B. wegen eines Absturzes, neu gestartet oder gänzlich ausgetauscht werden. Der Absturz einer einzelnen Komponente bedeutet nicht zwangsläufig den Absturz des ganzen Systems. Neben der schwer zu optimierenden Koordination der Kernel-Prozesse ist die Minimierung der mehrfachen Kopiervorgänge bei den Kontextwechseln eine der großen Herausforderungen beim Mikrokernell-Design.

Die Abbildung 2.1 stellt die Struktur der auf dem Mikrokernell basierten Betriebssystemen dar. Solche Systeme besitzen eine große Verbreitung in den Anwendungsbereichen mit hohen Anforderungen an die Robustheit, Sicherheit und Zuverlässigkeit, wie z.B. bei Militär, Luft- und Raumfahrt oder Automatisierungs- und Medizintechnik. Die prominentesten Vertreter der Mikrokernellsysteme sind: GNU/Hurd, L4Linux, Minix, QNX, Singularity.

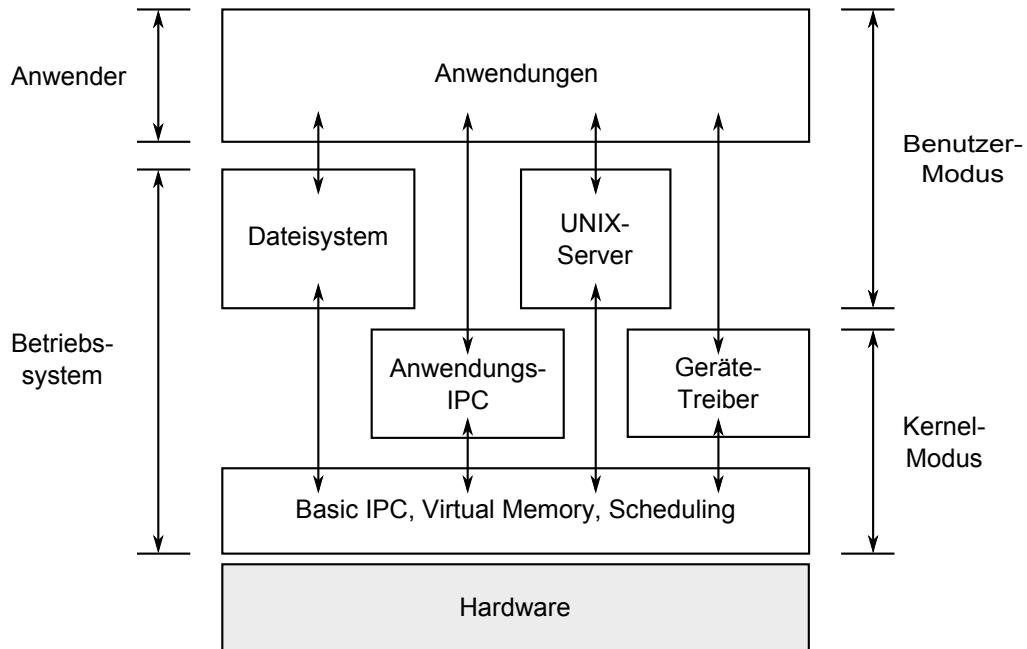

Abbildung 2.2: Hybridkernel Betriebssysteme

## 2.2.2 Hybridkernel

Ein Hybridkernel ist eine Mischung aus den Eigenschaften von Mikrokerneln und einem monolithischen Kernel. Dabei werden einige zusätzliche Teile des monolithischen Kernels in den Kern mit aufgenommen, und dadurch ist es kein Mikrokernel mehr, jedoch auch noch kein vollwertiger monolithischer Kernel. Durch die Aufnahme der ausgewählten Funktionen in den Kernel, wie z.B. Grafiktreiber, erzielt man eine Steigerung der Leistungsfähigkeit bei der Darstellung von graphischen Elementen.

Jedes Betriebssystem, dass auf dem Hybridkernel aufgebaut ist, kann unterschiedliche Teilfunktionen im Kernel implementiert haben.

Die Aufnahme zusätzlicher Betriebssystemfunktionen in den Kernel bildet einen Vorteil gegenüber dem Mikrokernell, weil dadurch die Anzahl der Kontextwechsel reduziert wird und somit die Interprozesskommunikation vereinfacht wird. Diese Maßnahmen steigern die Geschwindigkeit des Kernels. Dieser Vorteil des Hybridkernels gegenüber dem Mikrokernell bringt gleichzeitig auch einen Nachteil mit sich. Dieser Nachteil äußert sich durch die Steigerung der Fehleranfälligkeit des gesamten Systems. Diese Fehleranfälligkeit ist geringer als bei einem monolithischen Kernel. Der Hybridkernel vereint nicht nur die Vorteile der beiden anderen Kernelarten, sondern auch deren Nachteile.

Die Abbildung 2.2 stellt eine mögliche Struktur des Hybridkernels dar. Die typischen Vertreter der Betriebssysteme mit dem Hybridkernel sind: alle auf Windows NT basierten Systeme sowie BeOS, MacOS X.

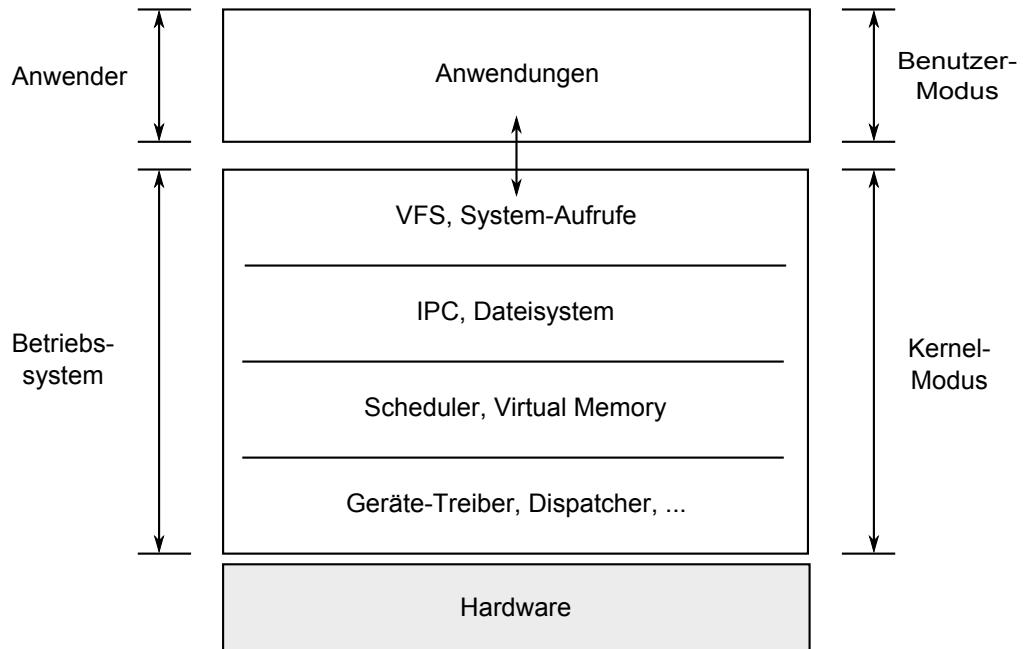

Abbildung 2.3: Betriebssysteme mit dem monolithischen Kernel

### 2.2.3 Monolithischer Kernel

Der monolithische Kernel ist die Kernelart, mit der die Entwicklung von Betriebssystemen begann. Gegenüber anderen bereits erwähnten Kernelarten, besitzt der monolithische Kernel ein einfacheres Design. In einem monolithischen Kernel sind alle Funktionen und die Treiber für die Hardwarekomponenten direkt eingebaut. Monolithische Kernel stellen mit sich einen einzelnen Prozess dar, der in einem Adressraum abläuft. Der Kernel ist somit ein statisches Programm. Die ganzen Funktionen und die Kernel-Dienste laufen alle in einem großen Kernel-Adressbereich. Die Interprozesskommunikation innerhalb des Kernels lässt sich wegen des gemeinsamen Adressraums leicht implementieren, wobei die Funktionen im Kernel direkt aufgerufen werden können. Die erforderlichen Treiber für die Hardware müssen in dem Kernel enthalten sein. Im Vergleich zu den anderen Kernelarten erzielt man hierdurch einen Geschwindigkeitsvorteil, wenn die Treiber nicht als eigenständige Programme laufen.

Dadurch, dass alle Kernel-Dienste und die Treiber für die Hardware in einem Adressbereich laufen, sind monolithische Kernel fehleranfälliger. Es besteht eine große Gefahr, dass z.B. ein abgestürzter Kernel-Dienst das gesamte System abstürzt.

Der Abbildung 2.3 kann man die Struktur des Betriebssystems entnehmen, das auf einem monolithischen Kernel aufbaut. Einige der Betriebssysteme, die auf monolithischen Kernel aufbauen, sind: MS-DOS (Microsoft Disk Operating System), Unix, BSD, OS/2.

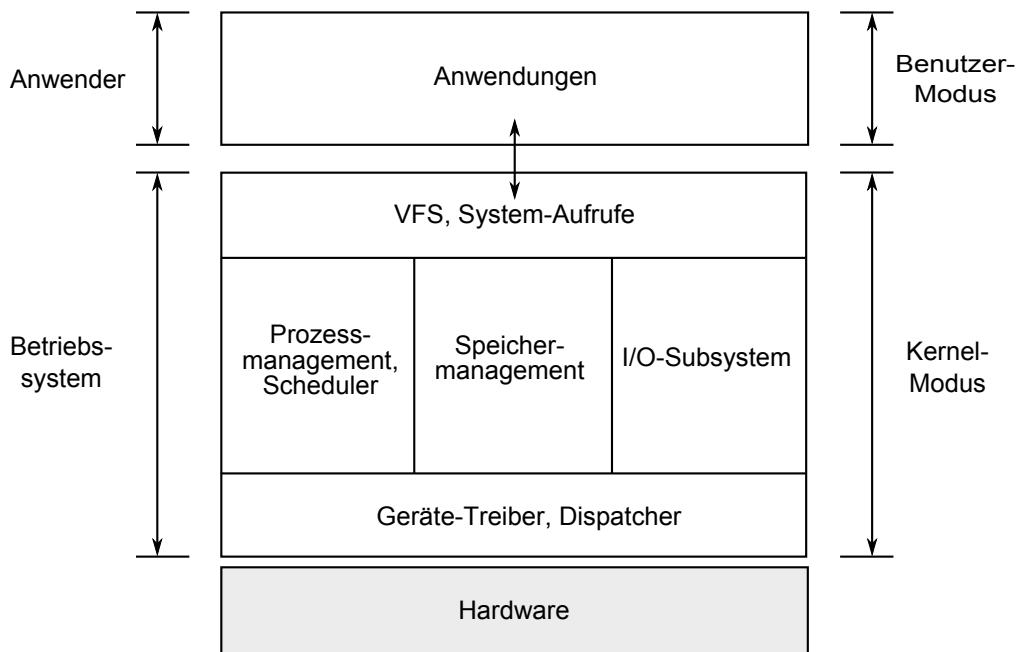

Abbildung 2.4: Linux Betriebssystem

## 2.3 Linux-Kernel

Der Linux-Kernel ist selbst ein monolithischer Betriebssystemkern. Er wird in einem Adressbereich im Kernel-Modus ausgeführt. Die Linux-Entwickler waren sich der mit dem monolithischen Kernel verbundenen Nachteilen bewusst und haben mehrere gute Ansätze des Mikrokernels umgesetzt. Der Linux-Kernel ist modular aufgebaut, unterstützt die Kernel-Threads, unterstützt präemptives Multitasking, selbst für Kernel Tasks, und bietet ein Interface mit dessen Hilfe man dynamisch zusätzliche Kernel-Module laden und entladen kann.

Die Abbildung 2.4 stellt die wesentlichen Komponenten des Betriebssystems Linux dar.

- Interface für die System-Aufrufe

- Prozessverwaltung

- Speicherverwaltung

- I/O-Subsystem

- Gerätetreiber

Diese Komponenten werden nachfolgend näher vorgestellt.

### 2.3.1 Interface für die System-Aufrufe

Alle Anwendungen, die im Benutzer-Modus ausgeführt werden und die vom Betriebssystem zur Verfügung gestellten Dienste in Anspruch nehmen, müssen das Interface für die System-Aufrufe benutzen. Diese Schnittstelle wird über die Software-Interrupts realisiert. So kann die Anwendung auf die Dateien zugreifen oder z.B. die Rechte des Benutzers prüfen. Die Anwendungen, die Software-Interrupts auslösen, müssen über die übergebenen Parameter die zur Ausführung notwendige Information bereitstellen. Nach der Auslösung eines Interrupts führt dann der Kernel die entsprechende Interrupt-Service-Routine durch und gibt der Anwendung einen Rückgabewert zurück.

Die meisten Anwendungen werden von den Entwicklern mit Hilfe von Hochsprachen programmiert. In den Anwendungen werden z.B. die Funktionen aus den Bibliotheken benutzt. In solchen Funktionen werden dann die eigentlichen Systemcalls aufgerufen. Es ist aber auch möglich, dass die Entwickler die System-Aufrufe direkt aus der Anwendung einsetzen können.

Beim Ausführen einer Anwendung muss neben dem eigentlichen Code der Anwendung noch der Code der verwendeten Bibliotheken und der Kernelcode ausgeführt werden. Der Kernelcode wird z.B. ausgeführt, wenn die eingesetzte Bibliothek System-Aufrufe tätigt. Dabei lösen die System-Aufrufe Software-Interrupts aus, die vom Kernel abgearbeitet werden müssen.

Im Linuxkernel (2.6) sind rund 300 System-Aufrufe realisiert, die man alle in der Datei `<asm/unistd.h>` der Kernel-Sources nachschlagen kann.

Listing 2.1: Ausschnitt aus `linux/arch/x86/include/asm/unistd_32.h`

```

#define __NR_restart_syscall      0

#define __NR_exit                  1

#define __NR_fork                  2

#define __NR_read                  3

#define __NR_write                 4

#define __NR_open                  5

#define __NR_close                 6

```

Der System-Aufruf mit der Nummer 1 beendet einen Rechenprozess. Mit dem System-Aufruf *fork*, dem Aufruf mit der Nummer 2, erzeugt man einen neuen Rechenprozess. System-Aufruf mit der Nummer 3 wird z.B. aufgerufen, wenn die Daten aus den Dateien oder von den Geräten gelesen werden sollen.

### 2.3.2 Prozessverwaltung

Ein weiterer Teil des Kernels ist die Prozessverwaltung. Die Prozessverwaltung trägt unter anderem dazu bei, dass mehrere Rechenprozesse quasi parallel auf einem Einprozessor-System abgearbeitet werden können. Bei Systemen mit mehreren Prozessoren werden die auszuführenden Prozesse auf diese verteilt. Für den Kernel sind die Applikationen einfache Rechenprozesse. Jeder Rechenprozess besteht aus dem Codesegment und dem Datensegment. Beim Anlegen eines neuen Prozesses belegt das Betriebssystem mindestens

tens drei Speicherblöcke: für ausführbaren Code, für Daten und zuletzt für den Stack. Die Prozessverwaltung ist in der Lage den mehrfachen Verbrauch an Speicher zu vermeiden, wenn es z.B. mehrere Prozesse gibt, die den gleichen Code-Block verwenden.

Linux ist ein Multitasking-Betriebssystem. Seit der Kernel-Version 2.6 beherrscht Linux nicht nur präemptives Multitasking sondern auch präemptibles Multitasking. Beim präemptiven Multitasking stellt das Betriebssystem jedem lauffähigen Prozess nur einen Zeitschlitz zur Abarbeitung bereit. Nach Ablauf der zugewiesenen Zeit unterbricht der Kern den laufenden Prozess und startet den nächsten lauffähigen Rechenprozess. Weil die Zeitabschnitte sehr kurz sind, entsteht der Eindruck, dass die Programme parallel ablaufen. Die Wahl des nächsten rechenbereiten Prozesses erfolgt durch einen Scheduling-Algorithmus. Der Kernel verwaltet dazu zwei Listen:

- Liste der lauffähigen Prozesse: In dieser Liste stehen alle ablauffähigen Prozesse, die bei freien Prozessoren sofort abgearbeitet werden können. Dabei besteht kein Bedarf an weiteren Ressourcen. Wenn vor dem Ablauf der zugewiesenen Laufzeit der Prozess noch nicht fertig mit den Berechnungen ist, dann wird er wieder in die Liste der lauffähigen Prozesse eingetragen. Der Scheduler wählt den nächsten Prozess aus dieser Liste.

- Liste der „schlafenden“ Prozesse: In diese Liste werden alle Prozesse eingetragen, die z.B. auf die Daten aus dem Speicher warten, oder auf die langsame Peripherie angewiesen sind, und damit nicht lauffähig sind. Wenn die von dem Prozess angeforderte Ressource irgendwann zur Verfügung steht, dann wird der entsprechende Rechenprozess aus der Liste der „schlafenden“ Prozesse in die Liste der lauffähigen Prozesse verschoben. Der verschobene Prozess wird aber unter Umständen nicht sofort ausgeführt, sondern erst dann, wenn der Scheduler ihn aussucht.

Der Scheduler und die Speicherverwaltung sind die kritischsten Teile des Kernels. Deren Entwurf und die Implementierung beeinflussen die Entwicklung anderer Teile des Betriebssystems und damit die gesamte Leistungsfähigkeit des Systems.

Der Scheduler berechnet die Prioritäten aller Prozesse auf einmal. Die Berechnung der Prioritäten und damit die neue Positionierung der Prozesse wird erst dann ausgeführt, wenn alle Prozesse auf der Liste der lauffähigen Prozessen ihr Pensum an Rechenzeit verbraucht haben. Im Vergleich dazu haben frühere Versionen von Linux und ältere Unix-Versionen die Neupositionierung der Prozesse nach jeder abgelaufenen Zeitscheibe berechnet. Der Scheduler führt die Statistik über die Rechenzeit und kann den Prozessen mit der großen Laufzeit gegenüber den Prozessen mit sehr geringen Laufzeit die Prioritäten anpassen. Scheduler von Linux und Unix bevorzugen bei der Auswahl des nächsten abzuarbeitenden Prozesses interaktive<sup>1</sup> vor rechenintensiven Prozessen. Es wird versucht, dass die Reaktionszeit der Anwendungen auf die Benutzereingaben im Bereich zwischen 50 und 150 ms liegt. Der Scheduler ist in der Datei `<kernel/sched.c>` implementiert.

Die Prozesse in Linux-Kernel werden durch die sogenannten Prozess-Kontrollblöcke PCB (Process Control Block) repräsentiert. Der Prozess-Kontrollblock ist mit Hilfe der

---

<sup>1</sup>Prozesse, die sich in der Interaktion mit dem Benutzer befinden, wie z.B. Prozesse für die Tastatur- und die Mauseingaben.

Task-Struktur `struct task_struct` in der Datei `<linux/sched.h>` definiert. Die Kontrollblöcke beinhalten eine Reihe von Informationen, die der Scheduler speichern muss, wenn die Prozesse unterbrochen werden. Dabei wird der Prozesszustand, die Prozessidentifikationsnummer, der Inhalt aller Register der CPU zum Zeitpunkt der Unterbrechung im PCB gesichert. Der Scheduler speichert hier zusätzlich die Prozesspriorität und die verbrauchte Rechenzeit.

In Linux existiert eine Prozesshierarchie, d.h. es gibt einen aller ersten Prozess und alle weiteren Prozesse sind die Kinder von den jeweiligen Elternprozessen. Die Wurzel aller Prozesse in dem Hierarchiebaum ist der beim Systemstart erzeugte `init`-Prozess. Das ist der einzige Prozess, der keinen Elternprozess besitzt. Weil die Prozesse über die Eltern-Kind Beziehung miteinander verknüpft sind, ist es unter anderem möglich, dass das Beenden der Prozesse auf die möglichen Fehler hin überprüft werden kann.

Die Prozesse in Linux können sich in acht Zuständen befinden.

- aktiv: Der Prozess ist in diesem Zustand nur dann, wenn er gerade abgearbeitet wird.

- lauffähig: Die Prozesse sind in diesem Zustand, wenn sie nur auf die Ressource CPU warten, d.h. Prozess ist bereit und wartet auf die Prozessorzuteilung.

- ruhend/terminiert: Die Prozesse befinden sich in diesem Zustand, entweder bevor sie gestartet und damit lauffähig werden oder nachdem sie beendet wurden.

- zombie: Nach dem Beenden eines Rechenprozesses geht dieser nicht sofort in den Zustand `ruhend/terminiert`, sondern er kommt in den Zustand `zombi` und bleibt in diesem, solange der Elternprozess, der den beendeten Prozess erzeugt hat, den beim Betriebssystem gespeicherten Exitcode nicht abholt. Der Exitcode wird in dem entsprechenden PCB gespeichert. Erst nachdem der Elternprozess den Exitcode abgeholt hat, geht der beendete Prozess in den Zustand `ruhend/terminiert` über.

- unterbrechbar wartend: Die Rechenprozesse können ihren Verlauf über die Signale gegenseitig beeinflussen. Der wartende Prozess kann z.B. von einem anderen Prozess über den System-Aufruf in den Zustand `lauffähig` versetzt werden.

- nicht unterbrechbar wartend: Prozesse, die sich in diesem Zustand befinden, warten auf eine Ressource, die noch nicht frei ist. Im Unterschied zu dem Zustand `unterbrechbar wartend` kann die notwendige Ressource nicht von einem weiteren Prozess zur Verfügung gestellt werden.

- `TASK_STOPPED`: Dieser Zustand wird für das Debugging und Systemcall-Tracing benötigt.

- `TASK_TRACED`: Dieser Zustand wird für das Debugging und Systemcall-Tracing benötigt.

### 2.3.3 Speicherverwaltung

Die Speicherverwaltung ist eine weitere Komponente des Betriebssystems Linux. Das Betriebssystem weist jeder Anwendung ihren eigenen Adressraum zu. Dafür muss das Betriebssystem den Speicher virtualisieren. Somit ist es den Anwendungen nicht möglich bzw. nicht erlaubt direkt auf die physikalischen Adressen des Hauptspeichers zuzugreifen. Die Speicherverwaltung übernimmt die Übersetzung der virtuellen Adressen in die physikalischen Adressen. Diese Umrechnung funktioniert nur für die Task, die sich im Zustand **aktiv** befindet.

Die Speicherverwaltung wird durch das sogenannte Paging erleichtert. Dabei wird der Arbeitsspeicher in gleich große Seiten unterteilt. Bei der Übersetzung der virtuellen Adresse in die physikalische muss nicht jede Adresse einzeln übersetzt werden, sondern es muss lediglich festgestellt werden zu welcher Seite die Adresse gehört und zu welcher physikalischen Seite die virtuelle Seite verknüpft ist. Diese Seiten sind z.B. bei den x86 Systemen 4 kB groß. Eine Seite definiert also einen Adressbereich, der 4 kB Speicher adressiert. Die Zuordnung der Seiten zu den physikalischen Seiten erfolgt meistens so, dass keine Fragmentierung stattfindet. Eine interne Fragmentierung des Speichers ist aber nach wie vor möglich, wenn die Seite selbst z.B. nicht vollständig mit Daten gefüllt wird.

Die Aufteilung des Arbeitsspeichers auf die Seiten und der Verzicht auf die Behandlung einzelner Adressen erleichtert das sogenannte Swapping. Bei diesem Verfahren kann der Kernel bestimmte Seiten aus dem Arbeitsspeicher auf die Festplatte auslagern. Die Auslagerung der bestimmten Seiten erfolgt z.B. dann, wenn der freie Platz des Speichers erschöpft ist. Die Auslagerungs-Algorithmen müssen sich auf der Ebene der Seiten bewegen und sie müssen sich nicht um die einzelnen Adressen kümmern. Das Swapping war besonders wichtig, als der Speicher eine knappe Ressource darstellte.

Der Kernel verwaltet den virtuellen Speicher, d.h. jeder Prozess besitzt einen eigenen Speicherbereich und kann bei Bedarf benötigten Speicher anfordern. Die Zuordnung der virtuellen Seiten zu den physikalischen erfolgt durch die sogenannte Pagetable. Die Pagetable enthält neben der Zuordnung der Seiten noch weiter Informationen, z.B. wann der letzte Zugriff stattfand, ob die Seite ausgelagert ist oder ob sie verändert wurde.

Die beschriebene Speicherverwaltung mit Swapping und Paging ist auf die hardwareseitige Unterstützung angewiesen. Die Adressübersetzung erfolgt mit Hilfe der Memory Management Unit. Wenn der Prozess auf eine Speicheradresse zugreift, die keine Abbildung auf die entsprechende physikalische Adresse in der Pagetable besitzt, so löst die MMU einen Page Fault Interrupt aus und die Prozessausführung wird angehalten. Die Interrupt Service Routine des Betriebssystems lädt die betroffene Seite, falls sie vorher ausgelagert wurde, von der Festplatte in RAM und aktualisiert die Seitentabelle. Danach wird der Page Fault verursachende Befehl des Prozesses wiederholt und diesmal kann die MMU die geforderte Adresse auflösen. In den Fällen, in denen die Interrupt Behandlungsroutine merkt, dass die angeforderte virtuelle Adresse keiner entsprechenden physikalischen Seite zugeordnet werden kann, wird der Prozess mit einem Speicherzugriffsfehler beendet.

Die Adressräume aller Prozesse sehen gleich aus. Bei den Systemen mit der 32-Bit-

Architektur steht jedem Prozess einen 4 GB großen Adressraum zur Verfügung. In diesem Adressraum muss der Code und die Daten des Prozesses Platz befinden. Zusätzlich wird ein besonderer Bereich für das Betriebssystem reserviert. Zu jedem Prozess gehört ein sogenannter Stack. Der Stack wird bei den Funktionsaufrufen gebraucht um z.B. die Übergabeparameter an die Funktionen zu speichern. Die Threads, die in einem Prozess laufen, müssen jeweils ihre eigenen Stacks haben, die sich ebenfalls alle im Adressraum des Prozesses befinden müssen. Linux beansprucht das oberste Gigabyte Platz im Adressraum jedes Prozesses für sich. Der Grund für die Einrichtung eines speziellen Bereichs für das Betriebssystem im Adressraum eines Prozesses ist die Interrupt-Behandlung. Wenn der Interrupt auftritt, so geht der Kernel in den Ausführungsmodus Ring 0 und beginnt sofort mit der Abarbeitung der Interrupt Service Routine. Damit dies geschieht, muss sich die Startadresse der Routine bei jedem Prozess an der gleichen Stelle befinden.

Der Bereich für das Betriebssystem ist geschützt und ist aus dem Usermode weder lesbar noch schreibbar. Obwohl es in jedem virtuellen Adressraum den Kernelbereich gibt, verweisen alle diese virtuellen Seiten auf dieselben physikalischen Seiten.

### 2.3.4 I/O-Subsystem

Das I/O-Subsystem, auch I/O-Management genannt, ist eine weitere Komponente des Betriebssystems. Der gesamte Datenaustausch zwischen den Programmen und den Geräten wird über dieses Subsystem durchgeführt. Dieses System sollte einerseits einheitliche Schnittstellen zur Einbindung der Hardware an das Betriebssystem bieten und andererseits eine weitere einheitliche Programmierschnittstelle für die Anwendungen zum Zugriff auf die Peripherie zur Verfügung stellen.

In Linux (und Unix) unterscheidet man traditionell zwischen zwei Arten von Geräten. Die zeichenorientierten Geräte, auch „Character-Devices“ genannt, und die blockorientierten Geräte, die sogenannten „Block-Devices“, die ihre jeweiligen Schnittstellen zur systemkonformen Anbindung an das System erfordern. Die zeichenorientierten Geräte verarbeiten oder liefern ihre Daten zeichenweise. Den gesamten Datenaustausch kann man sich als eine Art Datenstrom vorstellen. Dabei kommen die Zeichen der Reihe nach einzeln hintereinander und ein Springen innerhalb dieses Streams ist normalerweise nicht möglich. Dadurch, dass der wahlfreie Zugriff auf die Daten nicht möglich ist, kann man die Reihenfolge der verfügbaren Daten nicht beeinflussen. Die typischen zeichenorientierten Geräte sind z.B. die Maus und die Tastatur.

Die blockorientierten Geräte sind in der Lage, im Vergleich zu den zeichenorientierten Geräten, ihre Daten blockweise zu verarbeiten, zu empfangen oder zu senden. Die Datenübertragung z.B. zwischen dem System und dem Gerät kann in einem kontinuierlichen Strom erfolgen. Die Reihenfolge der Daten kann jedoch zumindest blockweise beliebig sein. Die typischen blockorientierten Geräte sind z.B. Disketten-, CDROM-Laufwerke oder Festplatten.

Mittlerweile gibt es sehr viel mehr verschiedene Geräte, die sich nicht mehr eindeutig zu den zeichenorientierten bzw. zu den blockorientierten Geräten zuordnen lassen. Moderne Multimedia-Peripherie trug dazu bei, dass weitere Schnittstellen zu dem Kernel hinzugefügt wurden. Neben den Subsystemen, die speziell für die Integration von z.B.

Soundkarten, Grafikkarten oder Netzwerkkarten implementiert wurden, gibt es Subsysteme, die nicht für die bestimmten Gerätetypen implementiert sind, sondern für die Art der Anbindung dieser Geräte. Es gibt z.B. ein PCI (Peripheral Component Interconnect) -Subsystem, USB (Universal Serial Bus) -Subsystem, SCSI (Small Computer System Interface) -Subsystem usw.

Die oben beschriebenen Schnittstellen dienen innerhalb des I/O-Managements der systemkonformen Integration der Hardware. Die Aufgabe der einheitlichen Programmierschnittstelle der I/O-Verwaltung ist die Abbildung jeglicher Hardware auf die speziellen Dateien. Das Betriebssystem erzeugt die Gerätedateien, die die vorhandene Hardware repräsentieren. Die Anwendungen können über die normalen Dateizugriffsoperationen auf die Hardwarekomponenten zugreifen. Die tatsächlichen Zugriffe, sowohl auf die normalen Dateien als auch auf die Gerätedateien, sind innerhalb der I/O-Verwaltung realisiert. Mit der Einführung weiterer Geräteklassen wurde die Programmierschnittstelle um die eigenen Zugriffsfunktionen für die Multimediasysteme erweitert.

### 2.3.5 Gerätetreiber

Gerätetreiber sind die Software-Komponenten, die den Anwendungen die Funktionalitäten aller Geräte zur Verfügung stellen. Die Funktionalitäten der Geräte werden von den Treibern über die definierten Schnittstellen für die Anwendungen nutzbar gemacht. Fast alle Geräte, mit der Ausnahme von Prozessor, Speicher und wenigen anderen Komponenten, benötigen Einstellungs- und Steuerungssoftware, die Treiber. Der Kernel muss die Treiber für die vorhandenen Hardwarekomponenten, die verwendet werden sollen, in sich eingebettet haben.

Dabei gibt es eine Fülle an unterschiedlichsten Geräten, die über die Treiber in das System integriert werden, wie z.B. die systemnahen Tastaturen, Bildschirme, Netzwerkkarten und im Allgemeinen die Drucker, Bandlaufwerke, Scanner, Erweiterungskarten.

Wie bereits im Kapitel 2.3.4 dargestellt wurde, können die zahlreichen Hardwarekomponenten über die speziellen Bussysteme mit dem Betriebssystem verbunden werden. Deswegen gibt es die unterschiedlichen Schnittstellen für die Treiber zu den entsprechenden Treiber-Subsystemen, die von dem Betriebssystem zur Verfügung gestellt werden. Nach der Art der Anbindung oder nach den anderen Eigenschaften unterscheidet man unter Anderen zwischen den folgenden Subsystemen.

- Character-Devices

- Block-Devices

- Netzwerk

- USB

- SCSI

- FireWire

- Bluetooth

- PCI/PCIe

- Cardbus und PCMCIA

Die breite Palette an den möglichen Hardwarekomponenten, die möglichst leicht und gleichzeitig auf die universelle Art und Weise in das System integriert werden sollen, brachte die Erweiterung der Standard-API (Standard-Programmierschnittstelle) mit sich. Die zusätzlichen Applikationsschnittstellen sind:

- Standard-API (mit *open*, *close*, *read*, *write* und *ioctl*)

- Multimedia-Schnittstellen (z.B. Video4Linux, die oft von Webcams verwendet wird)

- Kommunikationsschnittstellen

- Card-Services

Der Linux-Kernel ist ein monolithischer Kernel. Das bedeutet, dass alle notwendigen Treiber als Teil des Kernels vorhanden sein müssen. Bei den monolithischen Kernen muss der gesamte Kernel neu generiert werden, wenn ein neuer Treiber hinzugefügt werden soll. Die Linux-Entwickler haben eine Möglichkeit geschaffen die Treiber als Module zum laufenden Kernel hinzu zu laden. Im Vergleich zu den fest eingebauten Treibern können die als Modul ausgeführten Treiber ohne der neuen Generierung des Kernels und ohne den Neustart des Systems zum Kernel hinzugefügt und wieder entfernt werden. Diese Fähigkeiten erleichtern das Entwickeln und das Testen der neuen Treiber erheblich. Ein weiterer Vorteil der Modularisierung der Treiber ist die erhöhte Robustheit des ganzen Systems. Zum Beispiel der Absturz eines als Modul geladenen Treibers wird meist nicht zum Absturz des gesamten Systems führen und ein entsprechendes Fehlverhalten kann durch das erneute Laden des Treibers behoben werden.

Die Treiber als Module erleichtern den Benutzern die Verwendung von gewünschten Geräten, weil sie den Treiber einfach laden können. Durch die Modul-Treiber entfällt die Notwendigkeit den gesamten Kernel erneut zu erstellen. Die Benutzer müssen keine Kenntnisse darüber besitzen wie sie einen Kernel neu generieren sollen. In der Realität spielt dieser Vorteil aber keine große Rolle. Es gibt zwei Effekte, die diesem Vorteil entgegenwirken.

1. Aus der Sicht des Benutzers ist es meistens eine Herausforderung den passenden Treiber zuerst zu finden. Viele Hardwarehersteller konzentrieren sich bei der Vermarktung ihrer Peripherie in erster Linie an die Betriebssysteme, die weite Verbreitung erfahren haben. Dadurch werden die Treiber in der Regel nicht von dem Hersteller zur Verfügung gestellt, sondern sie werden von den Programmierern auf Grund von zugänglicher Dokumentation erstellt. In solchen Fällen heißt das, dass die Treiber für Linux meistens nicht den vollen Funktionsumfang des Geräts abdecken und zweitens relativ spät, wenn überhaupt, nach dem Erscheinen des Geräts verfügbar sind. Mittlerweile gibt es immer mehr Hersteller, die Linux als Betriebssystem mit den Treibern unterstützen.

2. Die Linux-Entwicklung schreitet stetig voran. Das heißt aber auch, dass die spezifischen Funktionen, die die Treiber benutzen, und die Treiber-Schnittstellen selbst, sich innerhalb des Betriebssystems verändern. Dadurch kommt es oft vor, dass ein Kernelmodul, das für eine bestimmte Kernel-Version erstellt wurde, nicht mehr kompatibel zu der vom Benutzer verwendeten Kernel-Version ist. Für die Vermeidung der Instabilität beim Betrieb muss die Kernel-Version genau zu dem Modultreiber passen.

Die *Open Source* Treiber sind mit ihrem Quellcode verfügbar. Damit kann jeder den Treiber für die verwendete Kernel-Version selbst erstellen und damit Inkompatibilität vermeiden. Manche PC Komponentenhersteller, wie z.B. die Grafikchiphersteller Nvidia oder AMD, bieten ihre Treiber nicht als *Open Source* Treiber an, um ihr Know-How nicht preiszugeben.

Den logischen Aufbau von Treibern kann man in drei Schichten unterteilen: High-Level-Schicht, Kern-Schicht und die Low-Level-Schicht. Die High-Level-Schicht kümmert sich, wie z.B. bei den USB Geräten, um die Auswertung und um das Zusammensetzen von Kommandopaketen, da die Kommunikation zwischen dem Gerät und dem Treiber mit Hilfe von Paketen erfolgt. Die Kern-Schicht ist z.B. für die Verwaltung der angeschlossenen Geräte oder für die spezifische Hardwareerkennung zuständig. Dies ist notwendig, wenn z.B. mehrere Geräte im System vorhanden sind. Die Low-Level-Treiber führen die tatsächlichen Interaktionen mit der Hardware durch, wie z.B. das Auslesen und Beschreiben von Registern.

Jeder Linux-Treiber muss einen bestimmten Satz an Funktionen implementiert haben.

1. Funktionen, die die Integration des Treibers in den Kernel ermöglichen.

2. Funktionen, deren Ausführung von den Anwendungen ausgelöst werden.

3. Funktionen, die vom Kernel aufgerufen werden.

Die Integration des Treibers in den Kernel erfolgt mit Hilfe der folgenden Funktionen: `init_module`, `cleanup_module`, `probe`, `remove`. Beim Laden des Treibers oder bei dessen Aktivierung, falls dieser nicht als Modul sondern als fester Bestandteil des Kernels ist, müssen vom Treiber benötigte Ressourcen reserviert werden oder es muss die Hardwareerkennung durchgeführt werden. Entsprechende Funktionen werden z.B. beim Entladen des Treibers oder beim Herunterfahren des Systems benötigt, die die belegten Ressourcen wieder freigeben oder die Hardwarekomponenten in einen definierten Zustand bringen.

Die Anwendungen greifen auf die von Treibern bereitgestellten Funktionalität über die Funktionen wie `open`, `close`, `read`, `write` zu. Wenn der Kernel einen Systemaufruf von einer Anwendung bekommt, die die Dienste des Treibers fordert, dann wird die dem Systemaufruf entsprechende Funktion des Treibers aufgerufen.

Die Funktionen, die vom Kernel aufgerufen werden, sind z.B. die Interruptbehandlungs Routinen. Diese Funktionen werden bei der Treiberinitialisierung beim Kernel ange meldet. Dazu gehören unter Anderen die möglichen Kernel Threads oder die Tasklets. Die Interruptsbehandlungsroutine muss den Fall berücksichtigen, dass der evtl. notwendige

Datentransfer zwischen dem Treiber und der Anwendung während dieser Ausführungsphase nicht möglich ist, da der Treiber nicht in der Lage ist auf die Speicherbereiche der Anwendung zuzugreifen. In solchen Fällen setzt der Treiber intern ein Statusbit, dass ein Interrupt ausgelöst wurde. Als erstes, nachdem die Anwendung wieder aktiv wird, muss sie dieses Bit beim Treiber abfragen und somit einen eventuell notwendigen Datentransfer einleiten.

# 3 PCIe - Schnittstelle

In diesem Kapitel wird die PCIe-Architektur vorgestellt und den anderen Ein-/Ausgabebussen gegenübergestellt. Es werden die Vorteile und die Schlüsselqualifikationen der PCIe-Verbindungen dargestellt. Darüberhinaus werden detailliert die charakteristischen Merkmale des PCIe-Busses beschrieben. Es wird die Schichtarchitektur der über den PCIe-Bus angeschlossenen Teilnehmer mit der jeweils kurzen Funktionsbeschreibung einzelner Schichten vorgestellt.

## 3.1 Einführung

PCIe stellt mit sich ein Bussystem der dritten Generation dar. Ein Bussystem dient der Datenübertragung zwischen mehreren Teilnehmern über einen gemeinsamen Übertragungsweg. PCIe wird sowohl zum Anbinden von Peripherie als auch zur Kommunikation zwischen Endgeräten benutzt. Die Vertreter der ersten Generation sind: ISA (Industry Standard Architecture), VESA (Video Electronics Standards Association) Local Bus und Micro Channel. Die Vertreter der zweiten Generation sind: PCI und AGP (Accelerated Graphics Port).

Der ISA-Bus wurde als ein Teil des IBM-PC Projektes im Jahre 1981 entwickelt. Ursprünglich handelte es sich dabei um eine einfache Herausführung des 8 Bit breiten Systembusses. Die Erweiterung des Busses auf 16 Bit erfolgte mit der Einführung des neuen Intel 80286 Prozessors. Der Takt des Busses war synchron mit dem der CPU. Der Bus war für die Taktfrequenz von 6 bzw. 8 MHz ausgelegt. Mit der fortschreitenden Entwicklung der Prozessoren und stetig steigenden Taktfrequenzen wurden Chipsätze entwickelt, mit deren Hilfe man den ISA-Bus mit der CPU verbinden konnte. Die Entwicklung des PCI-Busses verdrängte den ISA-Bus nahezu vollständig. ISA-Busse werden auch noch heute in Industrie-PCs oder in eingebetteten Systemen eingesetzt. Die theoretische Bandbreite des ISA-Busses mit einem Bustakt von 8.3 MHz und der Busbreite von 16 Bit beträgt 15.9 MBytes pro Sekunde, da aber die Addressierung jedes Zugriffs einen Takt dauerte fiel die theoretische Bandbreite auf die ca 8 MBytes pro Sekunde. Die tatsächlich erzielte maximale Bandbreite lag zwischen 1 und 2 MBytes pro Sekunde.

VESA Local Bus wurde als Ergänzung zu dem ISA-Bus eingeführt. Die schnellen Grafikkarten erforderten einen höheren Datendurchsatz als dies der ISA-Bus ermöglichte. Der Bus bestand hauptsächlich aus den herausgeführten Signalen des i486 Prozessors, dadurch war die Portierung auf andere als x86 Systeme nahezu aussichtslos. Der Slot für die Erweiterungskarten musste 112 Pins aufnehmen. Es konnten maximal 3 Karten gleichzeitig eingesteckt werden. Die enge Anbindung an den speziellen Prozessortyp erforderte hohen Schaltungsaufwand für die Anpassung an die nächste Prozessorgeneration. Die große Länge der Schnittstelle in Verbindung mit der erhöhten Anzahl von Pins, in

Vergleich zur ISA-Schnittstelle, führte nicht selten beim Installieren oder Entfernen der Karten zum Bruch der Hauptplatten. Der VESA Local Bus ist Rückwärtskompatibel zu dem ISA-Bus. Die maximale theoretische Bandbreite betrug 130 MBytes pro Sekunde wobei die im Einsatz erzielte Bandbreite durchschnittlich 32 MBytes pro Sekunde betrug.

Die Entwicklung des PCI-Busses wurde durch die Firma Intel im Jahre 1990 angestoßen. Intel wollte den VESA Local Bus als Nachfolger des ISA-Busses nicht unterstützen und eine neue, prozessorunabhängige Bus-Architektur etablieren. Der PCI-Bus wurde als eine Plattform angesehen, die die Ausnutzung aller Rechenkapazitäten der kommenden Pentium-Prozessoren erlaubte. Intel versuchte die PC-Industrie für den PCI-Bus zu gewinnen und gründete 1992 die sogenannte *Peripheral Component Interconnect Special Interest Group (PCI-SIG)*. Die Ziele dieser Organisation sind die Verwaltung, Weiterentwicklung und die Verbreitung des PCI-Standards. Mittlerweile zählen über 800 Mitglieder zu der Gruppe. Im Laufe der Zeit wurden mehrere Versionen des Standards beschlossen und umgesetzt. Der Bus zeichnet sich durch die Möglichkeit der Hierarchisierung aus. Der Bus wird je nach Version mit 33 MHz bzw. 66 MHz betrieben. Die Bandbreite beträgt für PCI 1.0 (1991) bis PCI 3.0 (2004) 133 MBytes pro Sekunde - 532 MBytes pro Sekunde. Die sogenannte Host-Bridge dient als Schnittstelle zwischen den CPU mit Arbeitsspeicher und dem Bus. Die masterfähigen Peripheriegeräte können über die Hostbridge als Target direkt in den Arbeitsspeicher schreiben und aus ihm lesen. Auf dem PCI-Bus kommuniziert immer ein Master mit einem Target. Die angeschlossenen Komponenten teilen sich die zur Verfügung stehende Bandbreite untereinander auf. Mit einer steigenden Anzahl an Busteilnehmern sinkt die Bandbreite entsprechend. Die gängigste Bus-Konfiguration in einem PC ist: eine Busfrequenz von 33 MHz und eine Busbreite von 32 Bit. Die dabei erzielbare maximale Bandbreite ist etwa 90 MBytes pro Sekunde. Der PCI-Bus hat sehr große Verbreitung in vielen Bereichen erfahren. Seit 2005 wird aber der PCI-Bus durch seinen Nachfolger den PCIe-Bus allmählich verdrängt.

Der PCI-Bus erfüllte die Anforderungen für Grafik-, Netzwerk- und andere Schnittstellenkarten über eine längere Zeit. Allerdings reichte nach einiger Zeit die verfügbare Bandbreite für die damals aufkommenden Grafikkarten mit 3D-Beschleunigung nicht mehr aus. Aus diesem Grund wurde das AGP Bus-System eingeführt. Der AGP-Bus stellte eine Punkt-zu-Punkt-Verbindung zur Anbindung der Grafikkarte an die Northbridge dar. Die Vorteile gegenüber dem PCIe-Bus haben sich z.B. dadurch ergeben, dass immer nur ein Teilnehmer an Datentransfers beteiligt war, oder dadurch, dass es kein „richtiger“ Bus war und man deswegen die Taktfrequenz höher wählen konnte. Die erste Version des AGP Systems wurde von Intel im Jahre 1997 veröffentlicht. Im Laufe der Zeit wurde der Standard erweitert und die mögliche maximale Bandbreite erhöht. Die AGP-Schnittstelle der Version 1.0 (1x) erlaubte den Datendurchsatz von 266 MBytes pro Sekunde. Die letzte Version der Schnittstelle erlaubt die Bandbreite von 2133 MBytes pro Sekunde. Es gab wenige Ausnahmen von Hauptplatten, die über mehr als eine AGP-Schnittstelle verfügten. Die zusätzliche Schnittstelle konnte dann für einige RAID-Kontroller benutzt werden um den Datendurchsatz nicht mit den anderen Komponenten am PCI-Bus teilen zu müssen. Eine weitere Steigerung der Datentransferleistung von AGP ist ohne grundlegende Veränderungen an der Architektur nicht mehr

möglich. Die parallele Datenübertragung bei hohem Takt und die damit verbundenen, strengen Timing-Anforderungen machten das Platinendesign sehr Aufwendig. Die Anbindung der Grafikkarten an den Arbeitsspeicher des PCs ist nicht mehr so wichtig wie früher, weil die Grafikkarten im Zuge der gefallenen Preise für Speicherchips über genügend dedizierten Speichers verfügen. Der Hauptnachfolger für den AGP-Bus ist der PCIe-Bus.

Die Entwicklung der Prozessoren ist seit der Einführung des PCI-Busses schneller vorangegangen als die des Busses selber. Der PCI-Bus sollte seinerzeit verschiedene, bereits vorhandene Busse ersetzen und eine gemeinsame Plattform für unterschiedliche Aufgaben darstellen. Diese Funktion konnte er nicht lange aufrecht halten. Mit den neuen Möglichkeiten der neuen Prozessoren und immer größere, zur Verfügung stehende Menge an Speicher öffneten ganz neue Tätigkeitsfelder. Dabei entstanden neue Anwendungen, die weit größere Bandbreiten forderten als der PCI-Bus anbot. Es entstanden wieder zahlreiche Bus-Systeme, die nur für bestimmte Anwendungsfälle spezialisiert waren, wie z.B. AGP, ATA100 usw. Die Gemeinsamkeit aller erwähnten Busse war die parallele Datenübertragung. Dem immer weiter steigenden Bandbreitenbedarf entgegnete man mit der Erhöhung der Busfrequenz. Die hohe Anzahl an benötigten Pins verbrauchte viel Platz auf den Platinen. Steigende Frequenzen in Verbindung mit den vielen Leitungen brachten elektrische Probleme mit sich und somit stellt sich nun der Bus als Flaschenhals bei der Kommunikation zwischen der Peripherie und der CPU dar. Unter der Berücksichtigung solcher Aspekte hat die PCI-SIG den PCIe-Standard entworfen, der sowohl PCI als auch AGP ersetzen soll und eine größere Datenübertragungsrate als AGP bieten soll.

## 3.2 PCIe

PCIe ist eine separate, serielle Punkt-zu-Punkt Verbindung mit differentieller Signalübertragung. Dadurch sind viele Vorgehensweisen, wie sie bei dem PCI-Bus üblich waren, nicht mehr anwendbar. Im Vergleich zu dem PCI-Bus müssen die Kommunikationspartner nicht mehr um den Zugriff auf den Bus konkurrieren. Jeder Teilnehmer treibt exklusiv den eigenen Satz an Sendeleitungen und ist gleichzeitig der Empfänger über die Empfangsleitungen. Bei den Punkt-zu-Punkt Verbindungen gibt es immer nur zwei Kommunikationsteilnehmer, die entsprechende Leitungen treiben können.

Die Verbindung zwischen den zwei PCIe Geräten bezeichnet man als *Link*. Ein *Link* kann aus mehreren *Lanes* bestehen. Eine *Lane* wiederum besteht aus zwei Paaren der differentiellen Leitungen. Jedes Paar ist für die Kommunikation in eine Richtung verantwortlich. Außer der erwähnten Leitungen gibt es keine weiteren, wie z.B. für die Adressen, Daten oder für Kontrollssignale, wie beim PCI-Bus. Die bewusste Beschränkung an die wenigen Signale erleichtert die Skalierung der Verbindung für die steigenden Anforderungen in Zukunft und engt die Möglichkeiten der Implementierung der neuen Einsatzmodellen nicht ein. Die starke Veränderung des physischen Aufbaus gegenüber dem PCI erfordert eine gänzlich neue Infrastruktur der Systemkomponenten. Die Entwickler von der PCI-SIG haben Wert darauf gelegt, dass die Softwareschnittstelle für

den PCIe-Bus voll kompatibel zu dem PCI-Bus bleibt. Dadurch müssen weder Betriebssysteme, Treiber noch Anwendungsprogramme angepasst werden.

Die erste Version des PCIe Erweiterungsstandards arbeitet mit einer Datenrate je Lane von maximal 250 MByte/s pro Richtung beziehungsweise 500 MB/s in beide Richtungen zusammen. Für die Anwendungen mit hohen Anforderungen an Bandbreite kann man die *Lanes* koppeln und damit diese Anforderungen erfüllen. Die Tabelle 3.1 zeigt die theoretisch erreichbaren Bandbreiten in Abhängigkeit von der Anzahl der gekoppelten *Lanes* und der Version des Standards. Inzwischen existiert die Version 2.0 der PCIe-

Tabelle 3.1: Datenrate PCI-Express

|     | PCIe 1.0  | PCIe 2.0   | PCIe 3.0   |

|-----|-----------|------------|------------|

| x1  | 250 MB/s  | 500 MB/s   | 1000 MB/s  |

| x2  | 500 MB/s  | 1000 MB/s  | 2000 MB/s  |

| x4  | 1000 MB/s | 2000 MB/s  | 4000 MB/s  |

| x8  | 2000 MB/s | 4000 MB/s  | 8000 MB/s  |

| x16 | 4000 MB/s | 8000 MB/s  | 16000 MB/s |

| x32 | 8000 MB/s | 16000 MB/s | 32000 MB/s |

Spezifikation mit einer Datenrate von 500 MByte/s pro Lane. Die neueste Spezifikation in der Version 3.0, die bis 2011 festgelegt werden soll, soll eine Datenrate von 1000 MByte/s pro Lane ermöglichen.

Die PCIe-Spezifikation beschreibt einige Typen von PCIe Elementen: *root complex*, *PCIe-PCI bridge*, *endpoint* und *switch*.

- *Root complex*: Diese Komponente ist das Bindeglied zwischen dem Ein-/Ausgabesystem und der CPU mit dem Hauptspeicher. Der *root complex* verwaltet und konfiguriert die über den Bus angeschlossene Peripherie. Weiterhin übersetzt er die Zugriffe in beide Richtungen.

- *PCIe-PCI bridge*: Eine *PCIe-PCI bridge* ermöglicht die Koexistenz von älteren Bussystemen wie PCI/PCI-X neben PCIe.

- *Endpoint*: Ist ein konkretes Gerät, das die PCIe-Transaktionen empfangen oder selbst auslösen kann. Der *Endpoint* kann selbst z.B. eine Bridge zum USB sein. Man unterscheidet zwei Typen von *Endpoints*: *legacy* und *native*. Der Unterschied beruht auf der Fähigkeit bestimmte Transaktionen verarbeiten zu können.

- *Switch*: *Switches* spannen die PCIe-Hierarchie auf. Mehrere *endpoint*-Geräte werden mit dem *Switch* verbunden. Der *Switch* ermöglicht die Verbindung entweder zwischen zwei Kommunikationspartnern oder zwischen dem *endpoint* und dem *root complex*.

### 3.3 PCIe Transaktionen

Die Transaktionen bilden die Basis der Informationsübertragung zwischen den PCIe-Geräten, wobei der Informationstransport paketbasiert ist. Die Transaktionen sind als eine Serie von Übertragungen eines oder mehrerer Pakete definiert, die für die komplette Informationsübertragung zwischen den Kommunikationspartnern notwendig sind. Eine Transaktion besteht aus zwei Abschnitten: einer Anfrage oder Aufforderung und Fertigstellung oder Erfüllung dieser Anfrage. Die Einheit, welche die Anfrage macht, sendet das entsprechende Paket zu der Einheit, welche diese Anfrage bearbeiten soll. Dieses Paket kann dabei über mehrere *Switches* hinweg zu dem Ziel geleitet werden. Die Reaktion auf das Aufforderungspaket kann aus keinem, einem oder auch mehreren Fertigstellungspaketen bestehen.

Die PCIe-Architektur beschreibt vier verschiedene Typen von Transaktionen:

1. Memory Transactions

2. I/O Transactions

3. Configuration Transactions

4. Message Transactions

#### 3.3.1 Memory Transactions

Bei den sogenannten Speicher-Transaktionen werden über die Speichereinblendung verfügbare Daten von oder zu den PCIe-Geräten transportiert. In den meisten Fällen erfolgt der Datentransfer zwischen dem PCIe-Gerät und dem Arbeitsspeicher des Rechners. Man unterscheidet zwischen unterschiedlichen Arten der Speicher-Transaktionen, einige von ihnen sind: *Memory Read Request*, *Memory Read Completion* und *Memory Write Request*. Die Adressierung erlaubt die Verwendung von kurzen, d.h. 32 Bit langen Adressen als auch von langen, d.h. 64 Bit langen Adressen.

Beim lesenden Speicherzugriff eines PCIe-Geräts sendet dieses ein *Memory Read Request* mit der Angabe der Adresse und der gewünschten Datenmenge aus. Der *Root complex* führt den eigentlichen Speicherzugriff auf den Arbeitsspeicher aus und liefert die angeforderten Daten an das PCIe-Gerät mit den, evtl. mehreren, *Memory Read Completions*.

Wenn ein PCIe-Gerät in den Arbeitsspeicher schreibt, dann werden die *Memory Write Requests* abgeschickt. Auf die Bestätigung des erfolgreichen Schreibvorgangs kann dabei zu Gunsten der besseren Leistungsfähigkeit verzichtet werden.

#### 3.3.2 I/O Transactions

Das sind Transaktionen, die den Speicherbereich der Ein-/Ausgabe betreffen. Dieser Speicherbereich wird aus Kompatibilitätsgründen zu den bereits vorhandenen Geräten unterstützt. Einige interessante Transaktionen sind: *I/O Read Request*, *I/O Read Completion*, *I/O Write Request* und *I/O Write Completion*. I/O Transactions verwenden immer nur 32 Bit breite Adressen.

### 3.3.3 Configuration Transactions

Die *Configuration Transactions* greifen auf den Konfigurationsspeicherbereich der PCIe-Geräte. Sie dienen der Konfiguration und der Einstellung aller am Bus hängenden Geräte. Der Konfigurationsspeicherbereich erstreckt sich nur über die Konfigurationsregister, die jedes PCI oder PCIe-Gerät hat. Im Unterschied zu dem PCI-Standard können die PCIe-Geräte einen wesentlich größeren Satz an Registern vorweisen. Die *Configuration Transactions* sind: *Configuration Read Request*, *Configuration Read Completion*, *Configuration Write Request* und *Configuration Write Completion*.

Die Konfigurations-Transaktionen gehen normalerweise nicht von den Endgeräten aus. Diese werden ausschließlich vom *root complex* aus getriggert.

### 3.3.4 Message Transactions

Eine weitere Transaktionsart, die es so bei PCI nicht gab, sind die *Message Transactions*. Unter den *Message Transactions* sind viele verschiedene Pakete zusammengefasst, die für die Kommunikation zwischen den Endgeräten eingesetzt werden. Mit diesen Transaktionen werden z.B. Interrupts oder Fehler signalisiert oder sie werden für die Energieverwaltung gebraucht.

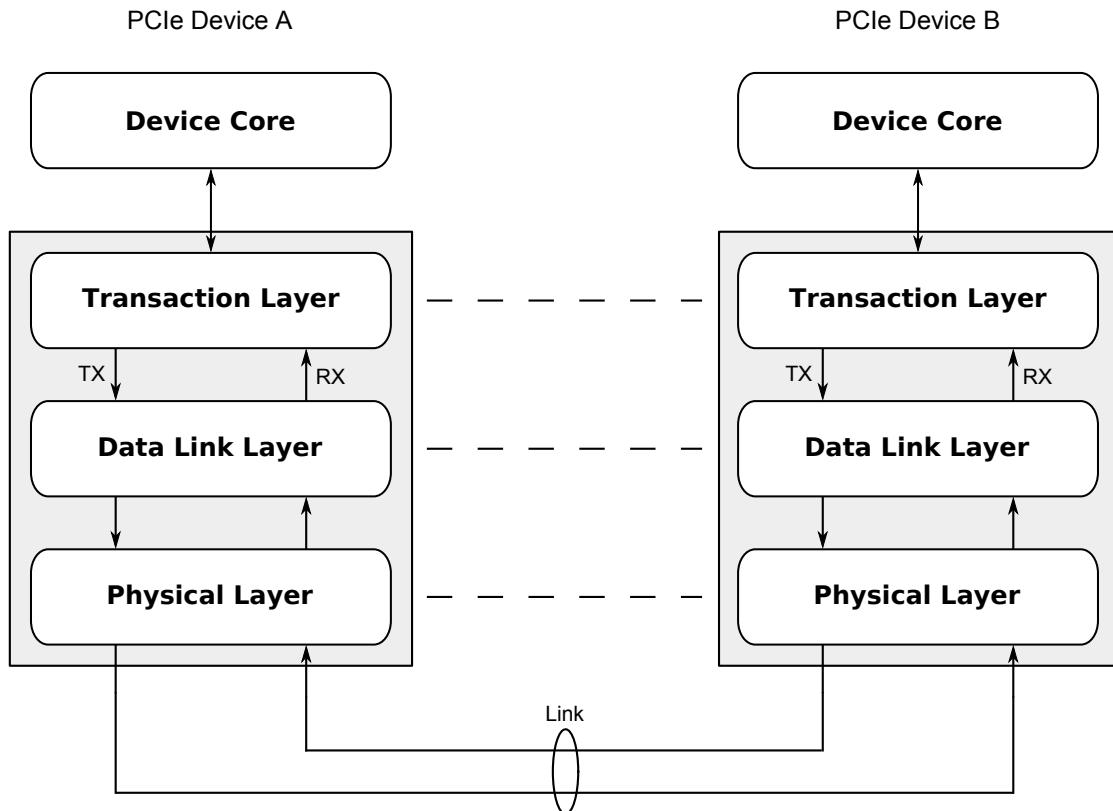

## 3.4 PCIe Übertragungsschichten

Die PCIe-Spezifikation definiert eine Architektur der Übertragung, die aus drei Schichten besteht. Jedoch müssen sich die Geräteentwickler nicht an diese Architektur halten, solange die vom Standard geforderte Funktionalität geboten wird. Die Abbildung 3.1 stellt die definierten Schichten dar.

Jede Transaktion durchläuft diese drei Schichten. Die erste Schicht lässt sich zum *Transaction Layer* zusammenfassen. Die Hauptaufgabe dieser Schicht ist die Bildung eines Transaktionspaketes aus den Daten, die von Kern des Gerätes kommen. Die ankommenden Pakete werden ausgewertet und die enthaltenen Daten an den Kern weitergeleitet. Diese Schicht entspricht der Zusammenfassung von *Transport* und *Network* Schichten des OSI-Modells.

Die zweite Schicht ist der *Data Link Layer*. Die Hauptaufgabe dieser Schicht ist Sicherstellung des korrekten Senden und Empfangen aller Transaktionen. Die Funktionalität des *Data Link Layer* stimmt mit der des OSI-Modells überein.

Die dritte und letzte Schicht ist der *Physical Layer*. Diese Schicht führt tatsächlich das Senden und Empfangen der Transaktionspakete durch. Die Funktionalität der *Physical Layer* stimmt mit der des OSI-Modells überein.

Dabei lässt sich jede dieser Schichten in zwei Blöcke aufteilen: ein Block, der für das Senden verantwortlich ist, und einer, der für das Empfangen verantwortlich ist. Beim Senden wird der Paketinhalt aus den funktionsbezogenen Daten des Gerätetkerns in der *Transaktionsschicht* gebildet. Dieses Paket wird in einem Puffer aufbewahrt und an den darunter liegenden *Data Link Layer* weitergegeben. Der *Data Link Layer* hängt an das Paket eigene zusätzliche Informationen zur Fehlererkennung auf der Empfangsseite an.

Abbildung 3.1: Übertragungsschichten der PCIe-Geräte

Dieses Paket wird schließlich an den *Physical Layer* weitergegeben. Das Paket wird dabei neu kodiert und mit zusätzlichem Header und Trailer über den Link analog, differentiell an den unmittelbaren Nachbarn übertragen.

Auf der Empfangsseite läuft das Paket in der umgekehrten Reihenfolge die drei Schichten durch. Der Empfänger dekodiert das empfangene Paket im *Physical Layer* und über gibt den Inhalt an die nächsthöhere Schicht. Der *Data Link Layer* überprüft das Paket auf Fehler, und falls es keine Fehler gab, wird das Paket an die *Transaktionsschicht* weitergereicht. Die *Transaktionsschicht* wandelt die Paketdaten in eine Form um, die der Gerätekern mit der entsprechenden Funktion verarbeiten kann.

### 3.4.1 PCIe Transaktionsschicht

Diese Schicht bildet das Rückgrat der Datenübertragung innerhalb des PCIe-Systems. Die Hauptaufgabe dieser Schicht ist das Generieren von entsprechenden Transaktionen, darunter die *Requests* und die *Completions*.

Die *Transaktionsschicht* empfängt auf der Sendeseite die Daten von dem Kern des Geräts, welche in PCIe-Transaktionen umgesetzt werden. Diese Daten können z.B. die Anforderung des Gerätes von bestimmten Daten sein oder aber die Antwort des Gerätes auf die vorangegangene Anfrage. Auf der Empfangsseite bekommt die *Transaktionsschicht* die PCIe-Transaktionen von der *Data Link Schicht*. Dabei geht die *Transaktionsschicht* davon aus, dass die ankommenden Pakete alle fehlerfrei und in der richtigen Reihenfolge sind. Die Sicherstellung der Fehlerfreiheit und der richtigen Reihenfolge ist die Aufgabe der *Data Link Schicht*.

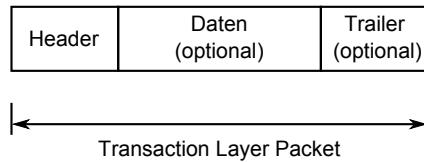

Die *Transaktionsschicht* verwendet zur Kommunikation mit den anderen PCIe-Geräten die eigenen Pakete: TLP (Transaction Layer Packet). Die Vielfalt der verschiedenen Transaktionstypen und der zu erfüllenden Aufgaben lässt sich über die Daten im Header des Transaktionspaketes einstellen. Dabei werden die Pakete in der *Transaktionsschicht* eines „Sendegerätes“ erzeugt und in der *Transaktionsschicht* des Empfängers ausgewertet und verarbeitet. Neben der bereits erwähnten Funktionalität ist die *Transaktionsschicht* auch für die Flusskontrolle der TLP und für einige Funktionen der Energieverwaltung zuständig ist.

Ein Paket der *Transaktionsschicht* besteht aus dem Header, den optionalen Daten und einem optionalen Trailer. Die Abbildung 3.2 stellt die Struktur eines Pakets der *Transaktionsschicht* dar. Ein TLP hat immer einen Header, dessen Länge nicht konstant ist, aber immer ein Vielfaches von vier Bytes beträgt. Die Länge des Header hängt von dem Typ der Transaktion ab. Vom Typ der Transaktion hängt auch das Vorhandensein von Nutzdaten ab. Die Menge an Nutzdaten muss ebenfalls ein Vielfaches von vier Bytes betragen. Wenn die Menge der zu übertragenden Daten nicht genau in einem Vielfachen von vier Bytes aufgeht, dann werden die fehlenden Bytes aufgefüllt. Das Auffüllen kann entweder bereits in den ersten vier Bytes oder aber in den letzten vier Bytes erfolgen. In dem Header des TLP werden die speziellen Bits gesetzt, die die Identifikation von „nutzlosen“ Bytes ermöglichen. Der Trailer des Paketes ist wie die Daten auch optional und wird nur selten benutzt. Der Trailer ist für die ECRC (end-to-end CRC)-Prüfsumme gedacht. Der *Data Link Layer* deckt mögliche Fehler ab, die bei der Übertragung über den

Link entstehen können. Die ECRC-Prüfsumme ermöglicht auch die Fehler zu erkennen, die während der Bearbeitung des Paketes auf der Ebene der *Transaktionsschicht* in den dazwischen liegenden Geräten, wie z.B. Switches, entstehen können.

Abbildung 3.2: Struktur eines TLP-Paketes

Ein Aufforderungspaket kann mehrere Antwortpakete nach sich ziehen. Es ist aber nicht möglich mehrere anstehende Aufforderungen mit nur einem Antwortpaket zu erfüllen

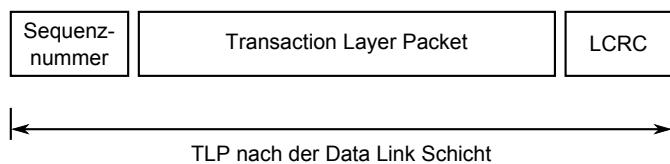

### 3.4.2 PCIe Data Link Schicht

Die Hauptaufgabe dieser Schicht ist die Sicherstellung der korrekten Übertragung auf dem Link, d.h. Fehlererkennung und Fehlerkorrektur. Der *Data Link Layer* sorgt dafür, dass die Pakete fehlerfrei und in der richtigen Reihenfolge über die einzelnen Links transportiert werden.

Der *Data Link Layer* setzt die Bildung der PCIe-Transaktion fort, indem sie das von der *Transaktionsschicht* kommende Paket um eigene Informationen erweitert und das neu entstandene Paket an die *Bitübertragungsschicht* weiterleitet. Die *Data Link Schicht* fügt jedem zu sendenden TLP als Header eine sogenannte Sequenznummer hinzu. Als Trailer wird eine spezielle Prüfsumme hinzugefügt: LCRC (Link CRC). Die Abbildung 3.3 zeigt ein TLP, das um die zusätzlichen Informationen für die Fehlererkennung von dem *Data Link Layer* erweitert wurde.

Sowohl die Ein- als auch die Ausgangsseite des *Data Link Layer* haben jeweils ihre eigenen Aufgaben. Beim Eintreffen eines Paketes übernimmt die *Data Link Schicht* dieses von der *Bitübertragungsschicht*. Es wird die Korrektheit des empfangenen Paketes anhand der Sequenznummer und der LCRC überprüft und dann, wenn sowohl die Sequenznummer als auch die LCRC zeigen, dass es keine Fehler gab, wird dieses Paket, bereinigt von der Sequenznummer und der LCRC, an die Empfangsseite der *Transaktionsschicht* weitergereicht. In diesem Fall, wenn das Paket als fehlerhaft erkannt wird,

Abbildung 3.3: Erweiterung des TLPs um die zusätzlichen Informationen in der *Data Link Schicht*

wird es erst gar nicht an die *Transaktionsschicht* weitergeleitet. Die *Data Link Schicht* versucht mit der entsprechenden Protokollinstanz auf der Gegenseite den Fehler zu be seitigen. Die Fehlerbeseitigung erfolgt meistens durch die Aufforderung das fehlerhafte Paket noch einmal zu senden. Der *Data Link Layer* lässt also nur die korrekt empfan genen Pakete an die *Transaktionsschicht* durch. Die *Transaktionsschicht* geht dadurch immer davon aus, dass alle Pakete, die sie empfängt, auch korrekt sind.

Wenn ein Sender einen TLP an einen Empfänger über den Link sendet, dann erwartet er eine Quittierungsantwort. Es kann ein NACK (von engl. negative acknowledgement = negative Bestätigung) DLLP (Data Link Layer Packet), im Falle eines falschen LCRC, ein ACK (von engl. acknowledgment = Bestätigung) DLLP, wenn es keine Fehler gab, oder er bekommt gar keine Bestätigung, wenn das gesendete Paket z.B. beim Empfänger gar nicht ankommt. Die Quittierungsantworten folgen nicht unbedingt nach jedem empfangenen Paket. Zwei Kommunikationspartner auf einem Link tauschen die sogenannten „credits“ unter sich aus. Diese „credits“ erlauben dem Sender eine bestimmte Anzahl an Paketen abzusenden ohne eine Quittierungsnachricht abzuwarten. Der Empfänger kann mit einer Quittierungsantwort einen fehlerfreien Empfang eines bestimmten Paketes bestätigen. Und wenn es noch mehrere unbestätigten Pakete vor diesem Paket gegeben hat, dann gelten damit auch diese als bestätigt.

Auf der Sendeseite wird einem zu sendenden TLP eine Sequenznummer und LCRC hinzugefügt. Das gesendete Paket wird in einem Puffer der *Data Link Schicht* zwischengespeichert. Wenn der Empfänger das Paket auf der Linkebene fehlerfrei empfangen hat, dann bestätigt er es mit einem ACK DLLP, das die Sequenznummer des empfangenen Paketes enthält. Der Sender entfernt daraufhin das gespeicherte Paket aus dem Puffer. Falls andererseits der Empfänger einen LCRC-Fehler im Paket entdeckt, dann sendet er ein NACK DLLP mit der Sequenznummer. In diesem Fall veranlasst der Sender einen erneuten Versand des betroffenen Paketes. Die *Data Link Schicht* des Senders kann den Fehler zum Protokollieren an den Rootkomplex melden. Falls es für einen bestimmten TLP aus dem Puffer dreimal ein NACK DLLP kam, d.h. es wurde viermal erfolglos versucht das Paket zu übertragen, dann veranlasst die *Data Link Schicht* die Reinitialisierung des Links und meldet einen korrigierbaren Fehler an den Rootkomplex.

Auf der Empfangsseite überprüft die *Data Link Schicht* die LCRC der eintreffenden Pakete. Diese Seite veranlasst dann, je nach Ergebnis der Prüfung, das Versenden der ACK DLLP oder NACK DLLP. Die Empfangsseite erhält auch die Quittierungsantworten von der Sendeseite des Kommunikationspartners. Daraufhin wird innerhalb dieser Schicht auf der Sendeseite entweder das entsprechende TLP aus dem Puffer entfernt oder noch einmal versendet. Auf dieser Seite wird auch auf die Einhaltung der Reihenfolge geachtet. Dabei wird die Sequenznummer der eintreffenden Pakete überprüft. Durch diesen Mechanismus können fehlende oder sich wiederholende Pakete sicher erkannt werden.

Die Sequenznummer ist eine 12 Bit breite Zahl, die, zusammen mit den zusätzlichen ungenutzten 4 Bits zu einem 2 Byte großen Header zusammengefasst werden. Das LCRC-Feld ist 32 Bit breit und wird an das TLP angehängt. LCRC wird über alle Bits des zu sendenden Paketes berechnet, auch über die sogenannten „reserved“ und über die angehängte Sequenznummer.

Die *Data Link Schicht* unterscheidet nicht um welchen Typ von TLP es sich handelt,

wenn eine Sequenznummer dem Paket zugewiesen wird. Die Sequenznummern hängen auch nicht davon ab, wer die Anfrage startet und wer sie erfüllt. Die Instanz der *Data Link* Schicht des Senders ist die einzige Bestimmungsgröße bezüglich der Sequenznummer. Diese Nummer hat ihre Gültigkeit nur innerhalb eines Links, d.h. wenn ein Switch das Paket von einem Link auf das andere weiterleitet, dann hat das Paket eine unterschiedliche aber jeweils für den Link gültige Sequenznummer. Die nötigen Informationen zum Routing der Pakete innerhalb des PCIe-Netzwerks steckt im Header des TLP.

Die *Data Link* Schicht verwendet noch einen eigenen Pakettyp: DLLP. Diese Pakete dienen linkspezifischen Funktionen, wie z.B. Benachrichtigungen über die aufgetretenen Fehler und für die Energieverwaltung. Diese Pakete entstehen in der *Data Link* Schicht und werden immer in dieser verarbeitet. Sie werden auch anders als Pakete der *Transaktionsschicht* beim Senden behandelt. Die DLLP werden immer nur zwischen den direkten Nachbarn auf dem Link versendet im Unterschied zu den TLPs, die auch über mehrere Kommunikationsgeräte hinweg transportiert werden können. Neben den bereits beiden erwähnten Typen von DLLPs wie NACK und ACK gibt es noch zwei weitere:

- Flow control DLLP: Diese Pakete dienen der Datenflusssteuerung. Es gibt insgesamt drei Typen davon: zwei werden bei der ersten Initialisierung des Links verwendet und der dritte Typ wird im Betrieb gebraucht, um den direkten Kommunikationspartnern die noch zur Verfügung stehende Kapazität an freien Plätzen für die reinkommenden Pakete anzuzeigen. Die Erzeugung und den „Verbrauch“ von diesen Paketen übernimmt die *Data Link* Schicht, die Kontrolle über das Senden und über die Daten in diesen Paketen hat allein die *Transaktionsschicht*.

- Power management DLLP: Diese Pakete dienen der Steuerung und der Kontrolle vom Energiestatus des Links. Dabei entscheidet nicht die *Data Link* Schicht wann und ob sie die power management DLLP versendet, sondern es tut die Logik, die für Energieverwaltung zuständig ist, die dann das Versenden auslöst. Werden die power management DLLP empfangen, dann werden die Daten an die Energieverwaltung abgegeben.

Alle DLLPs haben eine konstante Länge von 6 Bytes: 4 Bytes für die Daten und 2 Bytes für die CRC (Cyclic Redundancy Check) Summe. Das CRC-Feld wird hierbei anders berechnet als das Feld für LCRC und ECRC. Die Verarbeitung dieser Pakete seitens der *Data Link* Schicht unterscheidet sich von den „normalen“ TLP-Paketen. Die *Bitübertragungsschicht* leitet die DLLP an die *Data Link* Schicht weiter und diese Schicht teilt auch mit ob es Fehler bei der Übertragung gab oder nicht. Erst wenn es keine Fehler gab, überprüft die *Data Link* Schicht das Paket mit Hilfe der CRC-Prüfsumme auf die Korrektheit. Falls die *Bitübertragungsschicht* einen Fehler meldet, wird das Paket von der *Data Link* Schicht verworfen. Das wiederholte Senden von DLLPs ist nicht vorgesehen und sie werden deswegen auch nicht in den Puffern zwischengespeichert. Die *Flow Control* DLLPs haben einen Einfluss auf die *Transaktionsschicht*, die *Power Management* DLLPs üben Einfluss auf die Energieverwaltung aus und die NACK und ACK DLLPs werden innerhalb der *Data Link* Schicht benutzt.

### 3.4.3 PCIe Bitübertragungsschicht

Die *Bitübertragungsschicht* ist die unterste Schicht. Eine ihrer Aufgaben ist es, die elektrische Verbindung zwischen zwei direkt miteinander verbundenen Geräten herzustellen. Diese Schicht übernimmt die Pakete von der *Data Link* Schicht, um sie über „Link“, eine logische Verbindung wegzuschicken und sie leitet die über den „Link“ empfangenen Pakete an die höhere Schicht weiter.

Man kann die *Bitübertragungsschicht* in zwei weitere Schichten unterteilen: in eine logische und eine elektrische Schicht. Die Aufgaben des logischen Teils ist die Bearbeitung der zu sendenden und zu empfangenen Paketen. Der sogenannte elektrische Teil stellt eine elektrische Schnittstelle dar, die eine Verbindung zwischen zwei Geräten herstellt. Diese Schnittstelle beinhaltet unter anderem auch die differentiellen Treiber und Empfänger für jede *Lane*.

Auf der Sendeseite der logischen Schicht werden die Bytes des Pakets zuerst mittels eines *Scramblers* pseudozufällig umkodiert, diese Bytes werden in einem 8b/10b Verfahren kodiert und anschließend um die speziellen Paketmarker erweitert. Die Empfangsseite führt die gleichen Operationen in der umgekehrten Reihenfolge durch. Im Folgenden werden die einzelnen Operationen näher erläutert.

#### 8b/10b - Kodierung

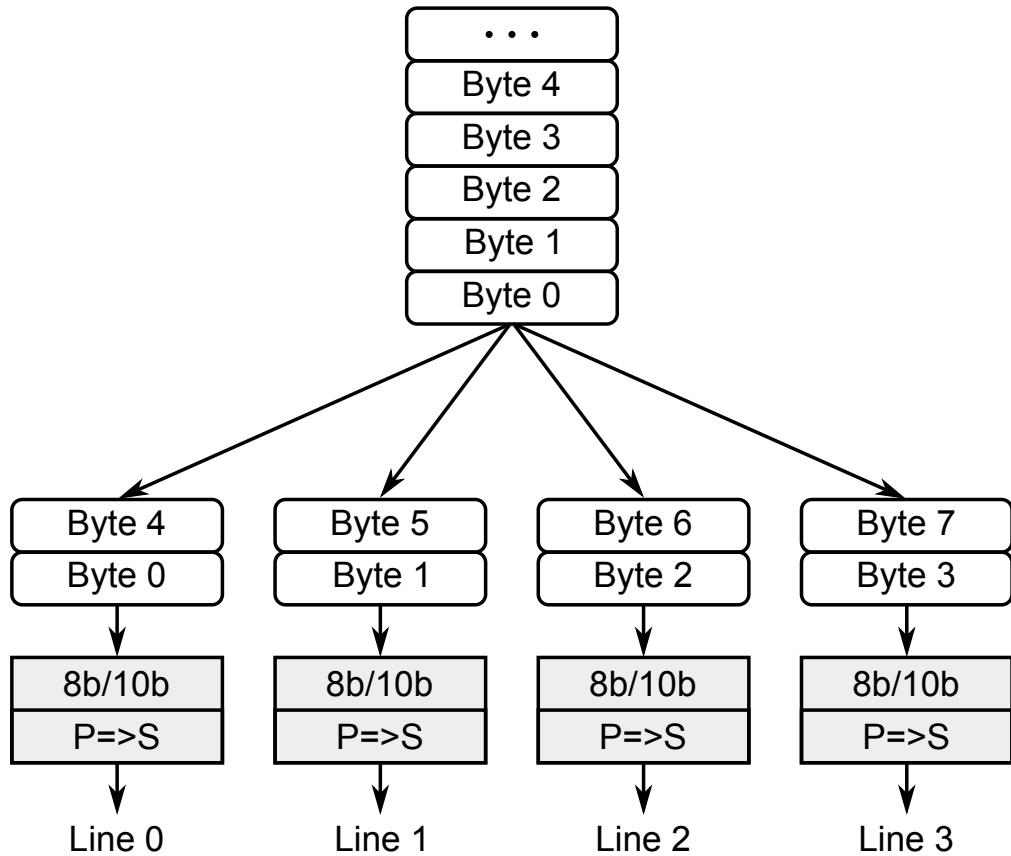

Eine weitere Aufgabe, die die *Bitübertragungsschicht* zu erfüllen hat, ist die 8b/10b - Kodierung der Daten. Der Hauptzweck dieser Kodierung ist es, das Taktsignal in den Datenstrom einzubinden. Bei dieser Kodierung werden 8 Bit Daten mit einem 10 Bit langen Symbol kodiert. Neben der erwähnten Taktrückgewinnung erlaubt die Kodierung den Gleichspannungsausgleich.