Stuttgart University

Distributed Systems Dept

Breitwiesenstraße 20-22

D-70565 Stuttgart, Germany

St. Petersburg Technical University

Distributed Computing & Networks Dept

Politehnicheskaya ul. 29

195251 St. Petersburg, Russia

# Configuration and Synchronization Management in Distributed Multimedia Systems

CR-Klassifikation: C.2.4, C.4, D.4.7, G.1.6, G.2.2., I6

*Technical Report of the Project OPTIMUS 01 IR 605

'Optimization, Modeling and Implementation of

Distributed Multimedia Systems'*

Prof. Dr. K.Rothermel

Responsible Head of the Project

Distributed Systems Dept

Stuttgart University

Prof. Dr. Yu.Karpov

Responsible Head of the Partner

Research Group

Distributed Computing and Networks Dept

St. Petersburg Technical University

Fakultätsbericht 1997/11

Technical Report

August 1997

Fakultät Informatik

Institut für Parallele und

Verteilte Höchleistungsrechner

Universität Stuttgart

Breitwiesenstraße 20-22

D-70565 Stuttgart

## Abstract

This annual technical report presents the current state of the project OPTIMUS 01 IR 605 'Optimization, Modeling and Implementation of Distributed Multimedia Systems', which is a research activity at St. Petersburg Technical University, Distributed Computing and Networks Department in collaboration with Stuttgart University, Distributed Systems Department. The project is supported by a research grant of the 'Bundesministeriums für Bildung, Wissenschaft, Forschung und Technologie' of Germany<sup>1</sup>.

The project is dedicated to the problems of configuration and synchronization management modeling, analysis, optimization and development for distributed multimedia systems.

The annual report presents the methods, models, algorithms, mechanisms, and a simulation tool developed for analysis, optimization and design of distributed multimedia application configuration management, negotiation and resource reservation protocol, and adaptive synchronization protocol, that support configurable distributed multimedia applications. Results of computational experiments conducted for complexity evaluation of algorithms proposed are presented as well. Problems of testbed platform development and implementation for configuration and synchronization management of distributed multimedia systems are discussed.

The research results obtained are oriented on the further development of CINEMA (Configurable IntEgrated Multimedia Architecture) that was designed at the Distributed Systems Department of Stuttgart University and supports development and control of multimedia applications with arbitrary processing topologies consisting of multiple data sources and sinks as well as arbitrary intermediate processing stages.

---

<sup>1</sup> Das diesem Bericht zugrundeliegende Vorhaben OPTIMUS wurde mit Mitteln des Bundesministeriums für Bildung, Wissenschaft, Forschung und Technologie unter dem Förderkennzeichen 01 IR 605 gefördert. Die Verantwortung für den Inhalt dieser Veröffentlichung liegt bei den Autoren.

## Executors

Distributed Systems Department

Dept

University of Stuttgart

Stuttgart

Germany

Kurt Rothermel, Prof., Dr.

Responsible Head of the Project

Gabriel Dermler, PhD

Walter Fiederer, PhD

Distributed Computing & Networks

Technical University of St. Petersburg

St. Petersburg

Russia

Yuri Karpov, Prof., Dr.

Responsible Head of

the Partner Research Group

Alexander Hagini, Prof., Dr.

Responsible Research Executor

Igor Chernorutskij, Prof, Dr.

Yuri Senichenkov, Assoc. Prof., Dr.

Alexander Glebovsky, Assoc. Prof.

Andrei Borshev, Dr.,

Viktor Roudakov,

Gennadiy Shchemelev,

Nikolaj Kolesnikov,

Vladislav Voinov, PhD

## CONTENTS

|          |                                                                                                            |           |

|----------|------------------------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>INTRODUCTION .....</b>                                                                                  | <b>1</b>  |

| <b>2</b> | <b>APPLICATION LIFECYCLE.....</b>                                                                          | <b>3</b>  |

| 2.1      | PREPARATION PHASE.....                                                                                     | 3         |

| 2.2      | ESTABLISHMENT PHASE .....                                                                                  | 4         |

| 2.3      | ACTIVE PHASE.....                                                                                          | 5         |

| 2.4      | TERMINATION PHASE .....                                                                                    | 5         |

| 2.5      | CONCERN OF THIS PAPER.....                                                                                 | 5         |

| <b>3</b> | <b>CINEMA SYSTEM FOR CONFIGURING AND CONTROLLING DISTRIBUTED MULTIMEDIA APPLICATIONS.....</b>              | <b>6</b>  |

| 3.1      | APPLICATION MODEL .....                                                                                    | 6         |

| 3.2      | CINEMA SYSTEM ARCHITECTURE.....                                                                            | 6         |

| 3.3      | QoS ARCHITECTURE .....                                                                                     | 7         |

| <b>4</b> | <b>CONFIGURATION SERVICE.....</b>                                                                          | <b>9</b>  |

| 4.1      | NEGOTIATION REQUIREMENTS .....                                                                             | 9         |

| 4.1.1    | <i>Functional capabilities and resource shortages.....</i>                                                 | 9         |

| 4.1.2    | <i>Port type compatibility.....</i>                                                                        | 9         |

| 4.1.3    | <i>Format constraints of media parameters .....</i>                                                        | 9         |

| 4.1.4    | <i>Stream relations.....</i>                                                                               | 9         |

| 4.1.5    | <i>Topology complexity.....</i>                                                                            | 10        |

| 4.1.6    | <i>Requirements to the configuration service .....</i>                                                     | 10        |

| 4.2      | CONFIGURATION SERVICE ARCHITECTURE .....                                                                   | 11        |

| 4.3      | CONFIGURATION SERVICE ALGORITHM .....                                                                      | 12        |

| 4.3.1    | <i>General algorithm .....</i>                                                                             | 12        |

| 4.3.2    | <i>Input data for the configuration server .....</i>                                                       | 12        |

| 4.3.3    | <i>Refinement of the configuration server algorithm .....</i>                                              | 13        |

| <b>5</b> | <b>MAPPING A DMA TO A DCS .....</b>                                                                        | <b>15</b> |

| 5.1      | INTRODUCTION TO MAPPING PROBLEM.....                                                                       | 15        |

| 5.2      | MATHEMATICAL FORMULATION.....                                                                              | 16        |

| 5.3      | MAPPING ALGORITHMS .....                                                                                   | 18        |

| 5.3.1    | <i>An exact searching algorithm.....</i>                                                                   | 18        |

| 5.3.2    | <i>Approximate algorithm.....</i>                                                                          | 21        |

| 5.3.3    | <i>Heuristic algorithm based on cluster analysis .....</i>                                                 | 22        |

| 5.3.4    | <i>An algorithm to find the feasible assignment of a DMA to a DCS .....</i>                                | 24        |

| 5.3.5    | <i>Initial asSIGNment iMproving Algorithm (SIGMA) .....</i>                                                | 25        |

| 5.4      | EXPERIMENT: COMPUTATIONAL COMPLEXITY AND ACCURACY OF MAPPING ALGORITHMS .....                              | 29        |

| 5.4.1    | <i>Technology .....</i>                                                                                    | 29        |

| 5.4.2    | <i>Testable DMA graphs .....</i>                                                                           | 29        |

| 5.4.3    | <i>Results .....</i>                                                                                       | 31        |

| <b>6</b> | <b>PERFORMANCE EVALUATION AND OPTIMIZATION OF AN ADAPTIVE PROTOCOL FOR SYNCHRONIZING MEDIA STREAM.....</b> | <b>38</b> |

| 6.1      | MODELING AND SIMULATION ENVIRONMENT COVERS 3.0 .....                                                       | 38        |

| 6.1.1    | <i>COVERS 3.0 modeling methodology.....</i>                                                                | 39        |

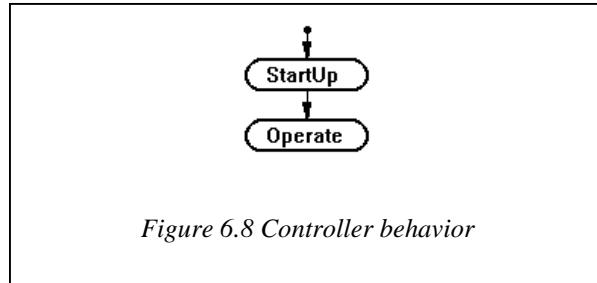

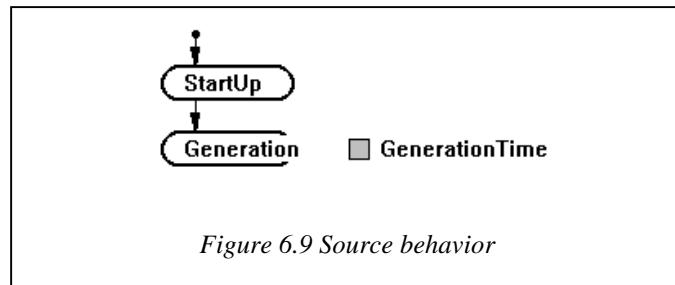

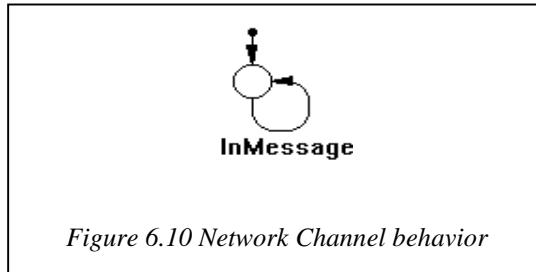

| 6.1.2    | <i>Object behavior .....</i>                                                                               | 40        |

| 6.1.3    | <i>COVERS 3.0 environment .....</i>                                                                        | 42        |

| 6.1.4    | <i>Interactive model execution.....</i>                                                                    | 44        |

| 6.1.5    | <i>Statistics collection and reporting .....</i>                                                           | 45        |

| 6.1.6    | <i>Comments .....</i>                                                                                      | 45        |

| 6.2      | MODELING THE ADAPTIVE SYNCHRONIZATION PROTOCOL USING COVERS 3.0.....                                       | 46        |

| 6.2.1    | <i>A COVERS model of the Adaptive Synchronization Protocol .....</i>                                       | 46        |

|           |                                                                                |           |

|-----------|--------------------------------------------------------------------------------|-----------|

| 6.2.2     | <i>Future work</i>                                                             | 50        |

| <b>7</b>  | <b>PLATFORM FOR CONFIGURATION AND SYNCHRONIZATION MANAGEMENT INVESTIGATION</b> | <b>51</b> |

| <b>8</b>  | <b>CONCLUSIONS</b>                                                             | <b>53</b> |

| <b>9</b>  | <b>REFERENCES</b>                                                              | <b>56</b> |

| <b>10</b> | <b>APPENDIX 1. MAPPING PROBLEM SPECIFICATION LANGUAGE</b>                      | <b>58</b> |

| 10.1      | DMA GRAPH PRESENTATION                                                         | 58        |

| 10.1.1    | <i>DMA component specification structure</i>                                   | 58        |

| 10.1.2    | <i>DMA link specification structure</i>                                        | 58        |

| 10.2      | THE DCS GRAPH PRESENTATION                                                     | 59        |

| 10.2.1    | <i>DCS computer specification structure</i>                                    | 59        |

| 10.2.2    | <i>DCS virtual connection specification structure</i>                          | 59        |

| 10.2.3    | <i>DCS communication resource specification structure</i>                      | 59        |

| 10.3      | INITIAL ASSIGNMENT SPECIFICATION                                               | 60        |

| 10.4      | EXAMPLE OF SPECIFICATION FILE                                                  | 60        |

## 1 Introduction

This annual technical report presents the current state of the project OPTIMUS 01 IR 605 'Optimization, Modeling and Implementation of Distributed Multimedia Systems', which is a research activity at St. Petersburg Technical University, Distributed Computing and Networks Department in collaboration with Stuttgart University, Distributed Systems Department. The project is supported by a research grant of the 'Bundesministeriums für Bildung, Wissenschaft, Forschung und Technologie' of Germany.

Distributed multimedia applications (DMA) such as multimedia mail, collaborative work systems, teleconferencing, kiosks, virtual reality applications and others require high-speed computer networks with high processing and transfer rate, adaptive, lightweight transmission protocols on top of the network.

The usage of multimedia was enabled by the technological progress in the fields of networks and endsystems that supply needful equipment for an even increasing transmission and computational power. However, the functionality of modern operating and transport systems is not sufficient to allow the efficient development, implementation and control of distributed multimedia applications. A multimedia development platform is required to enrich the given functionality by specialized abstractions and mechanisms that support distributed multimedia processing. The main issues that have to be tackled are communication and processing of multimedia data under real-time conditions, the automatic placement of DMA in distributed computer systems (DCS), resource reservation, and synchronization of multimedia data streams.

The project is dedicated to the problems of configuration and synchronization management modeling, analysis, optimization and development for distributed multimedia systems. The goal of OPTIMUS project is as follows:

- to develop an approach, models, optimization methods and algorithms for configuration management based on automatic mapping of a distributed multimedia application (DMA) to a distributed computer system (DCS) and negotiation and resource reservation protocol,

- to develop the adaptive synchronization protocol and elaborate simulation models for its analysis and optimization,

- to develop a testbed platform to probe and evaluate algorithms and mechanisms proposed for DMA management

The annual report presents the methods, models, algorithms, mechanisms, and a simulation tool COVERS developed and used for analysis, optimization and design of DMA configuration management, negotiation and resource reservation protocol, and adaptive synchronization protocol, that support configurable distributed multimedia applications. Results of computational experiments conducted for evaluation of complexity of algorithms proposed are presented as well. Problems of testbed platform development and implementation for configuration and synchronization management of distributed multimedia systems are discussed.

The research results obtained are oriented on the further development of CINEMA (Configurable IntEgrated Multimedia Architecture) that was designed at the Distributed Systems Department of Stuttgart University and supports the development and control of multimedia applications with arbitrary processing topologies consisting of multiple data sources and sinks as well as arbitrary intermediate processing stages.

The remaining part of the report is organized in the following way. In Section 2, the DMA lifecycle and management tasks at each stage are described, the problems concerning the paper are formulated. In Section 3, architecture and models of CINEMA system for configuring and controlling DMA are presented. In Section 4, negotiation requirements, architecture and an algorithm of configuration service are described.

In Section 5, the problem of mapping a DMA to a DCS is discussed and formulated, mapping algorithms that differs by computational complexity and solution error are proposed, experimental results of algorithms' complexity analysis are presented and discussed.

In Section 6, the adaptive synchronization protocol developed at the IPVR is considered. A formal specification and model of the protocol are described using the abstractions, high-level language, and functionality provided by COVERS software platform elaborated by the research team of the Technical University of St. Petersburg. The protocol performance evaluation and optimization problems are formulated.

In Section 7, a prototype of videoconferencing system as base of a designed platform for configuration and synchronization management is described.

In Conclusions, the main results obtained are summarized. In Appendix, mapping problem specification language developed and implemented in C++ is represented.

## 2 Application lifecycle

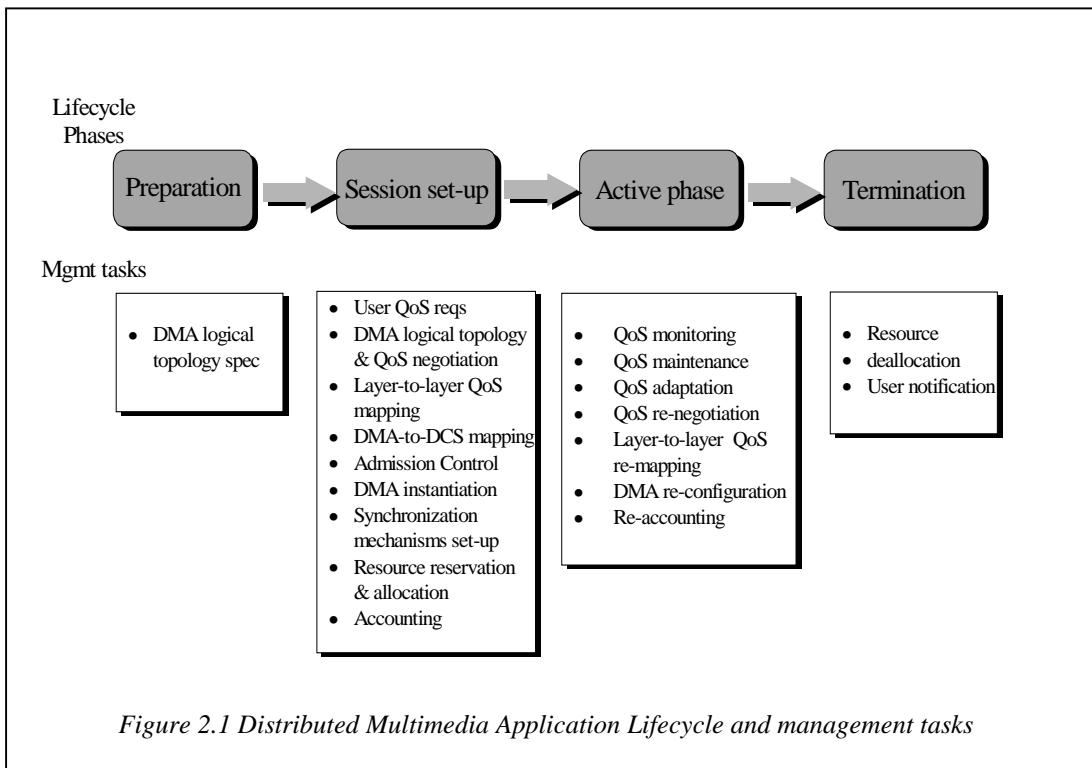

To get better understanding of management tasks concerning a DMA we consider the following application lifecycle a DMA follows after it's installed on a computer system (Figure 2.1).

We suggest to consider the following four steps during the lifecycle of a DMA session: the preparation phase, the session set-up phase, the active phase and the termination phase. To provide a requested service, the management system should analyze the correctness of a user request and specify DMA logical structure (topology) at the preparation phase, to establish a DMA session with QoS requested by the user, to control and to maintain the session QoS during the active phase, and to terminate the session when requested by the user or due to a failure, e.g. during heavy network congestion.

Let us give a brief description of DMA management tasks needed during these four phases.

### 2.1 Preparation phase

Initially a user specifies a DMA logical topology he wants to utilize. The user also can be asked to specify how he is going to work with the application - supposed session time (i.e. how long), start time (immediately or at any time in the future), etc. The user may declare some QoS management policies, such as what the system should do if QoS degrades below a particular level - terminate the application, try to automatically adapt QoS without user intervention or negotiate new QoS with the user, - what QoS requirements the user is ready to weaken, if all the requirements can't be satisfied all together, etc. Doing that the user and the system prepare a contract, in which the user is obliged to use the application in a certain manner, and the system has to provide a certain level of QoS in turn. The contract assignment will be done in the next phase, when DMA will be placed in the DCS and user QoS requirements will be negotiated with the DMA topology.

*DMA logical topology specification* is concerned with defining DMA topology as a set of components interconnected via links. Components are processing elements encapsulating functions for capturing, storing, presenting and manipulating continuous data streams. A link is an abstraction of an unidirectional communication channel, conveying stream from one component to one or more others.

The specified DMA topology is checked syntactically and semantically for media stream compatibility between interconnected components.

## 2.2 Establishment phase

After DMA user submitted logical topology and the topology was checked, the session set-up phase begins.

User specifies QoS and stream synchronization requirements, the sources and sinks of the DMA, that have to be established at a time. The management system negotiates the QoS requirements of the user and QoS constraints of the DMA topology, finds a DMA placement in the DCS, defines required resources needed to support desired QoS, reserves the resources, prepares all mechanisms useful for streams' synchronization. After that, the session can be initiated at the given start time by launching the DMA and its associated clock.

Additionally the user may require in advance the fixed allocation of particular DMA components (usually sources and sinks) in the DCS, i.e. which components have to be placed to which computers.

*User QoS requirements* are concerned with defining required levels of QoS for the DMA user(s). Required QoS values may be expressed in terms of advisory values, mandatory values, upper and lower thresholds or a variety of other forms.

*Layer-to-layer QoS mapping* performs the translation between representations of QoS at different system levels. In particular, this mapping function is required to translate the user QoS parameter values to those of the service provider to perform resource reservation as required to support the requested QoS.

*DMA logical topology & QoS negotiation* permits to refine a DMA topology, which might support the requested QoS. QoS requirements of the DMA user(s) have to be mapped to each component of the DMA. So, the problem is to decompose the QoS requirements of the DMA users to QoS requirements to each component of the DMA taking into account the DMA topology, functional capabilities and resource availability of the DCS.

Moreover, because a DMA can have many users with different conflicting QoS requirements, the management system analyses correctness of every user request and negotiates the QoS requirements of the different DMA users with each other and with the DMA topology. When user specifications are submitted, the management system is to check for inconsistencies among the requirements of a single user as well as the whole user community. If the system cannot provide requested QoS for a user, it should re-negotiate QoS requirements with the user or refuse the user request.

*DMA-to-DCS mapping* permits to find the optimal placement plan of the DMA topology into a given DCS taking into account the resources required by the DMA and the DCS resources available in an offered time interval of the DMA session.

*Admission control* is responsible for comparing the resource requirements that arise from the QoS levels associated with a new DMA, and the available resources in the DCS.

*Synchronization mechanisms set-up* allows controlling and synchronizing the data flow of data streams arriving at sink components.

*DMA instantiation* is concerned with loading DMA component code.

*Resource reservation & allocation* is usually necessary in order to support a given level of QoS during DMA session. While resource reservation is done during *DMA-to-DCS mapping* operation, allocation of the resources is conducted after DMA instantiation, i.e. just before the beginning of the active phase.

*Accounting* concerns with the evaluation of the costs relative to a service requested by a user.

### **2.3 Active phase**

The active phase starts at the time specified by a user, i.e. immediately or at any time in future. In the last case, the management system provides advance reservations for guaranteed and predictive service as shown in [DKPS95], [FGV95], [WDS<sup>+</sup>95].

At the active stage the application is launched providing certain services to its users. The management system should support QoS monitoring and maintenance, if QoS requirements are violated.

*QoS maintenance* is based on dynamic mechanisms (e.g., fine grained resource tuning strategies), which allow to ensure that the required performance of individual DMA components as well as of DMA as the whole are kept within given bounds.

*QoS monitoring* is used to allow each layer of the system to track the ongoing QoS levels and compare them with the initial QoS requirements.

*QoS adaptation* implements coarse grained QoS maintenance control and must be able to exhibit graceful degradation reacting adaptively on changes in the environment and to violations of the contracted QoS.

QoS re-negotiation, layer-to-layer QoS re-mapping, DMA reconfiguration and re-accounting are performed if the DMA performance violates the contracted QoS.

### **2.4 Termination phase**

It's time when all the resources submitted to the application (or its part) should be freed and the users should be notified about session termination. The latter is important when application termination was initiated not by the users, but by the system due to the certain reasons (allowed service usage time has elapsed, or an unrecoverable error occurred). *Resource deallocation* procedure sends the notifications to all entities involved in the QoS provision relative to this DMA session to free reserved resources.

### **2.5 Concern of this paper**

Undoubtedly, being different all the DMA management tasks mentioned above have a lot of common properties. To perform any of them one should have dependencies between QoS parameters, which comprise a QoS goal, and system parameters at various levels of system architecture. Expressed in some form these dependencies are interpreted specifically for a particular management task (e.g. monitoring, diagnosis or operational control) and management policies. For instance, in papers [AH+97], [AH+97a], the active phase of the distributed application lifecycle mostly is considered, when all application components are attached to the resources, and management architecture, model based approach for QoS monitoring and operational control schemes for the World Wide Web system are proposed.

In our paper, we will discuss mostly the preparation and session set-up phases, algorithms and protocols used for management tasks of these two DMA lifecycle phases.

### 3 CINEMA system for configuring and controlling distributed multimedia applications

#### 3.1 Application model

In this section we briefly introduce abstractions for modeling configurable distributed multimedia applications. Similar concepts are pursued by various research groups [KHS95], [BCA<sup>+</sup>92] including the group defining IMA MMS [IMA93]. Here we describe the terminology used for CINEMA (Configurable INtegrated Multimedia Architecture) development platform. For detailed description of CINEMA we refer to [RBH94], [RDF97].

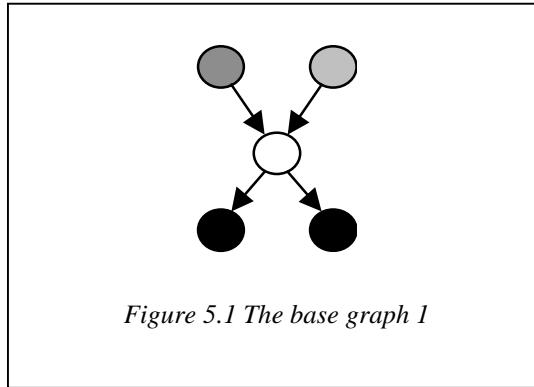

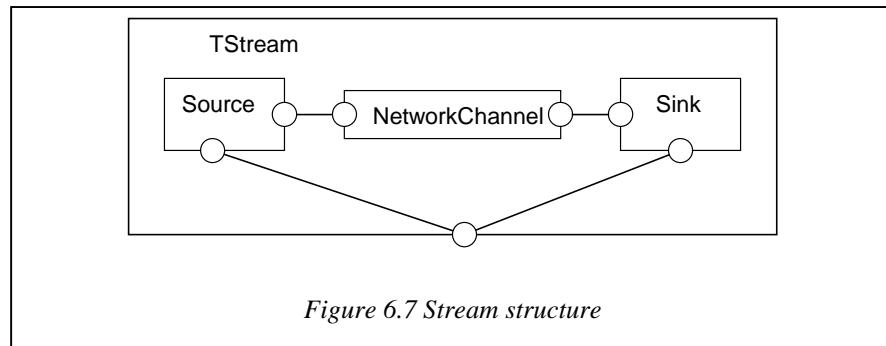

DMA are employed to generate, process and consume (e.g. present) continuous (e.g. audio, video) data streams over distributed locations into computer network. Generally, a DMA consists of some or more components, interacting with each other by data streams [RBH94]. Source components generate data, filters and mixers manipulate data, and sink components present data to users. DMA can be represented by one or some data flow graphs, composed out of such components and links representing the data streams between components.

Components encapsulate processing of multimedia data, e.g. for generating, presenting or manipulating data. To provide a uniform data access point for components, ports are used that deliver data units to the component (input port) or take data units from the component (output port). Source components are associated with output ports only, sink components – with input ports only. Intermediate components receive data from a number of input ports, perform some operation on the received data, and send the result via a number of output ports.

An application is constructed by specifying a topology of components interconnected via links. A link indicates a data flow between two interconnected ports and provides an abstraction from underlying communication mechanisms that may be used to perform the transport of data units.

#### 3.2 CINEMA system architecture

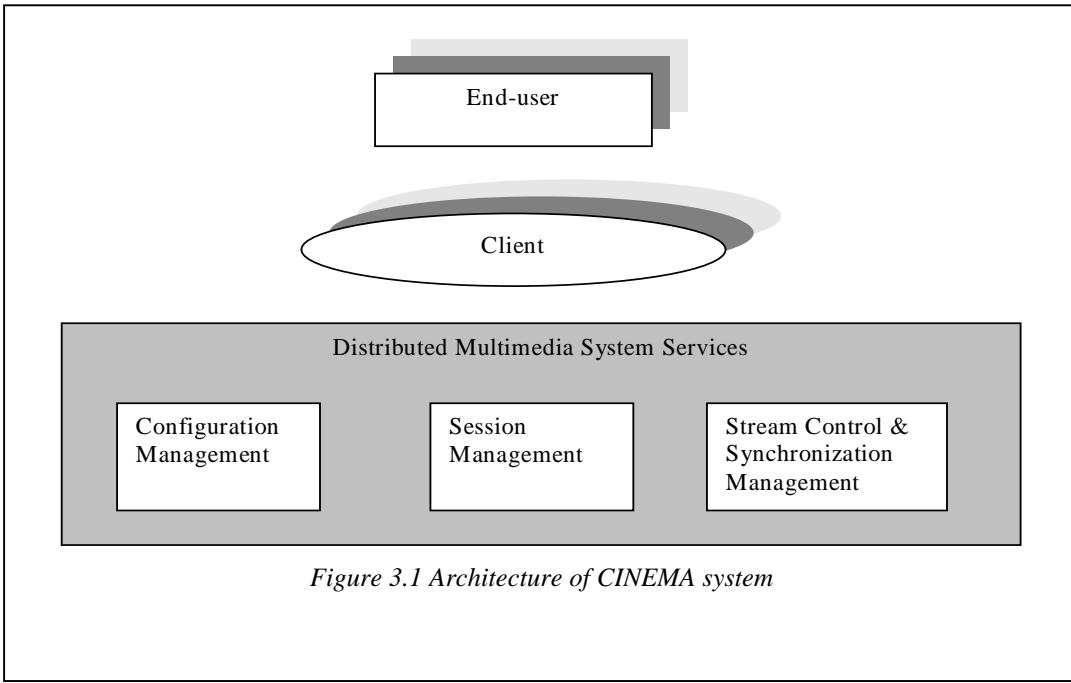

CINEMA [RBH94] is a middleware system that provides high abstractions and services for configuration distributed multimedia applications, the set-up of communication sessions along with QoS negotiation and resource reservation, as well as the service for data flow control and synchronization. CINEMA assists the client in these services in an integrated way.

Architecture of CINEMA system is depicted in Figure 3.1.

A client is a program entity that realizes, on one hand, a graphical interface service towards human end-users and, on the other hand, performs DMA topology construction, session set-up and data flow control using the services offered by CINEMA.

In CINEMA, a configurable distributed multimedia application is defined as a client containing the description of a topology of interconnected components, temporal properties of the topology and a session. The session is defined to select parts of the topology, that shall be established at a time, and to specify a media-specific and end-to-end QoS parameters corresponding to a QoS requested by end-user. The QoS description is located at the input ports of sinks.

In [RBF96], [RDF97] and [Bar96], configuration and session management services were defined assuming that a location of a DMA in a DCS is specified in any way in advance (e.g., by end-user). Now we consider extended configuration management that includes the automated mapping a logical application topology to a computer network. Adding the mapping function causes some rearrangements of the previous function distribution between the configuration and session services.

Figure 3.1 Architecture of CINEMA system

The configuration process is executed during the preparation and session set-up phases. First, the client refers to existing components by globally unique names and interconnects components to a logical application topology. Each stream and all ports connected to the stream are associated with one media type, e.g. "MPEG\_encoded\_video". A specified DMA logical topology is checked syntactically and semantically (for compatibility between interconnected ports) by the configuration service.

The second step of the configuration process is initialized when the client starts a session set-up. During the session set-up phase, the components necessary for the session (may be not all ones of the DMA) are selected. Desired QoS has to be indicated to CINEMA. Stream media values between the component ports are negotiated corresponding to the requested QoS taking into account a set of acceptable computers, their functional capabilities and resource availability. Then an optimal placement of the DMA in the DCS is found, resource reservation for the components and links is executed, and the physical application topology is instantiated. The instantiation concerns the provision of runnable code for components and links and the establishment of communication channels required for managing subsequent services.

Synchronization management is used within a session to control the data flow of data streams arriving at sink ports. CINEMA offers VCR-like commands to start, stop, and scale data flow of such streams. In addition, CINEMA allows to group streams for atomic control and to specify synchronization requirements between several streams by offering the concept of clock hierarchies [RH96a].

A stream synchronization service frees a client from the ever-recurring task of implementing flow control and synchronization algorithms as part of the development process of each multimedia application. By using the middleware service for stream synchronization, time-dependent data streams can easily be integrated into various applications, such as CSCW applications or tools to present multimedia documents.

### 3.3 QoS architecture

The necessity of different QoS levels arises from different tasks that have to be solved by a user and by a service provider. At highest level, end-user oriented QoS abstractions must be allowed to express user QoS requirements. At the lowest level, QoS descriptions serve to indicate resource demands. Consequently, the lowest level QoS description is resource oriented and independent on media-specific characteristics.

Besides at the middle level, media-specific QoS parameters are needed to negotiate QoS. The goal of the QoS negotiation is to settle on the best QoS complying with client (user) QoS request under two

kinds of restrictions: limited functional capabilities of computers that are used for allocation and processing DMA components, and limited resource availability for links and components.

In CINEMA, three levels of QoS are considered: client level QoS (C-QoS), session level QoS (S-QoS) and transport level QoS (T-QoS).

At the highest level, C-QoS is specified in a manner appropriate to end users, and hence is end-user-specific.

The QoS specified at the session level is media-specific. The media parameters of the stream's type and a number of generic parameters, such as delay, jitter and loss rate, define S-QoS of a stream. The client is responsible to map the C-QoS specified by the end user to the S-QoS at the session level. Of course, for a given type of S-QoS, various types of C-QoS and mappings are conceivable.

At the transport level, T-QoS is specified in a media independent fashion, e.g., such parameters as packet size, packet rate, burst size, delay, and jitter. In CINEMA, the mapping from media-specific QoS parameters to the T-QoS parameters is done within the link objects.

During session establishment, flowspecs are used to convey QoS information at the session and transport level. At the transport level, a flowspec carries media-independent parameters and is communicated along the selected network path. At the session level, a flowspec contains media specific and generic parameters and is passed along the flow graph structure, where both links and components are involved in QoS negotiation.

## 4 Configuration service

### 4.1 Negotiation requirements

Before discussing the configuration management, we consider DMA topology peculiarities, which cause QoS dependencies across the application topology. These dependencies have to be taken into account to construct QoS negotiation and mapping algorithms and protocols of the configuration service.

#### 4.1.1 Functional capabilities and resource shortages

Functional capabilities of a DMA component to support different QoS levels are restricted. Limited functional capabilities of components depend on their design. This kind of capabilities has to be taken into account just at the preparation phase of the DMA life cycle.

Moreover, different computers can implement components in various soft- and hardware ways, thereby it may also influence the component functional capabilities that are practicable. So, functional capabilities of DMA components may depend on functional capabilities of computers (their soft- and hardware) on which they are placed.

Resource shortage somewhere in a DCS (e.g. on the computer) forces a component or link (located in the computer) to support QoS below their functional limitations.

#### 4.1.2 Port type compatibility

In distributed multimedia applications, data streams are typed. Each media type defines a set of so-called media parameters, which specify the characteristics of a particular stream instance. As streams are communicated via ports, ports objects are typed and can only be linked if they are of compatible type. Such port type checking is performed during the preparation phase when application logical topology is instantiated.

#### 4.1.3 Format constraints of media parameters

As ports are typed, only a certain type of stream can be communicated via a given port. However, the instances of a particular stream type may significantly differ in their media parameter values. It cannot be assumed that a component port supports the entire value range for each media parameter.

To express the capabilities of components with regard to the stream formats they are able to consume and/or produce, so-called *format constraints* are introduced in [RDF97]. Each component port is associated with a media that is characterized by appropriate media parameters. Each media parameter has a (possibly empty) set of format constraints, which indicate the value range of such parameter that can be supported by the component at that port.

Format constraints for each media parameter associated with each component port depend on functional capabilities of computer, on which the component is placed. Hence, unlike XNRP, format constraints relate both to components and computers, and they have to be specified for each (component, computer) pair.

#### 4.1.4 Stream relations

In addition to format constraints, so-called *stream relations* between ports of a same component have to be considered by the negotiation process [RDF97]. For example, an audio mixer mixing several audio streams usually requires the same quality to be delivered at all input ports.

For fixed filter, a stream relation between input and output ports is as follows:

*param: @outport = F \* @inport.*

Such stream relation means that the value of media parameter at input port is to be F times greater than the value of this parameter at the output port. Here F denotes the filter factor.

For mixer components, mixing stream relations are defined between pairs of input ports  $(i,j)$ :

*param: @inport\_i =  $f_{i,j} * @inport_j$ .*

The relation means that the value of media parameter at input port  $i$  is to be  $f_{i,j}$  times the value of this parameter at input port  $j$ . For the mixer with  $n$  input ports, it is enough to specify  $n-1$  factors  $f_{i,j}$  relative to any input port  $j$ .

Mixing relation between the output port and an input port of a mixer

*param: @outport\_k =  $f_{k,j} * @inport_j$ .*

Usually, input port  $j$  of the mixer is chosen such that  $f_{k,j} = 1$  and such input port  $j$  is used for specification other  $n-1$  input ports. Hence, to define all stream relations between input and output ports of a mixer, it is enough to specify number of input ports and number  $j$  of the input port, relative to which filter factors of other input ports are specified. Such input port  $j$  of a mixer is called *key port*.

Obviously, the stream relations defined at a component not only affect the media parameters of this component's input and output streams but impact the entire flow graph.

#### 4.1.5 Topology complexity

Introducing mixing components and multicasting links into application topology makes the topology more complex. Such components and links complicate the negotiation process and cause additional QoS dependencies that reduce QoS ranges for which the negotiation process will be successful. To isolate and to reduce the impact of such QoS dependencies, the concept of special components, termed variable filters, is proposed in [DFR95], [DFBR95].

In effect, a variable filter decouples QoS provided at its input port from QoS delivered at its output port. This feature of the variable filter allows negotiating QoS for the DMA topology closer to QoS requirements and raises DMA session flexibility for “heterogeneous” QoS requests reflecting the varying QoS requests of independent (human) end-users supported by the client.

#### 4.1.6 Requirements to the configuration service

Above arguments laid the ground for requirements to the configuration service for distributed multimedia applications:

- Support for media specific QoS parameters,

- Support for port type compatibility for DMA logical topology (at the preparation phase),

- Support for various QoS due to limited functional capabilities of components, computers and resource availability of the computers,

- Support for media parameter format constraints associated with each component port. Unlike NRP [DFBR95] and XNRP [RDF97], the format constraints relate both to components and computers, and they have to be specified for each (component, computer) pair,

- Support for stream relations,

- Support for complex DMA topologies including mixing components, variable filters and multicasting links.

All these requirements have to be taken into account for development of the configuration service (realized by Configuration server).

## 4.2 Configuration service architecture

The configuration service is divided into three parts. One part, called application handler [Bar96], is located on the system the client is established and services the client to build up DMA logical topology as a flow graph at the preparation phase (see Figure 2.1). Application handler checks syntactically and semantically the topology, e.g., port type compatibility.

The second part, called configuration server, can be organized as a centralized entity. It starts at the session set-up phase (see Figure 2.1) and defines DMA physical topology including:

- selecting all DMA components that are part of session creation,

- defining format constraints for each component port,

- pre-negotiating media values between component ports for given QoS requirements taking into account format constraints and a set of acceptable computers for each component,

- mapping pre-negotiated DMA topology to the DCS,

- resource reservation for components, and sending and receiving sides of links,

- loading and instantiating components.

The third part, we call configuration handler following [Bar96], is based on XNRP [RDF97] and is distributed over the computers that have been used for allocation of DMA components. The configuration handler completes the session set-up phase including following operations:

- final QoS negotiation taking into account communication resource demands of the links and resource availability of the transport network,

- final computational and communication resource reservation,

- distribution of components on threads,

- preparation of all mechanisms necessary for stream synchronization.

At the termination phase (see Figure 2.1), configuration service selects all components that are part of session deletion, terminates the session and releases all resources occupied by the components.

The algorithms for selecting components, which are part of session creation and deletion, as well as for distribution of components on threads are proposed in [Bar96].

Let us discuss the configuration server in detail.

The main complexity to develop an algorithm of the configuration server is the interdependency of the QoS negotiation and DMA mapping processes. Actually, as argued above, format constraints relate both to components and computers, and they have to be specified for each (component, computer) pair. So, to negotiate QoS, format constraints for each port of every component must be given. To define format constraints, the functional capabilities and resource availability of computers, on which the components will be placed, have to be given, i.e. the components must be pre-attached to computers. However to find an acceptable or an optimal placement of components on computers, required resources of components and links are necessary. To define required resources, negotiated values of media parameters at each port corresponding to QoS requirements have to be given. Thus the “closed circle” is got that verifies the interdependency mentioned above.

To construct a configuration server algorithm, we base on approaches, methods and algorithms for QoS negotiation implemented in NRP [DFBR95] and XNRP [RDF97], and for DMA to DCS mapping developed in [HRD96], [HRD96a], [IH96].

It is important to note that QoS negotiation algorithms deal with QoS value ranges, i.e. format constraints. And they compute one value of each media parameter at every port in the DMA topology. Such set of point values obtained, on one hand, minimizes resource consumption, and on the other hand, supports the highest possible QoS values in the acceptable intervals of QoS requirements specified by the client at sink components.

In opposite side, at the beginning, the mapping algorithms deal with one value of resource demands for each resource type for every DMA component and link, and also with point values of available corresponding resources of a computer network. And they try to find an optimal or quasi-optimal placement of the DMA in the computer network.

Hence, the problem is to define initial format constraints as input data for the QoS negotiation algorithm. Then the point media values obtained by the algorithm are transformed to resource demands, which are used as input data by the mapping algorithm for DMA placement in the DCS.

The proposed approach for definition of initial format constraints is as follows. Configuration server asks every computer what kind of components and what format constraints for each component type it can support. Then, for each component of the DMA, a set of acceptable computers is created. After, the **aggregated format constraints** are defined for ports of each DMA component taking into account the corresponding set of acceptable computers and their format constraints.

When QoS negotiation algorithm will obtain the negotiated media values, these values will be used for refining the set of acceptable computers for every component. Obviously, every such refined set will contain not more computers than corresponding initial set.

### **4.3 Configuration service algorithm**

#### **4.3.1 General algorithm**

General representation of the configuration service algorithm is as follows:

1. Specifying (by the client) and checking (by the application handler) a DMA flow graph.

2. Specifying (by the client) clocks for stream synchronization, all source and sink components that have to be active in a session, QoS requirements, the component placement constraints.

3. Selecting all components that will be part of the session.

4. Specifying a set of acceptable computers and aggregated format constraints for each component.

5. Negotiating media values between component ports for highest possible user QoS requirements such that each media parameter at each port is characterized by one value and aggregated format constraints are satisfied. If the QoS negotiation failed then notify the client that user request can be not satisfied, stop.

6. Refining the set of acceptable computers for each component on the base of media values obtained.

7. Deriving resource requirements for each acceptable (component, computer) pair as well resource requirements of component's ingoing and outgoing links.

8. Assigning the DMA to the DCS.

9. If the assigning is not successful then checking whether the DMA can be placed in the DCS for lowest possible user QoS. For such checking, steps 5 - 8 are repeated but for lowest user QoS requirements.

If re-assigning failed then notify client that user-request can not be satisfied and stop, otherwise any policy can be used to improve the DMA assignment obtained.

10. Reservation of computer resources needed for components as well as for its sending and receiving links, loading and instantiating the components.

11. The configuration handler based on XNRP executes the operations mentioned in 4.2.

The configuration server executes steps 3 – 10.

#### **4.3.2 Input data for the configuration server**

Configuration server collects following information

1. From client:

- flow graph, including

- a) both all components (their classes and their port types) and links (adjacent components as well as type of their output and input ports connected by the link) specification,

- b) for each fixed filter, filter factor,

- c) for each mixer

- number of input ports,

- key input port,

- filter factors of input ports relative to the key port,

- QoS requests specified for input ports of sinks,

- the set of (pre-attached component, computer) pairs defining what components and to which computer they are assigned in advance (these are usually sink and source components).

2. From computers:

- set of component types supported by each computer (as result of admission control using information of functional capabilities and resource availability of the computers),

- format constraints for each (component type, acceptable computer) pair,

- resource requirements for (component, its negotiated media values, acceptable computer) triple,

- resource requirements for sending side (output port of one adjacent component) and receiving side (input port of other adjacent component) of each link,

- resource availability,

- cost of each resource type.

The configuration server asks and uses the data<sup>1</sup> from the client at step 3 (see 4.3.1).

The information about sets of supported components and format constraints is asked from computers and used at step 4 to derive aggregated format constraints. The latter is used then for QoS negotiation at step 5.

The data of resource requirements are asked from computers and used at step 7. It is important to note that QoS negotiation at step 5 makes possible to ask resource demand for each (component, its negotiated media values, acceptable computer) triple not for all values of media parameter range but only for one media value obtained at the step 5.

At step 8, the server asks and uses the data of resource availability and resource costs.

Thus, the configuration server requests the input data not simultaneously but consistently (step by step) and exactly at the step when the data is needed. Such approach allows to get actual data and take into account the results of the previous steps for revision the volume and content of the required data.

### 4.3.3 Refinement of the configuration server algorithm

Let us refine some steps of the general algorithm (see 4.3.1)

At step 4, the configuration server receives from each computer the set of supportable component types. Let  $SupCmpo_n$  denotes the set of component types supported by the computer  $n$ . Then to specify the set of acceptable computers  $AcCmpu_j$  for a DMA component  $j$ , the server includes in the set  $AcCmpu_j$  every such computer  $n$  which set  $SupCmpo_n$  contains the component  $j$ .

At step 4, the server receives also format constraints for each (component type, acceptable computer) pair. Assume that from all acceptable computers, the server got format constraints for a media parameter  $V$  for component  $j$   $FormCstr_j = \{(minV_n \dots maxV_n), n \in AcCmpu_j\}$ , where  $(minV_n \dots maxV_n)$  denotes value range for the parameter  $V$  provided by the computer  $n$ . Then the aggregated format constraints for the component  $j$  is obtained as  $(minV, maxV)$ , where  $minV = \min\{minV_n, n \in AcCmpu_j\}$  and  $maxV = \max\{maxV_n, n \in AcCmpu_j\}$ . So, the aggregated format constraints for any

---

<sup>1</sup> To include into consideration also end-to-end QoS requirements, (throughput, delay, loss-rate), additional input data are needed, namely corresponding QoS parameter values for each (component, computer) and (link, virtual channel) pairs. In the current report, to simplify a general conception of configuration server represented, we omit the end-to-end parameters.

media parameter at any port of a DMA component are obtained by merging all format constraints from all computers acceptable for the component.

At step 5, the server negotiates media values between ports of all DMA components in two phases. In the first phase, the aggregated format constraints are “propagated” in a down stream direction from source components to sink components. The results of the phase are possible QoS ranges provided by the sources to the sinks. In the second phase, best acceptable QoS are defined for sinks taking into account the QoS ranges obtained for sinks at the first phase and QoS requirements specified by the client at the input ports of sinks. Then obtained best acceptable QoS values are “propagated” from sinks to sources to define needed exact media values at every port of components including source components. During the propagation of QoS in both phases, the aggregated format constraints and stream relations are taken into account.

At step 5, the server realizes the first and second phases of XNRP [RDF97] but without resource constraint consideration, i.e. assuming that resources are unlimited. However it is important to note, that actually resource constraints were introduced before in aggregated format constraints, and thus, they are taken into account implicitly at the step 5. For a detailed description of the two phases algorithm we refer to [RDF97].

Negotiated media values for every port of DMA components obtained at step 5 are used for refinement of acceptable computers set for every component at step 6. It means the computers of set  $AcCmp_j$  that can not provide a negotiated media value for component  $j$  must be excluded from the set  $AcCmp_j$  of computers acceptable for this component.

Mapping the DMA to the DCS executed at step 8 will be discussed in detail in the next section.

At step 9, if the mapping for the best possible QoS is not successful then the server re-negotiates the DMA logical topology for lowest possible QoS and tries to map such the DMA to the DCS.

At step 10, the obtained DMA placement in the DCS with best possible QoS or with lowest possible QoS is used by the server to complete the session set-up phase.

It is important to note the step 9 could be supplemented such that if a DMA placement for lowest QoS is found, then one can try to re-place the DMA in a way to improve QoS. Different policy for DMA re-mapping can be used. Let us consider such one.

There are given

- for lowest user QoS requirements, resource requirements of each DMA component, sending and receiving links

- for highest QoS requirements, also resource requirements of each DMA component, sending and receiving links

Hence, each component  $i$  is characterized by resource difference  $dR_i$  needed to improve user QoS from the lower level to highest one. Using the flow graph of the DMA, one can determine which sinks are influenced by component  $i$ . Let  $dQoS_i$  is the sum of differences in QoS between the highest and the lowest levels for all sinks connected directly or indirectly with component  $i$ .

Then the component  $n$  with maximum value  $dQoS_n/dR_n$  is a start point for improving the QoS. The next acceptable higher media value of format constraints is chosen for this component, and one continues the algorithm from step 5 to renegotiate the port format constraints of DMA components and so on.

Thus we not have to do immediately with sink QoS requirements but with a component which minimum resource demand increase allows getting maximum QoS improvement.

If no acceptable DMA allocation exists for such DMA graph with new port format constraints then other component with maximum value  $dQoS_n/dR_n$  will be considered and so on until an acceptable DMA location for best possible QoS is found or a permissible time for the DMA mapping is finished.

## 5 Mapping a DMA to a DCS

### 5.1 *Introduction to mapping problem*

The general mapping problem<sup>1</sup> deals with the question of assigning components of a DMA to computers of a distributed system (network) so as to minimize a criterion (e.g. cost of usage of DCS resources) satisfying QoS requirements of DMA users and taking into account DCS functionality and resource constraints. The particular mapping problem deals with a DMA which components and links are specified by required computation and communicational resources that can guarantee requested QoS. Thus, in the particular mapping problem, QoS requirements are taken into account in an indirect way.

Several formulations of the mapping problem are known to be NP-Complete (e.g., [HDR96], [HDR96a]). Approximate techniques with polynomial complexity for mapping DMA, whose topology are restricted to a chain-like and tree-like structures are presented in [IH96]. In [HDR96] the mapping algorithm based on branch-bound method is proposed, and in [HDR96a] the technique for DMA initial placement improvement is considered.

There are no simple procedures, which can guarantee an optimal solution to the mapping problem due to its complexity. Therefore, heuristics techniques are employed as well to find pseudo-optimum or local optimum solutions.

Mapping techniques are usually either constructive or iterative. A constructive approach assigns the components one a time to the different computers until all components are eventually assigned. Constructive methods can be distinguished by the strategies to select the next unassigned component, and to assign the selected component.

Iterative methods transform a given complete placement into a new, hopefully improved, complete placement. If an acceptable criterion is satisfied, the new placement replaces the current one. This process is repeated until a stopping criterion is satisfied. During each iteration, a new placement is found by selecting some components and moving them to alternate computers. The initial placement needed to start the iterative process can be generated in any way, e.g. manually by user, randomly or, at last, using a constructive method.

In the paper, both constructive and iterative methods will be discussed.

Let us consider some peculiarities of the DMA topology and requirements of the real time resource management that must be taken into account for the mapping problem formulation.

The first one is the multicasting communication mode, that allows to use the capacity of a single real channel to transfer the same data to many sinks and is widely used in distributed multimedia applications. The DMA topology consisting of a single source, multicasting link and many sinks is the simplest example of multicasting application. . Multicasting logical topology can be mapped to multicasting physical topology if and only if the DCS (or some useful channels in a DCS) supports multicasting mode.

The multicasting case influences the computations of cost functions and resource usage in mapping algorithms.

Another feature of a DMA concerns, that computer resources needed for a component depend on whether adjacent components are placed in the same computer or in other one. If two adjacent components are allocated on the same computer no additional expenses are needed for their communication. In this case the capacity of required resources is determined only by processing modules of both components as soon as its link does not require the mapping to a DCS channel.

---

<sup>1</sup> The problems closed to the mapping are also addressed in literature as assignment problem (e.g. [Bok97]) or placement problem (e.g. [RPP94]). All these terms we use in our paper as synonyms.

However, should these components be placed on the different computers each of them will require, usually, transport and compression or decompression processing modules to interact. Hence, in the last case, such modules require additional computer resources that increase the total cost of DMA allocation. Thus, computation resources required by a component depend on whether the connected components are allocated to the same computer or not.

The next important property that must be taken into consideration is dynamic nature of the processes of allocating and releasing resources performed by distributed applications, which can start and terminate at random moments. So, the current resource availability of DCS units and channels varies in time. It makes the practical solution of the mapping problem even more complex. There is some kind of a contradiction: on one hand, the most mapping techniques assume that the DCS resource availability is fixed until the DMA assignment solution will be obtained. On other hand, the DCS resource availability is a function of a time and depends on other applications' activities.

In [RDH96a], static, pseudo-static and dynamic mapping policies that differ in duration of blocking the DCS available resources are considered. The dynamic policy does not require blocking but allows only step by step DMA component assignment and requires any re-assignment mechanism in the case if the resource manager can not support the requested resources for the allocation of the component assigned.

The duration of blocking in static and pseudo-static policies has a threshold, its violation may cause a deterioration of behavior of applications running at the same time in the DCS. Therefore, a mapping algorithm consuming a lot of time should be manageable to be interrupted at any time, to place already assigned components in a DCS, and to resume the work from an interrupted point when the control is given back from the system. Thus, it is desirable that a mapping algorithm assigning and allocating once a component to a computer does not revise that assignment. Just a few of mapping approaches have such a property, e.g., branch bound method based approach [HDR96] does not have this property.

## 5.2 Mathematical formulation

The mapping problem formulation is as follows. We are given:

1. A flow graph of DMA topology including

$\eta$  – a set of components,

$d_i(n)$  - a conditional required computational capacity for every component  $i$  (i.e. CPU cycles per second needed by the component to run normally) provided that computer  $n$  is used to assign component  $i$ ,

$m_i(n)$  - a conditional required memory amount for every component  $i$  provided that computer  $n$  is used to assign component  $i$ ,

$\lambda$  - a set of links connecting components with each other,  $\lambda = \{(i,j), i,j \in \eta\}$ ,

$b_{ij}$  - a required bandwidth for every link  $(i,j) \in \lambda$ ,

$d_{(ij)(nm)1}, d_{(ij)(nm)2}$  - a conditional required computational capacity for component  $i$  (a sender) and component  $j$  (a receiver) of a link  $(i,j) \in \lambda$  correspondingly to transfer (i.e. to send and to receive) data through the link provided that the components  $i$  and  $j$  are mapped to computers  $n$  and  $m$ . Parameters  $d_{(ij)(nm)1}, d_{(ij)(nm)2}$  compose a matrix of  $(|\lambda| * |\pi|)$  elements,

$m_{(ij)(nm)1}, m_{(ij)(nm)2}$  - a conditional required memory amount for component  $i$  (a sender) and component  $j$  (a receiver) of link  $(i,j) \in \lambda$  correspondingly provided that computers  $n$  and  $m$  are used<sup>1</sup>. Parameters  $m_{(ij)(nm)1}, m_{(ij)(nm)2}$  compose a matrix of  $(|\lambda| * |\pi|)$  elements,

$\zeta_i$  - a set of acceptable locations (computers) for every component  $i \in \eta$  in the DCS.

2. A DCS topology including

$\zeta$  - a set of computers,

---

<sup>1</sup> In so-called homogeneous situation, when computational and memory resources required by every component do not depend on which computer is used for placement, the parameter  $n$  can be omitted.

- a set of virtual channels (simply channels) connecting computers with each other,  $\zeta = \{(n,m), n, m \in \zeta\}$ ,

- $R_n, M_n$  - an available (vacant) computation and memory resources of every computer  $n \in \zeta$ ,

- a set of shared or/and dedicated communicational resources in the DCS<sup>1</sup>,

- $\rho_{nm}$  - a set of communicational resources of the DCS used by channel  $(n,m)$ ,  $\rho_{nm} \in \rho$ ,  $\rho = \cup \rho_{nm}$ ,

- $\pi_s$  - a set of channels routed over communicational resources  $s \in \rho$ ,  $\pi = \cup \pi_s$ ,

- $A_s$  - a bandwidth of a communicational resource  $s$  available to the DMA,  $s \in \rho$ .

### 3. Cost functions

- $f$  - a matrix  $(|\eta| * |\zeta|)$  of component's allocations costs, an element  $f_{in}$  of  $f$  specifies the cost of mapping component  $i$  to computer  $n$ . If component  $i$  can not be assigned to computer  $n$  then  $f_{in} = \infty$ ,

- $g$  - a matrix  $(|\lambda| * |\pi|)$  of link's allocations costs, an element  $g_{(ij)(nm)}$  of  $g$  specifies the cost of mapping link  $(i,j)$  to virtual channel  $(n,m)$ . If link  $(i,j)$  can not be assigned to channel  $(n,m)$  then  $g_{(ij)(nm)} = \infty$ ,

- $u$  - a matrix  $(|2\lambda| * |\pi|)$  of costs for link sending and receiving sides allocations, an elements  $u_{(ij)(nm)1}$  and  $u_{(ij)(nm)2}$  of  $u$  specifies the cost of mapping the link sending side (output port of component  $i$ ) to computer  $n$  and the link receiving side (input port of component  $j$ ) to computer  $m$  correspondingly. If link  $(i,j)$  can not be assigned to channel  $(n,m)$  then  $u_{(ij)(nm)1} = \infty$  and  $u_{(ij)(nm)2} = \infty$ .

The solution variables are  $x_{in}$  such that  $x_{in} = 1$ , if component  $i$  is assigned to computer  $n$ , and  $x_{in} = 0$  otherwise.

The general mapping problem is to minimize the total cost of DCS resources used for DMA allocation

$$F(x_{in}) = \min \{ \sum_{n \in \zeta} \sum_{i \in \eta} x_{in} * f_{in} + \sum_{(n,m) \in \pi} \sum_{(i,j) \in \lambda} x_{in} * x_{jm} * (g_{(ij)(nm)} + u_{(ij)(nm)1} + u_{(ij)(nm)2}) \} \quad (5.1)$$

subject to

every component  $i$  of the DMA have to be placed on a DCS computer and only on one computer

$$\sum_{n \in \zeta} x_{in} = 1, \forall i \in \eta, \quad (5.2)$$

computational resource of each computer  $n \in \zeta$  used by all components assigned to the computer, and also by corresponding sending and receiving sides of links, must not exceed the available resource of the computer

$$\sum_{i \in \eta} [x_{in} * d_i(n) + \sum_{j \in \eta} \sum_{m \in \zeta} x_{jm} * (d_{(i,j)(nm)1} + d_{(i,j)(nm)2})] \leq R_n, \quad \forall n \in \zeta, i \neq j, n \neq m \quad (5.3)$$

memory units of each computer  $n \in \zeta$  used by all components assigned to the computer, and also by corresponding sending and receiving sides of links, must not exceed the available resource of the computer

$$\sum_{i \in \eta} [x_{in} * m_i(n) + \sum_{j \in \eta} \sum_{m \in \zeta} x_{jm} * (m_{(i,j)(nm)1} + m_{(i,j)(nm)2})] \leq M_n, \quad \forall n \in \zeta, i \neq j, n \neq m \quad (5.4)$$

total bandwidth of all DMA links mapped on communication resource  $s$  must not exceed the available bandwidth of the resource

$$\sum_{(n,m) \in \pi} \sum_{(i,j) \in \lambda} x_{in} * x_{jm} * b_{ij} \leq A_s, \quad \forall s \in \rho \quad (5.5)$$

Here  $g_{(ij)(nn)} = 0$  if components  $i$  and  $j$  are assigned to a same computer  $n$ ,  $(i,j) \in \lambda$ ;  $g_{(ij)(nm)} > 0$  if components  $i$  and  $j$  are assigned to different computers, i.e.  $n \neq m$ ,  $(i,j) \in \lambda$  and  $(n,m) \in \pi$ . Similarly,  $u_{(ij)(nn)1} = 0$  and  $u_{(ij)(nn)2} = 0$  if components  $i$  and  $j$  are assigned to a same computer  $n$ ,  $(i,j) \in \lambda$ ;  $u_{(ij)(nm)1} >$

<sup>1</sup> Depending on used mapping algorithm, different communication resources can be taken into account. For example, to simplify the mapping algorithm only computer interfaces and its bandwidths (and no communication links or networks) can be considered.

0 and  $u_{(ij)(nn)2} > 0$  if components i and j are assigned to different computers, i.e.  $m \neq n$ ,  $(i,j) \in \lambda$  and  $(n,m) \in \pi$ .

It is important to note that if it is needed take into account no resources of the communication network of the DCS then one omits coefficients  $g_{(ij)(nm)}$  in the objective function F and considers communication constraints (5.5) only for computer communication interfaces.

This mapping problem formulation is a nonlinear integer programming NP problem with Boolean variables.

### 5.3 *Mapping algorithms*

Several algorithms for mapping problem solution are presented in this section below.

#### 5.3.1 **An exact searching algorithm**

An exact algorithm is based on a branch-bound method [Min86] and takes into account the peculiarities of the mapping problem by building the search tree, choosing the bounding function to be assigned with each leaf of this tree and searching for the “optimal” vertex on each step that corresponds to the component that has to be mapped.

Actually, the exact algorithm we propose, consists of the following steps:

1. Mapping the pre-attached components (that are assigned to particular computers by the client in advance).

2. Choosing the next component to be mapped.

3. Generating all acceptable locations for this component.

4. Computing the bounding function for every feasible location.

5. Choosing the best assignment for the component using the bounding values found above.

6. Checking whether all components have been assigned. Return to step 2 if there’re unassigned component in a DMA otherwise an optimal DMA placement in the DCS is found.

7. The obvious advantage of the exact mapping algorithm is concluded in its orientation on obtaining an optimal mapping variant. However, exponential complexity of its implementation does not allow using this method in practice for really large mapping problems.

Let us consider several rules that allow to improve time complexity of the algorithm (still keeping it as exponential).

The first problem we face at step 2 is to select the unassigned component. All selection rules can be divided into the two general classes: static and dynamic.

A static selection rule orders all components with respect to a chosen criterion only once, usually at the beginning of the algorithm. Then the algorithm chooses sequentially, from this ordered set, the next component to assign. An advantage of static rules is its low time expense. A disadvantage is the impossibility to take into account dynamic features of assignment process, unassigned part of the DMA topology and available DCS resources.

A dynamic rule computes a selection criterion on every step of an algorithm. Dynamic rules do not need a preliminary complete ordering of all components as the static mode. It is enough to find the next component according to criterion chosen without ordering the other components every time. A criterion of a dynamic rule can take into account dynamic features mentioned above; and therefore, in comparison with static one, usually it narrows the domain of optimal solution search more effectively. However, on the other hand, the regular re-computation of the criterion increases time expenses and the total algorithm complexity.

Before considering several rules to select a component, we would like to introduce so-called TIGHTNESS value. As computational experiments have shown, TIGHTNESS is very useful for algorithm efficiency analysis and to get a domain of advantageous usage for rules and heuristics.

TIGHTNESS value is used to specify the relative difference between the amount of available DCS resources and the amount of DCS resources required by the DMA components and links. Let  $D_i$  be the amount of a resource required by component  $i$ , and  $R_n$  be the amount of available resources on computer  $n$ . Then for computer  $n$  and for given resource type

$$TIGHTNESS(n) = \sum_i D_i / R_n * 100\%, \quad (5.6)$$

where the sum is taken over all components for which the computer  $n$  is acceptable.

Actually, when TIGTNESS value is set to 100, one can expect the redundancy of available network resources. That fact, in its turn, may lead to the existence of a large number of feasible mapping variants, and finding an optimal allocation in this case may require more time. With TIGHTNESS value set to 100, we can also expect that all DMA components would finally be allocated to the same DCS computer thereby making the communicational expenses negligible. However, this way doesn't always lead to the optimal solution, especially when the computational resources required by the DMA components excel the communicational expenses required by the DMA graph in values.

By decreasing the TIGHTNESS value, one can achieve the situation in which there exist only few possible DMA allocation variants over the DCS graph. Actually, there is a limit for the TIGHTNESS value below that we cannot obtain any feasible mapping variants.

Several examples to demonstrate the effect of TIGHTNESS on solutions found by different algorithms will be presented below.

### 5.3.1.1 Component selection rules

The proposed component selection rules and their characteristics are presented in Table 5.1.

The *first* simple one is to choose the next component in the increasing order of the number of acceptable computers. Thus, the component that has less initial acceptable locations will be chosen for assignment before others.

Obviously, in the dynamic mode, the minimum number of acceptable computers can only be decreased during the algorithm execution with increasing number components assigned and decreasing available DCS resources. If not yet assigned component  $i$  has a current set  $\zeta_i$  of acceptable computers then the next component with  $\min\{|\zeta_i|, i\}$  is varied over all not yet assigned components} will be chosen, where  $|\zeta_i|$  is a cardinality of set  $\zeta_i$ .

This dynamic rule is very useful if, on every step of the algorithm, there exists only one acceptable computer for one or more components. Such components have so-called non-alternative assignment. Every such component must be assigned as early as possible. If its assignment will be postponed then chances to map the component will decrease in time because the available resources of the acceptable computer will decrease as well. This rule allows rejecting, as early as possible, the vertices in a search tree that can lead to a DMA allocation that is not acceptable. So, the rule supports the narrowing of the domain of optimal solution search.

Note, that the pre-attached components, that are assigned by the client in advance have also non-alternative assignments. At step 1, the algorithm checks the possibility of such assignments.

The rule to select the next component in the order of increasing the number of acceptable computers is one of the best from the point of time expense for static mode. However, in the static mode, only a situation at the beginning of the algorithm is considered. On the contrary, in the dynamic mode, current number of acceptable computers for each component is taken into account. That is right for all other rules: a dynamic rule takes into account a current value of a criterion used.

The *second* rule considered is to select the next component in the order of decreasing the resources required for component allocation. So, a component with largest resource demand will be chosen before others. This rule is useful in the case when one or more computers are acceptable for many components that have a large variation in the resource demands provided that the computers have a low or moderate TIGHTNESS. The rule allows to avoid the situation when components with relative

low resource demands will be placed first on such computer and do not permit to place the components with higher resource demands.

Table 5.1 Rules for choosing the next component to be assigned

| Rule                                                   | Static                                                                                                                                               |                                                                                                                        |                                                                                                                                         | Dynamic <sup>1</sup>                                     |                                                         |                                                         |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Selecting the next not yet assigned component that has | Minimum number of computers acceptable for the component                                                                                             | Maximum resources required by the component                                                                            | Maximum degree                                                                                                                          | Minimum number of computers acceptable for the component | Maximum resources required by the component             | Maximum degree                                          |

| Advantages                                             | Low time expense                                                                                                                                     | Low time expense                                                                                                       | Low time expense                                                                                                                        | More effective for narrowing the solution search domain  | More effective for narrowing the solution search domain | More effective for narrowing the solution search domain |

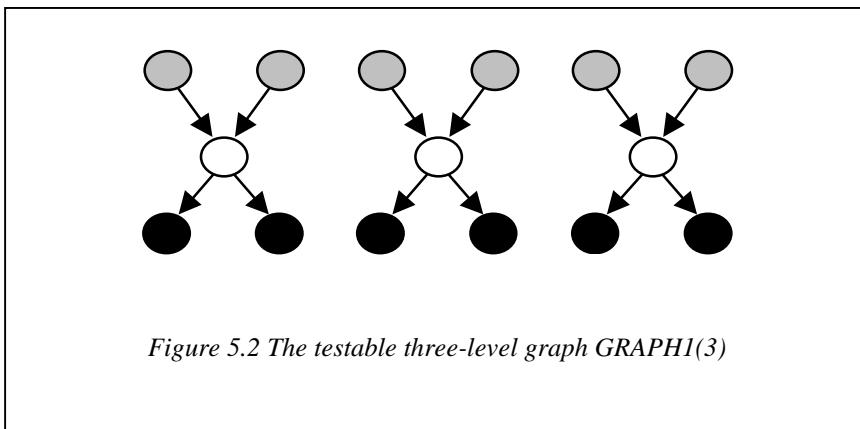

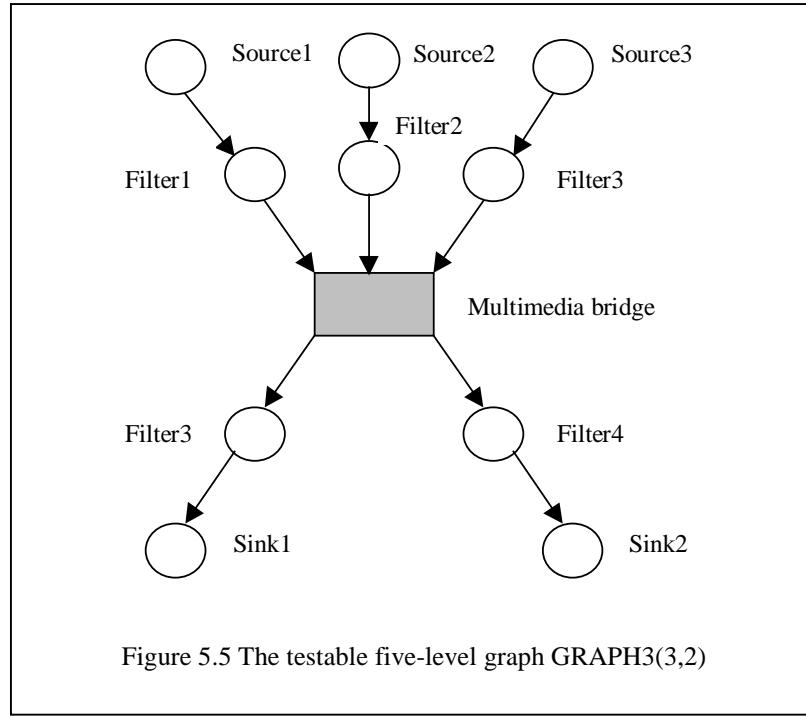

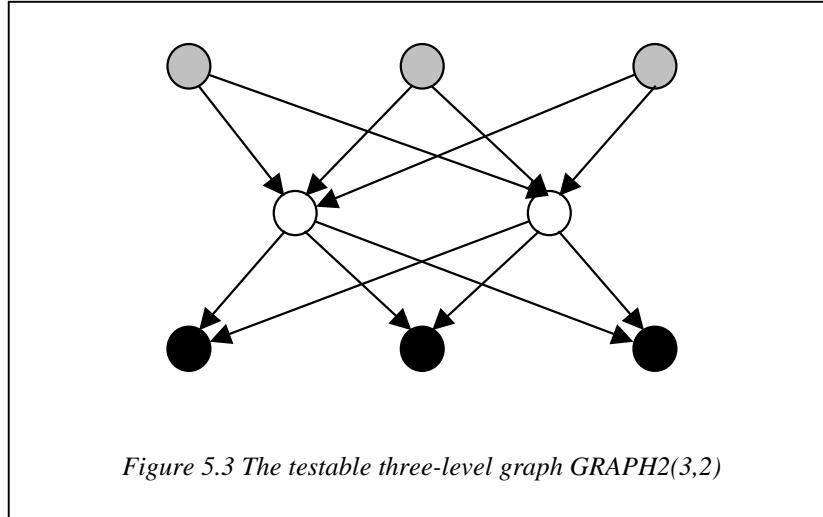

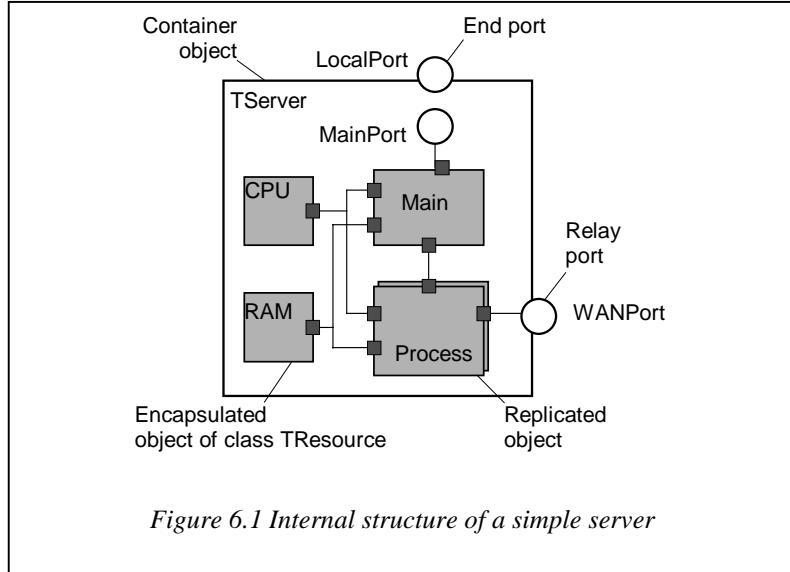

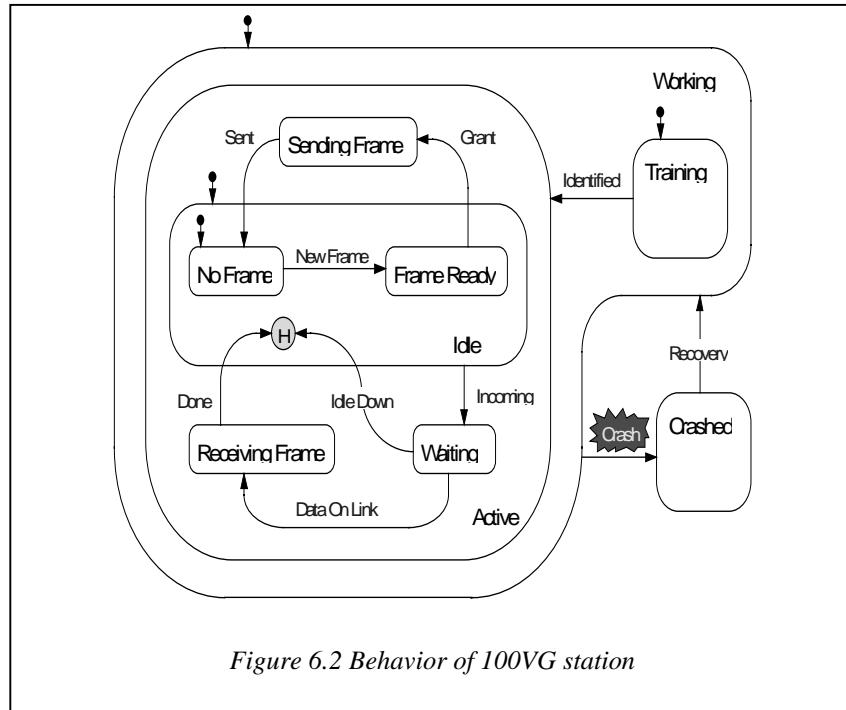

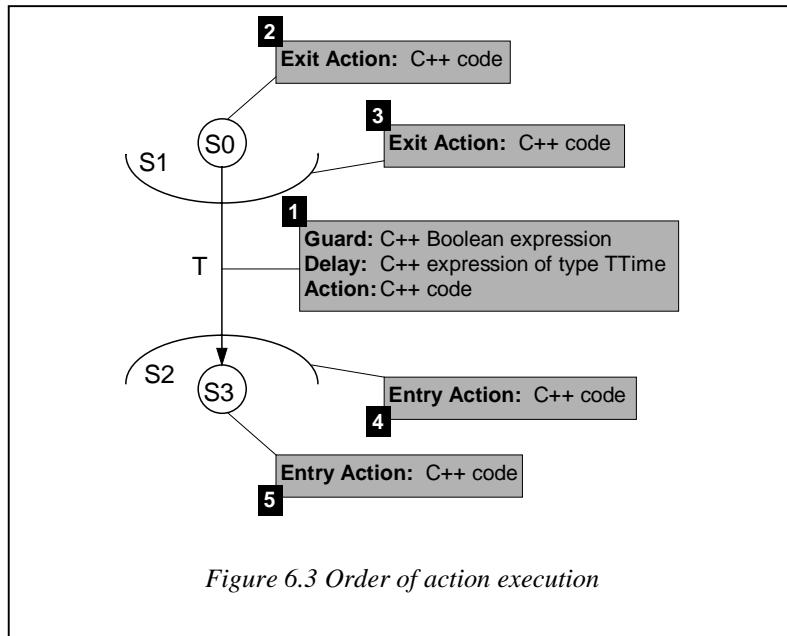

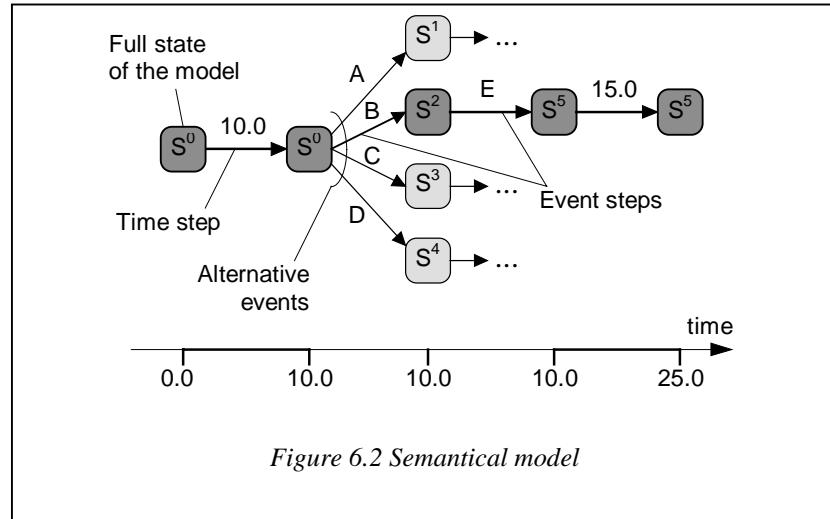

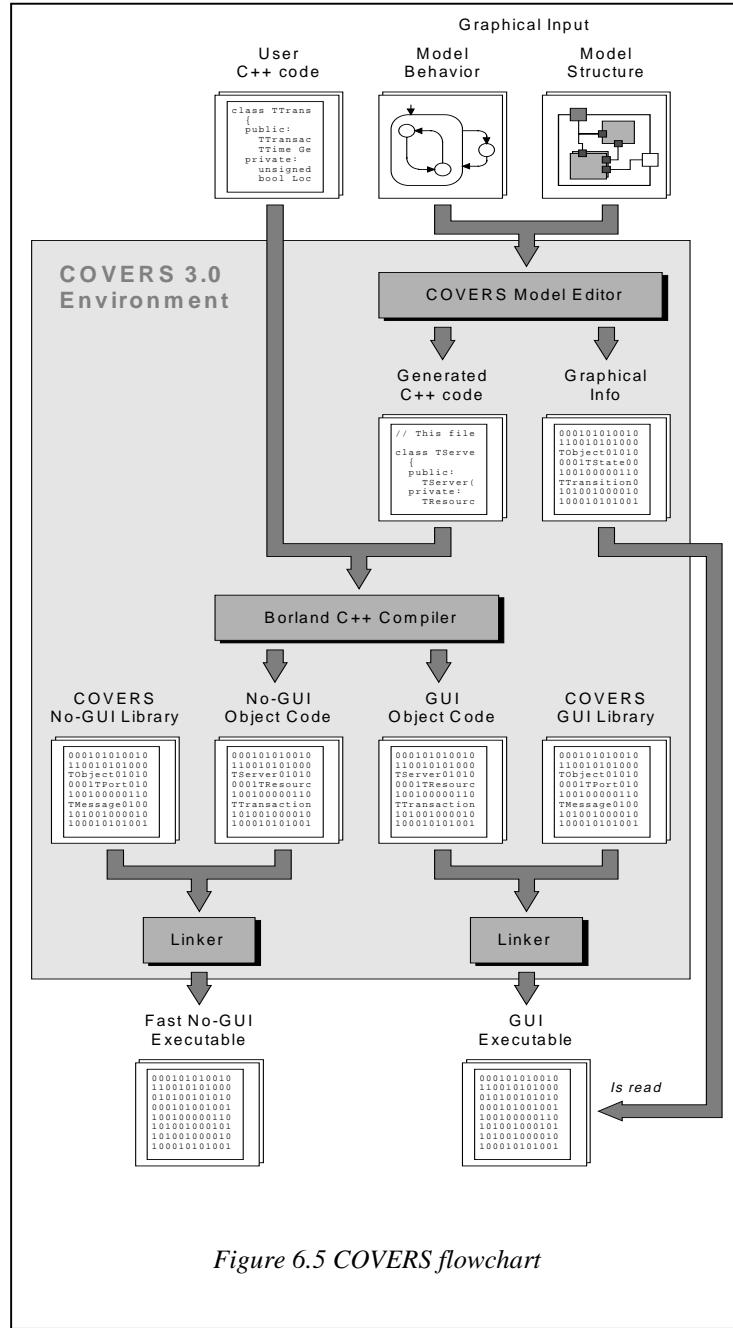

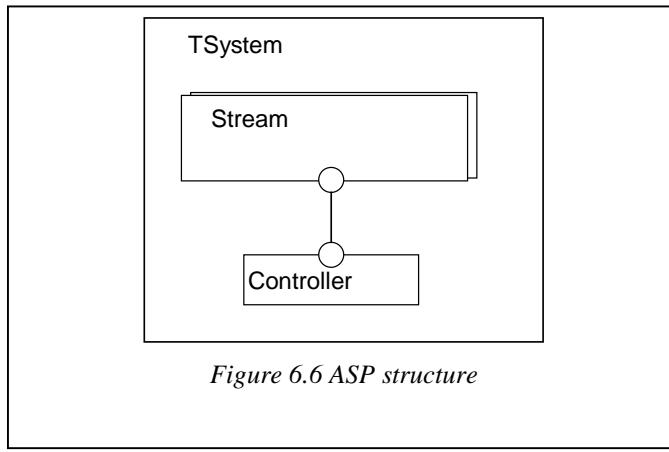

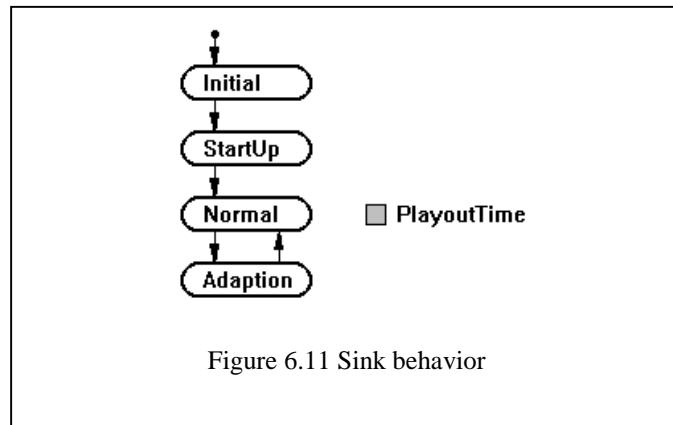

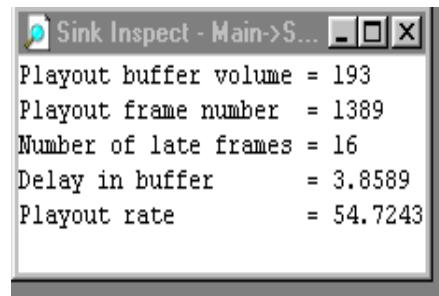

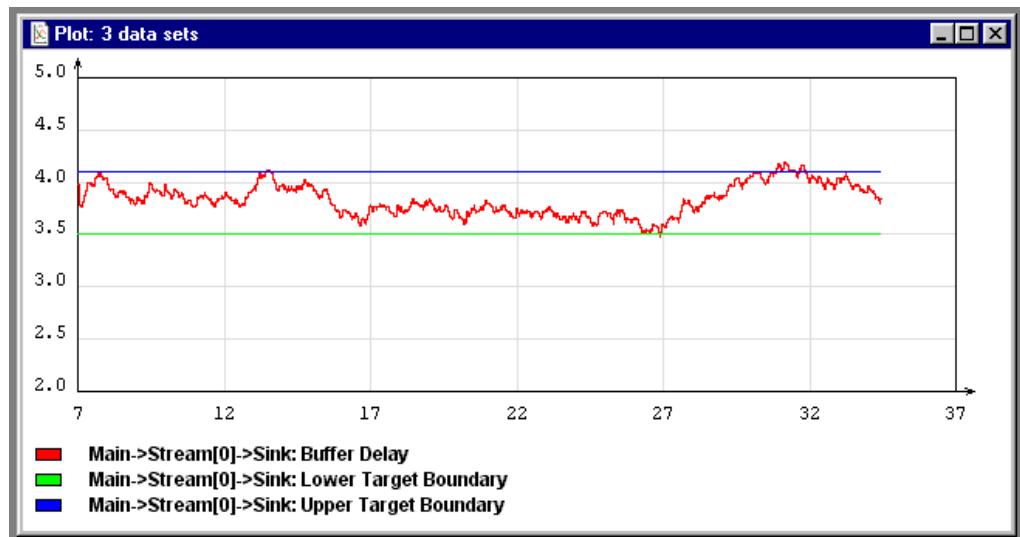

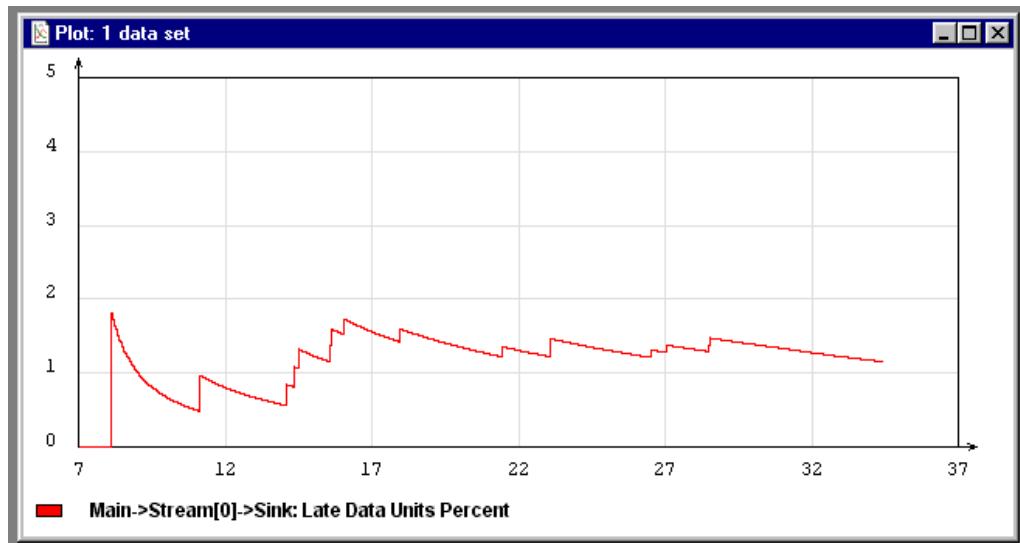

| Disadvantages                                          |                                                                                                                                                      |                                                                                                                        |                                                                                                                                         | High time expense                                        | High time expense                                       | High time expense                                       |